#### THE FRONTIERS COLLECTION

NANO-CHIPS 2030 NANO-CHIPS 203

Boris Murmann Bernd Hoefflinger (Eds.)

# NANO-CHIPS 2030

NANO-CHIPS 2030 NANO-C

HIPS 2030 NANO-CHIPS 20

30 NANO-CHIPS 2030 NANO

O-CHIPS 2030 NANO-CHIPS

S 2030 NANO CHIPS 2030

NANO-CHIPS 2030 NANO-C

HIPS 2030 NANO-CHIPS 20

30 NANO-CHIPS 2030 NAN

O-CHIPS 2030 NANO-CHIP

S 2030 NANO CHIPS 2030

NANO-CHIPS 2030 NANO-C

HIPS 2030 NANO-CHIPS 20

On-Chip AI for an Efficient

Data-Driven World

#### THE FRONTIERS COLLECTION

#### **Series Editors**

Avshalom C. Elitzur, Iyar, Israel Institute of Advanced Research, Rehovot, Israel Zeeya Merali, Foundational Questions Institute, Decatur, GA, USA Thanu Padmanabhan, Inter-University Centre for Astronomy and Astrophysics (IUCAA), Pune, India

Maximilian Schlosshauer, Department of Physics, University of Portland, Portland, OR, USA

Mark P. Silverman, Department of Physics, Trinity College, Hartford, CT, USA Jack A. Tuszynski, Department of Physics, University of Alberta, Edmonton, AB, Canada

Rüdiger Vaas, Redaktion Astronomie, Physik, bild der wissenschaft, Leinfelden-Echterdingen, Germany The books in this collection are devoted to challenging and open problems at the forefront of modern science and scholarship, including related philosophical debates. In contrast to typical research monographs, however, they strive to present their topics in a manner accessible also to scientifically literate non-specialists wishing to gain insight into the deeper implications and fascinating questions involved. Taken as a whole, the series reflects the need for a fundamental and interdisciplinary approach to modern science and research. Furthermore, it is intended to encourage active academics in all fields to ponder over important and perhaps controversial issues beyond their own speciality. Extending from quantum physics and relativity to entropy, consciousness, language and complex systems—the Frontiers Collection will inspire readers to push back the frontiers of their own knowledge.

More information about this series at http://www.springer.com/series/5342

Boris Murmann · Bernd Hoefflinger Editors

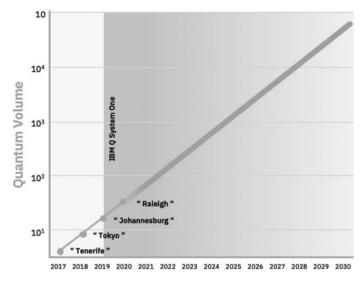

## NANO-CHIPS 2030

On-Chip AI for an Efficient Data-Driven World

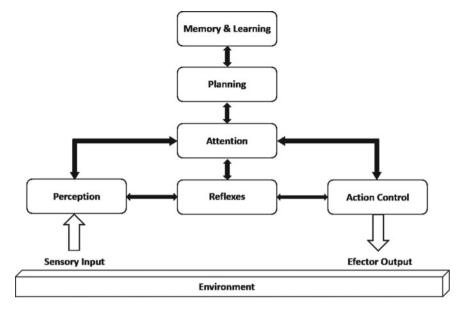

Editors

Boris Murmann

Department of Electrical Engineering

Stanford University

Stanford, CA, USA

Bernd Hoefflinger Sindelfingen, Baden-Württemberg, Germany

ISSN 1612-3018 ISSN 2197-6619 (electronic)

The Frontiers Collection

ISBN 978-3-030-18337-0 ISBN 978-3-030-18338-7 (eBook)

https://doi.org/10.1007/978-3-030-18338-7

#### © Springer Nature Switzerland AG 2020

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, expressed or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This Springer imprint is published by the registered company Springer Nature Switzerland AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

### **Contents**

| 1  | Boris Murmann and Bernd Hoefflinger                                                                                                                                                                           | 1   |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2  | IRDS—International Roadmap for Devices and Systems, Rebooting Computing, S3S                                                                                                                                  | 9   |

| 3  | Real-World Electronics Bernd Hoefflinger                                                                                                                                                                      | 19  |

| 4  | Silicon Complementary MOS into Its 7th Decade                                                                                                                                                                 | 31  |

| 5  | Nanolithography                                                                                                                                                                                               | 41  |

| 6  | The Future of Ultra-Low Power SOTB CMOS Technology and Applications  Nobuyuki Sugii, Shiro Kamohara and Makoto Ikeda                                                                                          | 47  |

| 7  | Dealing with the Energy Versus Performance Tradeoff in Future CMOS Digital Circuit Design  Wim Dehaene, Roel Uytterhoeven, Clara Nieto Taladriz Moreno and Bob Vanhoof                                        | 89  |

| 8  | Monolithic 3D Integration—An Update  Zvi Or-Bach                                                                                                                                                              | 117 |

| 9  | Heterogeneous 3D Nano-systems: The N3XT Approach?  Dennis Rich, Andrew Bartolo, Carlo Gilardo, Binh Le, Haitong Li, Rebecca Park, Robert M. Radway, Mohamed M. Sabry Aly, HS. Philip Wong and Subhasish Mitra | 127 |

| 10 | <b>High-Speed 3D Memories Enabling the AI Future</b> Zvi Or-Bach                                                                                                                                              | 153 |

vi Contents

| 11 | 3D for Efficient FPGAZvi Or-Bach                                                                                                                                                           | 165 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

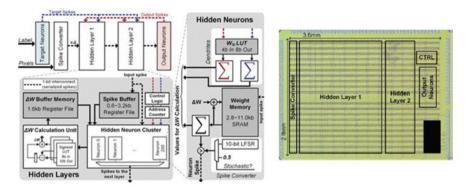

| 12 | Digital Neural Network Accelerators Ulrich Rueckert                                                                                                                                        | 181 |

| 13 | Enabling Domain-Specific Architectures with Programmable Devices Alireza Kaviani                                                                                                           | 203 |

| 14 | Coarse-Grained Reconfigurable Architectures Raghu Prabhakar, Yaqi Zhang and Kunle Olukotun                                                                                                 | 227 |

| 15 | A 1000× Improvement of the Processor-Memory Gap Zvi Or-Bach                                                                                                                                | 247 |

| 16 | <b>High-Performance Computing Trends</b>                                                                                                                                                   | 269 |

| 17 | Analog-to-Information Conversion                                                                                                                                                           | 275 |

| 18 | Machine Learning at the Edge                                                                                                                                                               | 293 |

| 19 | The Memory Challenge in Ultra-Low Power Deep Learning Francesco Conti, Manuele Rusci and Luca Benini                                                                                       | 323 |

| 20 | Multi-sensor Scenarios for Intelligent SOCs                                                                                                                                                | 351 |

| 21 | <b>High-Dynamic-Range and Wide Color Gamut Video</b> Zhichun Lei, Xin Yu and Markus Strobel                                                                                                | 359 |

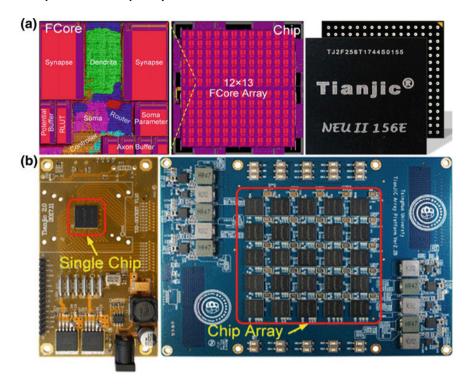

| 22 | Update on Brain-Inspired Systems                                                                                                                                                           | 387 |

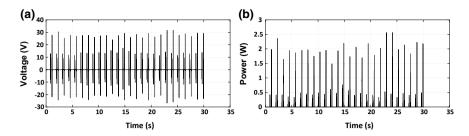

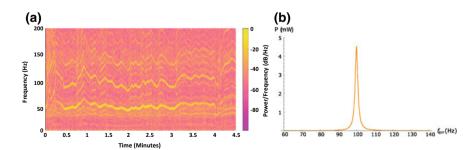

| 23 | Energy-Harvesting Applications and Efficient Power Processing Thorsten Hehn, Alexander Bleitner, Jacob Goeppert, Daniel Hoffmann, Daniel Schillinger, Daniel A. Sanchez and Yiannos Manoli | 405 |

| 24 | Artificial Retina: A Future Cellular-Resolution Brain-Machine Interface                                                                                                                    | 443 |

| 25 | Augmented and Virtual Reality                                                                                                                                                              | 467 |

Contents vii

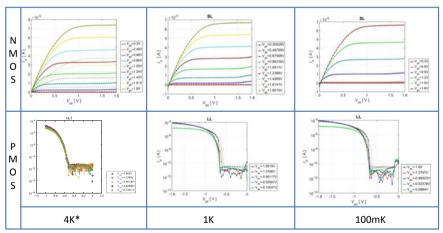

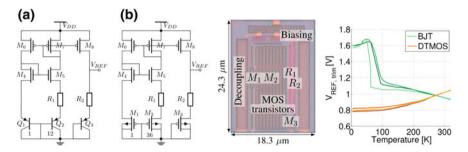

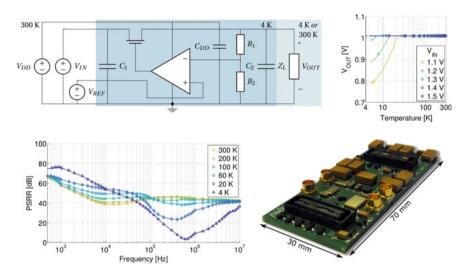

| 26  | Cryogenic-CMOS for Quantum Computing  Edoardo Charbon, Fabio Sebastiano, Masoud Babaie and Andrei Vladimirescu | 501 |

|-----|----------------------------------------------------------------------------------------------------------------|-----|

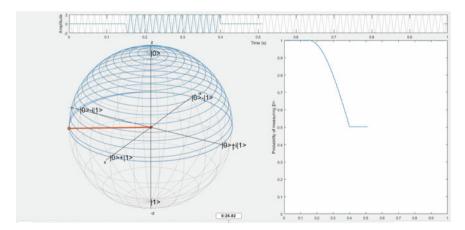

| 27  | Quantum Computing  Albert Frisch, Harry S. Barowski, Markus Brink and Peter Hans Roth                          | 527 |

| 28  | <b>Human-Machine Interaction and Cognitronics</b>                                                              | 549 |

| 29  | Efficient System-on-Chip (SOC) for Automated Driving with High Safety                                          | 563 |

| 30  | The Thirties  Boris Murmann and Bernd Hoefflinger                                                              | 577 |

| Ind | ex                                                                                                             | 585 |

#### **Editors and Contributors**

#### **About the Editors**

**Boris Murmann** received his Ph.D. degree from the University of California, Berkeley in 2003 and serves as a professor of electrical engineering at Stanford University. His research interests are in mixed-signal integrated circuit design, with a focus on sensor interfaces, data converters, and custom circuits for embedded machine learning. He has served as an associate editor of the IEEE Journal of Solid-State Circuits, an AdCom member, and a distinguished lecturer of the IEEE Solid-State Circuits Society, as well as the data converter subcommittee chair and the technical program chair of the IEEE International Solid-State Circuits Conference (ISSCC). He is a fellow of the IEEE.

**Bernd Hoefflinger** became an assistant professor at Cornell University, Ithaca, NY, USA, after completing his Ph.D. at the Technical University of Munich, Germany. He was a co-founder of the MOS Division of Siemens in Munich and founded the electrical engineering department of the University of Dortmund, Germany, which houses the first Ion-Implanted BiCMOS production line. After serving as the head of the electrical engineering departments at the University of Minnesota and then at Purdue University in Indiana, he established the Institute of Microelectronics Stuttgart, Germany, as the first ISO 9000-certified research and manufacturing facility—a leader in ASICs, HDR vision, and e-beam-driven nanotechnology.

#### **Contributors**

**Masoud Babaie** received the Ph.D. (cum laude) degree from the Delft University of Technology, Delft, The Netherlands, in 2016. In 2006, he joined the Kavoshcom Research and Development Group, Tehran, where he was involved in designing wireless communication systems. From 2009 to 2011, he was a CTO of that

x Editors and Contributors

company. From 2014 to 2015, he was a visiting scholar researcher with the Berkeley Wireless Research Center, Berkeley, CA, USA. In 2016, he joined the Delft University of Technology, where he is currently an assistant professor (tenured). He has co-authored one book, two chapters, 11 patents, and over 40 technical publications. His current research interests include RF/millimeter-wave integrated circuits and systems for wireless communications and cryogenic electronics for quantum computation. He has been a committee member of ISSCC Student Research Preview since 2017 and will join as a technical program committee of ESSCIRC in 2020. He was a co-recipient of the 2015–2016 IEEE Solid-State Circuits Society Pre-Doctoral Achievement Award and the 2019 IEEE ISSCC Best Demo Award. In 2019, he received the Veni Award from the Netherlands Organization for Scientific Research.

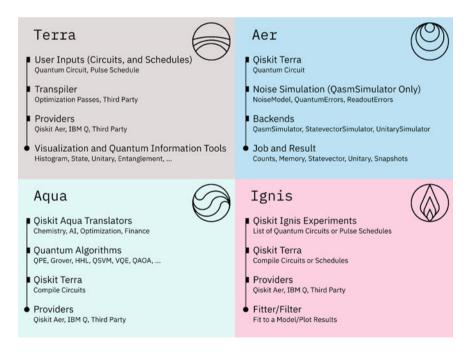

Harry S. Barowski studied physics at the University of Regensburg, where he graduated in low-temperature physics 1994. He finished his doctoral degree in 1997 on far and infrared spectroscopy on various types of cuprate-based high-temperature superconductors. After finishing his doctoral study, he started his career as logic designer of mainframe processors at IBM Research and Development in Boeblingen, Germany. Here he worked in logic design as logic design engineer professional of computational units for high-performance processors for P and Z systems and gaming consoles (Cell processor for Sony Playstation). He also was engaged in the field of formal logic verification and custom circuit design. He currently is focussed on custom array design and physical and logical design verification methodologies. As IBM master inventor, he drives technical innovations and new technologies. He contributed to several aspects of IBM system Q, such as design of classical hardware components to the IBM Q System One, superconducting chip design and was coaching the IBM Extreme Blue internship on implementation of the well-known HHL algorithm to solve a system of linear equations into Oiskit.

**Andrew Bartolo** received the B.S. and M.S. degrees in computer science from Stanford University, Stanford, CA, USA, where he is currently working toward the Ph.D. degree in computer science. His work focuses on hardware and software support for computation immersed in memory. His current research interests include the fields of architecture, compilers, digital design, and networking.

**Luca Benini** holds the chair of digital circuits and systems at ETHZ and is a full professor at the Università di Bologna. His research interests are in energy-efficient parallel computing systems, smart sensing micro-systems, and machine learning hardware. He has published more than 1000 peer-reviewed papers and five books. He is a fellow of the IEEE, of the ACM and a member of the Academia Europaea.

**Alexander Bleitner** received the B.Sc. and M.Sc. degrees in embedded systems engineering from the University of Freiburg, Freiburg, Germany, in 2013 and 2017, respectively, where he is currently pursuing the Ph.D. degree at the Fritz Huettinger Chair of Microelectronics, Department of Microsystems Engineering—IMTEK. From 2010 to 2013, he was an intern at Siemens Medical Solutions in Forchheim,

Editors and Contributors xi

Germany. There, he developed electronic circuits and FPGA designs for medical imaging. Additionally, in 2015, he pursued an internship at the Bosch Research and Technology Center in Palo Alto, CA, USA. During this internship, he was working on image processing algorithms and integrated circuit designs for a low-power image sensor. Currently, his main research interests evolve around ultra-low-voltage and ultra-low-power circuits using Schmitt trigger structures in the subthreshold region with a focus on digital standard cell and memory design.

Markus Brink as a physics graduate student in Paul McEuen's laboratory at Cornell University, investigated electronic properties of low-dimensional nanostructures using cryogenic scanning force microscopy combined with electronic transport measurements. He graduated from Cornell University in 2006 and started as postdoctoral associate in QLab with Michel Devoret at Yale University, where he built and characterized his first superconducting qubit circuits. In 2010, he joined IBM as a researcher at the T. J. Watson Research Center, where he has worked on scaling of classical (CMOS) and quantum hardware.

**Carlo Gilardo** received his B.S. (2015) and M.S. (2017) in engineering physics at Politecnico di Milano, Milan, Italy, and is currently pursuing his Ph.D. in electrical engineering at Stanford University, Stanford, CA. His current research interests include modeling and simulation of nanoscale carbon nanotube electronic devices and technology assessment and benchmarking.

Edoardo Charbon (SM'00-F'17) received the Diploma from ETH Zurich, the M.S. from the University of California at San Diego, and the Ph.D. from the University of California at Berkeley in 1988, 1991, and 1995, respectively, all in electrical engineering and EECS. He has consulted with numerous organizations, including Bosch, X-Fabs, Texas Instruments, Maxim, Sony, Agilent, and the Carlyle Group. He was with Cadence Design Systems from 1995 to 2000 and with Canesta from 2000 to 2002. Since 2002, he is a member of the faculty of EPFL, full professor since 2015. From 2008 to 2016, he was a full professor and chair of VLSI design with Delft University of Technology. He has been the driving force behind the creation of CMOS SPAD technology, which is mass produced since 2015 and the core of telemeters, proximity sensors, and medical diagnostics. His interests span from 3D vision, LiDAR, FLIM, FCS, NIROT to super-resolution microscopy, time-resolved Raman spectroscopy, and cryo-CMOS circuits and systems for quantum computing. He has authored or co-authored over 350 papers and two books, and he holds 21 patents. He has received several best paper awards and the prestigious award for best academic research team in Europe (London, 2019). He is a distinguished visiting scholar of the W. M. Keck Institute for Space at Caltech, a fellow of the Kavli Institute of Nanoscience Delft, and a fellow of the IEEE.

**E. J. Chichilnisky** is the John R. Adler Professor of Neurosurgery and Professor of Ophthalmology, at Stanford University, where he has worked since 2013. Previously, he worked at the Salk Institute for Biological Studies for 15 years. He received his B.A. in mathematics from Princeton University and his M.S. in mathematics and Ph.D. in neuroscience from Stanford University. His research has

xii Editors and Contributors

focused on understanding the spatiotemporal patterns of electrical activity in the retina that convey visual information to the brain, and their origins in retinal circuitry, using large-scale multi-electrode recordings. His ongoing work now focuses on using basic science knowledge along with electrical stimulation to develop a novel high-fidelity artificial retina for treating incurable blindness. He is the recipient of an Alfred P. Sloan Research Fellowship, a McKnight Scholar Award, a McKnight Technological Innovation in Neuroscience Award, and a Research to Prevent Blindness Stein Innovation Award.

**Francesco Conti** is a postdoctoral researcher at the IIS Laboratory, ETH Zurich, Switzerland, and the EEES Laboratory, University of Bologna, Italy, where he received his Ph.D. in 2016. His research focuses on enabling sophisticated AI capabilities on ultra-low-power computers, working on the full pipeline "from algorithm to silicon" to achieve that goal. He has co-authored more than 40 papers in international conferences and journals, and he has been the recipient of three Best Paper Awards and the 2018 HiPEAC Tech Transfer Award.

Wim Dehaene was born in Nijmegen, The Netherlands, in 1967. He received the M. Sc. degree in electrical and mechanical engineering in 1991 from the Katholieke Universiteit Leuven. In November 1996, he received the Ph.D degree at the Katholieke Universiteit Leuven. In the beginning of his career, he joined Alcatel Microelectronics, Belgium. There he was a senior project leader for the feasibility, design, and development of mixed mode systems on chip. The application domains were telephony, xDSL, and high-speed wireless LAN. In July 2002, he joined the staff of the ESAT-MICAS laboratory of the Katholieke Universiteit Leuven where he is now a full professor and head of the MICAS division. His research domain is the circuit-level design of digital circuits. The current focus is on ultra-low-power signal processing and memories in advanced CMOS technologies. Part of this research is performed in cooperation with IMEC, Belgium, where he is also a part-time principal scientist. He is a senior member of the IEEE. He was the technical program chair for ESSCIRC 2017. He is a member of the ESSCIRC/ ESSDERC steering committee and the ESSCIRC technical program committee. He has also served for several years on the ISSCC program committee.

Albert Frisch studied quantum optics and atomic physics at the Institute of Experimental Physics at the University of Innsbruck where he graduated in 2014. His PhD thesis on Dipolar Quantum Gases of Erbium was awarded the thesis prize by the Institute of Quantum Optics and Quantum Information at the Austrian Academy of Sciences. In 2015, he worked at this institute as a postdoctoral research scientist before he joined IBM Research and Development in Böblingen, Germany. He started as a circuit design engineering professional working on IBM's high-performance processor series P and Z. He primarily focussed on array design and physical design verification. Further, he co-developed an automated build process for synthesized soft arrays. Since 2017, he was additionally engaged in the hardware and software development for IBM Q. He contributed on several layers of the system including the design of classical hardware components for the IBM Q

Editors and Contributors xiii

System One, the superconducting chip design, as well as the quantum software development kit Qiskit. He co-supervised an Extreme Blue internship out of which an efficient implementation of the well-known HHL quantum algorithm for solving linear systems of equations was developed and contributed to Qiskit. Today, he is working on ion trap quantum computers.

**Jacob Goeppert** was born in Lahr, Germany, in 1984. He received the Dipl.-Ing. (M.Sc.) degree in microsystems engineering from the University of Freiburg, Germany, in 2010. From 2010 to 2019, he was with the Fritz Huettinger Chair of Microelectronics, Department of Microsystems Engineering (IMTEK), University of Freiburg, Germany, where he worked in his Ph.D. degree. During this time, his research focus lay on of ultra-low-voltage, ultra-low-power digital circuits, and thermoelectrical energy-harvesting interfaces. Since 2019, he is with Hahn-Schickard, Villingen-Schwenningen, Germany, where he is working as a research engineer continuing his work on low-voltage digital circuits in addition to inference hardware for machine learning systems.

**Thorsten Hehn** received the Dipl.-Ing. degree in microsystems engineering from the University of Freiburg, Germany, in 2006 and the Dr.-Ing. degree in microsystems engineering from the University of Freiburg in 2014.

From December 2006 to September 2012, he was a research assistant with the Fritz Huettinger Chair of Microelectronics, Department of Microsystems Engineering (IMTEK), University of Freiburg. From December 2006 to December 2009, he was a fellow in the graduate school micro energy harvesting, funded by the German Research Foundation (DFG).

In October 2012, he joined Hahn-Schickard, Villingen-Schwenningen, Germany, as a research assistant in the group "Energy Autonomous Systems." As of February 2016, he is leading the group "Electronic Systems" which develops low-power embedded hardware and software for sensor systems. His research interests include low-power electronics, cyber-physical sensor systems, power management, energy harvesting, and stress measurement.

**Daniel Hoffmann** received his Dipl.-Ing. degree (M.Eng.) in mechanical engineering from the Technical University of Ilmenau, Germany, in 2002. From 2002 to 2006, he was a research scientist at the Tyndall National Institute in Cork, Ireland, and obtained his Ph.D. degree in microelectronics engineering from University College Cork, Ireland, in 2006.

In 2007, he joined the group "Energy Autonomous Systems" at Hahn-Schickard in Villingen-Schwenningen, Germany, where he worked in the field of kinetic energy harvesting systems as a postdoctoral research fellow.

From 2016 to 2020, he was the head of the group "Energy Autonomous Systems" at Hahn-Schickard. His main field of research was the design and optimization of kinetic energy harvesting devices with emphasis on frequency-tunable devices and rotational systems. He now joined the group "Inertial Sensor Systems" at Hahn-Schickard working on low-power and zero power microsystems.

xiv Editors and Contributors

**Makoto Ikeda** received the B.E., M.E. and Ph.D. degrees in electrical engineering from the University of Tokyo, Tokyo, Japan, in 1991, 1993 and 1996, respectively. He is a professor at the University of Tokyo. His research interests including hardware security, asynchronous circuits design, smart image sensor for 3D range finding and time-domain circuits for associate memories. He is a program vice-chair of International Solid-State Circuits Conference 2020 (ISSCC 2020). He was a technical program chair (2016–2017), a symposium chair and an executive committee member for the symposium on VLSI circuits, a technical program chair for Asian Solid-State Circuits Conference 2015 (A-SSCC 2015) and also a chair for IEEE SSCS Japan Chapter. He is an elected IEEE SSCS AdCom member for 2020–2022. He is a senior member of IEEE, IEICE Japan, and member of IPSJ and ACM.

**Shiro Kamohara** received the B. S. degree in physics from Keio University in 1986, M. E. degree from University of Tokyo Institute Technology in nuclear engineering in 1988 and Ph.D. from Tokyo metropolitan University in electrical and electronic engineering in 2008. He joined the Central Research Laboratory of Hitachi Ltd. in 1988. Since 1995, he was the member of Semiconductor & and Integrated Circuit Div. of Hitachi Ltd. He is a member of Renesas Technology Corp since 2003 and Renesas Electronics Corp since 2010. He is now the director of business unit for SOTB products. He was the visiting industrial fellow of the University of California at Berkeley in 1996.

**Alireza Kaviani** is a distinguished engineer at Xilinx Research Laboratories with a focus on the next-generation FPGA architectures and tools. He has more than 25 years of FPGA and ASIC industry experience in the areas of architecture, tools, IC design, and applications. He has authored more than 55 patents and publications in a number of areas, including clocking, asynchronous design, FPGA architecture, and CAD tools. He is a senior IEEE member and holds a Ph.D. degree from University of Toronto in electrical and computer engineering.

**Katsuyuki Kimura** received the M.S. in information and computer science from Keio University in 2002. His major is processor and LSI architecture. From 2002 to 2016, he worked on the hardware of media processors, multimedia CODECs and image recognition at Center for Research and Development, Toshiba Corporation. Since 2017, he has been working on the development of an automotive SoC at Electronic Devices and Storage Research and Development Center, Toshiba Electronic Devices and Storage Corporation.

**Dr. Binh Le** is an assistant professor of electrical engineering at San Jose State University and a researcher at Stanford University. His current research interests include non-volatile memory, carbon electronics, brain-inspired computing, brain-machine interface, and especially high-performance and energy-efficient analog/digital machine learning systems using emerging memory technologies. His recent publication on the topic was highlighted in the Nature Electronics journal, February 2019 issue. He received his B.S. degree in electrical engineering and computer sciences from the University of California, Berkeley, in 1994, his M.S and Ph.D. degrees in electrical engineering from Stanford University in 1999 and 2004,

Editors and Contributors xv

respectively. He has more than 20 years of experience working in the semiconductor industry where his last position was the director of Design Engineering at SanDisk Corporation. He is a senior member of the Institute of Electrical and Electronics Engineers (IEEE) and has authored or co-authored 59 US patents.

Zhichun Lei was born in Qian'an, China, in 1964. He received the B.S. degree in communication technology from Tianjin University, China, in 1986, the M.S. degree in communication and electronic system from Tianjin University in 1989 and the Ph.D. degree in electronic engineering and information technology from University of Dortmund, Germany, in 1998. From 1989 to 1993, he was a scientific assistant in Department of Electronic Engineering, Tianjin University, China. From 1994 to 1998, he was a scientific assistant at Chair for Communication Technology, Circuits and Systems Laboratory, University of Dortmund, Germany. From 1998 to 2001, he was a scientific assistant at Philips Research Laboratory, Aachen, Germany. From 2001 to 2011, he was an engineer at Sony European Technology Center in Stuttgart, Germany. Since 2011, he has been a professor at Institute of Measurement Engineering and Sensor Technology, University of Applied Sciences Ruhr West, Germany. Since 2014, he has held a second professorship at School of Microelectronics, Tianjin University, China. His research interests include high dynamic range and wide color gamut.

**Haitong Li** is a Ph.D. candidate in electrical engineering at Stanford University, supervised by Prof. H.-S. Philip Wong. He received M.S. in electrical engineering from Stanford University in 2017 and B.S. in microelectronics from Peking University, China, in 2015. His research theme is centered around energy-efficient machine learning hardware enabled by emerging nanotechnologies (e.g., 3D resistive memories), with over 30 publications and 800 citations to date. He received 2019 IEEE EDS Ph.D. Student Fellowship, 2016 IEEE EDS Masters Student Fellowship, Best Paper Award at 2016 SRC TechCon, and Best Paper nomination at 2016 Symposium of VLSI Technology.

**Yiannos Manoli** holds a B.A. degree (summa cum laude) in physics and mathematics, a M.S. degree in electrical engineering and computer science from the University of California, Berkeley, and the Dr.-Ing. degree in electrical engineering from the Gerhard Mercator University, Duisburg, Germany.

He was a research assistant at the University of Dortmund, Germany, before joining the Fraunhofer Institute of Microelectronic Circuits and Systems in Duisburg in 1985. There he established a design group for microsystem and microcontroller integrated circuits. In1996, he was appointed as a chair of microelectronics in the department of electrical engineering at the University of Saarland, Saarbrücken, Germany.

He joined the department of microsystems engineering (IMTEK) at the University of Freiburg, Germany, in 2001, where he holds the Fritz Huettinger Chair of Microelectronics. Since 2005, he additionally serves as a director of the Hahn-Schickard Institute in Villingen-Schwenningen, Germany.

xvi Editors and Contributors

He received Best Paper Awards from ESSCIRC 1988, 2009, and 2012, MWSCAS 2007, MSE 2007, and PowerMEMS 2006. For his creative and effective contributions to the teaching of microelectronics and the design of a web-based visualization of circuit functionality (Spicy VOLTsim, <a href="https://www.imtek.de/svs">www.imtek.de/svs</a>), he received various awards including the Excellence in Teaching Award of the University of Freiburg and the Teaching Award of the State of Baden-Württemberg, both in 2010.

Subhasish Mitra is a professor of electrical engineering and of computer science at Stanford University, where he co-leads the computation focus area of the Stanford SystemX Alliance and is a faculty member of the Wu Tsai Neurosciences Institute. He also holds the Carnot Chair of Excellence in NanoSystems at CEA-LETI in Grenoble, France. His research ranges across robust computing, NanoSystems, electronic design automation (EDA), and neurosciences. Results from his research group have been widely deployed by industry and have inspired significant development efforts by government and research organizations in multiple countries. Jointly with his students and collaborators, he demonstrated the first carbon nanotube computer and the first three-dimensional NanoSystem with computation immersed in data storage. These demonstrations received widespread recognitions: cover of NATURE, Research Highlight to the U.S. Congress by the NSF, and highlights by news organizations worldwide. In the field of robust computing, he and his students created key approaches for soft error resilience, circuit failure prediction, CASP on-line self-test and diagnostics, and QED design verification and system validation. His X-Compact test compression has proven essential to cost-effective manufacturing and high-quality testing of almost all electronic systems. X-Compact and its derivatives have been implemented in widely used commercial EDA tools. His honors include the ACM SIGDA / IEEE CEDA Newton Technical Impact Award in EDA (a test of time honor), the Semiconductor Research Corporation's Technical Excellence Award (for innovation that significantly enhances the semiconductor industry), the Intel Achievement Award (Intel's highest corporate honor), and the Presidential Early Career Award for Scientists and Engineers from the White House. He and his students have published many award-winning papers at major venues. He is a fellow of the ACM and the IEEE.

**Dante Gabriel Muratore** is an assistant professor of Microelectronics at the Delft University of Technology. He received the B.S. degree and the M.S. degree in electrical engineering from Politecnico of Turin in 2012 and 2013, respectively. He received the Ph.D. degree in microelectronics from University of Pavia in 2017. From 2015 to 2016, he was a visiting scholar at MTL laboratories at the Massachusetts Institute of Technology. From 2016 to 2020, he was a postdoctoral fellow at Stanford University. He is the recipient of the Wu Tsai Neurosciences Institute Interdisciplinary Scholar Award. His research focuses on hardware design for brain—machine interfaces, bioelectronics, sensor interfaces, and machine learning.

Editors and Contributors xvii

Clara Nieto Taladriz Moreno was born in Madrid, Spain, in 1994. She received the B.S. with honors in Ingeniería de Tecnologías y Servicios de Telecomunicación from the Univeridad Politécnica de Madrid (UPM), Spain, in 2016. She got her M.S. degree with honors in telecommunication engineering from the UPM in 2018, after completing the second year in the University of KU Leuven (KUL), Belgium. Since 2018, she has been a research assistant at the MICAS division of the department of electrical engineering (ESAT) at the KU Leuven. She has been working on the design of ultra-low-voltage energy-efficient digital circuits under the supervision of Prof. Wim Dehaene.

**Kunle Olukotun** is the Cadence Design Systems professor of electrical engineering and computer science at Stanford University. Olukotun is well known as a pioneer in multicore processor design and the leader of the Stanford Hydra chip multiprocessor (CMP) research project and the founder of Afara Websystems, which designed the Niagara processors. Olukotun currently directs the Stanford Pervasive Parallelism Laboratory (PPL), which seeks to proliferate the use of heterogeneous parallelism in all application areas using domain-specific languages (DSLs). Olukotun is an ACM fellow and IEEE fellow.

Zvi Or-Bach is the founder and CEO of MonolithIC 3D<sup>TM</sup> Inc. He is a world recognized expert in monolithic 3D technologies, past chairman of the 3D of IEEE S3S Conference, and is active as an invited speaker and tutorial instructor in the USA, Korea, and Japan. He is currently the chairman of the Board for Zeno Semiconductors and VisuMenu. Prior to founding and running MonolithIC 3D since 2009, he founded eASIC in 1999 and served as its CEO for six years. eASIC was funded by leading investors, such as Vinod Khosla and KPCB, in three successive rounds. Intel acquired eASIC in 2018. Under his leadership, eASIC won the prestigious EETimes' 2005 ACE Award for Ultimate Product of the year in the Logic and Programmable Logic category and the Innovator of the Year Award and was selected by EE Times to be part of the "Disruptors—The people, products and technologies that are changing the way we live, work and play." Earlier, he founded Chip Express in 1989 and served as the company's president and CEO for 10 years, bringing the company to \$40M revenue. Chip Express was acquired by GigOptix which was later acquired by IDT. He received his B.Sc. degree (1975) cum laude in electrical engineering from the Technion-Israel Institute of Technology, and M.Sc. (1979) with distinction in computer science, from the Weizmann Institute, Israel. He holds over 251 issued patents.

**Rebecca Park** received her B.S. from Cornell University and is currently a Ph.D. candidate in electrical engineering at Stanford University, under the supervision of Professor H.-S. Philip Wong and co-advised by Professor Subhasish Mitra. Her current research interest is in the development of high-performance and energy-efficient nanoelectronics, in which she has focused on carbon nanotube-based FETs. She is a recipient of the Intel/SRCEA Masters Scholarship (2014–2016), the Intel/SRCEA Ph.D. Fellowship (2016–2019), and a finalist to participate in the Rising Stars Women in Engineering Workshop (2018). She has interned at IBM

xviii Editors and Contributors

(summer 2017) working on carbon nanotube transistors and at Apple (summer 2018) as a flat panel display engineer.

**Raghu Prabhakar** is a senior principal engineer and one of the founding engineers at SambaNova Systems. His research interests include designing high-level programming models, compiler optimizations, and novel architectures with a focus on reconfigurable hardware. He holds a Ph.D. in computer science from Stanford University, where he was advised by Prof. Kunle Olukotun and Prof. Christos Kozyrakis. He earned a M.S. in computer science from UCLA. He is a member of IEEE and ACM.

**Robert M. Radway** is a Ph.D. student in electrical engineering at Stanford University. His research focuses on performance benefits, design, and thermal considerations for monolithic 3D systems (through the DARPA 3DSoC Program). He has worked on emerging non-volatile memories such as resistive RAM, aiming to increasing effective density (multiple bits-per-cell, 1T4R designs) and improving resilience through development of endurance management techniques. He completed his bachelor's and master's at the Massachusetts Institute of Technology in EECS. For his Master's thesis, he developed designs and processes for thermally efficient GaN HEMTs fabricated via wafer bonding.

**Dennis Rich** is currently pursuing a Ph.D. at Stanford University, advised by Prof. Subhasish Mitra. He received his dual B.S. in electrical engineering and engineering physics from the University of Illinois at Urbana-Champaign, investigating thin-film device fabrication advised by Prof. Can Bayram. His current research interests include addressing system-level design and fabrication challenges of emerging nanotechnologies and nanosystems. Previously, he worked at Northwestern University investigating carbon nanotube fabrication and at Silicon Laboratories. He is a recipient of the Goldwater Scholarship, the Bardeen Undergraduate Award, and the Robert C. MacClinchie Scholarship.

**Peter Hans Roth** received his Dipl.-Ing. degree in electrical engineering and his Dr.-Ing. degree from the Stuttgart University in 1979 and 1985, respectively. In 1985, he joined the IBM Germany Research and Development Laboratory, starting in the department of VLSI logic chip development. Since 1987, he has been leading the VLSI test and characterization team of the Boeblingen Laboratory. Later on, he was leading several development projects in the area of IBM's mainframe and power microprocessors. He also was heavily involved in the development of gaming products like the cell processor for the Sony Playstation. He owned also the hardware strategy for the IBM Germany Research and Development Laboratory. In early 2017, he formed a quantum computing team in the IBM Boeblingen Laboratory, and today he is still involved on several quantum engagements.

Editors and Contributors xix

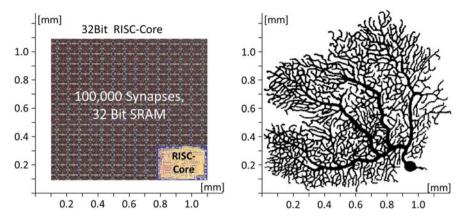

Ulrich Rueckert received the diploma degree (M.Sc.) with honor in computer science and the Dr.Ing. degree (Ph.D.) with honors in electrical engineering from the University of Dortmund, Germany, in 1984 and in 1989, respectively. He joined the Department of Electronic Components, University of Dortmund, in 1985, where he developed the first VLSI implementation of artificial neural networks in Europe. In February 1990, he accepted the position as a senior researcher at the Department of Electronic Components, University of Dortmund. From 1993 to 1995, he was an associate professor of microelectronics technology of the University of Hamburg-Harburg. From 1995 until 2009, he was a full professor of electrical engineering at the University of Paderborn. As a member of the Heinrich-Nixdorf Institute, he held the Chair "System and Circuit Technology". Since 2009, he has been at the Cognitive Interaction Technology Center of Excellence at the University of Bielefeld, heading the Research Group Cognitronics and Sensor Systems. Since 2001, he has been adjunct professor of the Faculty of Information Technology at the University of Technology, Brisbane, Australia. In 2006, he received the first Innovation Award of North-Rhine Westfalia (together with his colleague Prof. Noé). His main research interests are bio-inspired architectures for neural information processing and cognitive robotics. He has held many international positions, including the committee for the European Brain project.

**Dr. Manuele Rusci** is currently a postdoctoral researcher at the Energy-Efficient Embedded Systems Laboratory, University of Bologna, Italy. He received the Ph.D. degree in electronics from the same university in 2018. His main research interests include low-power embedded systems and AI-powered smart sensors, working at the intersection between machine learning and HW-SW system co-design.

**Mohamed M. Sabry Aly** is an assistant professor at Nanyang Technological University, Singapore. He received his Ph.D. degree in electrical and computer engineering from École Polytechnique Fédérale de Lausanne (EPFL), in 2013. He was a postdoctoral research fellow at Stanford University from 2014 to 2017. His current research interests include system-level design and optimization of computing systems enabled by emerging technologies. He is an active close collaborator with Stanford University and a founding member of the N3XT project at Stanford University. He was the recipient of the Swiss National Science Foundation Early Postdoctoral Mobility Fellowship in 2013.

**Daniel A. Sanchez** was born in Tepic, Mexico. He received his B.Sc. degree in electronic engineering from the Western Institute of Science and Technology (ITESO), Guadalajara, Mexico, in 2006, and the M.Sc. in microsystems engineering from the University of Freiburg, Germany, in 2012.

From 2006 to 2009, he worked in the Research and Development Center at Continental Automotive, Guadalajara, Mexico, designing instrument clusters for passenger cars. Between 2010 and 2011, he was with Corporate Technology, Siemens AG, Munich, Germany, working on piezoelectric harvesters. Between 2012 and 2017, he was with the Fritz Huettinger Chair of Microelectronics, University of Freiburg, Germany, working toward his Ph.D. degree, where he

xx Editors and Contributors

researched about efficient interface circuits for energy harvesting devices with special focus on integrated circuit design. Since 2017, he is with Hahn-Schickard in Freiburg, Germany, where he leads the microelectronics group.

He received second place in the statewide basic sciences challenge, Nayarit, Mexico, in 2002. In 2009, he was awarded with a DAAD-CONACYT scholarship and in 2016 with a Fritz Huettinger fellowship.

Fabio Sebastiano received the B.Sc. (cum laude) and M.Sc. (cum laude) degrees in electrical engineering from the University of Pisa, Italy, in 2003 and 2005, respectively, the M.Sc. degree (cum laude) from Sant'Anna school of Advanced Studies, Pisa, Italy, in 2006, and the Ph.D. degree from Delft University of Technology, The Netherlands, in 2011. From 2006 to 2013, he was with NXP Semiconductors Research in Eindhoven, The Netherlands, where he conducted research on fully integrated CMOS frequency references, deep-submicron temperature sensors, and area-efficient interfaces for magnetic sensors. In 2013, he joined Delft University of Technology, where he is currently an assistant professor. He has authored or co-authored one book, 11 patents, and over 60 technical publications. His main research interests are cryogenic electronics for quantum computing, quantum computing, sensor read-outs, and fully integrated frequency references. He has been a member of the "Emerging technologies" subcommittee of the technical program committee of the RFIC symposium. He was a co-recipient of the best student paper at ISCAS in 2008, the Best Paper Award at IWASI in 2017, and the Best IP Award at DATE in 2018. He is a distinguished lecturer of the Solid-State Circuit Society.

**Daniel Schillinger** was born in Freiburg im Breisgau, Germany, in 1985. At the Albert Ludwig University, Department of Microsystems Engineering–IMTEK, Freiburg im Breisgau, Germany, he received the bachelor's degree in microsystems engineering in 2009 as well as the master's degree in 2012. After that he became a Ph.D. candidate in the Fritz Huettinger Chair of Microelectronics.

Since 2017, he is additionally a part of the electronics systems design group, Hahn-Schickard, Villingen-Schwenningen, Germany, where he is working in the field of energy harvesting and RFID.

His current research interests are in efficient power processing circuits for vibration-based energy harvesters, where he is focusing on integrated circuit design as well as implementations with discrete components, and the power management for wireless and self-sustaining autonomous sensor systems. Currently, he is also involved in the development of long-lasting highly efficient LED drivers for lighting applications as well as in the development of a telemetric interface for a strain measurement chip in industrial applications.

He was a recipient of the German Research Foundation scholarship GRK 1322: Micro Energy Harvesting, in 2013.

Markus Strobel received his degree in electrical engineering (Dipl.-Ing.) from the University Stuttgart, Germany, and heads the Department Vision Sensors at the Institute for Microelectronics Stuttgart (IMS CHIPS). He has been with IMS CHIPS

Editors and Contributors xxi

since 1997 and focusses on CMOS Imaging including the development of logarithmic high dynamic range CMOS (HDRC) image sensors, optical characterization, optical and electrical test environments as well as camera system integration for automotive, autonomous, industrial and custom-specific applications. Recent research topics cover high dynamic range imagers with linear characteristics as well as photonic or plasmonic nanostructures to build multispectral CMOS sensors.

Nobuyuki Sugii received the B.S., M.S. and Ph.D. degrees in applied chemistry from the University of Tokyo in 1986, 1988 and 1995, respectively. He joined the Central Research Laboratory, Hitachi, Ltd. in 1988. Since 1996, he has been working on the research and development of CMOS devices, including strained silicon and SOI. From 2010 to 2015, he served as a research group leader for the Low-Power Electronics Association and Project and developed ultralow-power thin-BOX FDSOI (named SOTB) process and design environment for ICs operating down to 0.4 V. From 2004 to 2015 and 2018–2020, he served as a visiting professor with the Tokyo Institute of Technology. He is currently with the Research and Development Group, Hitachi, Ltd., where he is researching on sensing devices and systems, and energy management systems fully utilizing renewables. He has been a technical committee member of the IEEE VLSI Technology (2012-2019), the International Symposium on Solid-State Devices and Materials (2014–2017) and the IEEE S3S Conference (2011-). He is a fellow of the Japan Society of Applied Physics.

**Roel Uytterhoeven** was born in Sint-Truiden, Belgium, in 1992. He received the M.S. degree in electrical engineering magna cum laude from KU Leuven, Belgium, in 2015. He is currently working as a research assistant with the ESAT-MICAS laboratories at KU Leuven. Here, he pursues a Ph.D. degree under the supervision of Prof. Dr. Ir. Wim Dehaene in the field of ultra-energy-efficient digital circuits through near/subthreshold supply voltage operation. For this research, he is being sponsored by the Research Foundation Flanders (FWO) with an SB-fellowship.

**Bob Vanhoof** was born in Leuven, Belgium, in 1994. In 2017, he received the M.Sc. degree in electrical engineering from the KU Leuven with a master's thesis about the implementation on FPGA of the IEEE802.11ad PHY. Currently, he is a research assistant at MICAS where he is working toward the Ph.D. degree. His research interest lies in the fields of ultra-low-energy design and SRAM design.

Marian Verhelst is an associate professor at the MICAS laboratories of the EE department of KU Leuven. Her research focuses on embedded machine learning, hardware accelerators, HW-algorithm co-design, and low-power edge processing. Before that, she received a Ph.D. from KU Leuven in 2008, was a visiting scholar at the BWRC of UC Berkeley in the summer of 2005, and worked as a research scientist at Intel Laboratories, Hillsboro, OR from 2008 to 2011. She is a member of the DATE and ISSCC executive committees, is TPC co-chair of AICAS2020 and tinyML2020, and TPC member DATE and ESSCIRC. She is an SSCS distinguished lecturer, was a member of the Young Academy of Belgium, an associate editor for TVLSI, TCAS-II, and JSSC, and a member of the STEM advisory

xxii Editors and Contributors

committee to the Flemish Government. She currently holds a prestigious ERC Starting Grant from the European Union and was the laureate of the Royal Academy of Belgium in 2016.

Andrei Vladimirescu received the M.S. and Ph.D. degrees in EECS from the University of California, Berkeley, where he was a key contributor to the SPICE simulator, releasing the SPICE2G6 production-level SW in 1981. He pioneered electrical simulation on parallel computers with the CLASSIE simulator as part of his Ph.D. He is the author of "The SPICE Book" published by J. Wiley and Sons. For many years, he was R&D director leading the design and implementation of innovative software and hardware electronic design automation (EDA) products for Analog Devices Inc., Daisy Systems, Analog Design Tools, Valid Logic, and Cadence Design Systems. Currently, he is a professor involved in research at the University of California at Berkeley, Delft University of Technology, and the Institut Superieur d'Electronique de Paris, ISEP, as well as a consultant to industry. His research activities are in the areas of design, simulation, and modeling of CMOS circuits, new devices, and circuits for quantum computing. He is an IEEE life fellow.

Gordon Wetzstein is an assistant professor of electrical engineering and, by courtesy, of computer science at Stanford University. He is the leader of the Stanford Computational Imaging Laboratory and a faculty co-director of the Stanford Center for Image Systems Engineering. At the intersection of computer graphics, machine vision, optics, scientific computing, and applied vision science, his research has a wide range of applications in next-generation imaging, display, wearable computing, and microscopy systems. Prior to joining Stanford in 2014, he was a research scientist in the Camera Culture Group at MIT. He received a Ph.D. in computer science from the University of British Columbia in 2011 and graduated with honors from the Bauhaus in Weimar, Germany, before that. He is the recipient of an NSF CAREER Award, an Alfred P. Sloan Fellowship, an ACM SIGGRAPH Significant New Researcher Award, a Presidential Early Career Award for Scientists and Engineers (PECASE), an SPIE Early Career Achievement Award, a Terman Fellowship, an Okawa Research Grant, the Electronic Imaging Scientist of the Year 2017 Award, an Alain Fournier Ph.D. Dissertation Award, and a Laval Virtual Award as well as Best Paper and Demo Awards at ICCP 2011, 2014, and 2016 and at ICIP 2016.

**H.-S. Philip Wong** is the Willard R. and Inez Kerr Bell Professor in the School of Engineering. He joined Stanford University as a professor of electrical engineering in September 2004. From 1988 to 2004, he was with the IBM T.J. Watson Research Center. At IBM, he held various positions from research staff member to manager and senior manager. While he was a senior manager, he had the responsibility of shaping and executing IBM's strategy on nanoscale science and technology as well as exploratory silicon devices and semiconductor technologies. His research aims at translating discoveries in science into practical technologies. His works have contributed to advancements in nanoscale science and technology, semiconductor

Editors and Contributors xxiii

technology, solid-state devices, and electronic imaging. His present research covers a broad range of topics including carbon electronics, 2D-layered materials, wireless implantable biosensors, directed self-assembly, device modeling, brain-inspired computing, non-volatile memory, and monolithic 3D integration. He is a fellow of the IEEE. He served as the editor-in-chief of the IEEE Transactions on Nanotechnology (2005–2006), subcommittee chair of the ISSCC (2003–2004), general chair of the IEDM (2007), and is currently the chair of the IEEE Executive Committee of the Symposia of VLSI Technology and Circuits. He is the faculty director of the Stanford Non-Volatile Memory Technology Research Initiative (NMTRI) and is the founding faculty co-director of the Stanford SystemX Alliance—an industrial affiliate program focused on building systems.

Yutaka Yamada received the B.E. and M.E. degrees from Keio University, Yokohama, Japan, in 2003 and 2005, respectively. He joined Toshiba Corporation, Kawasaki, Japan, in 2005. He was involved in the research and development of reconfigurable processors and image processing accelerators. Since 2017, He is currently working as a research engineer in the Research and Development Center, Toshiba Electronic Devices and Storage Corporation, Kawasaki, Japan. His current research interests include the area of image recognition accelerators, image signal processors and system architecture for automotive SoCs. He is a member of IEEE and IEICE.

Ms. Xin Yu was born in Zhangjiakou, China, in 1995. She has received the B.S. degree in communication engineering from Hebei University of Technology, Tianjin, China, in 2017 and received the M.S. degree in information and communication engineering from Tianjin University, Tianjin, China, in 2020. From 2017 to 2020, she was a postgraduate at School of Microelectronics, Tianjin University, China. Her research interests include image and video acquisition and reproduction, image and video codec. As of March 2020, she will work as a software engineer at Huawei Technologies Co., Ltd.

Yaqi Zhang is a Ph.D. candidate in the electrical engineering department at Stanford University. She received a B.S. in electrical engineering from Duke University. Her research has been focusing on the architectural design of and compilation to reconfigurable hardware accelerators. Specifically, she has worked on an on-chip network design that improves the scalability of the accelerator. She also worked on compilation techniques that enhance programming abstraction and enhances the utilization and composability of reconfigurable architectures.

# Chapter 1 The New Era of Nano-chips: Green and Intelligent

1

**Boris Murmann and Bernd Hoefflinger**

Since their invention in 1959 by Robert Noyce, silicon integrated circuits have followed a unique history of steep exponential progress. Moore's Law, which was articulated by Noyce's friend and partner Gordon Moore in 1964, drove the semiconductor industry into a widely agreed upon roadmap of doubling the number of transistors per chip every 18 months. Guided by the "International Technology Roadmap for Semiconductors (ITRS)," this strategy worked well until about 2010, and was driven by mass-produced memory chips and von-Neumann computing architectures ranging from microcontrollers to microcomputers and supercomputers. The dynamics that shaped this epoque and how it changed from bipolar to CMOS technology leadership was described in the 2012 edition of "CHIPS 2020—A Guide to the Future of Nanoelectronics" [1]. Here, it was also predicted that the ITRS would end in 2016 (at 10 nm) and that future progress would be driven by

- The need for entirely new levels of energy efficiency,

- Ultra- low voltage Fully Depleted Silicon-on-Insulator (SOI) CMOS,

- 3D Integration,

- Intelligent, neuromorphic architectures,

- Human-Visual-System (HVS)-inspired video.

Shortly after the ITRS program ended in 2015, "CHIPS 2020, Vol. 2—New Vistas in Nanoelectronics" was published [2] and delivered a broad range of contributions focusing on the above-listed topics. Since then, the continuing global wave

B. Murmann  $(\boxtimes)$

Stanford University, Stanford, CA, USA

e-mail: murmann@stanford.edu

B. Hoefflinger

Sindelfingen, Germany

e-mail: bhoefflinger@t-online.de

toward innovative, sustainable, energy-efficient and intelligent nano-chip systems has inspired us to compile this book on a vision for 2030 and beyond. As shown in Table 1.1, we identified five major thrust areas that are covered by 28 chapter contributions from world-leading experts. Different from previous versions of this book, a larger fraction of the presented material is application focused, aiming to highlight the challenges that new applications will define for the semiconductor industry (see e.g., Chap. 25, "Augmented and Virtual Reality"). For the remainder of this introduction, we briefly discuss the positioning and interplay of these contributions within each thrust.

#### 1.1 Robust and Energy-Efficient Silicon

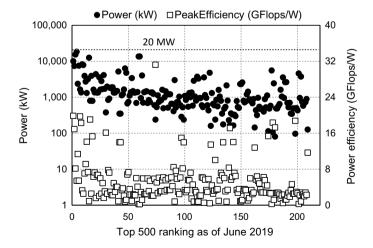

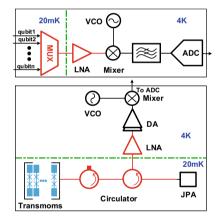

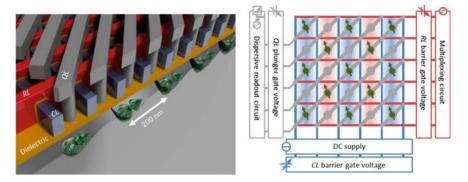

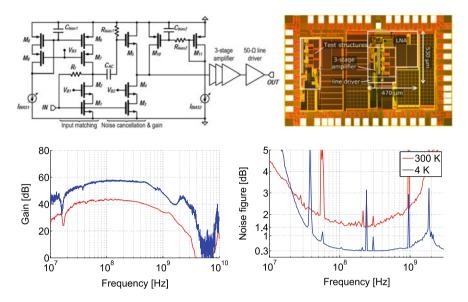

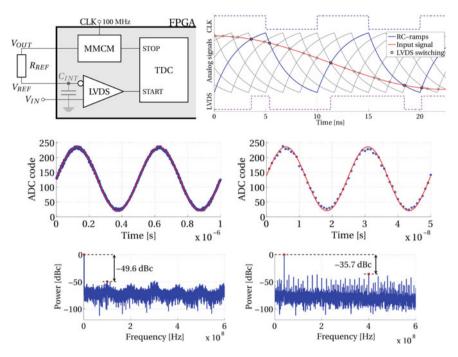

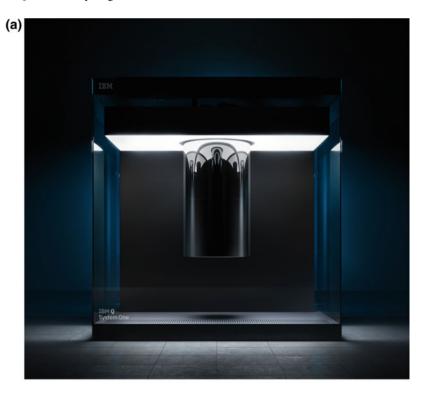

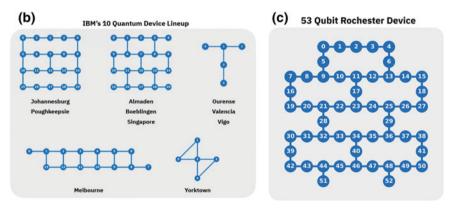

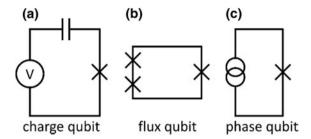

The International Technology Roadmap for Semiconductors (ITRS) had been critically evaluated in 2012 in CHIPS 2020 [1] and in 2014 in CHIPS 2020 Vol. 2 [2], leading to the prediction that it would end in 2016 at the 10 nm node. And indeed, the ITRS program ended in 2015 with a forecast limit of 10 nm, and the birth of the "International Roadmap for Devices and Systems" (IRDS) [3]. The IRDS inherited rich know-how and data from the ITRS and is now being continuously updated under the umbrella of the IEEE. Important focus areas of the IRDS are highlighted in Chap. 2, including the unique and sustained importance of silicon, as well as the need for more 3D Integration. These topics were already at the core of [1, 2] and continue to be the main technology underpinning for this book. The ITRS ended mainly because of diminishing gains in speed and in energy efficiency of von-Neumann computer architectures. This perceived wall increased the interest in "Rebooting Computing," a program that is reviewed in Chap. 2. Rebooting Computing started in 2012 and focuses on long-term research such as quantum computing, which gets special attention in Chaps. 26 and 27. In addition, Chap. 16 provides an update on trends in more conventional supercomputing platforms.

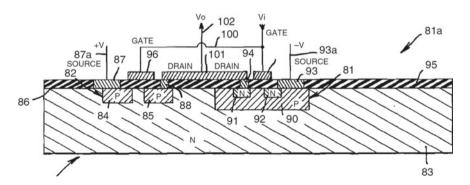

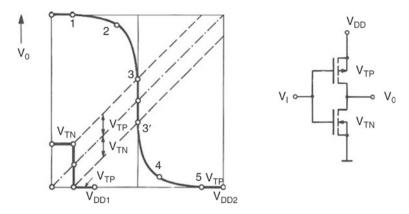

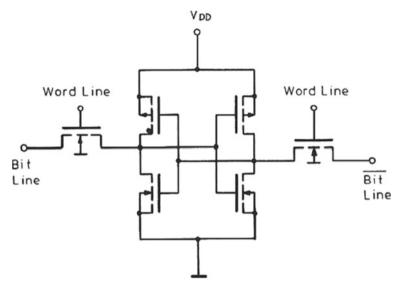

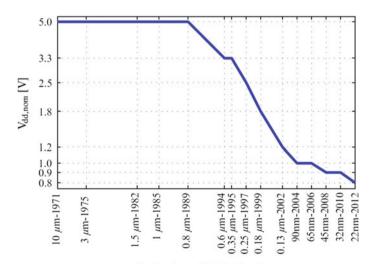

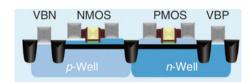

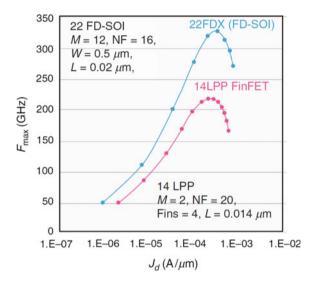

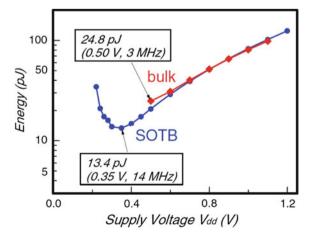

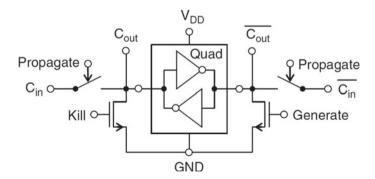

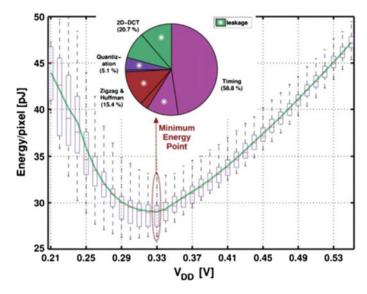

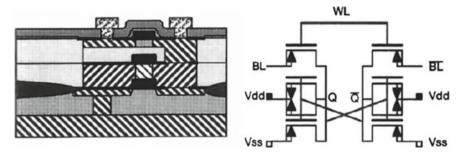

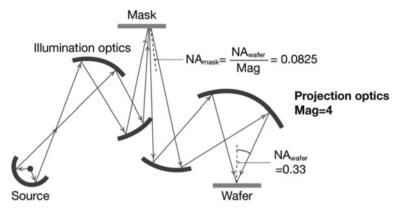

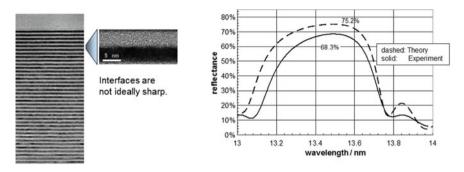

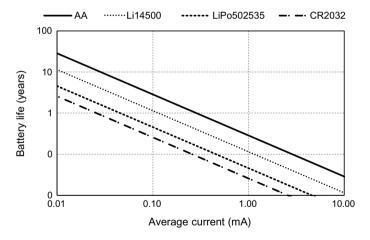

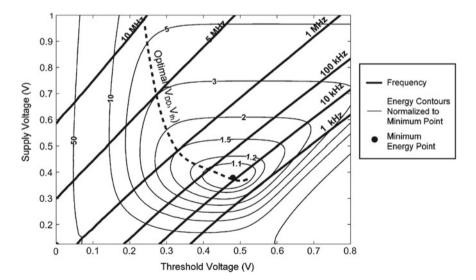

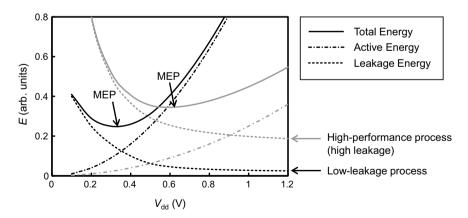

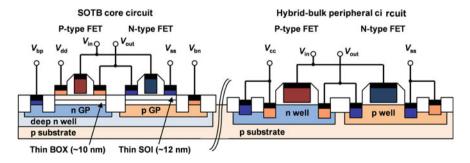

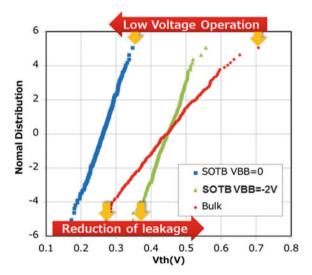

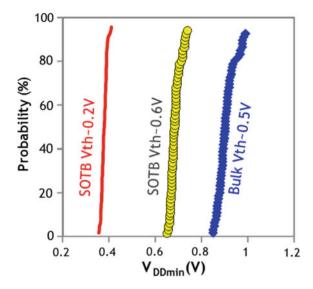

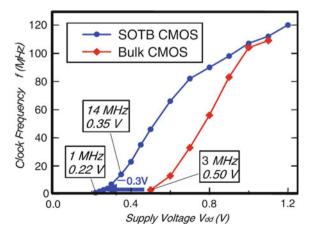

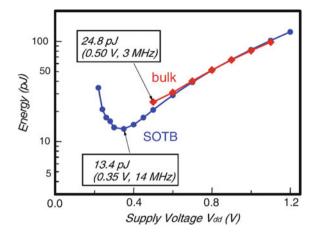

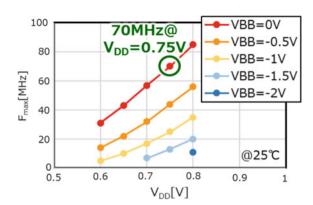

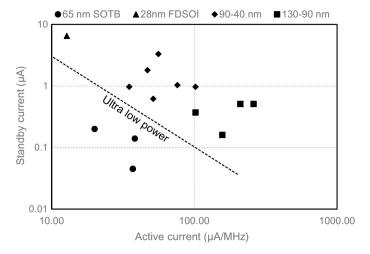

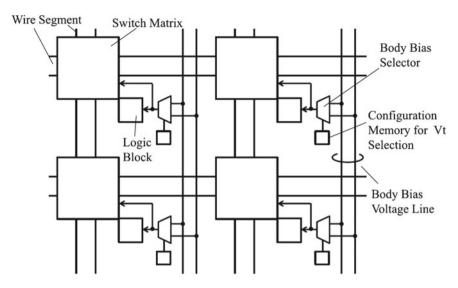

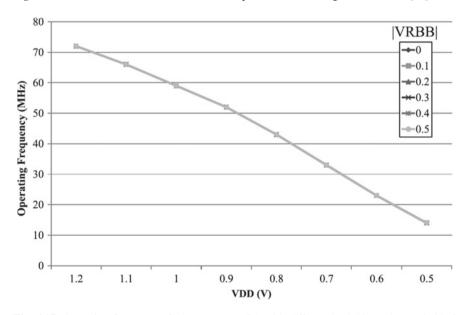

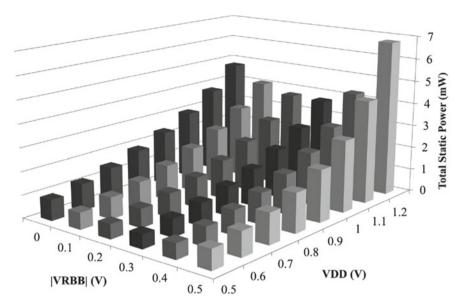

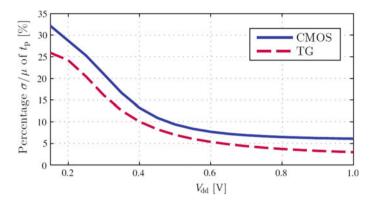

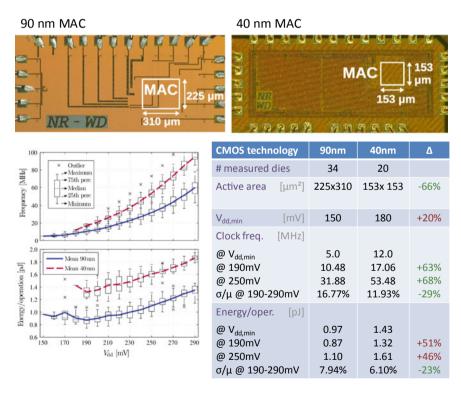

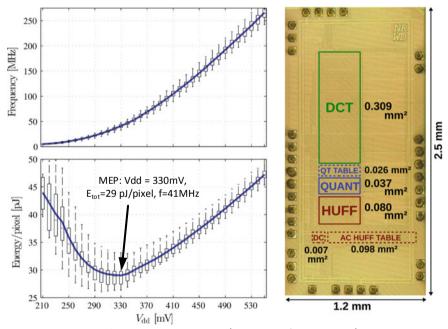

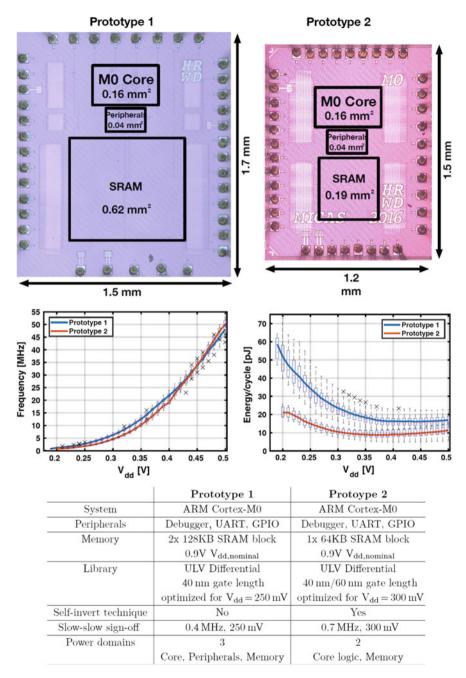

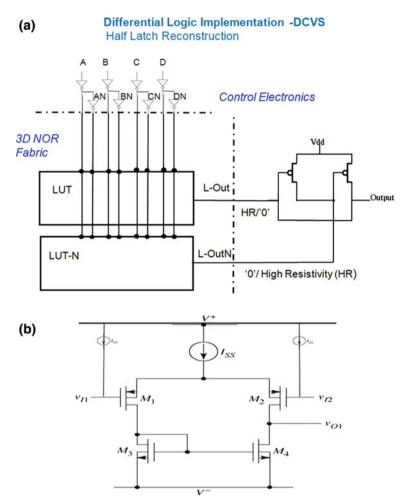

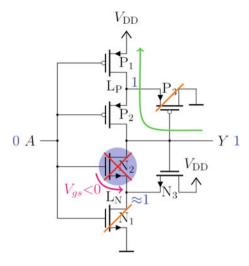

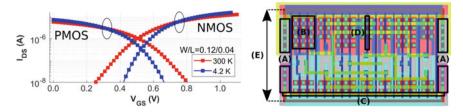

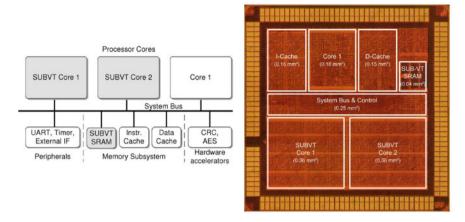

The IEEE conference S3S ("Silicon-on Insulator, 3D Integration and Sub-Threshold MOS") also gets a special mention in Chap. 2, because it reflects the technology base of [1, 2], which is substantially expanded in the present book, particularly in Chaps. 4, 6–11, 13–15, 19, 20, and 23. The unique and fundamental importance of the Silico/Silicon-Dioxide system is emphasized again in Chap. 4 for its lasting significance over the coming decades. Its optimum incorporation for processing functions in complementary MOS (CMOS) is highlighted in Chap. 4. Its optimum downscaling for process complexity, stability, speed, voltage and energy is presented in Chap. 6 for the most advanced realization of fully depleted CMOS Silicon-on-Insulator (SOI). Such low-power technologies are propelling a variety of applications, such as energy-autonomous microcontrollers for the IoT (Internet of Things). A critical aspect here is robustness, as the underlying circuits are typically operated in subthreshold and at very low supply voltages. Chapter 7 takes a look at this problem in the context of robust and energy-optimal design using differential-transmission-gate logic. Finally, manufacturing at the advanced nodes continues to

Table 1.1 Overview of chapter contributions

| Cha | pter                                                                                                  | Robust<br>and<br>Efficient<br>Silicon | Real-World<br>Electronics | Neuromorphic<br>Architectures | AI<br>On-Chip<br>and 3D<br>Integration | Man-Machine<br>Cooperation |

|-----|-------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------|-------------------------------|----------------------------------------|----------------------------|

| 2   | IRDS—International<br>Roadmap for Devices<br>and Systems, Rebooting<br>Computing, S3S                 | <b>✓</b>                              |                           | <b>V</b>                      | <b>✓</b>                               |                            |

| 3   | Real-World Electronics                                                                                | 1                                     | 1                         | 1                             | 1                                      | 1                          |

| 4   | Silicon Complementary<br>MOS in its 7th Decade                                                        | <b>✓</b>                              | 1                         |                               | 1                                      |                            |

| 5   | Nanolithography                                                                                       | 1                                     |                           |                               |                                        |                            |

| 6   | The Future of<br>Ultra-Low-Power SOTB<br>CMOS                                                         | 1                                     | 1                         |                               |                                        |                            |

| 7   | Dealing with the Energy<br>versus Performance<br>Tradeoff in Future<br>CMOS Digital Circuit<br>Design | <b>V</b>                              | 1                         |                               | <b>V</b>                               |                            |

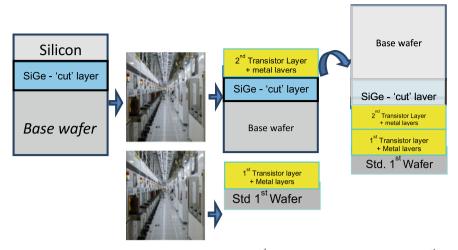

| 8   | Monolithic 3D<br>Integration—An Update                                                                | <b>✓</b>                              |                           |                               | <b>✓</b>                               |                            |

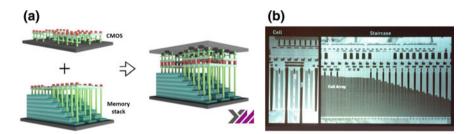

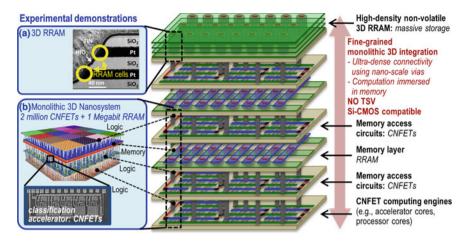

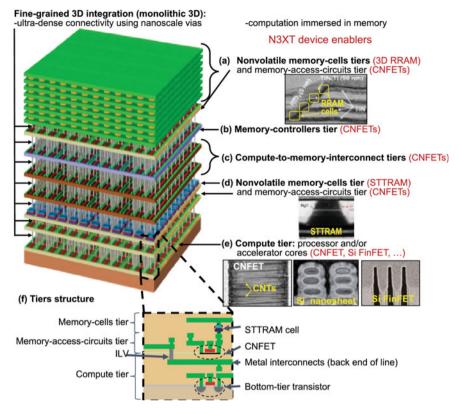

| 9   | Heterogeneous<br>Monolithic 3D<br>Nano-Systems: The<br>N3XT Approach                                  | ✓                                     |                           |                               | <b>✓</b>                               |                            |

| 10  | High-Speed 3D<br>Memories Enabling AI<br>Future                                                       | 1                                     |                           |                               | 1                                      |                            |

| 11  | 3D for Efficient FPGA                                                                                 | ✓                                     | 1                         |                               |                                        |                            |

| 12  | Digital Neural Networks                                                                               | ✓                                     | 1                         | 1                             | ✓                                      | ✓                          |

| 13  | Enabling Domain-specific Architectures with Programmable Devices                                      | <b>✓</b>                              |                           |                               | <b>✓</b>                               |                            |

| 14  | Coarse-Grained<br>Reconfigurable<br>Architectures                                                     | 1                                     |                           |                               | 1                                      |                            |

| 15  | A 1000x Improvement of<br>the Processor-Memory<br>Gap                                                 | 1                                     | 1                         |                               | 1                                      |                            |

| 16  | High-Performance<br>Computing Trends                                                                  | 1                                     |                           | 1                             | 1                                      |                            |

| 17  | Analog-to-Information<br>Conversion                                                                   | 1                                     | 1                         |                               | 1                                      |                            |

| 18  | Machine Learning at the Edge                                                                          | 1                                     | 1                         |                               | 1                                      | 1                          |

(continued)

Table 1.1 (continued)

| Chapter |                                                                                 | Robust<br>and<br>Efficient<br>Silicon | Real-World<br>Electronics | Neuromorphic<br>Architectures | AI<br>On-Chip<br>and 3D<br>Integration | Man-Machine<br>Cooperation |

|---------|---------------------------------------------------------------------------------|---------------------------------------|---------------------------|-------------------------------|----------------------------------------|----------------------------|

| 19      | The Memory Challenge<br>in Ultra-Low Power<br>Deep Learning                     | 1                                     | 1                         |                               | 1                                      | <b>✓</b>                   |

| 20      | Multi-Sensor, Intelligent<br>Microsystems                                       | <b>✓</b>                              | 1                         |                               |                                        | 1                          |

| 21      | High-Dynamic-Range<br>and Wide-Color-Gamut<br>Video                             | 1                                     | 1                         |                               | 1                                      | <b>✓</b>                   |

| 22      | Update on<br>Brain-Inspired Systems                                             | <b>✓</b>                              | 1                         | 1                             |                                        | <b>✓</b>                   |

| 23      | Energy-Autonomous<br>Chip-Systems                                               | ✓                                     | <b>✓</b>                  |                               |                                        | <b>✓</b>                   |

| 24      | Artificial Retina: A Future Cellular-Resolution Brain-Machine Interface         | ✓                                     | <b>✓</b>                  |                               |                                        | <b>V</b>                   |

| 25      | Augmented and Virtual<br>Reality                                                |                                       | 1                         |                               | 1                                      | 1                          |

| 26      | Cryogenic-CMOS for<br>Quantum Computing                                         | <b>✓</b>                              |                           |                               | <b>✓</b>                               |                            |

| 27      | Quantum Computing—Large-scale Quantum Systems based on Superconducting Qubits   | 1                                     |                           |                               | <b>V</b>                               |                            |

| 28      | Man-Machine<br>Cooperation and<br>Cognitronics                                  | 1                                     | 1                         | ✓                             | 1                                      | <b>✓</b>                   |

| 29      | Efficient<br>System-on-Chip (SOC)<br>for Autonomous Driving<br>with High Safety | <b>✓</b>                              | <b>✓</b>                  | <b>✓</b>                      | ✓                                      | <b>/</b>                   |

be challenging. The most expensive part, nanolithography, is handled by one of the Focus Teams in the IRDS structure, and it is reviewed in Chap. 5.

The CMOS technology base described in Chaps. 4, 6 and 7 is essential and virtually un-contested for providing continuous future growth, if combined with sustained efforts in 3D integration for sensing, memory and actuating, all aimed at realizing intelligent, energy-efficient architectures for real-world electronics.

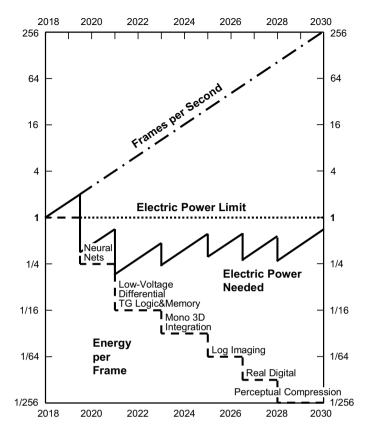

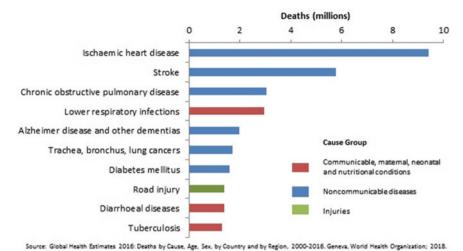

#### 1.2 Real-World Electronics

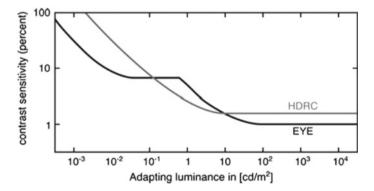

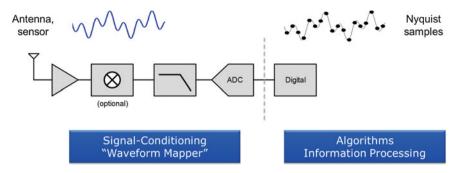

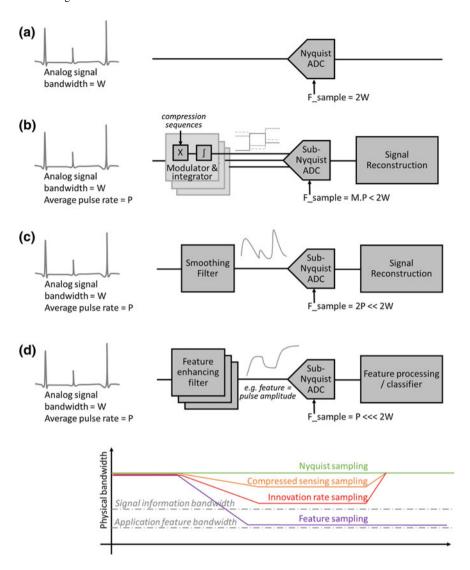

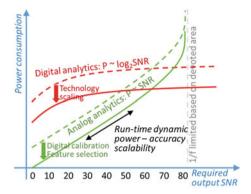

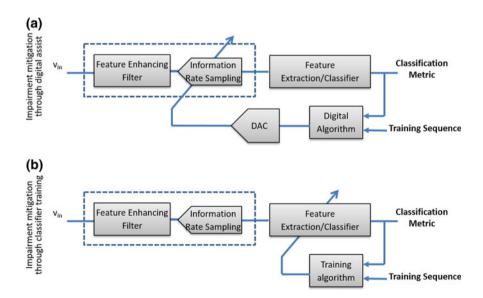

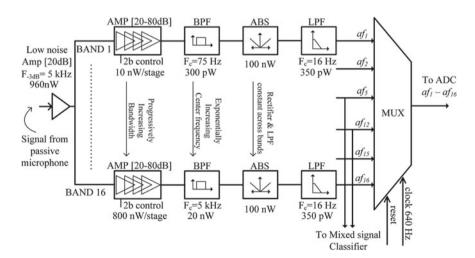

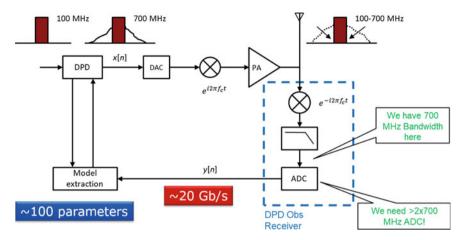

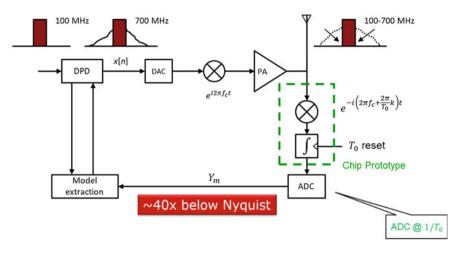

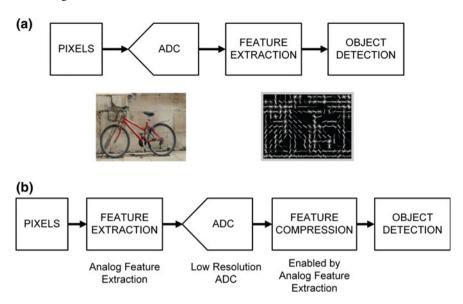

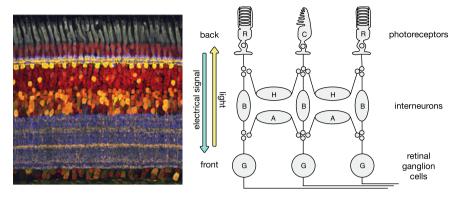

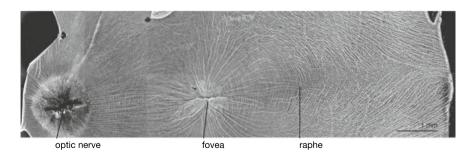

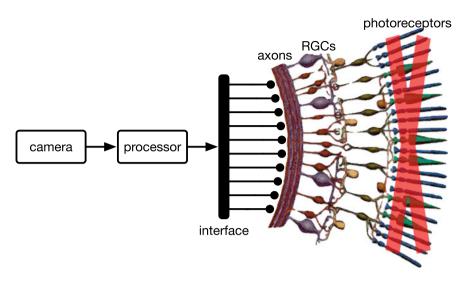

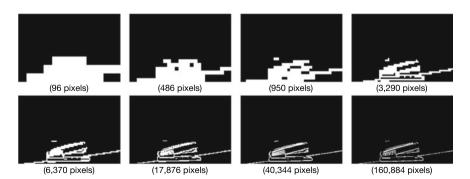

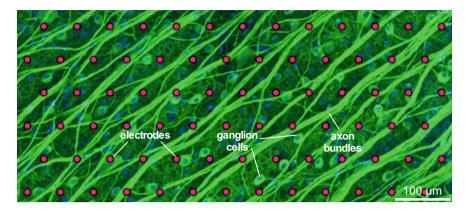

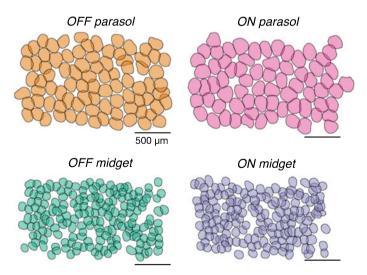

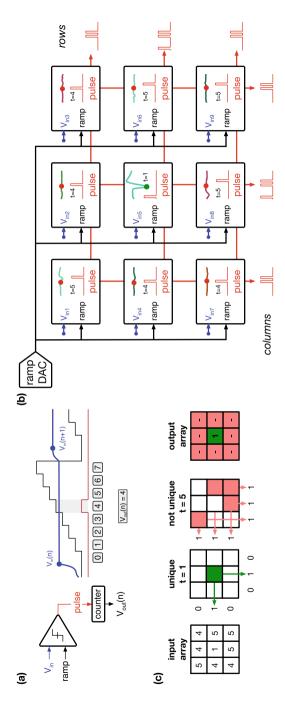

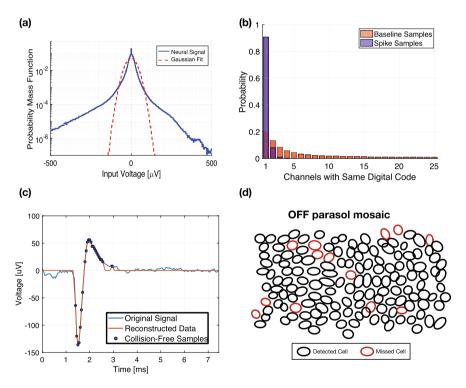

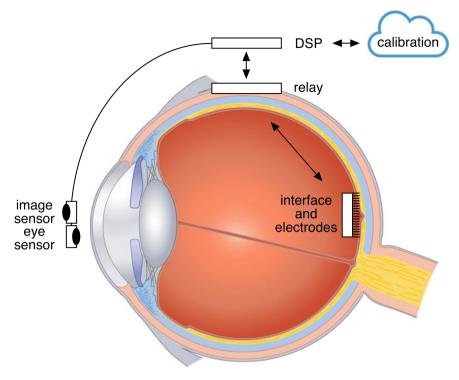

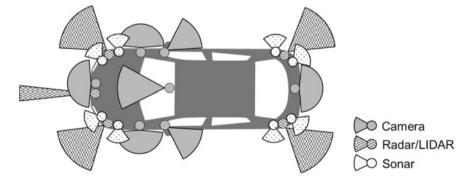

As electronic systems increase their interaction with the real world and strive to become significantly more power efficient, many of the traditional "brute force" data acquisition and signal processing approaches are being called into question. Chapter 3 of this book motivates this general trend and underlines the importance of log-domain perception, which is further underpinned in Chap. 21 on high dynamic range video. Chapter 17 advocates the concept of "Analog-to-Information" (A-to-I) conversion along similar lines as a replacement to conventional analog-to-digital conversion interfaces, which are bound to hit fundamental efficiency limits in the coming decade. An instantiation of A-to-I concepts is also found in Chap. 24, which details a massively parallel and data-compressive interface for cell mapping in the human retina. Finally, as many modern sensor interfaces to the real world take on the shape of large arrays, new ways to interface and integrate these with silicon must be found. Chapter 21 presents a cutting-edge example on a 3D-integrated photonic system for LIDAR and thereby builds bridges to Chap. 11 on 3D ASICS, as well as Chap. 29 on autonomous driving.

## 1.3 Neuromorphic Architectures and the Human Visual System

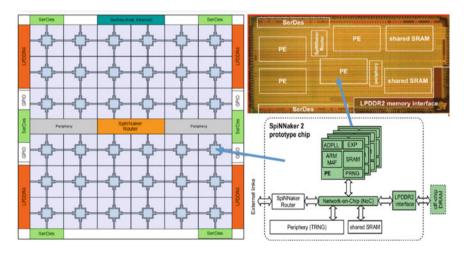

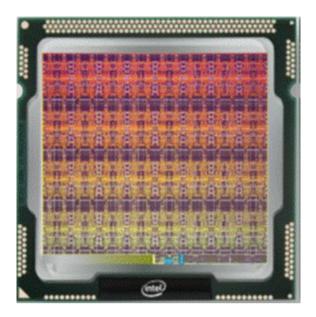

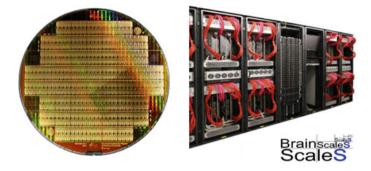

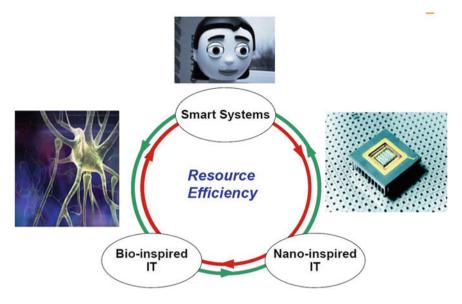

Reverse engineering and mimicking the brain has been an intriguing research direction in our long-standing quest on achieving the ultimate compute efficiency for intelligent systems. Recently, renewed interest in this topic has been fueled in part by large investments into the European Human Brain Project as well commercial activities such as Intel's Lohi development. Chapters 12 and 22 provide an overview of these activities and review the state of the art in brain-inspired architectures.

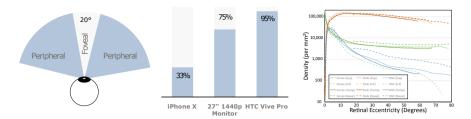

Ultimately, neuromorphic design is linked to our knowledge base in neuroscience, which nowadays is tightly coupled to progress in brain-machine interfaces and artificial intelligence research [4]. The dynamics between these fields are as exciting as ever and are beginning to inform the design of devices that would have been deemed science fiction not too long ago. An example covered in this book pertains to the next generation of artificial retina devices as described in Chap. 24. This application pushes our silicon capabilities to the limit and may enable the first high-fidelity prosthesis for restoring sight for age-related blindness. Another strong technology pull is expected to come from the processing needs for augmented and virtual reality (see Chap. 25), which will potentially redefine how we communicate, collaborate and learn. Chapter 28 expands on this trend with a more general discussion of man-machine collaboration and cognitronics and its technological needs.

#### 1.4 AI on-Chip and 3D Integration

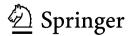

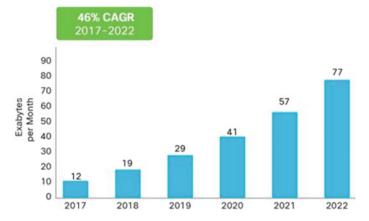

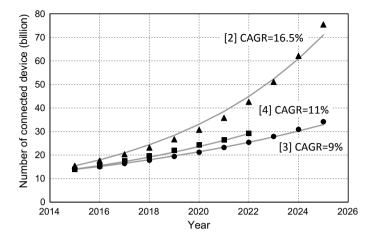

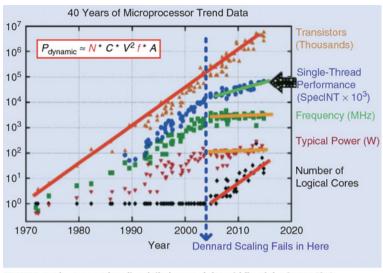

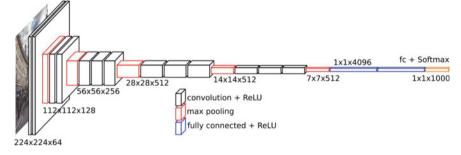

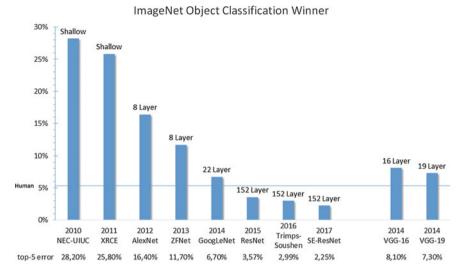

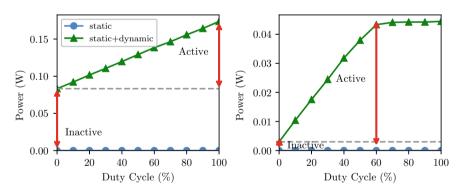

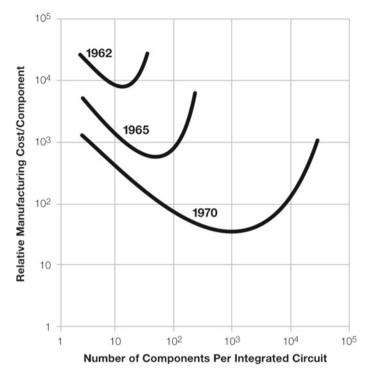

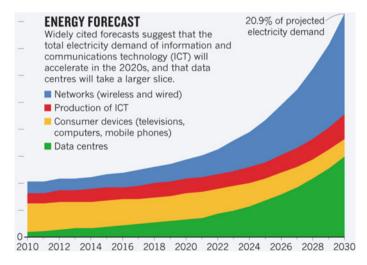

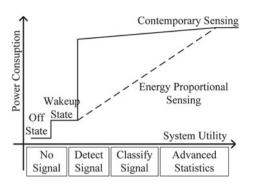

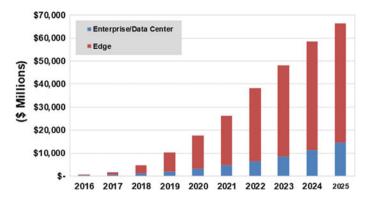

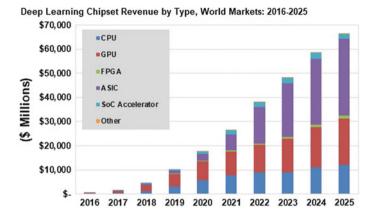

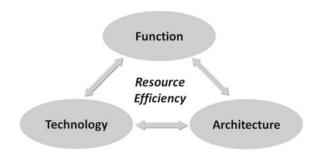

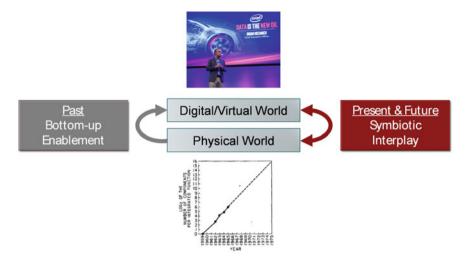

The past decade has brought renewed interest in deep neural networks as a cornerstone in our quest toward artificial intelligence (AI). While some of the core concepts behind these networks have been established decades ago, they are only now becoming mainstream with substantial application pull. The main factors behind this trend are the availability of immense amounts of data for training, as well as powerful computer hardware that can handle these data at high computational throughput. Figure 1.1 provides a simple, yet insightful cartoon that explains the success of deep learning. While older algorithms, often based on "hand-crafted" machine learning features, appeared to be superior with limited amounts of training data, deep learning approaches have shown unprecedented learning and classification abilities in today's environment with nearly unlimited data. Here, it is worth noting that the blue line in Fig. 1.1 is still sloping upward as of 2020, i.e. the algorithms continue to improve as we collect and use more training data.

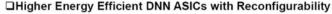

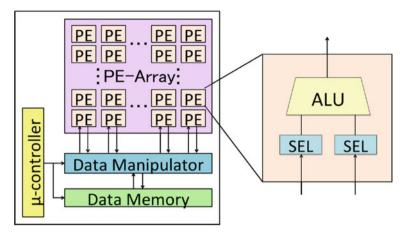

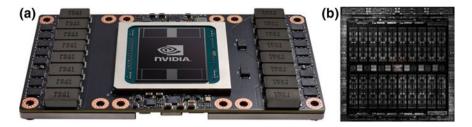

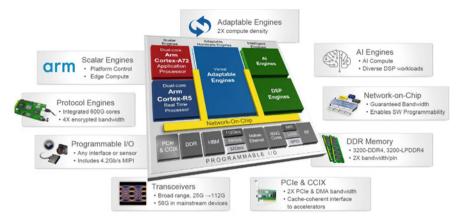

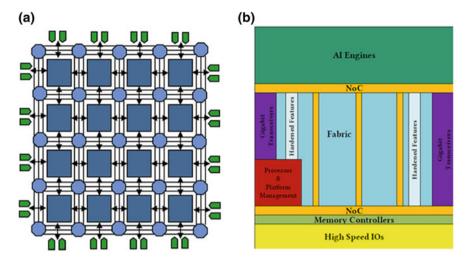

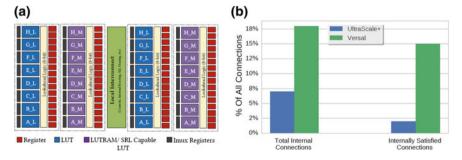

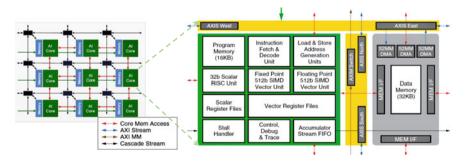

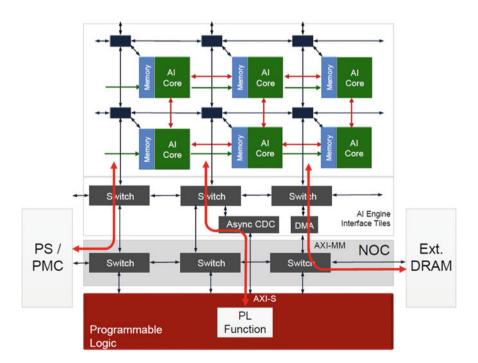

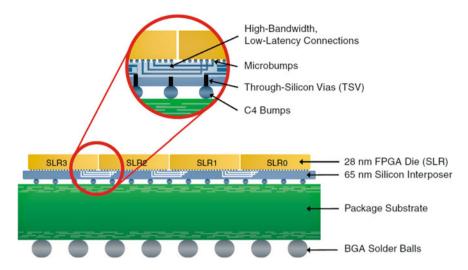

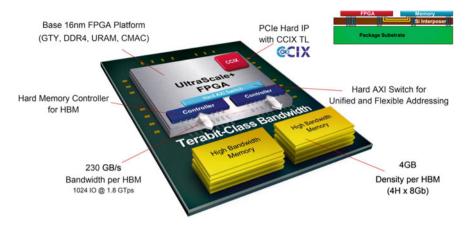

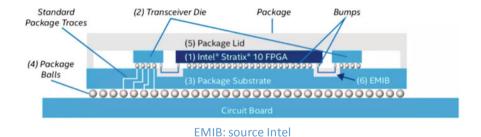

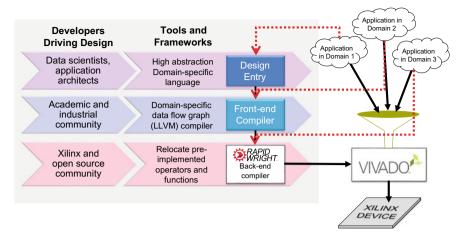

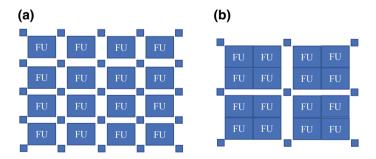

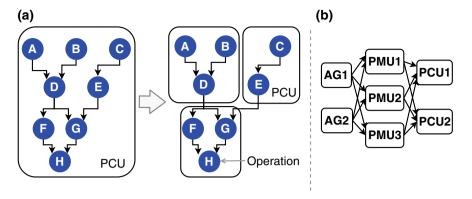

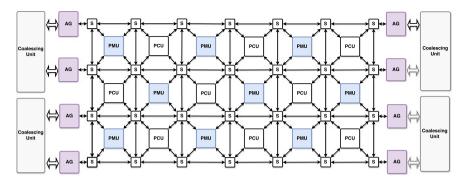

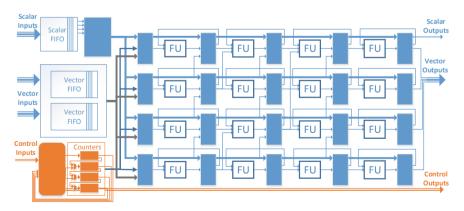

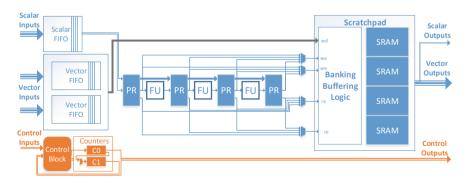

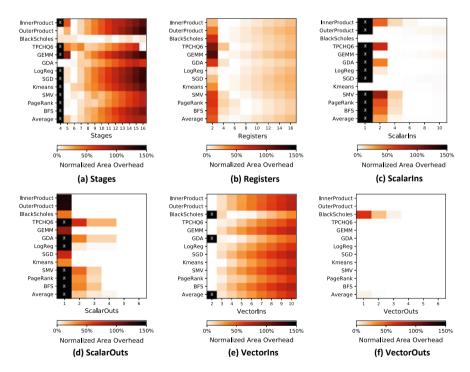

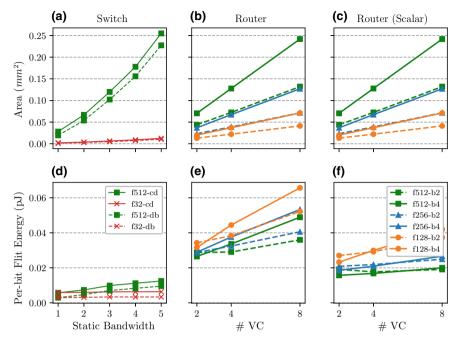

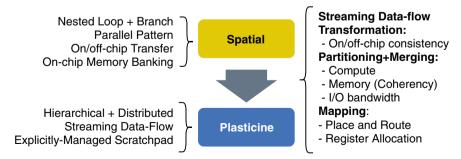

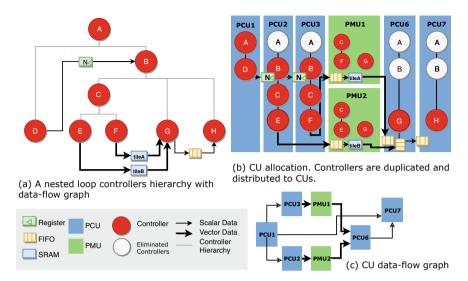

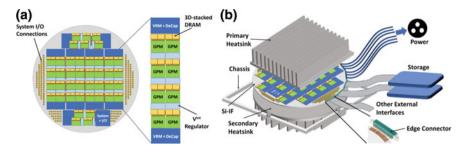

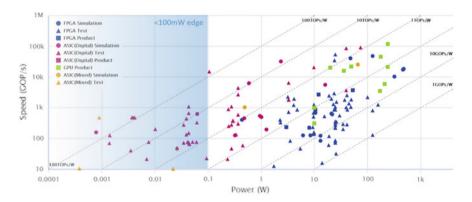

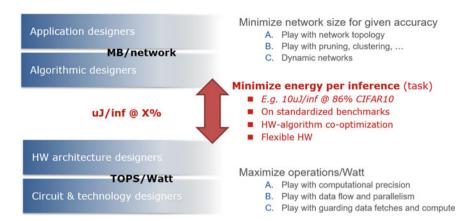

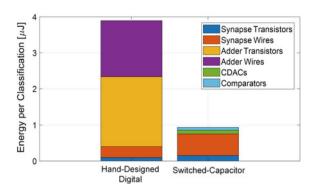

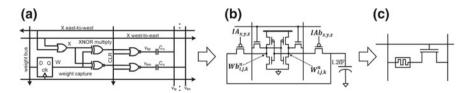

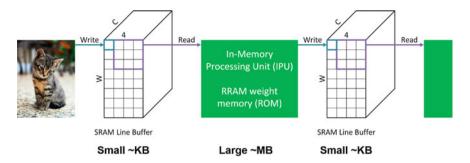

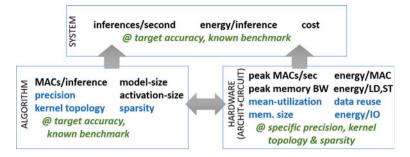

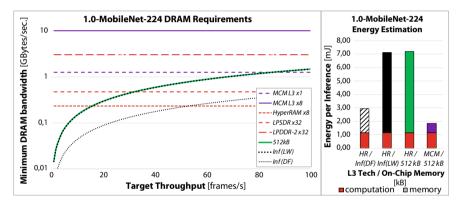

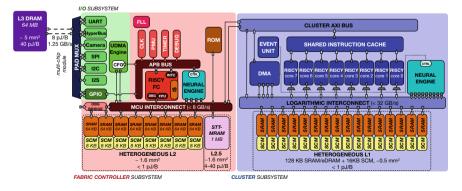

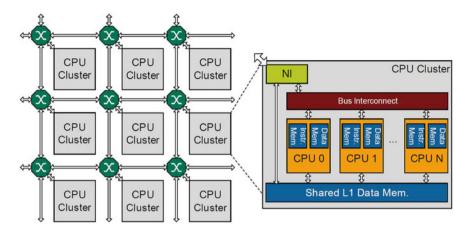

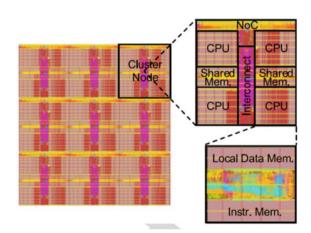

A grand challenge that arises from the aforementioned trend is the insatiable demand for memory and computing power, which persists across the various implementation scales of deep learning (servers, gateway systems, edge computing units, and tiny embedded systems). This book contains a number of contributions that discuss the underlying challenges and opportunities. Chapters 13 and 14 look at domain specific and coarse grain reconfigurable architectures (CGRAs) as a means to provide the required compute power while retaining a high degree of programmability that is needed in light of ever-changing algorithms and network topologies. Chapters 18 and 19 zoom in on relevant aspects for low-power edge systems, where the industry is already actively engaged in the developing custom deep learning processors.

A common denominator across all implementation scales is the challenge of memory access and data movement. These are discussed in detail in Chaps. 8–11,

Fig. 1.1 The success story of deep learning. Adopted from Andrew Ng, Stanford University

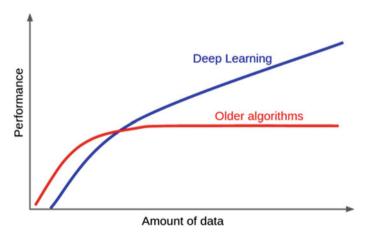

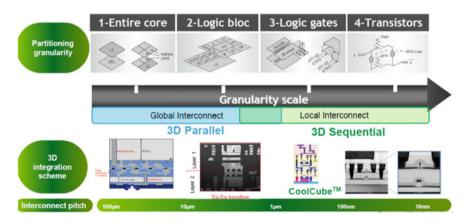

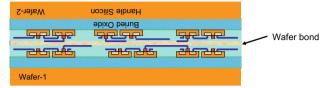

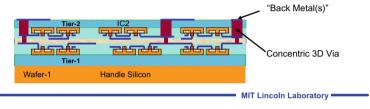

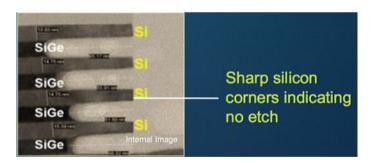

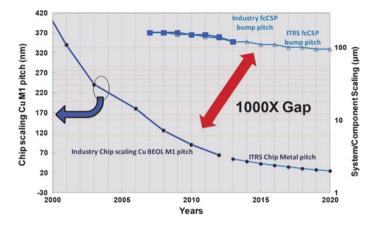

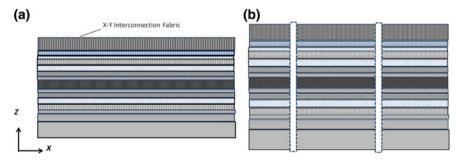

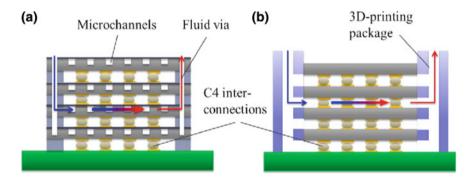

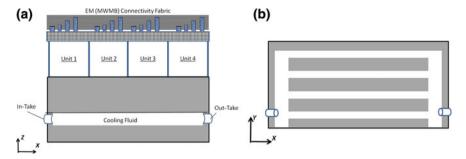

15, 18 and 19. In conventional 2D chips, designers are currently trying to tackle the issue using various forms of in-memory computing (see e.g., Chap. 18). For the long term, however, there is a growing consensus that we must explore the third dimension to couple memory and compute more closely. Through Chaps. 8–11 and 15, this book provides a comprehensive overview of the various competing approaches to 3D integration from chip stacking to monolithic integration.

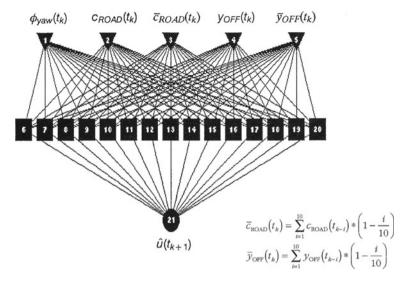

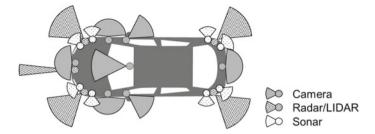

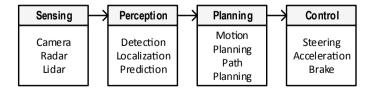

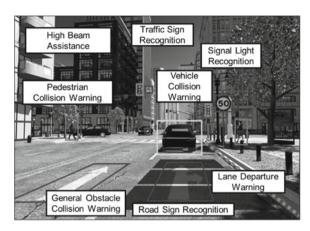

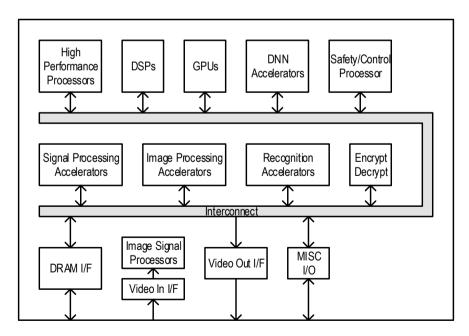

#### 1.5 Man-Machine Cooperation and Safe Control

The nano-electronic realization of artificial intelligence towards 2030 and beyond is among the key topics of this book, as already discussed. In most application scenarios, these chip systems are part of a "machine," as for instance a navigator, a surgery support system, a prosthesis, a robot, a "carebot" or a vehicle. As all of these machines are trending toward increasingly autonomous actions, effective communication and cooperation with them becomes essential and critical. Cognitive actions and special features on both sides, humans and machines, as well as within their class, must be planned, interpreted and understood in real time. A special overview on this subject is presented in Chap. 28, while virtually all chapters contain contributions that are relevant to the construction of such complex and intelligent systems. A leading system-on-chip for autonomous driving at level 4, which entails avoiding collisions with other vehicles and pedestrians, is described in Chap. 29. A recurring theme here is to devise safe architectures that can autonomously adapt to failures and operate in an error-resilient manner and with robust performance within dynamically changing and uncertain environments.

To realize the ultimate vision of effective man-machine cooperation, order-of-magnitude improvements in all aspects within the process technology, circuit and system stack are needed. We hope that the pathfinding discussions in this book will help the community to drive the next decade of great opportunities and benefits from the application and continuing development of nano-chips.

#### References

- B. Hoefflinger (ed.), in CHIPS 2020—A Guide to the Future of Microelectronics (Springer Science and Business Media, 2012). ISBN 978-3-642-22399-0