Begül Bilgin Jean-Bernard Fischer (Eds.)

# Smart Card Research and Advanced Applications

17th International Conference, CARDIS 2018 Montpellier, France, November 12–14, 2018 Revised Selected Papers

# Lecture Notes in Computer Science

Commenced Publication in 1973 Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

## Editorial Board

David Hutchison Lancaster University, Lancaster, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Friedemann Mattern ETH Zurich, Zurich, Switzerland John C. Mitchell Stanford University, Stanford, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel C. Pandu Rangan Indian Institute of Technology Madras, Chennai, India Bernhard Steffen TU Dortmund University, Dortmund, Germany Demetri Terzopoulos University of California, Los Angeles, CA, USA Doug Tygar University of California, Berkeley, CA, USA

More information about this series at http://www.springer.com/series/7410

# Smart Card Research and Advanced Applications

17th International Conference, CARDIS 2018 Montpellier, France, November 12–14, 2018 Revised Selected Papers

*Editors* Begül Bilgin Rambus - Cryptography Research Rotterdam, Zuid-Holland, The Netherlands

KU Leuven Leuven-Heverlee, Belgium Jean-Bernard Fischer Nagravision Cheseaux-sur-Lausanne, Vaud, Switzerland

ISSN 0302-9743 ISSN 1611-3349 (electronic) Lecture Notes in Computer Science ISBN 978-3-030-15461-5 ISBN 978-3-030-15462-2 (eBook) https://doi.org/10.1007/978-3-030-15462-2

Library of Congress Control Number: 2019933892

LNCS Sublibrary: SL4 - Security and Cryptology

#### © Springer Nature Switzerland AG 2019

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This Springer imprint is published by the registered company Springer Nature Switzerland AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

# Preface

These proceedings contain the papers selected for presentation at the 17th Smart Card Research and Advanced Applications Conference (CARDIS 2018), which was held in Montpellier, France, during November 12–14, 2018, and organized by the Montpellier Laboratory of Informatics, Robotics and Microelectronics (LIRMM).

Since 1994, CARDIS has provided a forum for experts from industry and academia to exchange ideas on the security of smart cards and related applications. The smart card object has been part of our daily life for so many years in the form of personal devices (banking cards, SIM cards, electronic IDs, etc.) that we do not remember a life without it. In relation to smart card security, the root of trust of embedded solutions is becoming key as Machine-to-Machine (M2M) and Internet of Things (IoT) applications are increasing massively. This increased exposure naturally widens the attack space, whether physical or logical, local or remote. It is more important than ever to understand how smart cards and other embedded devices can be secured by discussing all aspects of their design, development, deployment, evaluation, and application.

This year, CARDIS received 28 valid submissions from 12 countries. Each paper was double-blind reviewed by at least three independent reviewers. We selected 13 papers based on 102 written reviews from the 30 members of the Program Committee with the help of 35 external reviewers. The technical program also featured three invited talks: Frank Piessens from KU Leuven in Belgium presented "Security Specifications for the Hardware/Software Interface"; Benoit Feix from eshard in France presented "Exploiting a New Dimension in Side-Channel Analysis: Scatter on Symmetric and Asymmetric Embedded Cryptography"; and Wyseur Brecht from Nagravision in Switzerland presented "Challenges in Securing Industrial IoT and Critical Infrastructure." A free tutorial was held co-located with the conference: "Understanding Leakage Detection" organized by the REASSURE Consortium.

We would like to thank the general chair, Philippe Maurine, for the great venue and smooth operation of the conference. We would also like to express our gratitude to the Program Committee and the external reviewers for their thorough work, which enabled the technical program to be of such high quality, and the Steering Committee for giving us the opportunity to serve as program chairs at such a prestigious conference. The financial support of all the sponsors was highly appreciated and greatly facilitated the organization of the conference; we thank the sponsors: ANSSI, CNRS, Gemalto, Nagra-Kudelski, LETI-CEA, LIRMM, Rambus, STMicroelectronics, University of Montpellier. Last but not least, we would like to thank all the authors who submitted their work to CARDIS 2018.

January 2019

Begül Bilgin Jean-Bernard Fischer

# Organization

# **General Chair**

| Philippe Maurine          | University of Montpellier, France                                       |  |  |  |  |

|---------------------------|-------------------------------------------------------------------------|--|--|--|--|

| Program Chairs            |                                                                         |  |  |  |  |

| Begül Bilgin              | Rambus-Cryptography Research, The Netherlands<br>and KU Leuven, Belgium |  |  |  |  |

| Jean-Bernard Fischer      | Nagravision, Switzerland                                                |  |  |  |  |

| Steering Committee        |                                                                         |  |  |  |  |

| Emanagia Varian Standaart | UC Louvein Polgium                                                      |  |  |  |  |

| François-Xavier Standaert | UC Louvain, Belgium                     |

|---------------------------|-----------------------------------------|

| (Chair)                   |                                         |

| Thomas Eisenbarth         | Worcester Polytechnic Institute, USA    |

| Aurélien Francillon       | EURECOM, France                         |

| Edouard de Jong           | De Jong Frz. Holding BV                 |

| Marc Joye                 | NXP Semiconductors, USA                 |

| Konstantinos              | Royal Holloway University of London, UK |

| Markantonakis             |                                         |

| Amir Moradi               | Ruhr University Bochum, Germany         |

| Svetla Nikova             | KU Leuven, Belgium                      |

| Pierre Paradinas          | Inria and CNAM, France                  |

| Jean-Jacques Quisquater   | UC Louvain, Belgium                     |

| Francesco Regazzoni       | University of Lugano, Switzerland       |

| Yannick Teglia            | Gemalto, France                         |

|                           |                                         |

# **Program Committee**

| Josep Balasch       | KU Leuven, Belgium                          |

|---------------------|---------------------------------------------|

| Guillaume Barbu     | IDEMIA, France                              |

| Alessandro Barenghi | Politecnico di Milano, Italy                |

| Sonia Belaïd        | CryptoExperts, France                       |

| Thomas De Cnudde    | KU Leuven, Belgium                          |

| Jeroen Delvaux      | Nanyang Technological University, Singapore |

| Thomas Eisenbarth   | Universität zu Lübeck, Germany              |

| Benoix Feix         | eshard, France                              |

| Domenic Forte       | University of Florida, USA                  |

| Aurélien Francillon | Eurecom, France                             |

| Elke De Mulder      | Rambus-Cryptography Research, USA           |

| Elke De Mulder      | Rambus-Cryptography Research, USA           |

| Hannes Gross        | TU Graz, Austria                            |

|                     |                                             |

Vincent Grosso Radboud University, The Netherlands Annelie Heuser **CNRS/IRISA**. France Marc Jove NXP Semiconductors. USA Kerstin Lemke-Rust Bonn-Rhein-Sieg University, Germany Roel Maes Intrinsic ID, The Netherlands Oliver Mischke Infineon, Germany Ruhr University Bochum, Germany Amir Moradi IIT Kharagpur, India Debdeep Mukhopadhyay Axel Y. Poschmann DarkMatter, UAE Emmanuel Prouff ANSSI. France Francesco Regazoni ALaRi, Switzerland Kazuo Sakiyama University of Electro-Communications, Japan Sabanci University, Turkey Erkay Savas **Tobias Schneider** UC Louvain, Belgium Gemalto, France Yannick Teglia Yuval Yarom University of Adelaide, and Data61, Australia Carolyn Whitnall University of Bristol, UK Riscure. The Netherlands Marc Witteman

## **Additional Reviewers**

Alberto Battistello Ryad Benadjila Shivam Bhasin Manuel Bluhm Olivier Bronchain Giovanni Camurati Nicolas Debande David El-Baze Berk Gulmezoglu Christoph Herbst James Howe Malika Izabachene Angshuman Karmakar Elif Bilge Kavun Albert Levi Marco Martinoli Ahmet Can Mert Marius Muench

Erdinc Ozturk Jungmin Park Sikhar Patranabis Thomas Pöppelmann **Bastian Richter** Debapriya Basu Roy Okan Seker Rémi Strullu Shahin Tajik Benjamin Timon Lucille Tordella Rei Ueno Aurelien Vasselle Nikita Veshchikov Junwei Wang Felix Wegener Jan Wichelmann

# Contents

| Convolutional Neural Network Based Side-Channel Attacks                                                                                              |            |

|------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| in Time-Frequency Representations                                                                                                                    | 1          |

| Guang Yang, Huizhong Li, Jingdian Ming, and Yongbin Zhou                                                                                             |            |

| A Systematic Study of the Impact of Graphical Models on Inference-Based                                                                              |            |

| Attacks on AES                                                                                                                                       | 18         |

| Improving Side-Channel Analysis Through Semi-supervised Learning<br>Stjepan Picek, Annelie Heuser, Alan Jovic, Karlo Knezevic,<br>and Tania Richmond | 35         |

| Non-profiled Mask Recovery: The Impact of Independent                                                                                                | <b>5</b> 1 |

| Component Analysis                                                                                                                                   | 51         |

| How (Not) to Use Welch's T-Test in Side-Channel Security Evaluations<br>François-Xavier Standaert                                                    | 65         |

| Scalable Key Rank Estimation (and Key Enumeration) Algorithm                                                                                         |            |

| for Large Keys                                                                                                                                       | 80         |

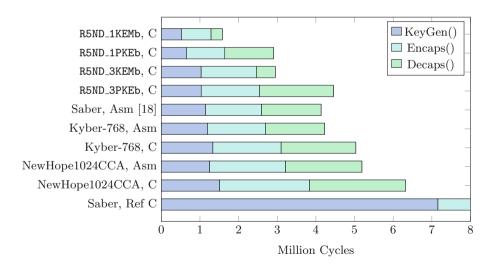

| Shorter Messages and Faster Post-Quantum Encryption with Round5<br>on Cortex M                                                                       | 95         |

| Markku-Juhani O. Saarinen, Sauvik Bhattacharya,<br>Oscar Garcia-Morchon, Ronald Rietman, Ludo Tolhuizen,<br>and Zhenfei Zhang                        |            |

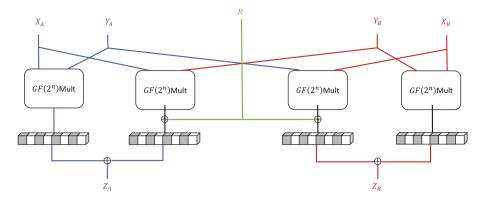

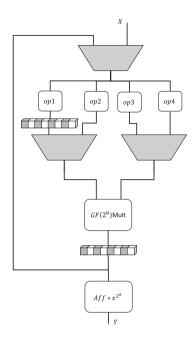

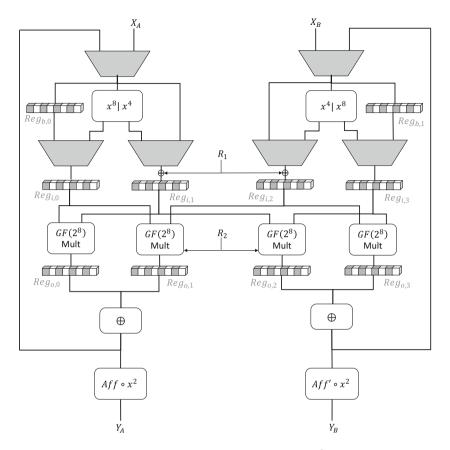

| Yet Another Size Record for AES: A First-Order SCA Secure                                                                                            |            |

| AES S-Box Based on GF(2 <sup>8</sup> ) Multiplication<br>Felix Wegener and Amir Moradi                                                               | 111        |

| Jitter Estimation with High Accuracy for Oscillator-Based TRNGs<br>Shaofeng Zhu, Hua Chen, Limin Fan, Meihui Chen, Wei Xi,<br>and Dengguo Feng       | 125        |

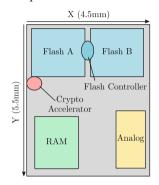

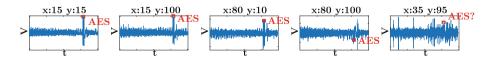

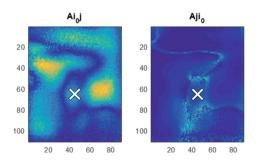

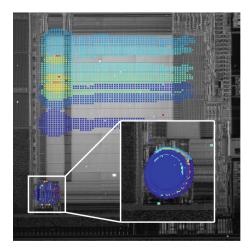

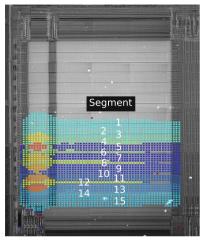

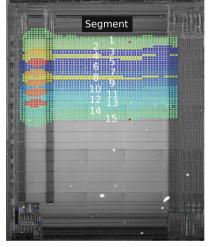

| Electromagnetic Activity vs. Logical Activity: Near Field Scans for Reverse Engineering.                                                             | 140        |

| Marc Lacruche and Philippe Maurine                                                                                                                   |            |

# X Contents

| An In-Depth and Black-Box Characterization of the Effects of Laser<br>Pulses on ATmega328P<br>Dilip S. V. Kumar, Arthur Beckers, Josep Balasch, Benedikt Gierlichs,<br>and Ingrid Verbauwhede | 156 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Breaking All the Things—A Systematic Survey of Firmware Extraction<br>Techniques for IoT Devices                                                                                              | 171 |

| Exploiting JCVM on Smart Cards Using Forged References<br>in the API Calls                                                                                                                    | 186 |

| Author Index                                                                                                                                                                                  | 201 |

# Convolutional Neural Network Based Side-Channel Attacks in Time-Frequency Representations

Guang Yang<sup>1,2</sup>, Huizhong Li<sup>1,2</sup>, Jingdian Ming<sup>1,2</sup>, and Yongbin Zhou<sup>1,2</sup>(🖂)

<sup>1</sup> State Key Laboratory of Information Security,

Institute of Information Engineering, Chinese Academy of Sciences, Beijing, China

$\{\texttt{yangguang2,lihuizhong,mingjingdian,zhouyongbin} \\ \texttt{Qiie.ac.cn}$

<sup>2</sup> School of Cyber Security, University of Chinese Academy of Sciences,

Beijing, China

Abstract. Profiled attacks play a fundamental role in the evaluation of cryptographic implementation worst-case security. For the past sixteen years, great efforts have been paid to develop profiled attacks from Template Attacks to deep learning based attacks. However, most attacks are performed in time domain – may lose frequency domain information. In this paper, to utilize leakage information more effectively, we propose a novel deep learning based side-channel attack in time-frequency representations. By exploiting time-frequency patterns and extracting high level key-related features in spectrograms simultaneously, we aim to maximize the potential of convolutional neural networks in profiled attacks. Firstly, an effective network architecture is deployed to perform successful attacks. Secondly, some critical parameters in spectrogram are studied for better training the network. Moreover, we compare Template Attacks and CNN-based attacks in both time and time-frequency domain with public datasets. The heuristic results in these experiments provide a new perspective that CNN-based attacks in spectrograms give a very feasible option to the state-of-the-art profiled attacks.

**Keywords:** Side-Channel Attacks  $\cdot$  Time-frequency analysis  $\cdot$  Spectrogram  $\cdot$  Convolutional neural networks  $\cdot$  Deep learning

# 1 Introduction

Side-Channel Attacks (SCAs), introduced in 1996 by Paul Kocher [16], have become a serious threat to practical security of cryptographic devices. They exploit side-channel leakages, such as power consumption and electromagnetic radiation, to recover the secret information of cryptographic algorithm implemented in a physical device. Side-Channel Attacks can be divided into two classes: non-profiled attacks, such as Differential Power Analysis (DPA) [17], Correlation Power Analysis (CPA) [4] and Mutual Information Analysis (MIA) [11],

B. Bilgin and J.-B. Fischer (Eds.): CARDIS 2018, LNCS 11389, pp. 1–17, 2019. https://doi.org/10.1007/978-3-030-15462-2\_1

<sup>©</sup> Springer Nature Switzerland AG 2019

and profiled attacks, such as Template Attacks (TA) [6] and Stochastic Attacks (SA) [30].

Among all the SCAs, profiled attacks are recognized as the most powerful ones and play a fundamental role of security evaluation of cryptographic algorithm implementations. A profiled attack consists of two phases: the profiling phase and the attack phase. For the profiling phase, the attacker procures a copy of the target device and learns the unique physical leakage characteristics with known keys. For the attack phase, the attacker attempts to recover the unknown key in the target device with the help of profiled leakage details. Among profiled attacks, TA is the most popular profiling approach. But in real profiled attacks, the dependency of preprocessing (need trace alignment), difficulties of numerical problems (need careful calculation) and curse of dimensionality (need dimension reduction) together affect the performance of TA [8].

Recently, a line of machine learning (ML), especially deep learning (DL) based attacks, raises SCA community's concern [5,14,21,24–26,28]. In 2016, Maghrebi et al. conducted the first analysis of deep learning techniques for profiled attacks [21]. In 2017, Cagli et al. found that convolutional neural network (CNN) based profiled attacks are robust to trace deformation like jitter due to CNN's translation invariance [5]. In 2018, Prouff et al. studied how hyperparameters affect deep learning based attacks in the presence of masking and desynchronization [26]. Picek et al. considered the class imbalance problem when training ML/DL models [24]. Robyns et al. proposed a Correlation Optimization method to improve Correlation Electromagnetic Analysis (CEMA) [28].

Generally, the SCAs including TA and deep learning based attacks are usually performed in the time domain and less in frequency domain. Because the sidechannel measurements (traces) are usually acquired in waveform, most attacks focus on analysing raw traces. But there are still several works proving that SCA in frequency has its own advantages in non-profiled attacks [10, 20, 22, 28]. Normally, directly analysing traces in time domain is less efficient while the traces are misaligned. To transform traces from time domain to frequency domain, a Fourier transform is performed. But the Fourier transform is only able to retrieve the global frequency content of a signal, thus more irrelevant information will be included and the time information is lost [10]. To overcome this shortcoming, short-time Fourier transform (STFT) is an optional approach. STFT computes the Fourier transform over windowed trace segmentation and shifts window over the trace. Previous work shows that CPA can be used on spectrograms (squared magnitude of STFT) [15]. In the field of image processing, CNN processes 2D signal better because it handles features in two dimension (2D) simultaneously. We inspire by the success of CNN in these areas and aim to perform successful profiled attacks based on CNN in spectrograms.

In this paper, we propose a novel deep learning based SCAs method with raw traces in time-frequency representations. In our work, we transform traces into spectrograms as the first step, then use CNN to learn time-frequency 2D patterns and extract high level key-related features. Effective network architecture is deployed to perform successful attacks. Furthermore, we study the relationship between some critical parameters (leakage patterns and window size) in spectrograms and the network performance. Finally, we demonstrate the effectiveness of our proposed method by comparing TA and CNN-based attacks in both time and time-frequency domain with public datasets.

#### 2 Preliminaries

#### 2.1 Notations

Let  $\mathbf{x} = {\mathbf{x}_i | i = 1, 2, ..., N}$  denote side-channel leakage acquisitions (traces) from a certain physical device, where  $\mathbf{x}_i$  denotes a single trace corresponding to one cryptographic calculation. Notice that  $\mathbf{x}_i$  is an one-dimension (1D) time sequence vector and the *i*-th entry of the vector  $\mathbf{x}$  is denoted by  $\mathbf{x}[i]$ . Let  $\mathbf{X} = {\mathbf{X}_i | i = 1, 2, ..., N}$  denote the spectrogram representation of  $\mathbf{x}$ . Notice that  $\mathbf{X}_i = \text{STFT}(\mathbf{x}_i)$  is a two-dimension (2D) time-frequency image metrix and the *i*, *j*-th entry of the matrix  $\mathbf{X}$  is denoted by  $\mathbf{X}[i, j]$ . During the acquisition, a target sensitive variable V = f(T, K) is handled, where T denotes plaintext or ciphertext, K the part of secret key the attacker aims to retrieve and f some transform functions (not mainly concerned in this paper). T is uniformly distributed which guarantees the randomness of corresponding measurement  $\mathbf{x}$ .

#### 2.2 Spectrogram

The short-time Fourier transform (STFT) is a ubiquitous tool for signal analysis and processing. As the signal is analysed in the frequency domain, it overcomes the time-domain limitations. Moreover, STFT can provide a precise time-frequency resolution within a specified window of the fixed size. In practice, the procedure for computing STFT is to divide a long time signal into several shorter segments of equal length and then compute the discrete time Fourier transform (DTFT) separately on each segment. Indeed, the STFT is usually computed with overlapping analysis windows, which introduces dependencies between adjacent windows and reduce artifacts at the boundary. In the discrete case, STFT function could be expressed as Eq. (1):

$$STFT\{x[n]\}(m,\omega) \equiv X(m,\omega) = \sum_{n=-\infty}^{\infty} x[n]w[n-mH]e^{-j\omega n}, \qquad (1)$$

where  $X(m, \omega)$  is DTFT of windowed data, x[n] is input signal at time n, w[n] is window function,  $\omega$  is phrase, m is position of window and H is an overlap constant between successive windows. In time-frequency signal processing, it is a common practice to work only with the magnitude of the STFT of a signal, so the phase information is ignored as in Eq. (2):

spectrogram{

$$x[n]$$

} $(m,\omega) \equiv |X(m,\omega)|^2$ . (2)

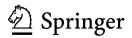

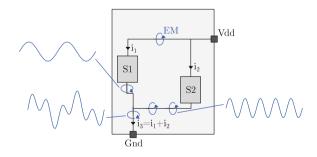

In other words, spectrogram is the visual representation of the energy of a signal expressed as a function of frequency and time. For the sake of clarity, an illustration of trace and spectrogram is shown in Fig. 1, the spectrogram in (b) is the energy of STFT function.

**Fig. 1.** An example of trace and spectrogram. The spectrogram is the magnitude of STFT (A bar graph is used here to show the 2D spectrogram intuitively).

#### 2.3 Profiled Side-Channel Attacks

A profiled attack consists of two phases: an offline profiling phase (training in machine learning context), and an online attack phase (testing respectively).

In profiling phase, the attacker has a device with knowledge about the secret key implemented and acquires a set of N side-channel traces  $\mathbf{x}_{profiling} = {\mathbf{x}_i | i = 1, 2, ..., N}$ . Each trace  $\mathbf{x}_i$  is corresponding to  $v_i = f(t_i, k)$  in one encryption or decryption with known key k. Usually the traces are measured from power consumption or electromagnetic radiation using probes with an oscilloscope. Once the acquisition is done, the attacker builds suitable models and computes the estimation of probability:

$$\Pr[\mathbf{x}|V=v]\,,\tag{3}$$

from a profiling set  $\{\mathbf{x}_i, v_i\}_{i=1,2,\ldots,N}$ .

In the attack phase, the attacker acquires a small new set of traces  $\mathbf{x}_{attack} = \{\mathbf{x}_i | i = 1, 2, ..., M\}$  with a fixed unknown key  $k^*$ . With the help of the established models, the attacker can easily calculate the estimated posterior probabilities among k guesses following the Maximum Likelihood Criterion:

$$d_k = \prod_{i=1}^{M} \Pr[v_i = f(t_i, k) | \mathbf{x} = \mathbf{x}_i] = \prod_{i=1}^{M} \frac{\Pr[\mathbf{x} = \mathbf{x}_i | v_i = f(t_i, k)] \cdot \Pr[v_i = f(t_i, k)]}{\Pr[\mathbf{x} = \mathbf{x}_i]} .$$

(4)

Equation (4) stands only when acquisitions are independent which is a practical condition in reality.

The most widely used profiled attacks are Template Attacks (TA) [6] and its modified version Efficient Template Attacks (ETA) [9]. In TA, the attacker estimates conditional probability Eq. (3) by assuming that  $\mathbf{x}$  follows a multivariate Gaussian distribution and estimating the mean trace  $\bar{\mathbf{x}}_{t_i,k}$  and the covariance matrix  $\Sigma_{t_i,k}$  for each possible  $(t_i, k)$  pair. Equation (3) then turns into:

$$\Pr[\mathbf{x}|V=v] = \frac{\exp(-\frac{1}{2} \cdot (\bar{\mathbf{x}} - \mathbf{x})^T \cdot \Sigma^{-1} \cdot (\bar{\mathbf{x}} - \mathbf{x}))}{\sqrt{(2\pi)^N \cdot |\Sigma|}}.$$

(5)

In ETA, the attacker replaces the covariance matrixes with one pooled covariance matrix to cope with some statistical difficulties [9].

#### 2.4 Convolutional Neural Networks

Convolutional Neural Networks (CNN) are a category of neural networks with advantages including being similar to the human visual processing system, being highly optimized in structure for processing images, and being effective at learning and extracting abstractions of features [2]. In this section, we will introduce basic concepts of CNN.

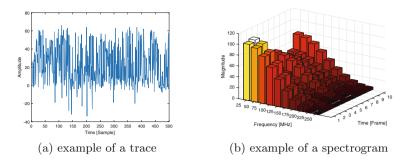

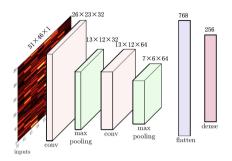

Fig. 2. The overall architecture of CNN

Figure 2 shows an overall architecture of CNN with two main parts: feature extractor and classifier. Feature extractor is composed of stacked operations of convolution, activation, pooling and sometimes normalization layers. The classifier is composed of several fully-connected layers of neurons. Each layer of the network receives the output from its immediate previous layer as its input, and passes its output as the input to the next layer, as it is called forward propagation. Higher-level features are derived from features propagated from lower level layers and finally calculate classification probabilities in the last output layer (for a classification task, usually the output layer is activated by softmax function as detailed in [5]).

**Convolutional Layer.** Convolutional layer is locally connected with shared weights in learnable kernels. Convolutional operation can be defined as:

$$s(t) \equiv (x * w)(t) = \sum_{a=1}^{n} x(a)w(t-a), \qquad (6)$$

where x are digital signals, w is the kernel function. Stride also affects Eq. (6) by controlling the step length of convolutional operation. The convolutional operations bring sparse connectivity and weight sharing. These properties reduce parameter amounts and computing time. The output of convolutional layers finally go through a non-linear activation function to simulate a biological neuron functionality. The activation adopted in this paper is Rectified Linear Unit (ReLU): y = max(0, x) [18].

**Pooling Layer.** Pooling layer performs the downsampled operations to keep useful features and discard unnecessary details [3]. It helps represent translation invariance. The pooling kernel also slides window on the signal. For example, if a  $2 \times 2$  max-pooling kernel with  $2 \times 2$  strides is used, it outputs the maximum values within the window. Finally, the output size will be half of the input size.

Through training CNN, Backward Propagation algorithm is used with optimizer, such as SGD, Adagrad, AdaDelta, RMSprop, and Adam [29]. In this paper, we use Adam for efficient training with better convergence of deep learning algorithms [19].

# 3 Our Method

In this section we describe the leakages in spectrograms and discuss how to use CNN profiling and attacking from spectrograms.

#### 3.1 Leakages in Spectrograms

In Sect. 2.2 we describe the mathematical definition of STFT and show a quick look of spectrogram. As STFT indicates the spectral content of the signal at each short time segment, it is a function of time and frequency that indicates how the spectral content of a signal evolves over time. Sliding windows are moved to obtain the spectral content of the signal over different time intervals, and the window length affects the time frequency resolution of the STFT. A small window results in a fine time resolution but a coarse frequency resolution because small windows have a short time duration but a wide bandwidth. A large window, on the contrary, results in a fine frequency resolution but a coarse time resolution because large windows have a long time duration but a narrow frequency bandwidth.

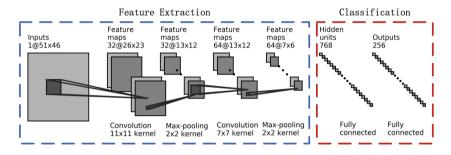

In profiling phase, as the sensitive value V = f(T, K) is related to the secret key, the attacker often uses statistical tools to locate the sensitive value position among discrete digital sample points. Such tools include Pearson correlation coefficient:  $\rho_{x,v} = \frac{\operatorname{cov}(x,v)}{\sigma_x \cdot \sigma_v}$  and Signal Noise Ratio (SNR):  $snr_{x,v} = \frac{\operatorname{Var}[E[x|v]]}{E[\operatorname{Var}[x|v]]}$ . By repetitively computing above equations through all sample points over raw trace set  $\mathbf{x}_{profiling}$ , leakage points (points of interest, PoI) stand out from sample points with high  $\rho$  or snr.

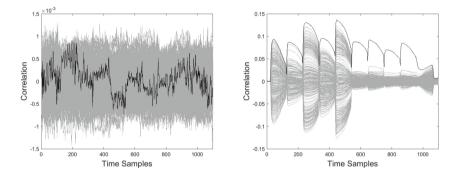

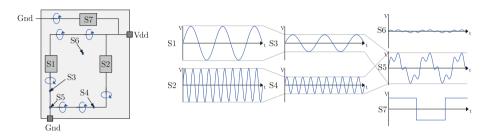

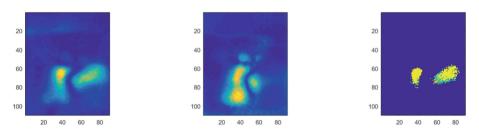

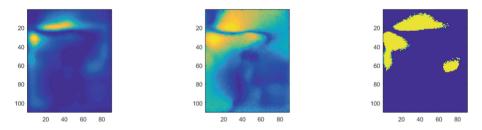

We transfer these statistical tools detecting leakages in 2D spectrograms and find leakage existing in spectral-temporal patterns within expectation. Specifically, we calculate  $\rho$  and *snr* through each sample point (pixel) in the 2D spectrogram. For example, spectrogram set  $\mathbf{X} = {\mathbf{X}_i | i = 1, 2, ..., N}$  is first calculated using Eq. (1) from raw trace set  $\mathbf{x} = {\mathbf{x}_i | i = 1, 2, ..., N}$ , where  $\mathbf{X}_i$

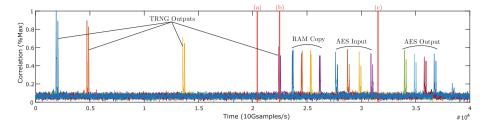

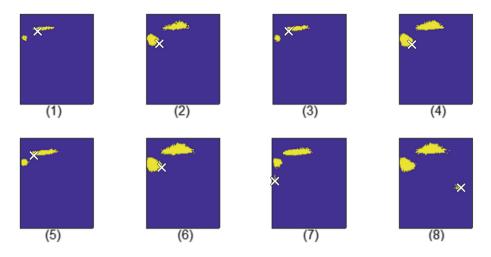

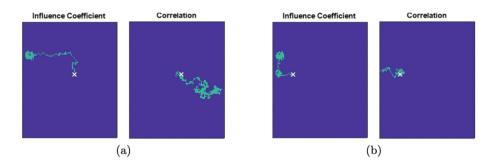

**Fig. 3.** Leakage detection of traces and spectrograms in Grizzly dataset (Color figure online)

is a matrix. After pixel-wise leakage detection, correlation coefficient matrix and SNR matrix can be obtained.

Figure 3 shows the leakage characteristics in traces and spectrograms from Grizzly dataset (detailed in Sect. 4.1). In both subfigures, the upper part is the normal leakage detection result of traces, the lower part is the result of spectrograms in the form of heat map. In heat maps, connected regions in white and yellow are dramatically distinguished from others in black, where brighter color corresponds to high numerical value of  $\rho$  and snr. Leakage in spectrogram is detected in warm regions, which reveals the fact that spectrogram contains the time-frequency leakage simultaneously. Time synchronization can be found in the upper and lower parts of the figure, while the difference between the raw trace and spectrogram leakages is that the leakages on the spectrogram form clusters on the two-dimensional plane. This simultaneity reflects in unique 2D image patterns which is quite suitable for CNN to classify.

#### 3.2 Builds CNN with Spectrograms

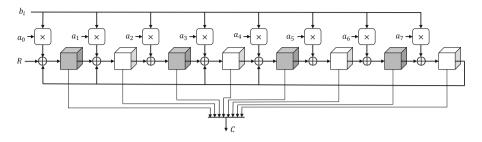

In this section, the 2D CNN network architecture is described in detail. We refer to some classic CNN architectures such as AlexNet [18] and VGGNet [31] to build our network. As shown in Fig. 4, the spectrograms are fed to the network, and the label of the spectrogram is the key-related sensitive variable. It is passed through a 2D convolutional layer, where we use filters with a small receptive field to extract features. In order to minimize information loss in the time and frequency dimensions, we set the convolution kernel size of equal width and height. The convolution operation extract patterns simultaneously on time and frequency. After the convolutional layer, a max-pooling layer is added with stride  $2 \times 2$  to downsample the time-frequency feature map. Then the combination of convolutional layer and pooling layer is performed once more for further feature extraction and reduction of network parameters amount. The max-pooling layer is followed by a fully-connected layer to flatten the data. All hidden layers are equipped with the ReLU non-linearity. The final layer is a fully-connected layer with 256 neuron nodes, corresponding to 256 categories respectively.

Fig. 4. A base network architecture for 2D CNN with spectrograms

## 4 Experiments

In this work, all experiments are conducted on an Intel(R) Xeon(R) CPU E5-2667 v3 @ 3.20 GHz 32 core machine, one NVIDIA Tesla K80 GPU and two NVIDIA Titan Xp GPUs. We use the Keras library [7] (version 2.1.3) with TensorFlow library [1] (version 1.4.1) as backend for CNN linked to NVIDIA CuDNN.

#### 4.1 Datasets

We consider three public datasets which mainly differ from implementations. All the datasets are made public exclusively for SCA research. We use these datasets for reproducibility of our results.

**DPA contest V4.1 (DPAv4.1)** provides measurement of a masked software implementation of AES-256 on an Atmel ATMega-163 smart-card [34]. For the acquisitions, we have 125 points per clock. We preselect consecutive 500 points for each trace. In our experiment, we use the first round S-box output as the label to train CNN:

$$V = \operatorname{Sbox}[P \oplus k^*] \oplus M, \tag{7}$$

where P is a plaintext byte, M is a known mask byte. Since all AES intermediate variables are defined in Galois field  $GF(2^8)$ , label V contains 256 classes.

**Grizzly** provides measurement of an unprotected implementation of the 8-bit CPU Atmel XMEGA 256 A3U [23]. In our experiments, we have 1000 points per clock. We preselect consecutive 2500 points for each trace. Our goal is to determine the success of the profiled attacks in recovering the byte k processed. The S-box output V is the label to train CNN, which is provided in the dataset.

**DPA contest V2 (DPAv2)** provides measurement of an unprotected hardware implementation of the AES-128 algorithm on SASEBO GII FPGA board [33]. There are roughly 213 points per clock. We preselect consecutive 1000 points for each trace. Since the parallel block cipher encryption is implemented, DPAv2 is a difficult dataset to attack. Previous works showed the most suitable leakage operation is the register writing in the last round:

$$V = \text{Sbox}^{-1}[C_1 \oplus k^*] \oplus C_2, \tag{8}$$

where  $C_1$  and  $C_2$  are two ciphertext bytes. In our experiments,  $C_1$  is the 12-th ciphertext byte and  $C_2$  is the 8-th one according to [25].

#### 4.2 Evaluation Method

In this paper, evaluation metrics like top-1 accuracy (Acc), top-3 accuracy (Top3 Acc), success rate (SR) and guessing entropy (GE) are used to evaluate the effectiveness of key retrieval. For SR and GE as detailed in [32], we run the attack 100 times with randomly selected sub-samples of  $\mathcal{D}_{validate}$  or  $\mathcal{D}_{attack}$  to find the average number of traces to achieve GE<1 bit and SR>80%. We run a 10-fold cross-validation on  $\mathcal{D}_{profiling}$  to determine the STFT window size, and a normal training and attack on  $\mathcal{D}_{profiling}$  and  $\mathcal{D}_{attack}$  to compare different profiled attacks.

#### 4.3 Preprocessing

For each dataset, we preselect a continuous segmentation of all sample points to reduce computing complexity. Then we perform STFT on each dataset with customized window size through exhaustive search for better attacking performances, detailed in Sect. 4.5. Just as the normal SCA and deep learning approach, we split each dataset into 2 distinct part  $\mathcal{D}_{profiling}$  and  $\mathcal{D}_{attack}$ . While in training phase, the  $\mathcal{D}_{profiling}$  is further divided into 2 parts  $\mathcal{D}_{train}$  and  $\mathcal{D}_{validate}$ , where the validation set  $\mathcal{D}_{validate}$  serves as an indicator of early stopping to avoid overfitting. Table 1 shows the data splitting size in each dataset.

| Dataset | Profiling | Attack |  |  |

|---------|-----------|--------|--|--|

| DPAv4.1 | 9000      | 1000   |  |  |

| Grizzly | 51200     | 10000  |  |  |

| DPAv2   | 90000     | 10000  |  |  |

Table 1. Data splitting size in 3 datasets

Finally, before training the networks, a Min-max normalization  $\frac{X-X_{\min}}{X_{\max}-X_{\min}}$  is performed to scale features into [0, 1] range, which will avoid gradient problems in network training phase. Notice that data augmentation [5,24,27] is not performed in our experiments, because the purpose of our experiments is to determine the validity of utilizing spectrograms, not to solve misalignment or jitter problems. And also there are no class imbalance issues since we consider identity function to generate the label.

#### 4.4 CNN Architecture

The signal, represented by 1D raw traces or 2D spectrograms, is feed-forwarded through CNN layers. The feature extraction part includes one or more operations: convolutional filter, activation, batch normalization and pooling [5,21]. Convolutional stride is set to 1 and zero-padding is used to prevent valid operation in the edge of feature map. The pooling stride is set to 2 for downsampling layer input size and the parameter amount of next layer. The classification part contains a stack of layers followed by several fully-connected layers with ReLU. A dropout rate of 50% is between the last 2 fully-connected layers to prevent overfitting. Sometimes a global max-pooling is used to downsample feature map in each channel to reduce the parameter size of fully-connected layers. The last fully-connected layer contains 256 neurons activated by softmax function, calculating the classification score. The cross-entropy is used as loss function.

The 2D CNN basic architecture is illustrated in Sect. 3.2. The design of neural architecture is under an overall consideration among previous works [5, 18, 21, 26]. The detailed architecture is slightly different between 3 datasets in the number of convolutional layers and pooling layers. For DPAv4.1 and Grizzly, since they are software implementations and the data amount is small, fewer convolution operations and small filters (size 3 and 5) are performed. For DPAv2, since it is an FPGA implementation, more convolutional operations and large filters (size 11) are used to enlarge receptive field against high sampling rate, and improve the feature extracting robustness against noises.

To train a proper network, several techniques are used to prevent overfitting and get better network generalization. The Adam optimizer with reduced learning rate is used to minimize the cross-entropy corresponds to maximize the likelihood of the right label. A mini batch of 200 is employed. The learning rate is initially 0.001 and reduced to half when the loss doesn't decrease for 10 epochs with a threshold of 0.0001. We set 200 epochs for the training, but also set an early stopping threshold of 40 epochs (which monitors the validation loss and stops the training if the loss doesn't fall). During the training, the network kernel weights are recorded for the best validation loss. Once the training is done we reconstruct the neuron network with the best recorded weights. With higher values for training epochs, overfitting occurs and no improvements have been noticed. The weight of filters activated by ReLU is randomly initialized with Gaussian distribution  $N(0, \sqrt{\frac{2}{n_l}})$  according to [12], where  $n_l$  is the neuron number of previous layer.

#### 4.5 Spectrogram Parameters

In this work, a single trace is segmented in several windows with overlap of 90%. We set the overlap for 90%, because it doesn't impact the real time-frequency resolution and more importantly would benefit for software implementations which have stronger but sparser leakage signals [35], such as Grizzly. The Hanning window is used to segment traces as a common choice. The STFT of each window is calculated in order to find square of the magnitude of dominating frequency. Then we scale the spectrogram images to [0, 1] range for the convenience of network training as described before.

In STFT, small window size results in high time resolution but low frequency resolution, and vice versa in large window size scenario. Because of the trade-off between time and frequency in STFT, spectrogram can not guarantee both high time and frequency resolution. As each dataset is measured in different implementations running frequencies and sampling rates, we introduce both absolute window size (window length) and relative window size (percentage of one clock) to represent window size. To find an optimal window size for SCA on spectrogram, an exhaustive search is used to determine window size, evaluated by a 10-fold cross-validation on the profiling set  $\mathcal{D}_{profiling}$ . We evaluate the robustness of window size configuration by calculating the average evaluation metrics on 10 validation sets.

Table 2 shows the cross-validation evaluation results on  $\mathcal{D}_{profiling}$  with the help of 2 NVIDIA Titan Xp GPUs. It takes 3 h for DPAv4.1, 6 h for Grizzly and 8 h for DPAv2 to run the cross-validation algorithms, roughly 3 min, 6 min and 8 min for a single training. In DPAv4.1, a window size of 64 (1/2 of a clock)achieves the best accuracy where a single spectrogram (Spc for short) has an average success rate of 95.9%. Since DPAv4.1 is a software implementation on a smart card, the noise is much lower than other two datasets. The leakages distribute in large range of time and frequency with high SNR. Window size influences the attack so little that similar accuracy is achieved with various window sizes. In Grizzly, when the window size is set to 125 (1/8 of a clock), the network loss converges to 3.74 and 8.49% accuracy is achieved. It takes only 3 traces for GE under 1 bit and 4 traces for SR more than 80%. When the window goes larger or smaller, more traces are needed accordingly. Same phenomenon occurs in DPAv2 dataset where proper windows size (100, 1/2 of a clock) results in better performances—averaging 700 traces to achieve SR over 80%. Large window (200 or 300) brings a coarse time resolution which explains the decline in performances. Furthermore, small window (less than 50) leads to profiling failure, thus no guarantee of successful key recovery.

As a matter of fact, the choice of window size is conditioned by two limitations: (1) the window length should be small enough (better within a clock length) so that the windowed trace segmentation is essentially stationary over the window interval, (2) the window length should be large enough (better more than 64) so that the DTFT of the windowed trace segmentation provides a reasonable frequency resolution. Considering both two constraints empirically, we think window size from 64 to 256 suits most cases in practice. Specifically, balanced

| Window@ | Percentage | Spc size  | Loss  | Acc               | Top3 Acc      | $\mathrm{GE} < 1$ | $\mathrm{SR} > 80\%$ |

|---------|------------|-----------|-------|-------------------|---------------|-------------------|----------------------|

| DPAv4.1 | 8@1/16     | (4, 494)  | 0.159 | 95.3%             | 99.6%         | 1                 | 1                    |

|         | 16@1/8     | (8,243)   | 0.168 | 94.9%             | 99.7%         | 1                 | 1                    |

|         | 32@1/4     | (16, 181) | 0.153 | 95.2%             | 99.7%         | 1                 | 1                    |

|         | 64@1/2     | (32, 63)  | 0.142 | 95.9%             | <b>99.7</b> % | 1                 | 1                    |

|         | 125@1      | (63, 29)  | 0.199 | 94.1%             | 99.6%         | 1                 | 1                    |

|         | 187@3/2    | (94, 17)  | 0.195 | 94.5%             | 99.5%         | 1                 | 1                    |

| Grizzly | 62@1/16    | (32, 349) | 4.08  | 6.56%             | 16.86%        | 5                 | 5                    |

|         | 125@1/8    | (63, 183) | 3.74  | 8.49%             | 21.28%        | 3                 | 4                    |

|         | 250@1/4    | (126, 91) | 3.76  | 8.28%             | 21.07%        | 3                 | 4                    |

|         | 500@1/2    | (251, 41) | 5.00  | 2.95%             | 7.40%         | >10               | >10                  |

|         | 1000@1     | (501, 16) | 5.51  | 0.51%             | 1.53%         | >10               | >10                  |

|         | 1000@3/2   | (751,7)   | 5.01  | 1.98%             | 5.55%         | >10               | >10                  |

| DPAv2   | 12@1/16    | (6,495)   | 5.544 | 0.43%             | 1.29%         | >1500             | >1500                |

|         | 25@1/8     | (12, 326) | 5.544 | 0.43%             | 1.30%         | >1500             | >1500                |

|         | 50@1/4     | (25, 191) | 5.536 | 0.62%             | 1.63%         | 750               | 750                  |

|         | 100@1/2    | (50, 91)  | 5.536 | $\mathbf{0.65\%}$ | <b>1.67</b> % | 700               | 700                  |

|         | 200@1      | (100, 41) | 5.538 | 0.60%             | 1.58%         | 950               | 900                  |

|         | 300@3/2    | (300, 48) | 5.538 | 0.63%             | 1.60%         | 950               | 950                  |

**Table 2.** Cross-validation averaging results for different window sizes of STFT toperform a 2D CNN-based attack

time and frequency resolutions lead to a balanced spectrogram image width and height. On the one hand, a balanced spectrogram size takes both time and frequency into consideration in STFT. On the other hand, a "square" spectrogram image is more suitable for convolution and pooling operations because the filter size and stride are usually designed with same width and height. For example, when the window is 1000 long in Grizzly, the spectrogram size is  $501 \times 16$ , namely high time but low frequency resolution, after 4 convolution layers and pooling layers with downsampling rate 2, the spectrogram size becomes  $32 \times 1$  which implies redundant frequency information but exhausted temporal information. The imbalance in information utilization probably leads to information loss and profiling failure.

#### 4.6 Attack Comparisons

In this section, by applying the proper STFT window size and network architecture in previous sections, we represent traces into spectrograms and compare different profiled attacks in raw and time-frequency representations.

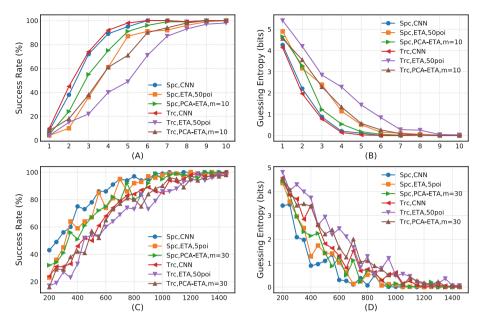

To exploit leakages in spectrogram and confirm the effectiveness of CNNbased attacks, we evaluate several CNN-based attacks and Template Attacks

13

(as baseline method) in raw traces and spectrograms on each dataset. For clarity, Efficient Template Attacks (ETA) in both spectrograms and traces are performed after a PoI selection (5,25,50 points with highest correlation coefficient). Furthermore, Principal Component Analysis (PCA) [13] is also used before ETA and serves as a reference feature extractor of raw traces and spectrograms. We select top 5, 10, 20, 30 eigenvectors picking by correlation coefficient to perform ETAs. For CNN-based attacks, to take the most of the profiling set, we random split a small ratio of the data as validation set when training in case of overfitting. Similar network architecture is used for 1D CNN as the same as 2D CNN by replacing 2D operations into 1D operations. 200 epochs (recording the best validation loss during training) are deployed for better convergence.

| Method               |           | DPAv4.1 |                   |                     | Grizzly |                   |                     | DPAv2 |                   |                     |

|----------------------|-----------|---------|-------------------|---------------------|---------|-------------------|---------------------|-------|-------------------|---------------------|

|                      |           | Acc     | $\mathrm{GE} < 1$ | $\mathrm{SR} > 0.8$ | Acc     | $\mathrm{GE} < 1$ | $\mathrm{SR} > 0.8$ | Acc   | $\mathrm{GE} < 1$ | $\mathrm{SR} > 0.8$ |

| $\operatorname{Spc}$ | 2D CNN    | 95.5%   | 1                 | 1                   | 8.47%   | 3                 | 4                   | 0.82% | 400               | 550                 |

|                      | ETA,5poi  | 15.0%   | 4                 | 3                   | 2.46%   | 7                 | 5                   | 0.67% | 600               | 550                 |

|                      | ETA,25poi | 58.4%   | 2                 | 2                   | 2.85%   | 6                 | 6                   | 0.61% | 650               | 750                 |

|                      | ETA,50poi | 82.5%   | 1                 | 1                   | 3.64%   | 5                 | 5                   | 0.65% | 1000              | 1050                |

|                      | PCA-ETA   | 82.5%   | 1                 | 1                   | 5.75%   | 5                 | 4                   | 0.59% | 650               | 650                 |

| Trc                  | 1D CNN    | 96.5%   | 1                 | 1                   | 9.52%   | 3                 | 4                   | 0.63% | 750               | 650                 |

|                      | ETA,5poi  | 1.9%    | 9                 | 7                   | 2.08%   | 8                 | 7                   | 0.59% | 1500              | 1500                |

|                      | ETA,25poi | 32.1%   | 2                 | 2                   | 2.76%   | 7                 | 6                   | 0.61% | 950               | 1000                |

|                      | ETA,50poi | 63.5%   | 2                 | 2                   | 2.59%   | 7                 | 6                   | 0.57% | 750               | 850                 |

|                      | PCA-ETA   | 86.9%   | 1                 | 1                   | 4.48%   | 6                 | 5                   | 0.60% | 850               | 750                 |

Table 3. Attack results of our method and baseline methods

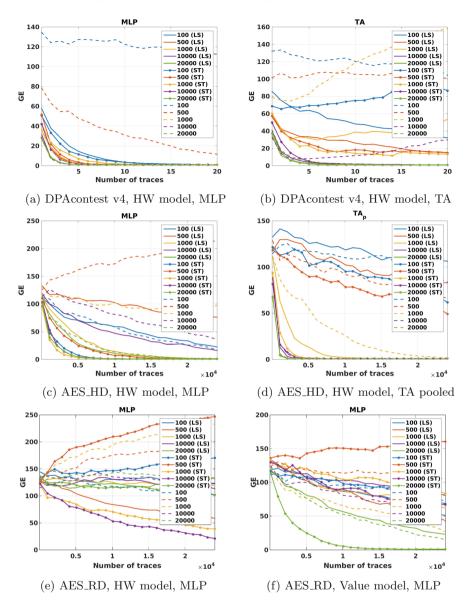

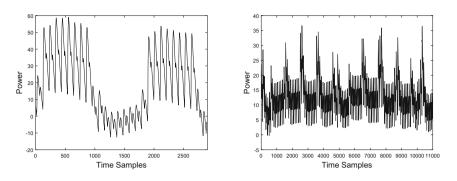

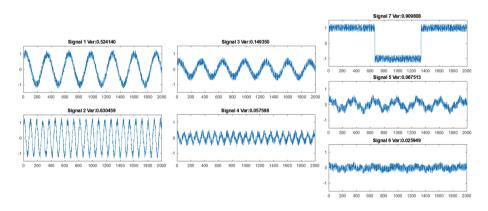

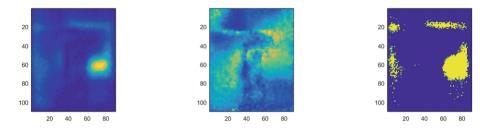

The results we obtained are summarized in Table 3 and Fig. 5 (without DPAv4.1 brevity). As for DPAv4.1, CNN-based attack in spectrograms can achieve more than 95% accuracy with a single spectrogram to recover the key byte, which proves the soundness of attacks in spectrograms. Next, we test our methods on Grizzly, an 8 bit MCU software implementation. As it is shown in Table 3 and Fig. 5, ETA in spectrograms get higher accuracy than in raw traces with same PoI number. PCA-ETA also works better in spectrograms than in traces with top 5, 10, 20, 30 eigenvectors picking by correlation coefficient. Meanwhile, CNN-based attacks significantly outperform ETA in both time and time-frequency domain, gaining GE<1 bit with only 3 traces. Finally we challenge our method in DPAv2, which is much more difficult to attack. The result shows that attacks in spectrogram are more effective than in raw traces with same profiling techniques. There, only 400 spectrograms are needed for GE less than 1 bit with the 2D CNN in spectrograms, compared with more than 750 traces with attacks (including 1D CNN) in raw traces. Since in this experiment more traces/spectrograms (nearly all profiling set  $\mathcal{D}_{profiling}$ ) are used for training, and evaluation is performed on  $\mathcal{D}_{profiling}$ , the neuron network trains with more data than in Sect. 4.5 and gets better performances.

Naturally, spectrogram is a combined representation of time domain and frequency domain. Compared with raw traces in time domain, spectrograms lose

Fig. 5. Results of Grizzly (A, B) and DPAv2 (C, D)

little time resolution but gain frequency resolution. A single pixel in spectrogram contains both time-frequency information than a point in raw traces with higher  $\rho$  and snr. This peculiarity shows its advantage if time information is not good enough for a successful attack. Last but not least, as it is observed in Sect. 3.1, PoI in spectrogram show patterns, gathered in clusters along time domain and expanded in low frequency domain. Patterns hide local time-frequency high level features in spectrogram. CNN extracts feature through recognizing patterns, which explains CNN-based attacks exceed ETA because PoI selection destroys 2D time-frequency patterns and ETA itself can't handle these 2D patterns. Therefore, CNN is naturally the choice of attacks in spectrograms.

# 5 Conclusions

In this paper, we investigate the side-channel leakage in time-frequency representations and propose a new profiling strategy using CNN. Experiments show that by analysing temporal-frequency transformation in spectrogram representation, 2D time-frequency patterns can be utilized for extracting high level features and classified for key recovery. Effects of different window sizes on CNN-based attacks are studied. Compared with classic profiled attacks in 1D raw traces, CNN-based attacks in 2D spectrograms achieve better performances than Template Attacks and at least same effectiveness (sometimes better) as CNN-based attacks in raw traces. Despite results shown here, there is still room for improvement. Side-channel countermeasures, masking and hiding, are not considered in this work, as this paper focus on pioneering a new profiled side-channel strategy. As STFT is calculated on each independent single trace, masking and hiding are completely reflected in single spectrogram. In other words, leakage existing in high order and random spatial positions, which can be analysed by CNN due to its feature extraction and transformation invariance. Future works will study CNN based attacks in time-frequency representations in the presence of masking and hiding countermeasures.

Acknowledgment. This work is supported in part by Natural Science Foundation of China (No. 61632020, 61472416 and 61602468), National Key Research and Development Program of China (No. 2017YFB0802705) and the National Cryptography Development Fund under Grant MMJJ 20180223.

## References

- Abadi, M., et al.: Tensorflow: a system for large-scale machine learning. OSDI 16, 265–283 (2016)

- 2. Alom, M.Z., et al.: The history began from alexnet: a comprehensive survey on deep learning approaches. CoRR abs/1803.01164 (2018)

- Boureau, Y., Ponce, J., LeCun, Y.: A theoretical analysis of feature pooling in visual recognition. In: Proceedings of the 27th International Conference on Machine Learning (ICML-2010), 21–24 June 2010, Haifa, Israel, pp. 111–118 (2010)

- Brier, E., Clavier, C., Olivier, F.: Correlation power analysis with a leakage model. In: Joye, M., Quisquater, J.-J. (eds.) CHES 2004. LNCS, vol. 3156, pp. 16–29. Springer, Heidelberg (2004). https://doi.org/10.1007/978-3-540-28632-5\_2

- Cagli, E., Dumas, C., Prouff, E.: Convolutional neural networks with data augmentation against jitter-based countermeasures. In: Fischer, W., Homma, N. (eds.) CHES 2017. LNCS, vol. 10529, pp. 45–68. Springer, Cham (2017). https://doi.org/ 10.1007/978-3-319-66787-4\_3

- Chari, S., Rao, J.R., Rohatgi, P.: Template attacks. In: Kaliski, B.S., Koç, K., Paar, C. (eds.) CHES 2002. LNCS, vol. 2523, pp. 13–28. Springer, Heidelberg (2003). https://doi.org/10.1007/3-540-36400-5\_3

- 7. Chollet, F., et al.: Keras (2015). https://keras.io

- Choudary, M.O., Kuhn, M.G.: Efficient, portable template attacks. IEEE Trans. Inf. Forensics Secur. 13(2), 490–501 (2018). https://doi.org/10.1109/TIFS.2017. 2757440

- Choudary, O., Kuhn, M.G.: Efficient template attacks. In: Francillon, A., Rohatgi, P. (eds.) CARDIS 2013. LNCS, vol. 8419, pp. 253–270. Springer, Cham (2014). https://doi.org/10.1007/978-3-319-08302-5\_17

- Debande, N., Souissi, Y., Elaabid, M.A., Guilley, S., Danger, J.: Wavelet transform based pre-processing for side channel analysis. In: 45th Annual IEEE/ACM International Symposium on Microarchitecture, MICRO 2012, Workshops Proceedings, Vancouver, BC, Canada, 1–5 December 2012, pp. 32–38 (2012). https://doi.org/ 10.1109/MICROW.2012.15

- Gierlichs, B., Batina, L., Tuyls, P., Preneel, B.: Mutual information analysis. In: Oswald, E., Rohatgi, P. (eds.) CHES 2008. LNCS, vol. 5154, pp. 426–442. Springer, Heidelberg (2008). https://doi.org/10.1007/978-3-540-85053-3\_27

- He, K., Zhang, X., Ren, S., Sun, J.: Delving deep into rectifiers: surpassing humanlevel performance on imagenet classification. In: 2015 IEEE International Conference on Computer Vision, ICCV 2015, Santiago, Chile, 7–13 December 2015, pp. 1026–1034 (2015). https://doi.org/10.1109/ICCV.2015.123

- Jolliffe, I.: Principal component analysis. In: Lovric, M. (ed.) International Encyclopedia of Statistical Science, pp. 1094–1096. Springer, Heidelberg (2011). https:// doi.org/10.1007/978-3-642-04898-2\_455

- Kim, J., Picek, S., Heuser, A., Bhasin, S., Hanjalic, A.: Make some noise: unleashing the power of convolutional neural networks for profiled side-channel analysis. IACR Cryptology ePrint Archive 2018, 1023 (2018)

- Kim, M., Han, D., Ryoo, J.C., Yi, O.: CPA performance enhancement based on spectrogram. In: IEEE International Carnahan Conference on Security Technology, ICCST 2012, Newton, MA, USA, 15–18 October 2012, pp. 195–200 (2012). https:// doi.org/10.1109/CCST.2012.6393558

- Kocher, P.C.: Timing attacks on implementations of Diffie-Hellman, RSA, DSS, and other systems. In: Koblitz, N. (ed.) CRYPTO 1996. LNCS, vol. 1109, pp. 104–113. Springer, Heidelberg (1996). https://doi.org/10.1007/3-540-68697-5\_9

- Kocher, P., Jaffe, J., Jun, B.: Differential power analysis. In: Wiener, M. (ed.) CRYPTO 1999. LNCS, vol. 1666, pp. 388–397. Springer, Heidelberg (1999). https://doi.org/10.1007/3-540-48405-1\_25

- Krizhevsky, A., Sutskever, I., Hinton, G.E.: Imagenet classification with deep convolutional neural networks. In: Advances in Neural Information Processing Systems 25: 26th Annual Conference on Neural Information Processing Systems 2012, Proceedings of a Meeting Held 3–6 December 2012, Lake Tahoe, Nevada, United States, pp. 1106–1114 (2012)

- Le, Q.V., Ngiam, J., Coates, A., Lahiri, A., Prochnow, B., Ng, A.Y.: On optimization methods for deep learning. In: Proceedings of the 28th International Conference on Machine Learning, ICML 2011, Bellevue, Washington, USA, 28 June–2 July 2011, pp. 265–272 (2011)

- Longo, J., De Mulder, E., Page, D., Tunstall, M.: SoC It to EM: electromagnetic side-channel attacks on a complex system-on-chip. In: Güneysu, T., Handschuh, H. (eds.) CHES 2015. LNCS, vol. 9293, pp. 620–640. Springer, Heidelberg (2015). https://doi.org/10.1007/978-3-662-48324-4\_31

- Maghrebi, H., Portigliatti, T., Prouff, E.: Breaking cryptographic implementations using deep learning techniques. In: Carlet, C., Hasan, M.A., Saraswat, V. (eds.) SPACE 2016. LNCS, vol. 10076, pp. 3–26. Springer, Cham (2016). https://doi. org/10.1007/978-3-319-49445-6\_1

- Mateos, E., Gebotys, C.H.: A new correlation frequency analysis of the side channel. In: Proceedings of the 5th Workshop on Embedded Systems Security, WESS 2010, Scottsdale, AZ, USA, 24 October 2010, p. 4 (2010). https://doi.org/10.1145/ 1873548.1873552

- Omar Choudary, M.G.K.: Grizzly: power-analysis traces for an 8-bit load instruction. https://www.cl.cam.ac.uk/research/security/datasets/grizzly/. Accessed Oct 2017

- Picek, S., Heuser, A., Jovic, A., Bhasin, S., Regazzoni, F.: The curse of class imbalance and conflicting metrics with machine learning for side-channel evaluations. IACR Trans. Cryptogr. Hardw. Embed. Syst. 2019(1), 209–237 (2019). https:// doi.org/10.13154/tches.v2019.i1.209-237

- Picek, S., Samiotis, I.P., Kim, J., Heuser, A., Bhasin, S., Legay, A.: On the performance of convolutional neural networks for side-channel analysis. In: Chattopadhyay, A., Rebeiro, C., Yarom, Y. (eds.) SPACE 2018. LNCS, vol. 11348, pp. 157–176. Springer, Cham (2018). https://doi.org/10.1007/978-3-030-05072-6\_10

- Prouff, E., Strullu, R., Benadjila, R., Cagli, E., Dumas, C.: Study of deep learning techniques for side-channel analysis and introduction to ASCAD database. IACR Cryptology ePrint Archive 2018, 53 (2018)

- Pu, S., et al.: Trace augmentation: what can be done even before preprocessing in a profiled SCA? In: Eisenbarth, T., Teglia, Y. (eds.) CARDIS 2017. LNCS, vol. 10728, pp. 232–247. Springer, Cham (2018). https://doi.org/10.1007/978-3-319-75208-2\_14

- Robyns, P., Quax, P., Lamotte, W.: Improving CEMA using correlation optimization. IACR Trans. Cryptogr. Hardw. Embed. Syst. 2019(1), 1–24 (2019). https:// doi.org/10.13154/tches.v2019.i1.1-24

- Ruder, S.: An overview of gradient descent optimization algorithms. CoRR abs/1609.04747 (2016)

- Schindler, W., Lemke, K., Paar, C.: A stochastic model for differential side channel cryptanalysis. In: Rao, J.R., Sunar, B. (eds.) CHES 2005. LNCS, vol. 3659, pp. 30–46. Springer, Heidelberg (2005). https://doi.org/10.1007/11545262\_3

- Simonyan, K., Zisserman, A.: Very deep convolutional networks for large-scale image recognition. CoRR abs/1409.1556 (2014)

- Standaert, F.-X., Malkin, T.G., Yung, M.: A unified framework for the analysis of side-channel key recovery attacks. In: Joux, A. (ed.) EUROCRYPT 2009. LNCS, vol. 5479, pp. 443–461. Springer, Heidelberg (2009). https://doi.org/10.1007/978-3-642-01001-9\_26

- TELECOM ParisTech SEN Research Group: DPA Contest (2nd edition) (2009– 2010). http://www.DPAcontest.org/v2/

- TELECOM ParisTech SEN Research Group: DPA Contest (4th edition) (2013– 2014). http://www.DPAcontest.org/v4/

- Zhang, L., Ding, A.A., Fei, Y., Luo, P.: Efficient 2nd-order power analysis on masked devices utilizing multiple leakage. In: IEEE International Symposium on Hardware Oriented Security and Trust, HOST 2015, Washington, DC, USA, 5–7 May 2015, pp. 118–123 (2015). https://doi.org/10.1109/HST.2015.7140249

# A Systematic Study of the Impact of Graphical Models on Inference-Based Attacks on AES

Joey Green<sup> $(\boxtimes)$ </sup>, Arnab Roy, and Elisabeth Oswald

Department of Computer Science, University of Bristol, Merchant Venturers Building, Woodland Road, Bristol BS8 1UB, UK {joey.green,arnab.roy,elisabeth.oswald}@bristol.ac.uk

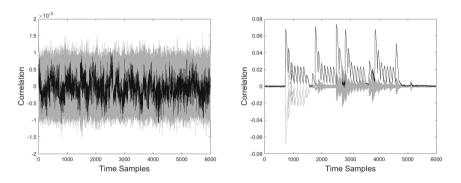

**Abstract.** Belief propagation, or the sum-product algorithm, is a powerful and well known method for inference on probabilistic graphical models, which has been proposed for the specific use in side channel analysis by Veyrat-Charvillon et al. [14].

We define a novel metric to capture the *importance* of variable nodes in factor graphs, we propose two improvements to the sum-product algorithm for the specific use case in side channel analysis, and we explicitly define and examine different ways of combining information from multiple side channel traces. With these new considerations we systematically investigate a number of graphical models that "naturally" follow from an implementation of AES. Our results are unexpected: neither a larger graph (i.e. more side channel information) nor more connectedness necessarily lead to significantly better attacks. In fact our results demonstrate that in practice the (on balance) best choice is to utilise an acyclic graph in an independent graph combination setting, which gives us provable convergence to the correct key distribution. We provide evidence using both extensive simulations and a final confirmatory analysis on real trace data.

**Keywords:** Belief propagation  $\cdot$  Factor graphs  $\cdot$  AES  $\cdot$  Inference based attacks  $\cdot$  Side channel attacks  $\cdot$  Template attacks

## 1 Introduction

Side channels in the form of power or EM traces are a significant source of information for adversaries. Extracting as much as possible of this information is clearly desirable, and the utilisation of graphical models for this purpose was early on described in publications such as [3,6,12]. These papers represented the algorithm under attack as a Markov model and inferred information about the underlying hidden state by using statistical inference, e.g. the max-product algorithm.

The key idea in such types of attacks is that the graphical model defines how variables (observed and hidden) depend on each other. By using different types

© Springer Nature Switzerland AG 2019

B. Bilgin and J.-B. Fischer (Eds.): CARDIS 2018, LNCS 11389, pp. 18–34, 2019. https://doi.org/10.1007/978-3-030-15462-2\_2

of algorithms it is possible to infer information about the hidden variables. The use of the sum-product algorithm (aka belief propagation, BP) on a factor graph was proposed recently in [14] as a way to utilise graphical models for complex algorithms such as AES. It proved to be very powerful: in comparison to other profiled attacks, this method can cope with very noisy side channel traces, and even combine information from many traces effectively. In follow on works this type of attack was compared to other types of DPA style attacks [4], and used in different contexts [13]. Although the method performed well in all these papers, it is well known that there are no guarantees for convergence, or even for the inferred distributions to be at all meaningful. This is due to the nature of the factor graphs that result from a typical implementation of e.g. AES. Thus like many other analysis methods it is possible that the method completely fails in some contexts, but is strong in other contexts.

In this submission we set out to determine how to best configure a graphical model to ensure attack success. We focus our study around the AES algorithm that was also chosen by the seminal papers introducing this method. Our results challenge in particular the intuition that "more" leakage makes for stronger attacks. This is interesting because more leakage intuitively implies more potential information: even if multiple leakages may provide redundant information (it is well known that AES achieves full diffusion after two rounds), this redundant information could be hoped to implicitly improve the signal quality. Consequently, one could expect that the more leakage information about AES is included in a factor graph, the more of this information can propagate to the key bytes.

#### 1.1 Outline of This Paper

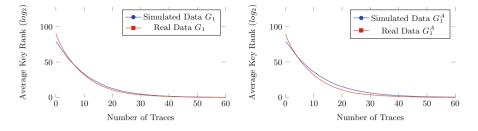

We review the necessary background on using (loopy) belief propagation in Sect. 2. Thereafter in Sect. 3 we explain two improvements of the sum-product algorithm. In Sect. 4 we give a novel definition that captures the *importance* of a variable node. We also define several variations of factor graphs of particular interest for attacks on AES. These variations essentially represent progressively smaller graphs, whereby the smallest is an acyclic graph requiring the least memory. For this graph the results guarantee convergence of the sum-product algorithm without any loss of success rate and efficiency. We also spell out three methods for combining multiple traces. Sections 5, 6, and 7 present results of experiments using simulated (we simulate leakage according to a weighted bit model, and add Gaussian noise) and real trace data. We observe that except for the noisiest of cases the acyclic graph with the most pragmatic trace combination method is on par with more complex variations. We conclude with recommendations for practice in Sect. 8.

To aid the flow of the paper we opted to supplying comprehensive tables and figures primarily in the appendix. The text however does summarise the most important findings from both tables and figures. There is also a full version of this work available on the IACR Eprint archive [2].

# 2 Preliminaries

The key ingredients for the attacks that we aim to study are a suitable graphical model and an algorithm for inference. We review these briefly using and relating them to AES as appropriate (for a more in-depth description we refer the reader to [7]). At the end of this section we provide the necessary details about our simulation environment.

### 2.1 Inference on Graphical Models

A factor graph is a bipartite graph  $G = (\mathcal{V}, \mathcal{F}, \mathcal{E})$  where  $\mathcal{V}, \mathcal{F}$  are two finite sets of vertices and  $\mathcal{E} \ (\subset \mathcal{V} \times \mathcal{F})$  is a set of undirected edges. We will refer to the vertices in  $\mathcal{V}$  as variable nodes and the vertices in  $\mathcal{F}$  as factor nodes. We will use the i, j, k to denote the variable nodes and f, g, h to denote the factor nodes. Given  $i \in \mathcal{V}$ , the set  $\partial i$  is defined as  $\partial i := \{f \in \mathcal{F} : (i, f) \in \mathcal{E}\}$ . For any  $f \in \mathcal{F}$ the adjacent vertices  $\partial f$  is defined in the same way.

A factor graph gives the joint distribution of the random variables  $\mathbf{X}_{\mathcal{V}} := (X_1, \ldots, X_{|\mathcal{V}|})$  where each  $X_i$  corresponds to a vertex in  $\mathcal{V}$ . For any subset of variable nodes  $\mathcal{I} := \{i_1, i_2, \ldots, i_m\} \subset \mathcal{V}$  we will denote the corresponding random variables as  $\mathbf{X}_{\mathcal{I}} := (X_{i_1}, X_{i_2}, \ldots, X_{i_m})$ . The values of these random variables  $\mathbf{x}_{\mathcal{I}}$ , are also defined in a similar way. For our application each random variable  $X_i$  can have values  $x_i \in \mathcal{X} := \{0, 1\}^n$ . For the rest of this article  $\mathcal{X}$  will denote the set  $\{0, 1\}^n$  unless specified otherwise. For the definition of the joint distribution we refer to the full version [2].

**Constructing a Factor Graph.** A factor graph can be constructed from (the implementation of) any iterative function  $F^1$ . The input variables, intermediate variables used in the iterative function, and the output variables are represented as the variable nodes of the factor graph. The factor nodes correspond to the basic functions/operations used to define (or implement) F. A factor node is usually connected to two or more variable nodes which represent the inputs and outputs of the function.

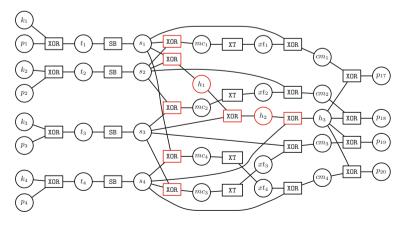

In practice an AES assembly implementation can be easily translated to a factor graph. The sixteen plaintext bytes and key bytes are represented as variable nodes. Parsing the (assembly) code, whenever an arithmetic operation is performed we add a factor node for this operation, and a new variable node to represent the output of the operation, and connect these elements to the existing graph. Although leaky, we excluded memory operations, such as ldr and str operations from our factor graph (so we do not artificially inflate leakages). Our AES factor graph thus includes the following factor operations: XOR, SBOX, and XTIMES.

<sup>&</sup>lt;sup>1</sup> A factor graph can also be constructed for non-iterative functions but this is not necessary for our work.

21

The Sum-Product Algorithm. The sum-product algorithm, also known as the belief propagation (BP) algorithm, is an iterative "message" passing algorithm where the messages are the probability distributions over the single variable space  $\mathcal{X}$ . For each edge in  $\mathcal{E}$  there are two such distributions  $\nu_{i\to f}(\cdot)$ , which is the message from variable node to factor node and  $\tilde{\nu}_{f\to i}(\cdot)$ , which is the message from a function node to variable node. The messages at the *t*th iteration are denoted as  $\nu_{i\to f}^{(t)}$  and  $\tilde{\nu}_{f\to i}^{(t)}$ .

For the definition of the sum-product algorithm, we refer the reader to the full version [2] of this article. When the factor graph is acyclic, the algorithm converges after a fixed number of iterations. When the factor graph contains cycles, it becomes *loopy belief propagation* and no longer has guaranteed convergence. A frequently used heuristic to stop the BP algorithm in such cases is to terminate after  $t_{max}$  iterations which is a fixed parameter to the algorithm. Typically one chooses  $t_{max}$  in line with the size (i.e. diameter) of the graph. For further details on factor graphs and BP algorithm we refer the interested readers to [7,11].

In our implementation, all variable nodes send their initial distribution along all their connected edges in the first round of the algorithm. Once completed, the factor nodes send their messages, by selecting an adjacent variable node, then collecting all incoming messages (excluding the one from the target variable node) and applying their own 'function' on these messages. They do this for all adjacent variable nodes. Upon termination of the algorithm, the marginal distributions of all sixteen key bytes are computed. This is done by taking the product of each key's initial distribution with all incoming messages to the respective key byte. To judge success of an attack, the keys are ranked according their probability.

#### 2.2 Attack Setup and Implementation Details

The work presented in this paper uses an adaptation of AES FURIOUS (originally written for Atmel's AVR) written in the ARM Thumb assembly language. Our lab setup consists of custom host board with an ARM Cortex-M0 of the LPC series. The board has an on board signal amplifier and filter. We utilise a stable external clock running at 125 MHz. The data is recorded by a PicoScope 2000 Series instrument. We took 150000 traces, of which 120000 were used for template building and 30000 for doing repeat attacks. In any attack the result of the template matching is utilised as the input probability distributions for the (leaky) variable nodes.

Because real trace data implies a fixed device leakage model and a corresponding signal-to-noise ratio (SNR), we also performed two types of simulations with varying SNRs. The first simulation was via using the tool ELMO [10], which emulates the leakage of a Cortex-M0. The emulator was built by profiling a different type of M0, manufactured by ST Micro. Thus we would expect the simulation results (when appropriate levels of Gaussian noise is added) to match our real trace results. We also performed Hamming weight (HW) based simulation, which turned out to give identical results to the ELMO simulations hence we opted to not include them in our tables. In our implementation we set the value of  $t_{max}$  (used by the BP algorithm) to be 50. This value was chosen because it is greater than the diameter of the largest graph G (which has a diameter of 42), and thus gives room for propagation around the loops. For the calculation of first-order success rates (SR) and key ranks, we follow the recommendation of [9] and compute average key ranks over 200 repeat experiments.

# 3 Improving Loopy Belief Propagation

Different variations of the (loopy) BP algorithm are proposed in the literature. We add our own improvements and explain the resulting algorithm in this section.

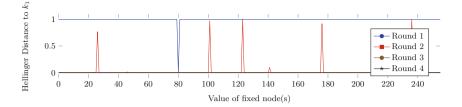

### 3.1 Epsilon Exhaustion

One of the parameters for the Belief Propagation Algorithm is how many iterations to run. This is represented by the value  $t_{max}$ . In this paper we propose an additional termination criterion, which allows the algorithm to terminate early, if certain conditions are met. As the BP algorithm is a message passing algorithm, there may come a point after a number of iterations where the messages being updated have received most of the information in the graph, and will not change significantly. If this is detected over a series of consecutive rounds, we can deduce that the factor graph has reached a stable equilibrium, and we can therefore terminate the algorithm without being at risk of discarding useful information.

We implement this by having two user defined parameters,  $\varepsilon$  and  $\varepsilon_s$ . After each iteration of the BP algorithm, we observe the incoming messages at the sixteen key byte nodes. If the Euclidean distance between the message from the current iteration and the message from the previous iteration is greater than the threshold  $\varepsilon$ , we conclude that the current round did not provide the key bytes with enough new information. If this occurs over  $\varepsilon_s$  consecutive rounds, we conclude that as enough information has propagated, further rounds would not benefit the key bytes, and it is safe to terminate the BP algorithm early.

We used the Euclidean distance metric to measure the difference between two probability distributions after considering other possibilities, see also Sect. 4.1.

## 3.2 Ground Truth Checking

One open problem encountered in template-based DPA style attacks is differentiating a 'good' trace from a 'bad' one, when it is not simply characterised by a large variance. For instance, even a small clock jitter can slightly misalign a trace in relation to the template values, which typically means that template matching gives very poor results. Due to the nature of the Belief Propagation algorithm, we compute the marginal distribution of the key bytes by taking the product of all their incoming messages (Sect. 2.1). If an erroneous trace is computed in an

23

Algorithm 1. BP algorithm with epsilon exhaustion and ground truth check

```

1 function BPA(\mathcal{G}_{aes}, \varepsilon, \varepsilon_s, \varepsilon_g, t_{max}, k^*, i_p)

/* k^*, i_p are the variable nodes corresponding to the key and

plaintext respectively */

Initialize the messages as i.i.d uniform random variables

\mathbf{2}

count := 0

3

foreach t \in \{1, \ldots, t_{max}\} do

4

foreach (i, f) \in \mathcal{E} do

\mathbf{5}

update \nu_{i \to f}^{(t)} with incoming messages

6

7

end

foreach (i, f) \in \mathcal{E} do

8

update \tilde{\nu}_{f \to i}^{(t)} with incoming messages

9

10

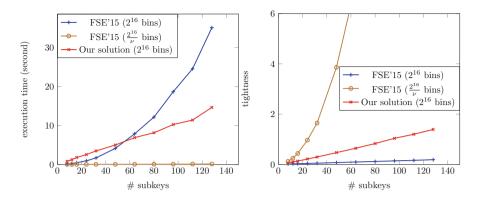

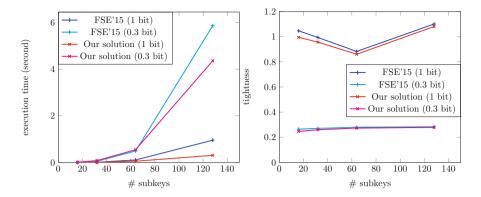

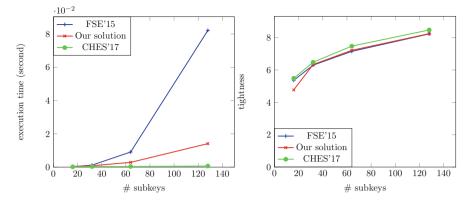

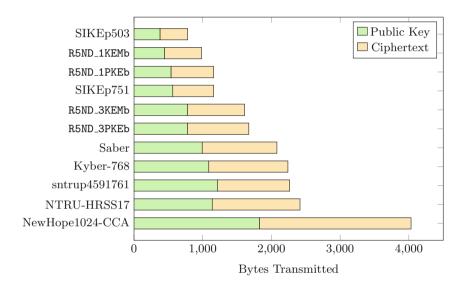

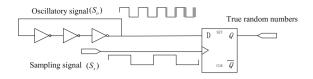

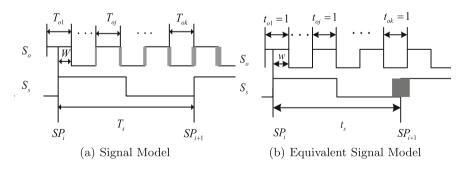

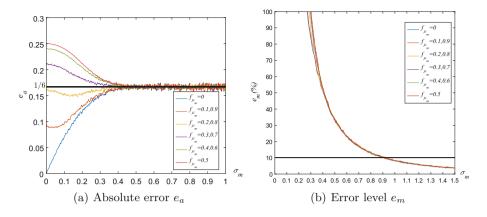

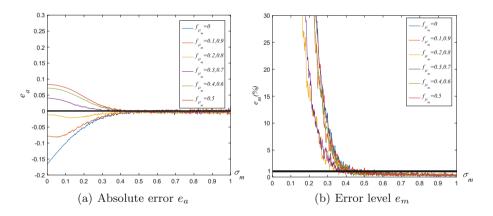

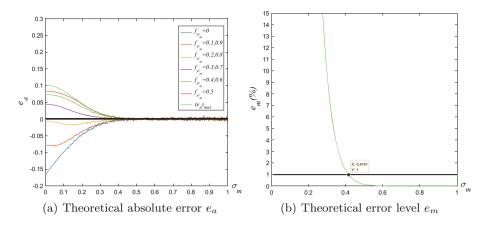

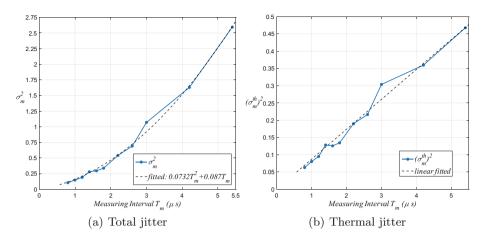

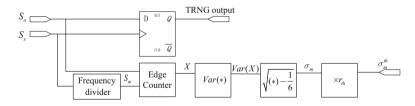

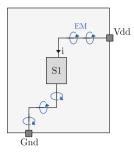

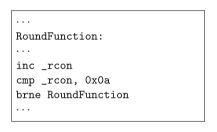

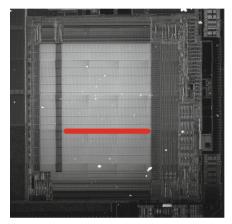

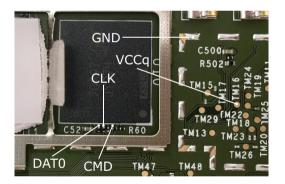

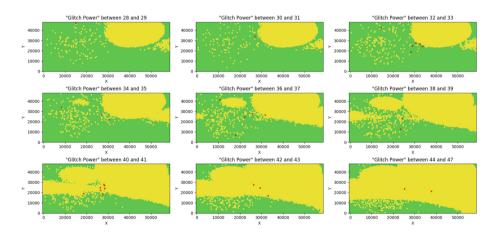

end