# Arya: Nearly Linear-Time Zero-Knowledge Proofs for Correct Program Execution

Jonathan Bootle<sup>(⊠)</sup>, Andrea Cerulli, Jens Groth, Sune Jakobsen, and Mary Maller

University College London, London, UK {jonathan.bootle.14,andrea.cerulli.13,j.groth,s.jakobsen, mary.maller.15}@ucl.ac.uk

**Abstract.** There have been tremendous advances in reducing interaction, communication and verification time in zero-knowledge proofs but it remains an important challenge to make the prover efficient. We construct the first zero-knowledge proof of knowledge for the correct execution of a program on public and private inputs where the prover computation is nearly linear time. This saves a polylogarithmic factor in asymptotic performance compared to current state of the art proof systems.

We use the TinyRAM model to capture general purpose processor computation. An instance consists of a TinyRAM program and public inputs. The witness consists of additional private inputs to the program. The prover can use our proof system to convince the verifier that the program terminates with the intended answer within given time and memory bounds. Our proof system has perfect completeness, statistical special honest verifier zero-knowledge, and computational knowledge soundness assuming linear-time computable collision-resistant hash functions exist. The main advantage of our new proof system is asymptotically efficient prover computation. The prover's running time is only a superconstant factor larger than the program's running time in an apples-to-apples comparison where the prover uses the same TinyRAM model. Our proof system is also efficient on the other performance parameters; the verifier's running time and the communication are sublinear in the execution time of the program and we only use a log-logarithmic number of rounds.

**Keywords:** Zero-knowledge proofs Succinct arguments of knowledge · TinyRAM Ideal linear commitments · Post-quantum security

The research leading to these results has received funding from the European Research Council under the European Union's Seventh Framework Programme (FP/2007-2013)/ERC Grant Agreement n. 307937.

M. Maller—Supported by a scholarship from Microsoft Research.

<sup>©</sup> International Association for Cryptologic Research 2018

T. Peyrin and S. Galbraith (Eds.): ASIACRYPT 2018, LNCS 11272, pp. 595–626, 2018. https://doi.org/10.1007/978-3-030-03326-2\_20

#### 1 Introduction

A zero-knowledge proof system [GMR85] enables a prover to convince a verifier that a statement is true without revealing anything else. We are interested in proving statements of the form  $u \in \mathcal{L}$ , where  $\mathcal{L}$  is a language in NP. A zero-knowledge proof is an interactive protocol between a prover and a verifier, where both hold the same instance u, and the prover also holds a witness w to  $u \in \mathcal{L}$ . The protocol should satisfy three properties:

**Completeness:** A prover holding a witness to  $u \in \mathcal{L}$  can convince the verifier. **Soundness:** A cheating prover cannot convince the verifier when  $u \notin \mathcal{L}$ . **Zero-knowledge:** The interaction only shows the statement  $u \in \mathcal{L}$  is true. It reveals nothing else, in particular it does not disclose anything of the witness.

Zero-knowledge proofs have numerous applications and are for instance used in constructions of public-key encryption schemes secure against chosen ciphertext attack, digital signatures, voting systems, auction systems, e-cash, secure multi-party computation, and verifiable outsourced computation. The zero-knowledge proofs impact the performance of all these applications, and it is therefore important for them to be as efficient as possible.

There are many zero-knowledge proofs for dealing with arithmetic or boolean circuit satisfiability. However, in applications usually the type of statements we want to prove is that a protocol participant is following the protocol honestly; whatever that protocol may be. This means we want to express statements relating to program execution such as "running program P specified by the protocol on public input x and private input y returns the output z." In principle such a statement can be reduced to circuit satisfiability but the cost of the NP-reduction incurs a prohibitive cost. In this paper, we therefore focus on the important question of getting zero-knowledge proofs for statements relating directly to program execution.

Performance can be measured on a number of parameters including the prover's running time, the verifier's running time, the number of transmitted bits and the number of rounds the prover and verifier interact. Current state of the art zero-knowledge proofs get very good performance on verification time, communication and round complexity, which makes the prover's running time the crucial bottleneck. Indeed, since the other costs are so low, we would happily increase them for even modest savings on the proving time since this is the barrier that make some applications such as verifiable outsourced computation currently unviable. The research challenge we focus on is therefore to get prover-efficient zero-knowledge proofs for correct program execution.

#### 1.1 Our Contribution

We use the TinyRAM model [BCG+13,BSCG+13] for computation. TinyRAM specifies a random access machine with a small instruction set working on W-bit words and addresses. The specification of TinyRAM considers a Harvard-architecture processor, which means that the program being executed is stored

separately from the data being processed and does not change during execution.<sup>1</sup> Experimental results [BCG+13] show that programs written in C can be compiled efficiently into TinyRAM programs and only have a modest constant overhead compared to optimized compilation to machine code on a modern processor.

In our proof system, an instance consists of a TinyRAM program and public data given to the program, and a witness is private data given as input to the program. The statement is the claim that the TinyRAM program P running on given public and private data will terminate with answer 0 within specific time and memory bounds. When measuring performance we think of the prover and verifier as being TinyRAM programs with the same word size<sup>2</sup>.

Our main contribution is an interactive proof system for correct TinyRAM computation, which has perfect completeness, statistical zero-knowledge, and computational knowledge soundness based on collision-resistant hash functions. Knowledge soundness means that not only do we have soundness and it is infeasible to prove a false statement, but it is also a proof of knowledge such that given access to a successful prover it is possible to extract a witness. For maximal asymptotic efficiency we may use linear-time computable hash functions, which yields the performance given in Fig. 1.

Our proof system is highly efficient for computationally intensive programs where the execution time dominates other parameters (see Sect. 6 for a detailed discussion of parameter choices). For a statement about the execution of a TinyRAM program of length L, running with time bound T and memory bound M, the prover runs in  $\mathcal{O}(\alpha T)$  steps<sup>3</sup> for an arbitrarily small superconstant function  $\alpha(\lambda) = \omega(1)$ . The proof system is also efficient on other performance parameters: the verifier running time and the communication grows roughly with the square-root of the execution time<sup>4</sup> and we have log-logarithmic round complexity. Figure 1 gives an efficiency comparison with a state of the art zk-SNARK [BCTV14b] for verifying correct program execution on TinyRAM.

<sup>&</sup>lt;sup>1</sup> TinyRAM can with minor changes also be adapted to a von Neumann architecture where program instructions are fetched from memory [BCTV14b]. The performance of our proof systems adapted to a von Neumann architecture would remain the same up to a constant factor.

<sup>&</sup>lt;sup>2</sup> We stress the choice of comparing the prover and verifier to program execution on the same platform. We do this to get an apples-to-apples comparison; there are many zero-knowledge proofs that are "linear time" because they use different metrics for statement evaluation and the prover time, for instance that the cost of validating the statement given the witness is measured in field multiplications and the prover computation is measured in exponentiations.

<sup>&</sup>lt;sup>3</sup> The big-O notation hides big constants and we do not recommend implementing the proof system as it is; our contribution is to make significant *asymptotic* gains compared to state-of-the-art zero-knowledge proofs by demonstrating that the prover's computation can be nearly linear.

<sup>&</sup>lt;sup>4</sup> Disregarding the SHVZK property for a moment, this is also the first proof system for general purpose computation that has both nearly linear computation for the prover and sublinear communication.

Further discussion of other proof systems that can verify correct TinyRAM or other types of program execution can be found in Sect. 1.3. The best of these achieve similar asymptotic prover efficiency as [BCTV14b].

| Work      | Prover                  | Verifier                                           | Communication                                | Rounds                     | Assumption |

|-----------|-------------------------|----------------------------------------------------|----------------------------------------------|----------------------------|------------|

| [BCTV14b] | $\Omega(T\log^2 T)$     | $\omega(L+ v )$                                    | $\omega(1)$                                  | 1                          | KoE        |

| This work | $\mathcal{O}(\alpha T)$ | $\operatorname{poly}(\lambda)(\sqrt{T} + L +  v )$ | $\operatorname{poly}(\lambda)(\sqrt{T} + L)$ | $\mathcal{O}(\log \log T)$ | LT-CRHF    |

Fig. 1. Efficiency comparisons between our arguments and the most efficient zero-knowledge argument for the correct execution of TinyRAM programs, both at security level  $2^{-\omega(\log \lambda)}$ . Computation is measured in TinyRAM steps and communication in words of length  $W = \Theta(\log \lambda)$  with  $\lambda$  the security parameter. KoE stands for knowledge of exponent type assumption in pairing-based groups and LT-CRHF stands for linear-time collision resistant hash function. It is worth noting KoE assumptions do not resist quantum computers while a LT-CRHF may be quantum resistant.

Remarks. Our proof system assumes some public parameters to be set up that include a description of a finite field, an error-correcting code, and a collision-resistant hash function. The size of the public parameters is just  $\operatorname{poly}(\lambda)(L+M+\sqrt{T})$  bits which can be computed from a small uniformly random string in  $\operatorname{poly}(\lambda)(L+M+\sqrt{T})$  TinyRAM steps. This means the public parameters have little effect on the overall efficiency of the proof system. Moreover, there are variants of the parameters where it is efficiently verifiable the public parameters have the correct structure. This means the prover does not need to trust the parameters to get special honest verifier zero-knowledge, so they can be chosen by the verifier making our proof systems work in the plain model without setup. We let the public parameter be generated by a separate setup though because they are independent of the instance and can be used over many separate proofs.

We did not optimize communication and verification time to go below  $\sqrt{T}$  but if needed it is possible to compose our proof system with a verifier-efficient proof system and get verification time that grows logarithmically in T. This is done by letting the prover send linear-time computable hashes of her messages to the verifier instead of the full messages. Since our proof system is public coin the prover knows after this interaction exactly how the verifier in our proof system ought to run if given the messages in our proof system. She can therefore give a verifier-efficient proof of knowledge that she knows pre-images to the hashes that would make the verifier in our proof system accept. We outline this procedure in the full paper [BCG+18].

#### 1.2 New Techniques

Ben-Sasson et al. [BCG+13,BCTV14b] offer proof systems for correct TinyRAM program execution where the prover commits to a time-sorted execution trace as well as an address-sorted memory trace. They embed words, addresses and

flags that describe the TinyRAM state at a given time into field elements. The correct transition in the execution trace between the state at time t and the state at time t+1 can then be checked by an arithmetic circuit, the correct writing and reading of memory at a particular address in the memory trace can be checked by another arithmetic circuit, and finally the consistency of memory values in the two traces can be checked by a third arithmetic circuit that embeds a permutation network. Importantly, in these proofs the state transitions can be proved with the same arithmetic circuits in each step so many of the proofs can be batched together at low average cost.

Combining their approach with the recent linear-time proofs for arithmetic circuit satisfiability by Bootle et al. [BCG+17] it would be possible to get a zero-knowledge proof system with sublinear communication and efficient verification. The prover time, however, would incur at least a logarithmic overhead compared to the time to execute the TinyRAM program. First, the use of an arithmetic circuit that embeds a permutation network to check consistency between execution and memory traces requires a logarithmic number of linear-size layers to describe an arbitrary permutation which translates into a logarithmic overhead when generating the proof. Second, TinyRAM allows both arithmetic operations such as addition and multiplication of words, and logical operations such as bitwise XOR, AND and OR. To verify logical operations they decompose words into single bits that are handled individually. Bit-decomposition makes it easy to implement the logical operations, but causes an overhead when embedding bits into full size field elements. From a technical perspective our main contribution is to overcome these two obstacles.

To reduce the time required to prove the execution trace is consistent with the memory usage we do not embed a permutation network into an arithmetic circuit. Instead we relate memory consistency to the existence of a permutation that maps one memory access in the execution trace to the next access of the same memory address in the execution trace. Neff [Nef01] proposed permutation proofs in the context of shuffle proofs used in mix-nets. Follow-up works [Gro10b, GI08] have improved efficiency of such proofs with Bayer and Groth [BG12] giving a shuffle argument in the discrete logarithm setting where the prover uses a linear number of exponentiations and communication is sublinear. These shuffle proofs are proposed for the discrete logarithm setting and we do not want to pay the cost of computing exponentiations. The core of the shuffle proofs can be formulated abstractly using homomorphic commitments to vectors though. Since the proofs by Bootle et al. [BCG+17] also rely on an idealization of homomorphic commitments to vectors the ideas are compatible and we get permutation proofs that cost a linear number of field operations.

To remove the overhead of bit-decomposition we invent a less costly decomposition. While additions and multiplications are manageable using a natural embedding of words into field elements, such a representation is not well suited to logical operations though. However, instead of decomposing words into individual bits, we decompose them into interleaved odd-position bits and even-position bits. A nibble  $(a_3, a_2, a_1, a_0)$  can for instance be decomposed into  $(a_3, 0, a_1, 0) + (0, a_2, 0, a_0)$ . The key point of this idea is that adding two interleaved even bit

nibbles yields  $(0, a_2, 0, a_0) + (0, b_2, 0, b_0) = (a_2 \wedge b_2, a_2 \oplus b_2, a_0 \wedge b_0, a_0 \oplus b_0)$ . So using another decomposition into odd-position and even-position bits we can now extract the XORs and the ANDs. Using this core idea, it is possible to represent all logical operations using field additions together with decomposition into odd and even-position bits. This reduces the verification of logical operations to verifying correct decomposition into odd and even bits. This decomposition and its use are described in the full paper [BCG+18].

To enable decomposition proofs into odd and even-position bits, we develop a new lookup proof that makes it possible to check that a field element belongs to a table of permitted values. By creating a lookup table of all words with even-position bits, we make it possible to verify such decompositions. Lookup proofs not only enable decomposition into odd and even-position bits but also turn out to have many other uses such as demonstrating that a field element represents a correct program instruction, or that a field element represents a valid word within the range  $\{0, \ldots, 2^W - 1\}$ .

Combining arithmetic circuits, permutations and table lookups we get a set of conditions for a TinyRAM execution being correct. The program execution of T steps on the TinyRAM machine can in our system be encoded as  $\mathcal{O}(T)$  field elements that satisfy the conditions. Using prime order fields of size  $2^{\mathcal{O}(W)}$  would make it possible to represent these field elements as  $\mathcal{O}(1)$  words each. However, the soundness of our proof systems depends on the field size and to get negligible soundness error we choose a larger field to get a superconstant ratio  $e = \frac{\log |\mathbb{F}|}{W}$ . This factors into the efficiency of our proof system giving a prover runtime of  $\mathcal{O}(\alpha T)$  TinyRAM steps for an instance requiring time T, where  $\alpha$  is a superconstant function which specifies how many steps it takes to compute a field operation, i.e.,  $\alpha = \mathcal{O}(e^2)$ .

Having the inner core of conditions in place: arithmetic circuits for instruction executions, permutations for memory consistency, and look-ups for word decompositions we now deploy the framework of Bootle et al. [BCG+17] to get a zero-knowledge proof system. They use error-correcting codes and linear-time collision-resistant hash functions to give proof systems for arithmetic circuit satisfiability, while we will use their techniques to prove our conditions on the execution trace are satisfied. Their proof system for arithmetic circuit satisfiability requires the prover to use a linear number of field multiplications and the verifier to use a linear number of field additions. However, we can actually get sublinear verification when the program and the input is smaller than the execution time. Technically, the performance difference stems from the type of permutation proof that they use for verifying the correct wiring of the circuit and that we use for memory consistency in the execution trace. In their use, the permutation needs to be linked to the publicly known wiring of the arithmetic circuit and in order for the verifier to check the wiring is correct he must read the entire circuit. We on the other hand do not disclose the memory accesses in the execution trace to the verifier, indeed to get zero-knowledge it is essential the memory accesses remain secret. We therefore need a hidden permutation proof and such proofs can have sublinear verification time.

#### 1.3 Related Work

Interaction. Interaction is measured by the number of rounds the prover and verifier exchange messages. Feige and Shamir [FS90] showed that constant round argument systems exist, and Blum, Feldman and Micali [BFM88] showed that if the prover and verifier have access to an honestly generated common reference string it is possible to have non-interactive zero-knowledge proofs where the prover sends a single message to the verifier.

Communication. A series of works [KR08,IKOS09,Gen09,GGI+15] have constructed proof systems where the number of transmitted bits is proportional to the witness size. It is unlikely that sublinear communication is possible in proof systems with statistical soundness but Kilian [Kil92] constructed an argument system, a computationally sound proof system, with polylogarithmic communication complexity. Kilian's zero-knowledge argument relies on probabilistically checkable proofs [AS98], which are still complex for practical use, but the invention of interactive oracle proofs [BCS16] have made this type of proof system a realistic option. Recent work by Ben-Sasson et al. [BSBTHR18] presents a new PCP-based argument system, known as STARKs, which also has polylogarithmic communication costs, and is optimized for better practicality. Ishai et al. [IKO07] give laconic arguments where the prover's communication is minimal. Groth [Gro10a], working in the common reference string model and using strong assumptions, gave a pairing-based non-interactive zero-knowledge argument consisting of a constant number of group elements. Follow-up works on succinct non-interactive arguments of knowledge (SNARKs) have shown that it is possible to have both a modest size common reference string and proofs as small as 3 group elements [BCCT12, GGPR13, PHGR16, BCCT13, Gro16].

**Verifier Computation.** In general the verifier has to read the entire instance since even a single deviating bit may render the statement  $u \in \mathcal{L}$  false. However, in many cases an instance can be represented more compactly than the witness and the instance may be small compared to the computational effort it takes to verify a witness for the instance. In these cases it is possible to get sublinear verification time compared to the time it takes to check the relation defining the language  $\mathcal{L}$ . This is for instance the case for the SNARKs mentioned above, where the verification time only depends on the size of the instance but not the complexity of the relation.

**Prover Computation.** Given the success in reducing interaction, communication and verification time, the important remaining challenge is to get good efficiency for the prover.

Boolean and Arithmetic Circuits. Many classic zero-knowledge proofs rely on cyclic groups and have applications in digital signatures, encryption schemes, etc. The techniques first suggested by Schnorr [Sch91] can be generalized

to NP-completel languages such as boolean and arithmetic circuit satisfiability [CD, Gro09, BCC+16]. In these proofs and arguments the prover uses  $\mathcal{O}(N)$  group exponentiations, where N is the number of gates in the circuit. For the discrete logarithm assumption to hold, the groups must have superpolynomial size in the security parameter though, so exponentiations incur a significant overhead compared to direct evaluation of the witness in the circuit. The SNARKs mentioned earlier also rely on cyclic groups and likewise require the prover to do  $\mathcal{O}(N)$  exponentiations. Recently, Bootle et al. [BCG+17] used the structure of [Gro09] to give constant overhead zero-knowledge proofs for arithmetic circuit satisfiability, where the prover uses  $\mathcal{O}(N)$  field multiplications, relying on error-correcting codes and efficient collision-resistant hash functions instead of cyclic groups. STARKs [BSBTHR18] achieve slightly worse, quasilinear prover computation but have lower asymptotic verification costs.

An alternative to these techniques is to use the "MPC in the head" paradigm by Ishai et al. [IKOS09]. Relying on efficient MPC techniques, Damgård, Ishai and Krøigaard gave zero-knowledge arguments with little communication and a prover complexity of polylog( $\lambda$ )N. Instead of focusing on theoretical performance, ZKBoo [GMO16] and its subsequent optimisation ZKB++ [CDG+17] are practical implementations of a "3PC in the head" style zero-knowledge proof for boolean circuit satisfiability. Communication grows linearly in the circuit size in both proofs, and a superlogarithmic number of repetitions is required to make the soundness error negligible, but the speed of the symmetric key primitives makes practical performance good. Ligero [AHIV17] provides another implementation using techniques related to [BCG+17]. It has excellent practical performance but asymptotically it is not as efficient as [BCG+17] due to the use of more expensive error-correcting codes. Another alternative also inspired by the MPC world is to use garbled circuits to construct zero-knowledge arguments for boolean circuits [BP12, JKO13, FNO15]. The proofs grow linearly in the size of the circuit and there is a polylogarithmic overhead for the prover and verifier due to the cryptographic operations but implementations are practical [JKO13].

There are several proof systems for efficient verification of outsourced computation [GKR08, CMT12, Tha13, WHG+16]. While this line of works mostly focus on verifying deterministic computation and does not require zero-knowledge, recent works add in cryptographic techniques to obtain zero-knowledge [ZGK+17, WJB+17, WTas+17]. Hyrax [WTas+17] offers an implementation with good concrete performance. It has sublinear communication and verification, while the prover computation is dominated by  $\mathcal{O}(dN+S\log S)$  field operations for a depth d and width S circuit when the witness is small compared to the circuit size. If in addition the circuit can be parallelized into many identical sub-computations the prover cost can be further reduced to O(dN) field operations. The system vSQL [ZGK+17] is tailored towards verifying database queries and as in this work it avoids the use of permutation networks using permutation proofs based on invariance of roots in polynomials as first suggested by Neff [Nef01].

Correct Program Execution. In practice, most computation does not resemble circuit evaluation but is instead done by computer programs processing one instruction at a time. There has been a sustained effort to construct efficient zero-knowledge proofs that support real-life computation, i.e., proving statements of the form "when executing program P on public input x and private input y we get the output z." In the context of SNARKs there are already several systems for proving correct execution of programs written in C [PHGR16,BFR+13,BCG+13,WSR+15]. These system generally involve a front-end which compiles the program into an arithmetic circuit which is then fed into a cryptographic back-end. Much work has been dedicated to improving both sides and achieving different trade-offs between efficiency and expressiveness of the computation.

When we want to reason theoretically about zero-knowledge proofs for correct program execution, it is useful to abstract program execution as a random-access machine that in each instruction can address an arbitrary location in memory and do integer operations on it. For closer resemblance to real-life computation, we can bound the integers to a specific word size and specify a more general set of operations the random-access machine can execute. TinyRAM [BSCG+13, BCG+13] is a prominent example of a computational model bridging the gap between theory and real-word computation. It comes with a compiler from C to TinyRAM code and underpins several implementations of zero-knowledge proofs for correct program execution [BCG+13,BCTV14b,BCTV14a,CTV15, BBC+17] where the prover time is  $\Omega(T \log^2 \lambda)$  for a program execution that takes time T. Similar efficiency is also achieved, asymptotically, by other proof systems that can compile (restricted) C programs and prove correct execution such as Pinocchio [PHGR16], Pantry [BFR+13] and Buffet [WSR+15]. Our work reduces the prover's overhead from  $\Omega(\log^2 \lambda)$  to an arbitrary superconstant  $\alpha =$  $\omega(1)$  and is therefore an important step towards optimal prover complexity.

Concurrent Work. Zhang et al. [ZGK+18] have concurrently with our work developed and implemented a scheme for verifying RAM computations. Like us and [ZGK+17], they avoid the use of permutation networks by using permutation proofs based on polynomial invariance by Neff [Nef01]. The idea underlying their technique for proving the correct fetch of an operation is related to the idea underpinning our look-up proofs. There are significant differences between the techniques used in our works; e.g. they rely on techniques from [CMT12] for instantiating proofs where we use techniques based on ideal linear commitments [BCG+17]. The proofs in [ZGK+18] are not zero-knowledge since they leak the number of times each type of instruction is executed, while our proofs are zero-knowledge. In terms of prover efficiency, [ZGK+18] focuses on concrete efficiency and yields impressive concrete performance. Asymptotically speaking, however, we are a polylogarithmic factor more efficient. This may require some explanation because they claim linear complexity for the prover. The reason is that they treat the prover as a TinyRAM machine with logarithmic word size in their performance measurement. Looking under the hood, we see that they use bit-decomposition to handle logical operations, which is constant overhead when you fix a particular word size (e.g. 32 bits) but asymptotically the cost of this is logarithmic since it is linear in the word size. Also, they base commitments on cyclic groups and the use of exponentiations incurs a superlogarithmic overhead for the prover when implemented in TinyRAM.

Setup and Assumptions. Many proof systems, such as SNARKs, require a large and complex common reference string in order to run. The common reference string must be generated correctly, or the security of the proof system is at stake. This leads to concerns over parameter subversion, and efficiency, since the more complex the common reference string, the more costly it is to ensure that it was generated correctly. Recently, alternatives have been investigated. Hyrax [WTas+17] relies on the discrete logarithm assumption, and Ligero [AHIV17] and STARKs [BSBTHR18] rely on collision-resistant hash functions. Our scheme relies only on collision-resistant hash functions for soundness, and pseudorandom generators in order to achieve full zero-knowledge, which means that the setup information required is comparable to existing works, like STARKs, which focus on transparency.

Our proof system benefits from simple setup ingredients, nearly linear prover costs, and sublinear, hence, scalable communication and verification costs, and therefore enjoys many of the same desirable properties as STARKs [BSBTHR18].

In addition, although we do not know how to prove that our scheme is secure in any quantum security model, it is based on post-quantum assumptions and may offer some security against quantum adversaries, since it is not known how to efficiently attack collision-resistant hash functions and pseudorandom generators using quantum algorithms. Note that there are general proof systems, such as ZKB++ [CDG+17], which do have quantum proofs of security, but are asymptotically less efficient as previously discussed.

#### 2 Preliminaries

#### 2.1 Notation

We write  $y \leftarrow A(x)$  for an algorithm returning y on input x. When the algorithm is randomized, we write  $y \leftarrow A(x;r)$  to explicitly refer to the random coins r picked by the algorithm. We use a security parameter  $\lambda$  to indicate the desired level of security. The higher the security parameter, the smaller the risk of an adversary compromising security should be. For functions  $f, g : \mathbb{N} \to [0, 1]$ , we write  $f(\lambda) \approx g(\lambda)$  if  $|f(\lambda) - g(\lambda)| = \frac{1}{\lambda^{\omega(1)}}$ . We say a function f is overwhelming if  $f(\lambda) \approx 1$  and that it is negligible if  $f(\lambda) \approx 0$ . In general we want the adversary's chance of breaking our proof systems to be negligible in  $\lambda$ . As a minimum requirement for an algorithm or adversary to be efficient it has to run in polynomial time in the security parameter. We abbreviate probabilistic (deterministic) polynomial time in the security parameter PPT (DPT). For a positive integer n, n denotes the set  $\{1, \ldots, n\}$ . We use bold letters such as n for row vectors over a finite field n.

#### 2.2 Proofs of Knowledge

We follow [BCG+17] in defining proofs of knowledge over a communication channel and their specification of the ideal linear commitment channel and the standard channel. A *proof system* is defined by stateful PPT algorithms  $(\mathcal{K}, \mathcal{P}, \mathcal{V})$ . The setup generator  $\mathcal{K}$  is only run once to provide public parameters pp that will be used by the prover  $\mathcal{P}$  and verifier  $\mathcal{V}$ . We will in our security definitions just assume  $\mathcal{K}$  is honest, which is reasonable since in our constructions the public parameters are publicly verifiable and could even be generated by the verifier.

The prover and verifier communicate with each other through a communication channel  $\stackrel{\text{chan}}{\longleftrightarrow}$ . When  $\mathcal{P}$  and  $\mathcal{V}$  interact on inputs s and t through a channel  $\stackrel{\text{chan}}{\longleftrightarrow}$  we let  $\text{view}_{\mathcal{V}} \leftarrow \langle \mathcal{P}(s) \stackrel{\text{chan}}{\longleftrightarrow} \mathcal{V}(t) \rangle$  be the view of the verifier in the execution, i.e., all inputs he gets including random coins, and we let  $\text{trans}_{\mathcal{P}} \leftarrow \langle \mathcal{P}(s) \stackrel{\text{chan}}{\longleftrightarrow} \mathcal{V}(t) \rangle$  denote the transcript of the communication between prover and channel. The protocol ends with the verifier accepting or rejecting the proof. We write  $\langle \mathcal{P}(s) \stackrel{\text{chan}}{\longleftrightarrow} \mathcal{V}(t) \rangle = b$  depending on whether he accepts (b=1) or rejects (b=0).

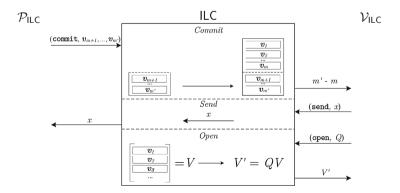

Fig. 2. Description of the ILC channel.

We say a proof system is *public coin* if the verifier's messages to the communication channel are chosen uniformly at random and independently of the actions of the prover, i.e., the verifier's messages to the prover correspond to the verifier's randomness  $\rho$ . All our proof systems will be public coin. In a proof system over the ILC channel, sequences of **commit, send** and **open** queries can alternate arbitrarily. However, since our proof systems are public coin we can without loss of generality assume the verifier will only make one big **open** query at the end of the protocol and then decide whether to accept or reject.

Let  $\mathcal{R}$  be an efficiently decidable relation of tuples (pp, u, w). We can define a matching language  $\mathcal{L} = \{(pp, u) | \exists w : (pp, u, w) \in \mathcal{R}\}$ . We refer to u as the *instance* and w as the *witness* to  $(pp, u) \in \mathcal{L}$ . The public parameter pp will specify the security parameter  $\lambda$ , perhaps implicitly through its length, and may also contain other parameters used for specifying the relation. Typically, pp will also contain parameters that do not influence membership of  $\mathcal{R}$  but may aid the prover and verifier, for instance the field and vector size in the ILC channel.

The protocol  $(\mathcal{K}, \mathcal{P}, \mathcal{V})$  is called a *proof of knowledge* over a communication channel  $\stackrel{\text{chan}}{\longleftrightarrow}$  for a relation  $\mathcal{R}$  if it has perfect completeness and computational knowledge soundness as defined below.

**Definition 1 (Perfect Completeness).** A proof system is perfectly complete if for all PPT adversaries A

$$\Pr\left[\begin{array}{c} pp \leftarrow \mathcal{K}(1^{\lambda}); (u,w) \leftarrow \mathcal{A}(pp): \\ (pp,u,w) \notin \mathcal{R} \ \lor \ \langle \mathcal{P}(pp,u,w) \stackrel{chan}{\longleftrightarrow} \mathcal{V}(pp,u) \rangle = 1 \end{array}\right] = 1.$$

**Definition 2 (Knowledge soundness).** A public-coin proof system has computational (strong black-box) knowledge soundness if for all  $DPTP^*$  there exists an expected PPT extractor  $\mathcal{E}$  such that for all PPT adversaries  $\mathcal{A}$

$$\Pr\left[pp \leftarrow \mathcal{K}(1^{\lambda}); (u, s) \leftarrow \mathcal{A}(pp); w \leftarrow \mathcal{E}^{\langle \mathcal{P}^*(s) \stackrel{chan}{\longleftrightarrow} \mathcal{V}(pp, u) \rangle}(pp, u) : \right] \approx 0.$$

Here the oracle  $\langle \mathcal{P}^*(s) \overset{chan}{\longleftrightarrow} \mathcal{V}(pp,u) \rangle$  runs a full protocol execution and if the proof is successful it returns the transcript  $\mathsf{trans}_{\mathcal{P}}$  of the prover's communication with the channel. The extractor  $\mathcal{E}$  can ask the oracle to rewind the proof to any point in a previous transcript and execute the proof again from this point on with fresh public-coin challenges from the verifier. We let  $b \in \{0,1\}$  be the verifier's output in the first oracle execution, i.e., whether it accepts or not, and we think of s as the state of the prover. The definition can then be paraphrased as saying that if the prover in state s makes a convincing proof, then  $\mathcal{E}$  can extract a witness.

If the definition holds also for unbounded  $\mathcal{P}^*$  and  $\mathcal{A}$  we say the proof has statistical knowledge soundness.

If the definition holds for a non-rewinding extractor, i.e.,  $\mathcal{E}$  only requires a single transcript of the prover's communication with the channel, we say the proof system has knowledge soundness with straight-line extraction.

We will construct public-coin proofs of knowledge that have special honest-verifier zero-knowledge. This means that if the verifier's challenges are known in advance then it is possible to simulate the verifier's view without knowing a witness. In our definition, the simulator works even for verifiers who may use adversarial biased coins in choosing their challenges as long as they honestly follow the specification of the protocol.

Definition 3 (Special Honest-Verifier Zero-Knowledge). A public-coin proof of knowledge is computationally special honest-verifier zero-knowledge (SHVZK) if there exists a PPT simulator S such that for all stateful interactive PPT adversaries A that output randomness  $\rho$  for the verifier, and (u, w) such that  $(pp, u, w) \in R$ ,

$$\begin{split} & \Pr\left[ \begin{array}{c} pp \leftarrow \mathcal{K}(1^{\lambda}); (u, w, \rho) \leftarrow \mathcal{A}(pp); \\ \operatorname{view}_{\mathcal{V}} \leftarrow \langle \mathcal{P}(pp, u, w) \overset{chan}{\longleftrightarrow} \mathcal{V}(pp, u; \rho) \rangle : \mathcal{A}(\operatorname{view}_{\mathcal{V}}) = 1 \end{array} \right] \\ & \approx \Pr\left[ pp \leftarrow \mathcal{K}(1^{\lambda}); (u, w, \rho) \leftarrow \mathcal{A}(pp); \operatorname{view}_{\mathcal{V}} \leftarrow \mathcal{S}(pp, u, \rho) : \mathcal{A}(\operatorname{view}_{\mathcal{V}}) = 1 \right]. \end{split}$$

We say the proof is statistically SHVZK if the definition holds also against unbounded adversaries, and we say the proof is perfectly SHVZK if the probabilities are exactly equal.

#### 2.3 TinyRAM

TinyRAM is a random-access machine model operating on W-bit words and using K registers. We now describe the key features of TinyRAM but refer the reader to the specification [BSCG+13] for full details. A state of the TinyRAM machine consists of a program P (list of L instructions), a program counter pc (word), K registers  $reg_0, \ldots, reg_{K-1}$  (words), a condition flag flag (bit), and M words of memory with addresses  $0, \ldots, M-1$ .

The TinyRAM specification includes two read-only tapes to retrieve its inputs but with little loss of efficiency we may assume the program starts by reading the tapes into memory<sup>5</sup> We will therefore skip the reading phase and assume the memory is initialized with the inputs (and 0 for the remaining words). Also, we will assume on initialization that pc, the registers and flag are all set to 0.

The program consists of a sequence of L instructions that include bit-wise logical operations, arithmetic operations, shifts, comparisons, jumps, and storing and loading data in memory. The program terminates by using a special command **answer** that returns a word. A description of the allowed operations is given in Table 1. We consider the program to have succeeded if it answers 0, otherwise we consider the answer to be a failure code.

We write  $\operatorname{reg}_i$  and  $\operatorname{r}_i$  when referring to register i and to its content, respectively. We write A to refer to either a register or an immediate value specified in a program instruction and write A for the value stored therein. Depending on the

<sup>&</sup>lt;sup>5</sup> The specification [BSCG+13] calls a program *proper* if it first reads all inputs into memory and provides a 7-line TinyRAM program that does this in  $\sim 5M$  steps.

instruction a word a may be interpreted as an unsigned value in  $\{0,\ldots,2^W-1\}$  or as a signed value in  $\{-2^{W-1},\ldots,2^{W-1}-1\}$ . Signed values are in two's complement, so given a word  $\mathbf{a}=(a_{w-1},\ldots,a_0)\in\{0,1\}^W$  the bit  $a_{W-1}$  is the sign and the signed value is  $-2^W+\mathbf{a}$  if  $a_{W-1}=1$  and  $\mathbf{a}$  if  $a_{W-1}=0$ . We distinguish operations over signed values by using subscript s, e.g.  $\mathbf{a}\times_s\mathbf{b}$  and  $\mathbf{a}\geq_s\mathbf{b}$  are used to denote product and comparison over the signed values.

Correct Program Execution. It is often important to check that a protocol participant supposedly running program P on public input x and private input w provides the correct output z. Without loss of generality, we can formulate the verification as an extended program that takes public input v = (x, z)and answers 0 if and only if z is the output of the computation. We therefore formulate correct program execution as the program just answering 0.

We now give a relation that captures correct TinyRAM program execution. An instance is of the form u = (P, v, T, M), where P is a TinyRAM program, v is a list of words given as input to the program, T is a time bound, and M is the size of the memory. A witness w is another list of words. We assume without loss of generality that the witness is appended by 0's, such that |v| + |w| = M and the program starts with the memory being initialized to these words.

The statement we want to prove is that the program P terminates in T steps using M words of memory on the public input v and private input w with the instruction **answer** 0. We therefore define

$$\mathcal{R}_{\mathsf{TinyRAM}} = \left\{ \begin{array}{l} (pp, u, w) = ((W, K, *), (P, v, T, M), w) \mid \\ P \text{ is a TinyRAM program with $W$-bit words, $K$ registers,} \\ \text{and $M$ words of addressable memory, which on inputs $v$ and $w$ terminates in $T$ steps with the instruction $\mathbf{answer}$ 0. \\ \end{array} \right.$$

Our main interest is to prove correct execution of programs that require heavy computation so we will throughout the article assume the number of steps outweigh the other parameters, i.e., T > L + M, where L is the number of instructions in the program.

# 3 Arithmetization of Correct Program Execution

As a first step towards the realization of proofs for the correct execution of TinyRAM programs we translate  $\mathcal{R}_{\mathsf{TinyRAM}}$  into a more amenable relation involving elements in a finite field. Given a TinyRAM machine with word-size W and a finite field  $\mathbb{F}$ , we can in a natural way embed words into field elements by encoding a word  $a \in \{0, \dots, 2^W - 1\}$  as the field element  $a \cdot 1_{\mathbb{F}} = 1_{\mathbb{F}} + \dots + 1_{\mathbb{F}}$  (a times). We will use fields of characteristic  $p > 2^{2W} - 2^{W-1}$  because then sums and products of words are less than p and we avoid overflow in the field operations we apply to the embedded words.

We will encode the program, memory and states of a TinyRAM program as tuples of field elements. We then introduce a new relation  $\mathcal{R}_{\mathsf{TinyRAM}}^{\mathsf{field}}$  consisting of a set of arithmetic constraints these encodings should satisfy to guarantee

the correct program execution. The relation will take instances u = (P, v, T, M), and witnesses w consisting of the encodings as well as a set of auxiliary field elements.

In this section we specify instructions supported by TinyRAM machines and the structure of the witness w and how the relation of correct program execution decomposes into simpler sub-relations. It will be the case that the encoding of the witness can be done alongside an execution of the program in  $\mathcal{O}(L+M+T)$  field operations.

Table 1 described the supported operations in TinyRAM. Each line in the program consists of one of these instructions in and up to three operands, e.g.  $\operatorname{add} \operatorname{reg}_i \operatorname{reg}_j A$ . The first operand,  $\operatorname{reg}_i$ , usually points to the register storing the result of the operation,  $\operatorname{add}$ , computed on the words specified by the next two operands,  $\operatorname{reg}_j$ , A. The last operand A indicates an immediate value that could be either used directly in the operation or to point to the content of another register. We refer to the value to be used in the operation generically as A, stressing that the selection between either the immediate value or a register value can be handled by using the appropriate selection vector.

Formatting the Witness. Given a correct program execution we encode program, memory and states of the TinyRAM machine as field elements and arrange them in a number of tables as pictured in Table 2. The execution table Exe, contains the field elements encoding of the states of the TinyRAM machine. It consists of T rows, where row t describes the state at the beginning of step t. A row includes field elements that encode the time t, the program counter  $\mathsf{pc}_t$ , the instruction  $\mathsf{inst}_{\mathsf{pc}_t}$  corresponding to  $\mathsf{pc}_t$ , an immediate value  $\mathsf{A}_t$ , the values  $\mathsf{ro}_t, \ldots, \mathsf{rk}_{t-1,t}$  contained in the registers  $\mathsf{reg}_0, \ldots, \mathsf{reg}_{t-1}$  at time t, and the flag flag. The next row contains the resulting state of the TinyRAM machine at time t 1. Each row also includes a memory address  $\mathsf{addr}_t$ , and the value  $\mathsf{vaddr}_t$  stored at this address after the execution of the step, as well as a constant number of auxiliary field elements to be specified later that will be used to check correctness of program execution.

The next table is the program table  $\operatorname{\mathsf{Prog}}$ , which contains the field elements encoding of the TinyRAM program P. Each row contains the description of one line of the program, consisting of one instruction, at most three operands, and possibly an immediate value. Furthermore, we introduce a constant number of auxiliary field elements in each row. These entries can be efficiently computed given the program line stored in the same row and will help verifying its execution, e.g. we encode the position of input and output registers as auxiliary field elements.

The memory table Mem has rows that list the possible memory addresses, their initial values, and an auxiliary field element  $\mathsf{usd} \in \{0,1\}$ . For every pair of address and corresponding initial value, the memory table Mem contains a row in which  $\mathsf{usd} = 0$  and another row in which  $\mathsf{usd} = 1$ . Recall that the memory is initialized with input words listed in v, w, i.e., the input words contributing to the instance and witness of the relation  $\mathcal{R}_{\mathsf{TinyRAM}}$ .

**Table 1.** TinyRAM instruction set, excluding the **read** command. The flag is set equal to 1 if the condition is met and 0 otherwise. If the pc exceeds the program length, i.e., pc  $\geq L$ , or we address a non-existing part of memory, i.e., in a **store** or **load** instruction  $A \geq M$ , the TinyRAM machine halts with answer 1.

| Instruction | Ope        | rands   |   | Effect                                                                                           | Flag                                                    |

|-------------|------------|---------|---|--------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| and         | $reg_i$    | $reg_j$ | A | Compute $r_i$ as bitwise AND of $r_j$ and A                                                      | Result is $0^W$                                         |

| or          | $reg_i$    | $reg_j$ | A | Compute $r_i$ as bitwise OR of $r_j$ and A                                                       | Result is $0^W$                                         |

| xor         | $reg_i$    | $reg_j$ | A | Compute $r_i$ as bitwise XOR of $r_j$ and A                                                      | Result is $0^W$                                         |

| not         | $reg_i$    | A       |   | Compute $r_i$ as bitwise NOT of A                                                                | Result is $0^W$                                         |

| add         | $reg_i$    | $reg_j$ | A | Compute $r_i = r_j + A \mod 2^W$                                                                 | Overflow: $r_j + A \ge 2^W$                             |

| sub         | $reg_i$    | $reg_j$ | A | Compute $r_i = r_j - A \mod 2^W$                                                                 | Borrow: $r_j < A$                                       |

| mull        | $reg_i$    | $reg_j$ | A | Compute $r_i = r_j \times A \bmod 2^W$                                                           | $\neg$ overflow: $\mathbf{r}_j \times \mathbf{A} < 2^W$ |

| umulh       | $reg_i$    | $reg_j$ | A | Compute $r_i$ as upper $W$ bits of $r_j \times A$                                                | $\neg$ overflow: $\mathbf{r}_i = 0$                     |

| smulh       | $reg_i$    | $reg_j$ | A | Compute $r_i$ as upper $W$ bits of the signed $2W$ -bit $r_j \times_s A$ (mull gives lower word) | $\neg$ over/underflow: $r_i = 0$                        |

| udiv        | $reg_i$    | $reg_j$ | A | Compute $r_i$ as quotient of $r_j/A$                                                             | Division by zero: $A = 0$                               |

| umod        | $reg_i$    | $reg_j$ | A | Compute $r_i$ as remainder of $r_j/A$                                                            | Division by zero: $A = 0$                               |

| shl         | $reg_i$    | $reg_j$ | A | Compute $r_i$ as $r_i$ shifted left by A bits                                                    | MSB of $r_j$                                            |

| shr         | $reg_i$    | $reg_j$ | A | Compute $r_i$ as $r_i$ shifted right by A bits                                                   | LSB of $r_j$                                            |

| cmpe        | $reg_i$    | A       |   | Compare if equal                                                                                 | Equal: $r_i = A$                                        |

| cmpa        | $reg_i$    | A       |   | Compare if above                                                                                 | Above: $r_i > A$                                        |

| cmpae       | $reg_i$    | A       |   | Compare if above or equal                                                                        | Above/equal: $r_i \ge A$                                |

| cmpg        | $reg_i$    | A       |   | Signed compare if greater                                                                        | Greater: $r_i >_s A$                                    |

| cmpge       | $reg_i$    | A       |   | Signed compare if greater or equal                                                               | Greater/equal: $r_i \geq_s A$                           |

| mov         | $reg_i$    | A       |   | Set $r_i = A$                                                                                    | Flag unchanged                                          |

| cmov        | $reg_i$    | A       |   | if $flag = 1$ set $r_i = A$                                                                      | Flag unchanged                                          |

| jmp         | A          |         |   | Set $pc = A$                                                                                     | Flag unchanged                                          |

| cjmp        | A          |         |   | If $flag = 1$ set $pc = A$                                                                       | Flag unchanged                                          |

| cnjmp       | A          |         |   | If $flag = 0$ set $pc = A$                                                                       | Flag unchanged                                          |

| store       | <i>A</i> 1 | $reg_i$ |   | Store in memory address A the word $r_i$                                                         | Flag unchanged                                          |

| load        | $reg_i$    | A       |   | Set $r_i$ to the word stored at address $A$                                                      | Flag unchanged                                          |

| answer      | A          |         |   | Stall or halt returning the word A                                                               | Flag unchanged                                          |

| Time | рс           | Instruction       | Immediate | $reg_0$       |   | $reg_{K-1}$                                              | Flag          | Address      | Value            | $ aux_{Exe} $ |

|------|--------------|-------------------|-----------|---------------|---|----------------------------------------------------------|---------------|--------------|------------------|---------------|

| 1    | 0            | inst <sub>0</sub> | $A_0$     | 0             |   | 0                                                        | 0             | 0            | 0                |               |

|      |              |                   |           |               | : |                                                          |               |              |                  |               |

|      |              |                   | _         |               |   |                                                          |               |              |                  |               |

| t    | $pc_t$       | $inst_{pc_t}$     | $A_t$     | $r_{0,t}$     |   | $r_{K-1,t}$                                              | $flag_t$      | $addr_t$     | $V_{addr_t}$     |               |

| t+1  | $ pc_{t+1} $ | $inst_{pc_{t+1}}$ | $A_{t+1}$ | $ r_{0,t+1} $ |   | $\begin{vmatrix} r_{K-1,t} \\ r_{K-1,t+1} \end{vmatrix}$ | $flag_{t+1}$  | $addr_{t+1}$ | $V_{addr_{t+1}}$ |               |

|      |              |                   |           |               |   |                                                          |               |              |                  |               |

|      |              |                   |           |               | : |                                                          |               |              |                  |               |

| T    | $pc_T$       | answer 0          | 0         | $r_{0.T}$     |   | $r_{K-1}$                                                | $flag_{\tau}$ | $addr_T$     | Vaddra           |               |

**Table 2.** The execution table Exe, the program table Prog, the memory table Mem and the table EvenBits.

(a) The execution table Exe.

| рс  | Instruction           | Immediate | $aux_{Prog}$ |

|-----|-----------------------|-----------|--------------|

| 0   | $inst_0$              | $A_0$     |              |

|     | :                     |           |              |

| L-1 | $\dots$ inst $_{L-1}$ | $A_{L-1}$ |              |

(b) The program table Prog.

| Address | Initial value | usd |

|---------|---------------|-----|

| 0       | 0             | 0   |

| 1       | $v_1$         | 0   |

|         | :             |     |

| M-1     | $v_{M-1}$     | 0   |

| 0       | 0             | 1   |

| 1       | $v_1$         | 1   |

|         | i             |     |

| M-1     | $V_{M-1}$     | 1   |

Values 0 1 4 5  $\vdots$   $\sum_{i=0}^{\frac{W}{2}-1} 2^{2i}$

(d) The table EvenBits.

(c) The memory table Mem.

In addition to these, we also consider an auxiliary lookup table EvenBits containing the encoding of words of length W whose binary expansion has 0 in all odd positions. The table contains  $2^{\frac{W}{2}}$  field elements and will be used as part of a check that certain field elements encode a word of length W.

#### 3.1 Decomposition of TinyRAM

Let (Exe, Prog, Mem, EvenBits) be the tables of field elements encoding the program execution and the auxiliary values. We can now reformulate the correct execution of a TinyRAM program defined by  $\mathcal{R}_{\mathsf{TinyRAM}}$  as a relation that imposes a number of constraints the field elements included in tables should satisfy:

$$\mathcal{R}_{\mathsf{TinyRAM}}^{\mathsf{field}} = \left\{ \begin{array}{l} (pp, u, w) = ((W, K, \mathbb{F}, *), (P, v, T, M), \mathsf{w}) \mid \\ \mathsf{w} = (\mathsf{Exe}, \mathsf{Prog}, \mathsf{Mem}, \mathsf{EvenBits}, *) \\ (pp, (P, v, T, M), \mathsf{w}) \in \mathcal{R}_{\mathsf{check}} \\ (pp, (T, M), \mathsf{w}) \in \mathcal{R}_{\mathsf{mem}} \\ (pp, \bot, \mathsf{w}) \in \mathcal{R}_{\mathsf{step}} \end{array} \right\}$$

where the relations  $\mathcal{R}_{\mathsf{check}}$ ,  $\mathcal{R}_{\mathsf{mem}}$ ,  $\mathcal{R}_{\mathsf{step}}$  jointly guarantee the witness w consists of field elements encoding a correct TinyRAM execution that answers 0 in T steps using M words of memory, public input v, and additional private inputs.

Specifically, the relation  $\mathcal{R}_{check}$  checks the initial values of the memory are correctly included into Mem, the program is correctly encoded in Prog, EvenBits

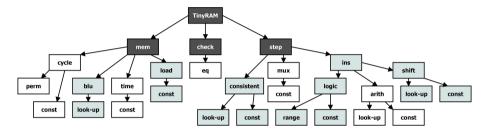

contains the correct encodings of the auxiliary lookup table, the initial state of the TinyRAM machine is correct and that it terminates with answer 0 in step T. The role of  $\mathcal{R}_{\mathsf{mem}}$  is to check that memory usage is consistent throughout the execution of the program. That is, if a memory value is loaded at time t then it should match the last stored value at the same address. Finally,  $\mathcal{R}_{\mathsf{step}}$  checks that each step of the execution has been performed correctly. In the rest of the section we describe  $\mathcal{R}_{\mathsf{check}}$ ,  $\mathcal{R}_{\mathsf{mem}}$  and  $\mathcal{R}_{\mathsf{step}}$ , gradually decomposing them into smaller and simpler relations. Ultimately, we specify each of these subrelations in terms of some building block: equality, lookup, permutation, and range relations. Figure 3 illustrates the decomposition of  $\mathcal{R}_{\mathsf{TinyRAM}}^{\mathsf{field}}$  into progressively smaller relations.

Fig. 3. Diagram of the decomposition of TinyRAM into equality, lookup, permutation, and range relations.

**Building Blocks.** We give a brief description of the building block relations used in the decomposition of  $\mathcal{R}_{\mathsf{TinvRAM}}^{\mathsf{field}}$ .

- An equality relation  $\mathcal{R}_{eq}$  checks that rows  $\mathsf{Tab}_i$  of a table  $\mathsf{Tab}$  in the witness encode tuples  $v_1, \ldots, v_m$  of given W-bit words

- A lookup relation checks the membership of a tuple of field elements  $\boldsymbol{w}$  in the set of rows of a table Tab. This differs from the previous relation as both  $\boldsymbol{w}$  and Tab are both in the witness. We extend this relation in the natural way for checking the membership of multiple tuples  $\boldsymbol{w}_1, \boldsymbol{w}_2, \ldots$  in a table.

- A range relation to check that a field element **a** can be written as a W-bit word, i.e., **a** is in the range  $\{0, \dots, 2^W 1\}$ .

- A permutation relation can be used to check that two ordered sets of a given size are permutations of each other. The permutation is in the witness i.e. it is unknown to the verifier.

#### 3.2 Checking the Correctness of Values

The role of  $\mathcal{R}_{\mathsf{check}}$  is to check that w consists of the correct number of field elements that can be partitioned into the appropriate tables and also to check that specific entries in these tables are correct.

$$\mathcal{R}_{\mathsf{check}} = \left\{ \begin{array}{l} (pp, u, w) = ((W, K, \mathbb{F}, *), (P, v, T, M), \mathsf{w}) \mid \\ \mathsf{w} = (\mathsf{Exe}, \mathsf{Prog}, \mathsf{Mem}, \mathsf{EvenBits}, *), \\ \mathsf{Exe} = \{\mathsf{Exe}_t\}_{t=1}^T, \quad \mathsf{Prog} = \{\mathsf{Prog}_i\}_{i=0}^{L-1} \\ \mathsf{Prog}_0 = (0, \mathsf{inst}_0, A_0, \ldots) \\ (pp, (1, 0, \mathsf{inst}_0, A_0, 0, \ldots, 0, \ldots), \mathsf{Exe}_1) \in \mathcal{R}_{\mathsf{eq}} \\ (pp, (T, \mathbf{answer}, 0, \ldots), \mathsf{Exe}_T) \in \mathcal{R}_{\mathsf{eq}} \\ \left(pp, \left(0, 1, 4, 5, \ldots, \sum_{i=0}^{\frac{W}{2}-1} 2^{2i}\right), \mathsf{EvenBits}\right) \in \mathcal{R}_{\mathsf{eq}} \\ (pp, P, \mathsf{Prog}) \in \mathcal{R}_{\mathsf{eq}} \quad (pp, v, \mathsf{Mem}) \in \mathcal{R}_{\mathsf{eq}} \end{array} \right\}.$$

The relation  $\mathcal{R}_{\mathsf{check}}$  checks that: the first and last row of the execution table contains the correct initial values; the auxiliary lookup table EvenBits contains the embeddings of all W-bit words with 0 in all odd positions; the program table Prog contains the correct field element embedding of the program P as well as the correct auxiliary entries; the memory table Mem contains the correct embedding of the input words listed in v.

### 3.3 Checking Memory Consistency

The relation  $\mathcal{R}_{\text{mem}}$  checks that the memory is used consistently across different steps in the execution. For instance, if at step t a value is loaded from memory, then it should be equal to the last value stored in the same address. If it is the first time a memory address is accessed, we need to ensure consistency with the initial values. If two consecutive memory accesses to the same address were placed into two adjacent rows of Exe it would be easy to check their consistency. However, this is generally not the case since the Exe table is sorted by execution time rather than memory access. Therefore, we need to devise a way to check consistency of memory accesses that could be located in any position of Exe. Overall the memory consistency relation  $\mathcal{R}_{\text{mem}}$  decomposes as follows

$$\mathcal{R}_{\mathsf{mem}} = \left\{ \begin{array}{c} (pp, u, w) = ((W, K, \mathbb{F}, *), (T, M), \mathsf{w}) \mid \\ \mathsf{w} = (\mathsf{Exe}, \mathsf{Prog}, \mathsf{Mem}, \mathsf{EvenBits}, \pi, *), \\ \mathsf{Exe} = \{\mathsf{Exe}_t\}_{t=1}^T & \mathsf{Mem} = \{\mathsf{Mem}_j\}_{j=0}^{2M-2} \\ (pp, T, (\mathsf{Exe}, \pi)) \in \mathcal{R}_{\mathsf{cycle}}, & (pp, T, \mathsf{Exe}) \in \mathcal{R}_{\mathsf{time}} \\ (pp, (T, M), (\mathsf{Exe}, \mathsf{Mem})) \in \mathcal{R}_{\mathsf{blookup}}, & (pp, T, \mathsf{Exe}) \in \mathcal{R}_{\mathsf{load}} \end{array} \right\}$$

To help with checking the memory consistency, we include in each row of the execution table the following auxiliary entries

$$m{aux}_{\mathsf{Exe}} = | au_{\mathrm{link}}|_{\mathsf{V}_{\mathrm{link}}}|_{\mathsf{V}_{\mathrm{init}}}|_{\mathsf{usd}}|_{\mathsf{S}}|_{\mathsf{L}}|\cdots$$

where  $\tau_{\rm link}$  contains the previous time-step at which the current address was accessed, unless this is the first time a location is accessed in which case it is set equal to the last time-step this location is accessed. Similarly,  $v_{\rm link}$  stores the value contained in the address after time  $\tau_{\rm link}$ , unless this is the first time that

location is accessed, in which case it stores the last value stored in that location. The value  $v_{\rm init}$  is a copy of the initial value assigned to that memory location, which is also stored in the memory table Mem. The value usd is a flag which is set equal to 0 if this is the first time we access the current memory address, and 1 otherwise. The values S, L are flags set equal to 1 in case the current instruction is a **store** or **load** operation, respectively, and 0 otherwise. The values S, L are also stored in the auxiliary entries of the program table  $aux_{\rm Prog} = |S|L|\cdots|$ .

Memory Accesses Form Cycles. We check memory consistency by specifying cycles of memory accesses, so that consecutive terms in a cycle correspond to two consecutive accesses to the same memory location. By using the above auxiliary entries, we use the relation  $\mathcal{R}_{\text{cycle}}$  for the memory access pattern in the rows of Exe being in correspondence with a permutation  $\pi$  defined by such cycles. The relation  $\mathcal{R}_{\text{cycle}}$  checks that all memory accesses (i.e. with S + L = 1) relative to the same address are connected into cycles and that rows not involving memory operations (S + L = 0) are not included in these cycles. The relation does not include any explicit checks on whether S + L is equal to 0 or 1. It is sufficient to check that  $S_t + L_t = S_{t'} + L_{t'}$ ,  $t = \tau_{\text{link}t'}$ ,  $v_{\text{add}r_t} = v_{\text{link}t'}$  and  $\text{addr}_t = \text{addr}_{t'}$  for some  $t' = \pi(t)$ , which ensures that operations which are not memory operations are not part of cycles including memory operations.

$$\mathcal{R}_{\mathsf{cycle}} = \left\{ \begin{array}{l} (pp, u, w) = ((W, K, \mathbb{F}, *), T, (\mathsf{Exe}, \pi)) \ \big| \\ \mathsf{Exe}_t = (t, \dots, \mathsf{addr}_t, \mathsf{v}_{\mathsf{link}t}, \tau_{\mathsf{link}t}, \dots, S_t, L_t, \dots) \ \text{for} \ t \in [T] \\ \boldsymbol{a}_t = (t, \mathsf{addr}_t, \mathsf{v}_{\mathsf{addr}_t}, \mathsf{S}_t + \mathsf{L}_t) \ \text{for} \ t \in [T] \\ \boldsymbol{b}_t = (\tau_{\mathsf{link}t}, \mathsf{addr}_t, \mathsf{v}_{\mathsf{link}t}, \mathsf{S}_t + \mathsf{L}_t) \ \text{for} \ t \in [T] \\ ((W, K, \mathbb{F}, *), T, (\{\boldsymbol{a}_i, \boldsymbol{b}_i\}_{i=1}^T, \pi)) \in \mathcal{R}_{\mathsf{perm}} \end{array} \right\}$$

Memory Accesses are in the Correct Order. Consecutive terms in a cycle should correspond to the consecutive time-steps in which the memory is accessed. To check that the memory cycles are time-ordered we can simply verify that  $t > \tau_{\text{link}t}$  for any given time-step  $t \in [T]^6$ . Since memory accesses are connected into cycles, the first time we access a new memory location the  $\tau_{\text{link}}$  entry stores the last point in time that location is accessed by the program. In this case (usd = 0), we verify that  $t \leq \tau_{\text{link}t}$ . The relation  $\mathcal{R}_{\text{time}}$  incorporates these conditions

$$\mathcal{R}_{\mathsf{time}} = \left\{ \begin{array}{c} (pp, u, w) = ((W, K, \mathbb{F}, *), T, \mathsf{Exe}) \mid \\ \mathsf{Exe}_t = (t, \dots, \tau_{\mathsf{link}_t}, \dots, \mathsf{usd}_t, \dots) \text{ for } t \in [T] \\ \forall \ t \in [T] : (\mathsf{usd} = 0 \land t \leq \tau_{\mathsf{link}_t}) \lor (\mathsf{usd} = 1 \land t > \tau_{\mathsf{link}_t}) \end{array} \right\}$$

Memory Locations are in no more than one Cycle. To ensure that the cycles correspond to sequences of memory addresses we also require that all the

<sup>&</sup>lt;sup>6</sup> For this to be sufficient we also need the time-steps in the execution table to be correct but this is ensured by the  $\mathcal{R}_{\mathsf{check}}$  and  $\mathcal{R}_{\mathsf{consistent}}$  (appears later) relations.

rows touching the same memory address are included in the same cycle. Since the cycles are time-ordered, they require one time-step for which  $\mathsf{usd} = 0$  in order to close a cycle. Thus, we can ensure each memory location to be part of at most on cycle by letting  $\mathsf{usd}$  to be set equal to 0 at most once for each memory address. We introduce a bounded lookup relation  $\mathcal{R}_{\mathsf{blookup}}$  to address this requirement. The relation checks that for any row in Exe, the tuple  $(\mathsf{addr}_t, \mathsf{v}_{\mathsf{init}t}, \mathsf{usd})$  is contained in one row of the table Mem and that each row  $(j, \mathsf{v}_j, 0)$  of Mem is accessed at most once by the program.

$$\mathcal{R}_{\mathsf{blookup}} = \left\{ \begin{array}{l} (pp, u, w) = ((W, K, \mathbb{F}, *), (T, M), (\mathsf{Exe}, \mathsf{Mem})) \mid \\ \mathsf{Exe}_t = (t, \dots, \mathsf{addr}_t, \dots, \mathsf{v}_{\mathsf{init}_t}, \mathsf{usd}_t, \dots) \text{ for } t \in [T] \\ \forall \ t \in [T] \ (pp, \bot, ((\mathsf{addr}_t, \mathsf{v}_{\mathsf{init}_t}, \mathsf{usd}_t) \,, \mathsf{Mem})) \in \mathcal{R}_{\mathsf{lookup}} \, \land \\ \forall \ (j, \mathsf{v}_j, 0) \in \mathsf{Mem} : (\dots, j, \dots, \mathsf{v}_j, 0, \dots) \text{ occurs at most once in Exe} \end{array} \right\}$$

**Load Instructions are Consistent.** Finally, we are only left to check that if the program executes a **load** instruction the value  $v_{\mathsf{addr}_t}$  loaded from memory is consistent with the value stored at the same address at the previous access. Similarly, if **load** is executed on a new memory location, then the value loaded should match with the initial value  $v_{\mathsf{init}_t}$ . No additional checks are required for **store** instructions. These checks are incorporated in the relation  $\mathcal{R}_{\mathsf{load}}$ .

$$\mathcal{R}_{\mathsf{load}} = \left\{ \begin{array}{l} (pp, u, w) = ((W, K, \mathbb{F}, *), T, \mathsf{Exe}) \ \big| \\ \mathsf{Exe}_t = (t, \dots, \mathsf{addr}_t, \mathsf{v}_{\mathsf{addr}_t}, \tau_{\mathsf{link}t}, \mathsf{v}_{\mathsf{link}t}, \mathsf{v}_{\mathsf{init}t}, \mathsf{usd}_t, \dots) \ \mathsf{for} \ t \in [T] \\ \forall \ t \in [T] : \mathsf{L}_t(\mathsf{v}_{\mathsf{addr}_t} - \mathsf{v}_{\mathsf{init}t} + \mathsf{usd}_t(\mathsf{v}_{\mathsf{init}t} - \mathsf{v}_{\mathsf{link}t})) = 0 \end{array} \right\}$$

#### 3.4 Checking Correct Execution of Instructions

We use the relation  $\mathcal{R}_{\mathsf{step}}$  to guarantee that each step of the execution has been performed correctly. This involves checking for each row  $\mathsf{Exe}_t$  of the execution table that the stored words are in the range  $\{0,\ldots,2^W-1\}$ , the  $\mathsf{flag}_t$  is a bit, the program counter  $\mathsf{pc}_t$  matches the instruction and the immediate value  $\mathsf{A}_t$  in the program, and that  $\mathsf{inst}_t$  is correctly executed. An instruction takes some inputs, e.g., values indicated by the operands  $\mathsf{reg}_j, A$  or the flag and as a result may change the program counter, a register value, a value stored at a memory address, or the flag. Since we have already checked memory correctness, if the operation is a load or store we may assume the memory value is correct.

$$\mathcal{R}_{\mathsf{step}} = \left\{ \begin{array}{l} (pp, u, w) = ((W, K, \mathbb{F}, *), \bot, \mathsf{w}) \mid \\ \mathsf{w} = (\mathsf{Exe}, \mathsf{Prog}, \mathsf{Mem}, \mathsf{EvenBits}, *) \ \land \ \mathsf{Exe} = \{\mathsf{Exe}_t\}_{t=1}^T \\ \forall t \in \{1, \dots, T-1\} : \\ (pp, \bot, (\mathsf{Exe}_t, \mathsf{Exe}_{t+1})) \in \mathcal{R}_{\mathsf{mux}} \\ (pp, \bot, (\mathsf{Exe}_i, \mathsf{Exe}_{i+1}, \mathsf{Prog})) \in \mathcal{R}_{\mathsf{consistent}} \\ (pp, \bot, (\mathsf{Exe}_i, \mathsf{Exe}_{i+1}, \mathsf{EvenBits}, *)) \in \mathcal{R}_{\mathsf{ins}} \end{array} \right\}.$$

To help checking the consistency of the operations the rows of the execution and program tables include some auxiliary entries. These consist of some temporary variables, an output vector, and some selection vectors which are also listed in the program table. The temporary variables are used to store a copy of the inputs and outputs of an instruction. The advantage of the temporary variables is that for each addition operation we check, we will always have the inputs and outputs stored, instead of having to handle multiple registers holding inputs and output in arbitrary order.

Ensuring Temporary Values are Correct. A multiplexing relation  $\mathcal{R}_{\text{mux}}$  is used to check that the temporary variables are consistent with operands contained in inst<sub>t</sub>. Checking operations on temporary values require us to multiplex the corresponding register, immediate, and memory values in and out of the temporary values. We do this using selection vectors that are bit-vectors encoding the operands of an instruction. Each row of the execution table includes multiple variables that may be selected as an operand. A selection vector will have a bit for each of these variables indicating whether it is picked or not. More details about the multiplexing relation are provided in the full version of the paper [BCG+18].

The Execution Table and the Program Table are Consistent. The consistency relation  $\mathcal{R}_{\text{consistent}}$  checks that the time is correctly incremented and that the program counter is in the correct range, i.e.  $\mathsf{pc}_{t+1} \in \{0, \dots, L-1\}$  and is incremented unless a jump-instruction is executed. It also checks that the instruction, the immediate value and the selection vectors stored in the execution table are consistent with the program the line indexed  $\mathsf{pc}$ . Furthermore, it checks that the entries in the output vector relevant to  $\mathsf{inst}_t$  are all equal to zero and that the contents of the registers do not change, unless specified by the instruction, e.g. the register storing the result of the computation. Verifying that rows of the execution table match with states of a TinyRAM machine involves checking that entries that are not affected by an instruction remain the same in the next state. For this we use another selector vector with entries equal to 0, positioned in correspondence of entries that are changed during the execution, and 1 for entries that do not change in the execution.

Instructions are Executed Correctly. An instruction checker relation  $\mathcal{R}_{ins}$  checking that the temporary values are in the range  $\{0,\ldots,2^W-1\}$  and are consistent with the output vector. We divide the entries of the output vector into 4 groups: logical (AND, XOR, OR), arithmetic (SUM, PROD, SSUM, SPROD, MOD), shift (SHIFT), and flag (FLAG<sub>1</sub>, FLAG<sub>2</sub>, FLAG<sub>3</sub>, FLAG<sub>4</sub>). By specifying constraints to all these entries, we can directly verify all the logical, arithmetic, and shifts operations after which the variables are named.

The  $\mathcal{R}_{\text{ins}}$  can be decomposed into 3 sub-relations:  $\mathcal{R}_{\text{logic}}$ ,  $\mathcal{R}_{\text{arith}}$ , and  $\mathcal{R}_{\text{shift}}$ . In the full paper [BCG+18] we show choices of selection vectors which reduce the verification of any other operation to the ones contained in these 3 categories. We also describe the decomposition of  $\mathcal{R}_{\text{logic}}$ ,  $\mathcal{R}_{\text{arith}}$ ,  $\mathcal{R}_{\text{shift}}$  into our elementary building blocks.

## 4 Efficient Bit Decomposition for Logical Relations

In this section we summarise a new decomposition technique which will enable verification of bitwise AND and XOR operations. This allows us to check all boolean operations more efficiently. Let a,b be the inputs of the bit-wise AND or bit-wise XOR operation, and let c be the output. To verify the correctness of the operation, e.g.  $a \land b = c$ , consider the decompositions of the inputs into their odd and even-position bits, namely  $a = 2a_o + a_e$  and  $b = 2b_o + b_e$ . Observe that taking the sum of the integers storing the even-positions of a and b gives

$$\begin{aligned} \mathbf{a}_{\mathrm{e}} + \mathbf{b}_{\mathrm{e}} &= (0, \mathbf{a}_{W-2}, \dots, 0, \mathbf{a}_{0}) + (0, \mathbf{b}_{W-2}, \dots, 0, \mathbf{b}_{0}) \\ &= (\mathbf{a}_{W-2} \wedge \mathbf{b}_{W-2}, \mathbf{a}_{W-2} \oplus \mathbf{b}_{W-2}, \dots, \mathbf{a}_{0} \wedge \mathbf{b}_{0}, \mathbf{a}_{0} \oplus \mathbf{b}_{0}) \end{aligned}$$

The above contains the bit-wise AND of the even bits of a and b placed in odd position and the bit-wise XOR of the even bits of a and b in even position. Therefore we can consider taking again the decomposition of  $a_e + b_e$  into its odd and even-position bits, i.e.  $a_e + b_e = 2e_o + e_e$  so that half of the bits of  $a \wedge b$  are stored in  $e_o$  and half of the bits of  $a \oplus b$  are stored in  $e_e$ . We can repeat the above procedure starting from the odd-position bits of a and b getting the following

$$\begin{aligned} \mathsf{a}_{\rm o} + \mathsf{b}_{\rm o} &= (0, \mathsf{a}_{W-1}, \dots, 0, \mathsf{a}_1) + (0, \mathsf{b}_{W-1}, \dots, 0, \mathsf{b}_1) \\ &= (\mathsf{a}_{W-1} \wedge \mathsf{b}_{W-1}, \mathsf{a}_{W-1} \oplus \mathsf{b}_{W-1}, \dots, \mathsf{a}_1 \wedge \mathsf{b}_1, \mathsf{a}_1 \oplus \mathsf{b}_1) = 2\mathsf{o}_{\rm o} + \mathsf{o}_{\rm e} \end{aligned}$$

where  $o_o$  stores half of the bits of  $a \wedge b$  and  $o_e$  stores and half of the bits of  $a \oplus b$ . Putting everything together, given the decompositions  $a_o, a_e, b_o, b_e, o_o, o_e, e_o, e_e \in \mathsf{EvenBits}$  such that the following hold

$$\mathsf{a} = 2\mathsf{a}_\mathrm{o} + \mathsf{a}_\mathrm{e} \qquad \mathsf{b} = 2\mathsf{b}_\mathrm{o} + \mathsf{b}_\mathrm{e} \qquad \mathsf{a}_\mathrm{o} + \mathsf{b}_\mathrm{o} = 2\mathsf{o}_\mathrm{o} + \mathsf{o}_\mathrm{e} \qquad \mathsf{a}_\mathrm{e} + \mathsf{b}_\mathrm{e} = 2\mathsf{e}_\mathrm{o} + \mathsf{e}_\mathrm{e}$$

then the bit-wise AND and XOR of a and b is given by the following

$$a \wedge b = 2o_0 + e_0$$

$a \oplus b = 2o_e + e_e$

it is then sufficient to check  $c=2\mathrm{o}_\mathrm{o}+\mathrm{e}_\mathrm{o}$  for checking  $a\wedge b=c.$

# 5 Proofs for the Correct Program Execution over the ILC Channel