# A Beginner's Guide to SSD Firmware

ବି ବି ବି ବି ବି ବି ବି

Designing, Optimizing, and Maintaining SSD Firmware

Gopi Kuppan Thirumalai

# A Beginner's Guide to SSD Firmware

Designing, Optimizing, and Maintaining SSD Firmware

Gopi Kuppan Thirumalai

Apress<sup>®</sup>

#### A Beginner's Guide to SSD Firmware: Designing, Optimizing, and Maintaining SSD Firmware

Gopi Kuppan Thirumalai San Jose, CA, USA

#### ISBN-13 (pbk): 978-1-4842-9887-9 https://doi.org/10.1007/978-1-4842-9888-6

ISBN-13 (electronic): 978-1-4842-9888-6

#### Copyright © 2023 by Gopi Kuppan Thirumalai

This work is subject to copyright. All rights are reserved by the publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

Trademarked names, logos, and images may appear in this book. Rather than use a trademark symbol with every occurrence of a trademarked name, logo, or image we use the names, logos, and images only in an editorial fashion and to the benefit of the trademark owner, with no intention of infringement of the trademark.

The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

While the advice and information in this book are believed to be true and accurate at the date of publication, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Managing Director, Apress Media LLC: Welmoed Spahr Acquisitions Editor: Smriti Srivastava Development Editor: Laura Berendson Editorial Assistant: Jessica Vakili Copy Editor: April Rondeau

Cover designed by eStudioCalamar

Cover image by Michael Dziedzic on Unsplash (www.unsplash.com)

Distributed to the book trade worldwide by Springer Science+Business Media New York, 1 New York Plaza, Suite 4600, New York, NY 10004-1562, USA. Phone 1-800-SPRINGER, fax (201) 348-4505, email orders-ny@springer-sbm.com, or visit www.springeronline.com. Apress Media, LLC is a California LLC and the sole member (owner) is Springer Science + Business Media Finance Inc (SSBM Finance Inc). SSBM Finance Inc is a **Delaware** corporation.

For information on translations, please e-mail booktranslations@springernature.com; for reprint, paperback, or audio rights, please e-mail bookpermissions@springernature.com.

Apress titles may be purchased in bulk for academic, corporate, or promotional use. eBook versions and licenses are also available for most titles. For more information, reference our Print and eBook Bulk Sales web page at http://www.apress.com/bulk-sales.

Any source code or other supplementary material referenced by the author in this book is available to readers on GitHub (github.com/apress). For more detailed information, please visit https://www.apress.com/gp/services/source-code.

Paper in this product is recyclable

#### To my mother, Vijaya T, and my father, Thirumalai J

# **Table of Contents**

| About the Author                                      | xiii |

|-------------------------------------------------------|------|

| About the Technical Reviewer                          | XV   |

| Chapter 1: Introduction to SSD Firmware               | 1    |

| What Is SSD?                                          | 1    |

| Summary                                               | 5    |

| Chapter 2: Understanding the Role of Firmware in SSDs | 7    |

| What Is Firmware?                                     | 7    |

| Summary                                               | 10   |

| Chapter 3: The History and Evolution of SSD Firmware  | 11   |

| History                                               | 11   |

| Summary                                               | 13   |

| Chapter 4: Basics of Flash Memory                     | 15   |

| Memory Types                                          | 15   |

| NOR Flash Memory                                      | 16   |

| NAND Flash Memory                                     | 17   |

| Similarities                                          | 19   |

| Differences                                           | 19   |

| A Flash Memory Cell                                   | 19   |

| NAND Memory Organization                              | 23   |

| Addressing                                            | 24   |

| Erase                                                                   | 25 |

|-------------------------------------------------------------------------|----|

| Write                                                                   | 25 |

| Read                                                                    | 27 |

| Program/Erase Cycle (P/E Cycle)                                         | 28 |

| Summary                                                                 | 30 |

| Chapter 5: 3D Vertical NAND                                             | 31 |

| Evolution of 3D Vertical NAND Technology                                | 31 |

| Unlocking New Possibilities with Vertical NAND Architecture             | 33 |

| Advantages of 3D Vertical NAND                                          | 35 |

| Applications of 3D Vertical NAND                                        | 36 |

| Understanding 3D Vertical NAND Architecture                             | 37 |

| Layers and Pages                                                        | 37 |

| Charge Trapping Technology                                              | 38 |

| Bit Line and Word Line Architecture                                     | 40 |

| Control and Decoding Circuits                                           | 40 |

| Memory Cell Size and Density in 3D Vertical NAND Flash Memory           |    |

| Technology                                                              |    |

| Understanding NAND Cell Types Supported: SLC, MLC, and TLC (QLC)<br>SLC |    |

| SLC                                                                     |    |

| TLC                                                                     |    |

|                                                                         |    |

| Read and Write Operations in 3D Vertical NAND                           |    |

| Erasing MLC 3D vertical NAND block                                      |    |

| Endurance and Data Retention Capabilities                               |    |

| Speed and Efficiency Compared to 2D Planar NAND                         |    |

| Advancements in Storage Capacity with 3D Vertical NAND                  |    |

| Summary                                                                 | 50 |

| C | hapter 6: Basic Understanding of NAND Flash Interface | .51               |

|---|-------------------------------------------------------|-------------------|

|   | Basic NAND IO Interfacing Pin Details                 | .52               |

|   | NAND Flash Interface Basics                           | .54               |

|   | Open NAND Flash Interface (ONFI)                      | .55               |

|   | Toggle Mode Interface                                 | .55               |

|   | Command Cycles for NAND Flash Operations              | .56               |

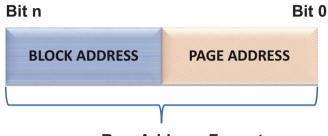

|   | Addressing                                            | .57               |

|   | Column Address                                        | .58               |

|   | Row Address                                           | .58               |

|   | Addressing Functions                                  | .58               |

|   | Address Cycle Order                                   | . <mark>58</mark> |

|   | Handling Unused Bits                                  | .59               |

|   | NAND Flash Commands                                   | .62               |

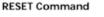

|   | RESET Operation                                       | .62               |

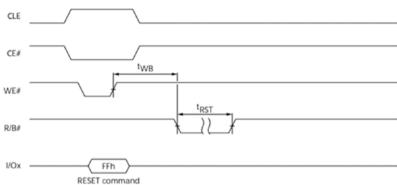

|   | READ ID Operation                                     | .63               |

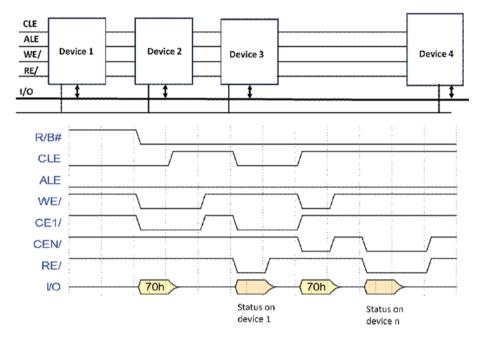

|   | READ STATUS Operation                                 | . <mark>64</mark> |

|   | READ STATUS Response                                  | . <mark>64</mark> |

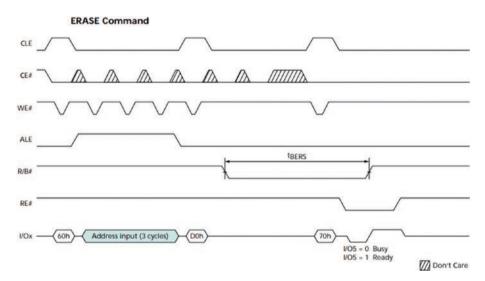

|   | ERASE Operation                                       | . <b>66</b>       |

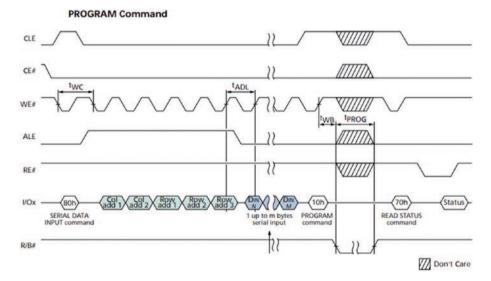

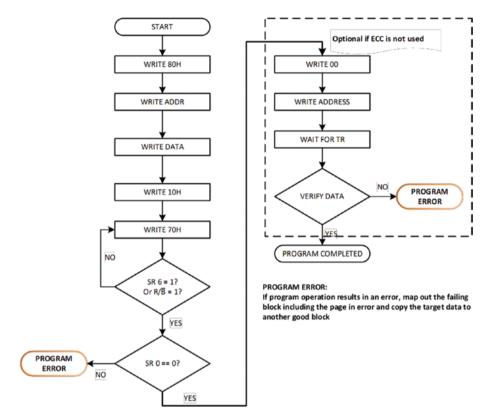

|   | PROGRAM Operations                                    | . <mark>68</mark> |

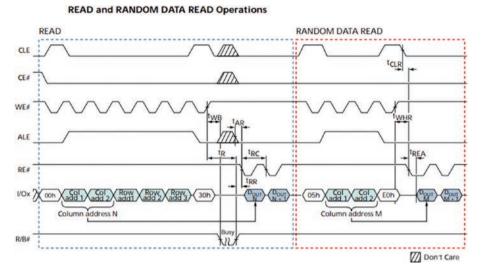

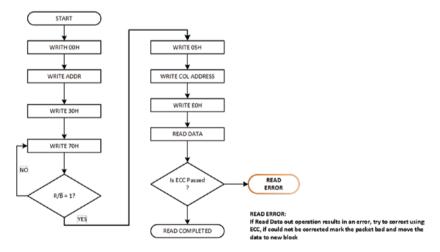

|   | READ Operation                                        | .70               |

|   | RANDOM DATA READ Operation                            | .72               |

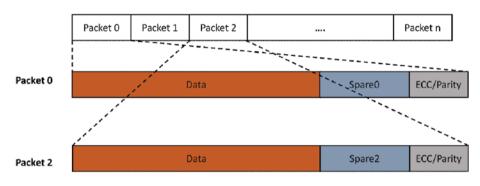

|   | Typical NAND Packet Structure                         | .73               |

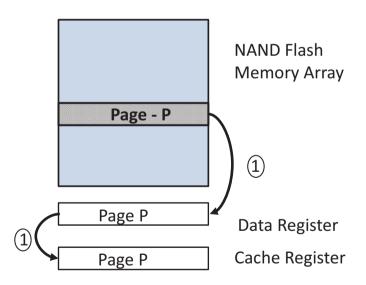

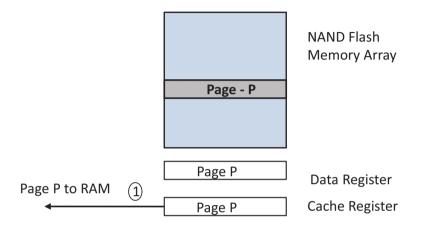

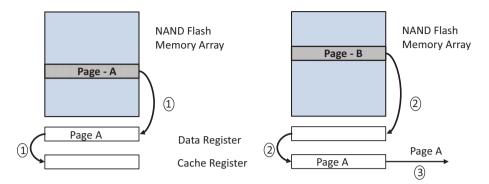

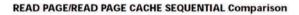

|   | PAGE READ CACHE MODE Operation                        | .74               |

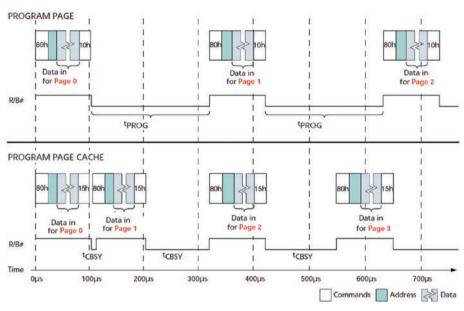

|   | PROGRAM PAGE CACHE Operation                          | .75               |

|   | Advanced Command Sets                                 | .78               |

|   | Address Input Restrictions for Multi-Plane Operations | .79               |

| Multi-plane Read                                          | 81         |

|-----------------------------------------------------------|------------|

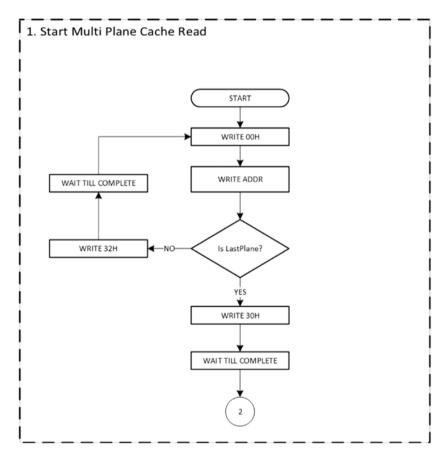

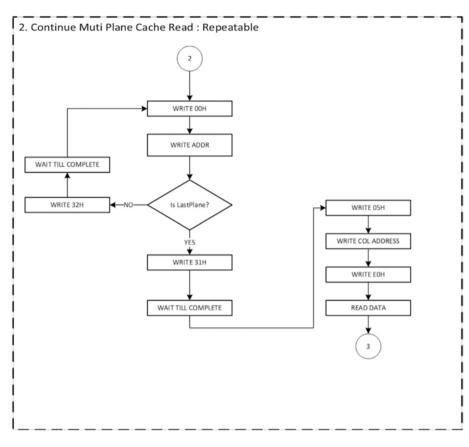

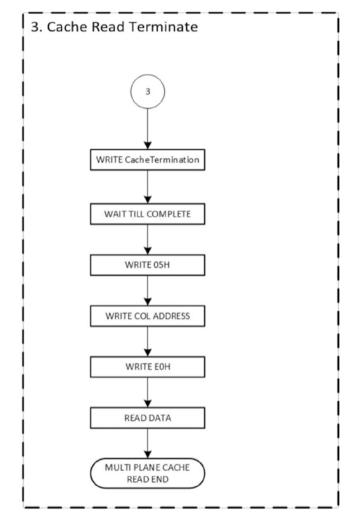

| MULTI- PLANE RANDOM CACHE READ Operation                  | 82         |

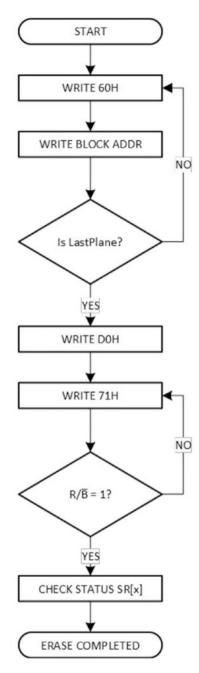

| Multi Plane Program Operation                             | 85         |

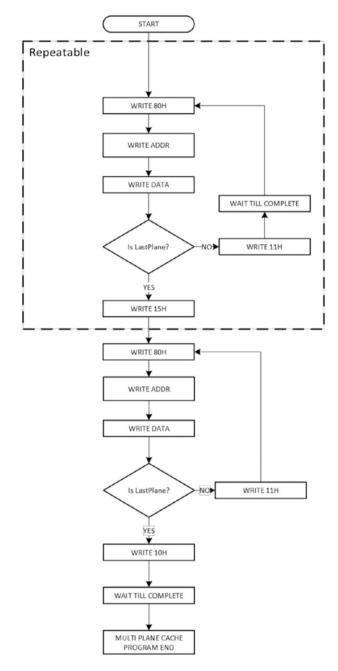

| Multi Plane Cache Program Operation                       | 88         |

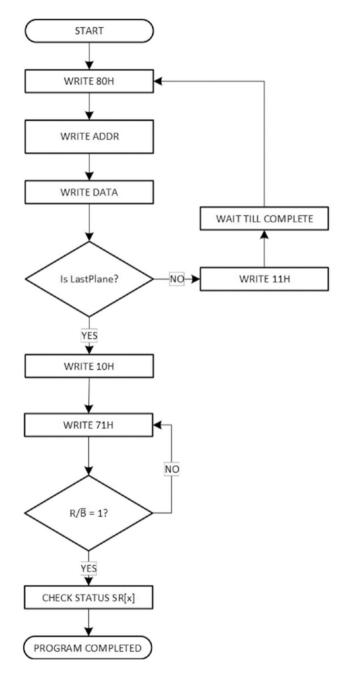

| Multi Block Erase Operation                               | 90         |

| Summary                                                   | 92         |

| Chapter 7: Common SSD Firmware Features                   | 93         |

| Significance of Garbage Collection in SSDs                | 95         |

| Types of Garbage Collection Strategies                    | 95         |

| Full Garbage Collection                                   | 95         |

| Partial Garbage Collection                                | 95         |

| Dynamic Garbage Collection                                | 96         |

| Error-Triggered Garbage Collection                        | 96         |

| Garbage Collection Read Process                           | 97         |

| Retrieving Valid Data during Compaction                   | <b>9</b> 8 |

| Handling Incomplete or Interrupted Reads                  | <b>9</b> 8 |

| Address Translation during Compaction Reads               |            |

| Writing Data during Compaction                            |            |

| Address Mapping and Updating                              |            |

| Managing Block Erasure and Wear-Leveling                  |            |

| Handling Unexpected Power-Off Conditions in Garbage Colle | ection 102 |

| Ensuring Data Consistency during Power Loss               |            |

| Write Journaling and Recovery Mechanisms                  |            |

| Managing Incomplete Compaction Operations                 |            |

| Performance Considerations in Garbage Collection          |            |

| Impact of Compaction on SSD Performance                   |            |

| Write Amplification and Its Effects                       |            |

| Strategies to Minimize Performance Degradation              | 107 |

|-------------------------------------------------------------|-----|

| Balancing Garbage Collection and Host Write Operations      | 108 |

| Understanding the Workload Characteristics                  | 108 |

| Garbage Collection Prioritization                           | 108 |

| Dynamic Resource Allocation                                 | 109 |

| Over-Provisioning                                           | 109 |

| Adaptive Garbage Collection                                 | 110 |

| Drawbacks of Garbage Collection and Minimizing Their Impact | 110 |

| Write Amplification                                         | 110 |

| Performance Degradation                                     | 111 |

| Increased Power Consumption                                 | 111 |

| Impact on Endurance                                         | 111 |

| Other Concerns                                              | 112 |

| Data Retention                                              | 112 |

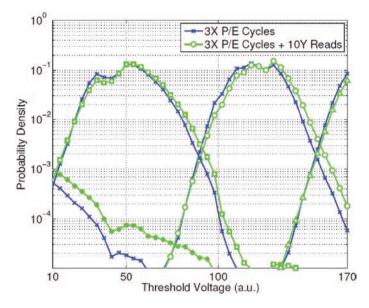

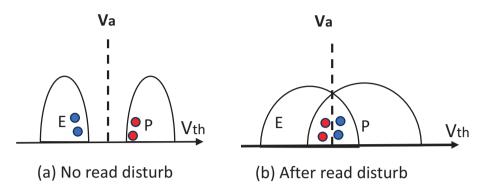

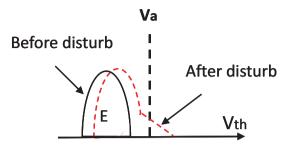

| Read Disturb                                                | 113 |

| Program Disturbance                                         | 115 |

| Write Amplification                                         | 116 |

| Over-provisioning                                           | 117 |

| Encryption                                                  | 118 |

| Summary                                                     | 118 |

| Chapter 8: SSD Firmware Design Considerations               |     |

| Design Considerations                                       |     |

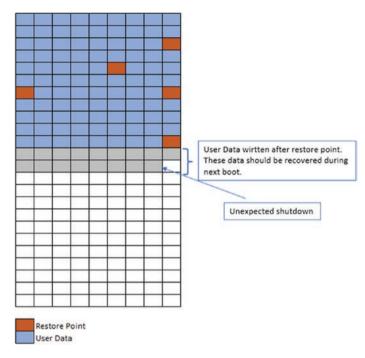

| Unexpected Shutdown                                         |     |

| Power-Loss Protection                                       |     |

| Power-Loss Design Considerations                            |     |

| Best Practices for Optimizing and Maintaining SSD Firmware  |     |

|                                                             |     |

| Summary                                                     |     |

| Chapter 9: Flash Translation Layer (FTL)      | 129 |

|-----------------------------------------------|-----|

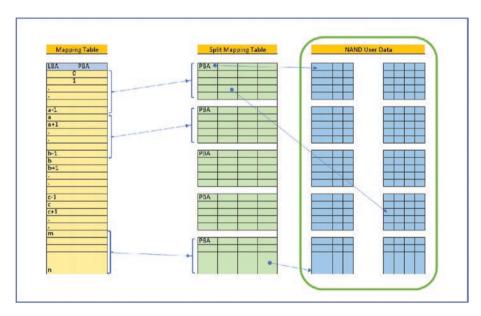

| Mapping Table                                 | 130 |

| Size of the Mapping Table                     | 131 |

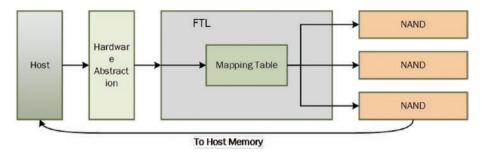

| Storing the Mapping Table in RAM              |     |

| Partial Loading of the Mapping Table          |     |

| Storage of Non-Loaded Mapping Entries         | 132 |

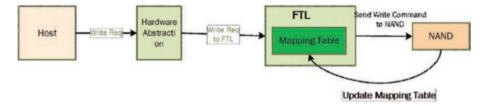

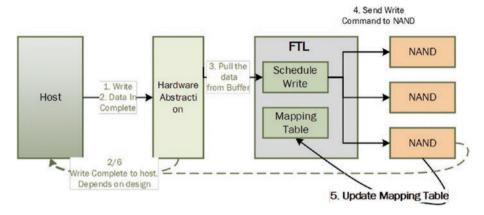

| Write/Update Operations and the Mapping Table | 133 |

| Dirty Cache Buffer in RAM                     | 133 |

| Mapping Table Management and Optimization     | 134 |

| Bad Block Management                          | 142 |

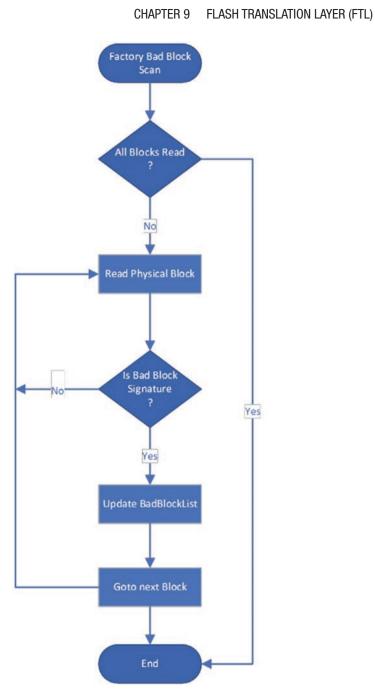

| Factory Bad Block Assessment                  | 142 |

| Bad Block Flash Address                       | 143 |

| Recording Bad Block Flash Address             | 143 |

| Initial Bad Block Handling Flow               | 143 |

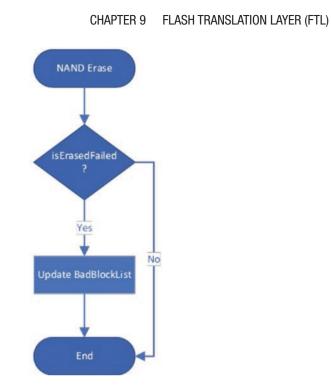

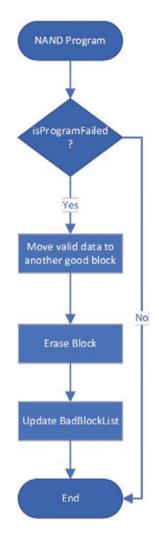

| Used Bad Block Assessment                     | 146 |

| Bad Block Skipping Strategy                   | 149 |

| Bad Block Replacement Strategy                | 149 |

| Summary                                       | 150 |

| Chapter 10: User Data Flow                    | 151 |

| Write Path                                    |     |

| Read Path                                     |     |

| Summary                                       | 153 |

| Chapter 11: Throttling                        | 155 |

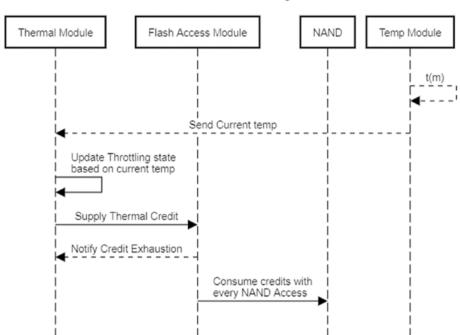

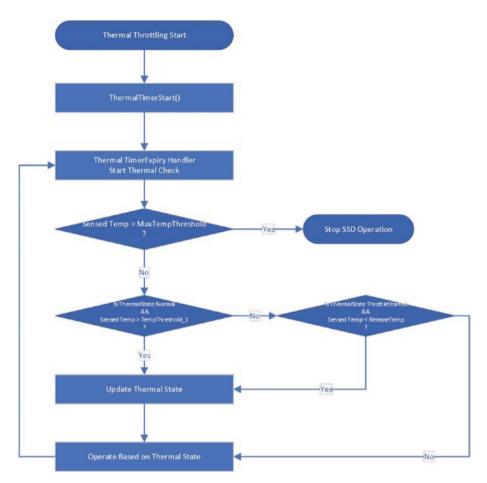

| Thermal Throttling                            |     |

| Temperature Monitoring                        |     |

| Throttling Mechanism                          |     |

| Temperature Recovery                          |     |

| Design Consideration                                                               | 156                      |

|------------------------------------------------------------------------------------|--------------------------|

| Power Throttling                                                                   | 158                      |

| Power Monitoring                                                                   | 158                      |

| Throttling Mechanism                                                               | 159                      |

| Power Recovery                                                                     | 159                      |

| Combined Throttling                                                                | 159                      |

| Synergistic Operation                                                              | 159                      |

| Priority Management                                                                | 159                      |

| Dynamic Performance Adjustments                                                    |                          |

| Workload Awareness                                                                 |                          |

| Logging and Reporting                                                              |                          |

| Event Logging                                                                      |                          |

| Health Monitoring                                                                  |                          |

| Summary                                                                            | 161                      |

|                                                                                    |                          |

| Chapter 12: Exception Handling                                                     | 163                      |

| Chapter 12: Exception Handling<br>Read Errors                                      |                          |

|                                                                                    | 163                      |

| Read Errors                                                                        | 163<br>164               |

| Read Errors                                                                        | 163<br>164<br>165        |

| Read Errors<br>Handling<br>Program Errors                                          | 163<br>164<br>165<br>165 |

| Read Errors<br>Handling<br>Program Errors<br>Handling                              |                          |

| Read Errors<br>Handling<br>Program Errors<br>Handling<br>Program Abort             |                          |

| Read Errors<br>Handling<br>Program Errors<br>Handling<br>Program Abort<br>Handling |                          |

| Read Errors                                                                        |                          |

| Chapter 13: Performance                              | 169 |

|------------------------------------------------------|-----|

| Access Patterns and Test Workloads                   | 170 |

| Workloads                                            |     |

| Host Interface                                       | 179 |

| Summary                                              |     |

| Chapter 14: Debugging                                | 181 |

| Summary                                              |     |

| Chapter 15: Future Developments and Innovations in S |     |

| Firmware                                             |     |

| Summary                                              |     |

| Chapter 16: Closing                                  | 191 |

| Bibliography                                         | 193 |

| Index                                                | 195 |

# **About the Author**

**Gopi Kuppan Thirumalai** is a highly experienced embedded design engineer with a proven track record of success in the industry. He has over 15 years of experience in a variety of domains, including wireless networks, software, automotive, and storage. He is an expert in client and datacenter SSD design and implementation and has a history of leading and mentoring teams to achieve their goals. He is also an outdoor enthusiast and enjoys hiking, fitness, reading books, and cooking.

# **About the Technical Reviewer**

Kenneth Fukizi is a software engineer, architect, and consultant with experience internationally in coding on different platforms. Prior to dedicated software development, he worked as a lecturer and was then head of IT at different organizations. He has domain experience working with technology for companies mainly in the financial sector. When he's not working, he likes reading up on emerging technologies and strives to be an active member of the software community.

Kenneth currently leads a community of African developers through a startup company called AfrikanCoder.

# **CHAPTER 1**

# Introduction to SSD Firmware

Welcome to the world of SSD firmware! This chapter marks the beginning of your journey into the intricate world of solid-state drive (SSD) firmware. In this chapter, I will lay the foundation by exploring the fundamental concepts and essential aspects of SSD firmware. My goal is to provide you with a clear understanding of what SSDs are, the role of firmware in optimizing their performance, and the key differences that set SSDs apart from traditional hard-disk drives (HDDs).

# What Is SSD?

A solid-state drive (SSD) is a type of storage device that uses flash memory to store data. Compared to traditional hard drives, which use spinning disks to store data, SSDs are much faster, more reliable, and more energy efficient. However, to take full advantage of the capabilities of an SSD, it is necessary to use specialized software known as SSD firmware. SSD firmware is the embedded software that controls the functions and features of an SSD. It is responsible for managing the storage, retrieval, and protection of data on the drive. SSD firmware is typically stored on the drive's non-volatile memory and is executed by the drive's controller when the drive is powered on. It plays a critical role in ensuring the reliable and efficient operation of an SSD.

© Gopi Kuppan Thirumalai 2023 G. Kuppan Thirumalai, *A Beginner's Guide to SSD Firmware*, https://doi.org/10.1007/978-1-4842-9888-6\_1

#### CHAPTER 1 INTRODUCTION TO SSD FIRMWARE

The first SSD, introduced in the late 1970s, used simple firmware that was primarily responsible for interfacing with the host system and translating its commands into actions on the drive. At the beginning, SSDs were introduced for use in early IBM supercomputers, but they were not often used due to their high cost. Over time, as SSD technology has evolved, the firmware has become increasingly complex, adding features such as wear leveling, garbage collection, and encryption. In addition, the capabilities of SSD firmware have improved over time to support larger SSDs, with current firmware able to support drives with capacities of up to 100 TB or more.

Today, SSD firmware is a crucial component of modern storage systems, providing numerous benefits over traditional hard disk drives (HDDs), such as faster access to data, higher reliability, and lower power consumption. It also enables advanced features such as data protection, power management, and error correction, which are essential for maintaining the integrity and performance of the drive.

Figure 1-1. Comparison of HDD and SSD

In addition to supporting larger SSDs, modern SSD firmware is also designed to improve the performance of the drive. For example, SSD firmware can optimize the process of reading and writing data to the drive, and it can also improve the reliability of the drive by using techniques such as error-correcting code (ECC) and wear leveling.

There are several different types of SSD that are commonly used, including data-center SSDs, client SSDs, external SSDs, and enterprise SSDs. Each of these types of SSD has its own unique set of requirements, and the firmware that is used with these drives is specifically designed to meet those requirements.

One important consideration when designing SSD firmware is the type of memory that is used in the drive. The most common types of memory used in SSDs are single-level cell (SLC), multi-level cell (MLC), triple-level cell (TLC), and quadruple-level cell (QLC). Each of these types of memory has its own unique characteristics, and the firmware that is used with the drive must be optimized to take advantage of those characteristics. SLC memory is generally considered to be the most reliable and robust type of memory, but it is also the most expensive. MLC, TLC, and QLC memory are generally less expensive than other types, but they are also less reliable and have lower endurance, meaning they can't withstand as much wear and tear (less P/E cycle (program/erase Cycle) compared to SLC). In addition, the firmware design and implementation for MLC, TLC, and QLC memory can be more complex compared to other types of memory. This means that the firmware used to control and manage the memory may be more intricate and require more effort to design and implement. In general, MLC, TLC, and QLC memory are less durable and more complex to work with compared to other types of memory, but they can be a costeffective option for certain applications.

Another important consideration when designing SSD firmware is the type of host interface that is supported. The host interface is the interface that connects the SSD to the rest of the system, and different interfaces have different performance characteristics. The most common types of host

#### CHAPTER 1 INTRODUCTION TO SSD FIRMWARE

interface for SSDs are SATA, USB, NVMe, and SAS (Serial-Attached Small Computer System Interface (SCSI). SATA is the most common and widely supported interface, but it has relatively low performance compared to other interfaces. NVMe is a newer interface that is designed specifically for highperformance storage devices, and it can provide much higher performance than SATA. USB is a universal interface that is commonly used for external storage devices, but it has lower performance than other interfaces. SAS is a high-performance interface that is commonly used in enterprise storage systems, but it is not as widely supported as SATA or NVMe.

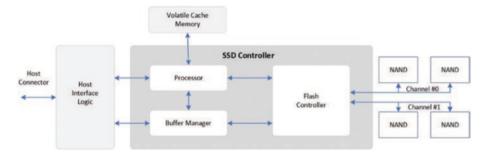

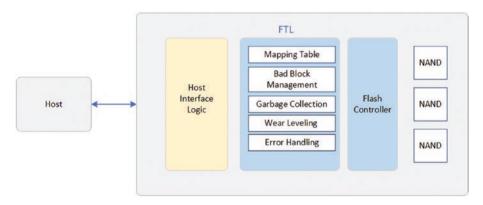

#### Figure 1-2. SSD block diagram

This book is a basic resource that covers the fundamental principles and technical aspects of SSD firmware and is designed to provide a basic understanding of the key concepts and technologies used in SSD firmware. The guide is divided into several chapters, each of which covers a different aspect of SSD firmware. The first few chapters provide an overview of SSD firmware, including the key features and benefits of SSDs and the ways in which they differ from traditional hard-disk drives (HDDs). These chapters help with understanding the role of the SSD firmware in managing the read and write operations of the drive and also dive into the history and evolution of SSD firmware.

The further chapters delve into the inner workings of SSD firmware, exploring fundamental NAND operations, various techniques for error correction, and strategies for endurance management. They also cover common SSD firmware features, design considerations, and the allimportant flash translation layer. The chapters then examine the flow of user data and exception handling in an SSD, as well as performance optimization and debugging support. Finally, the book concludes with a look to the future, examining the cutting-edge technologies and innovations that are shaping the future of SSD firmware.

This book may provide a valuable resource for anyone interested in understanding the technical details of SSD firmware basics and how firmware impacts the performance and reliability of solid-state drives. Whether you are a firmware engineer, a computer science student, or simply someone interested in learning more about SSDs, this book is sure to provide you with a basic information and insights.

# Summary

In this chapter, we covered the basics of SSD firmware. You have learned that SSD firmware is the software that controls the operation of an SSD. You have also learned that SSD firmware is responsible for tasks such as managing the wear leveling of the NAND flash memory, garbage collection, and error correction.

You have also learned about the different types of SSD that are commonly used, including data center SSDs, client SSDs, external SSDs, and enterprise SSDs. We have discussed the different types of memory that are used in SSDs, such as SLC, MLC, TLC, and QLC. We have also looked at the different types of host interfaces that are supported by SSDs, such as SATA, USB, NVMe, and SAS. This chapter set the stage for a deeper dive into the intricate workings of SSD firmware, promising insights into NAND operations, error correction techniques, performance optimization, and future innovations.

## **CHAPTER 2**

# Understanding the Role of Firmware in SSDs

Picture the hardware of a solid-state drive (SSD) as the engine of a car, and the firmware as the driver who controls and optimizes its performance. In the SSD world, firmware takes center stage, fine-tuning every interaction between the physical components and the digital world. This chapter embarks on a journey to unveil the firmware's pivotal role in SSDs, breaking down its intricate responsibilities and how it makes things happen.

# What Is Firmware?

For SSDs to work properly and help us with tasks, they rely on both hardware and firmware. The hardware consists of the physical components of the device, such as the processor, memory, and storage. The firmware, meanwhile, is the software that runs on the device and controls the hardware. It is responsible for ensuring that the device performs its designated tasks and functions properly.

#### CHAPTER 2 UNDERSTANDING THE ROLE OF FIRMWARE IN SSDS

The primary role of SSD firmware is to manage the storage, retrieval, and protection of data on the drive. Firmware is typically embedded into the hardware during the manufacturing process and is not intended to be modified by the user.

In SSDs, firmware plays a crucial role in the performance and functionality of the drive. It controls the various hardware components of the drive, such as the memory chips and interface controller, and manages the data stored on the SSD. Additionally, SSD firmware provides many advanced features that are essential for maintaining the performance and reliability of the drive. For example, it can include wear-leveling algorithms that distribute data evenly across the drive to prevent excessive wear on any one area of the drive, garbage-collection algorithms that reclaim unused space on the drive to improve performance, and algorithms to reduce write amplification. (Write amplification is a process that increases the amount of data written to the drive beyond the amount of data that the user writes.)

SSD firmware can also include encryption capabilities to protect data on the drive, as well as power-management functions to help conserve energy and extend the lifespan of the drive. These features are essential for modern SSDs, which are often used in high-performance computing environments and require the highest levels of data protection and reliability.

Additionally, SSD firmware is responsible for managing the internal data structures of the drive, such as the journaling data that is used to keep track of changes to the data on the drive. This allows the drive to recover from any errors or power failures that may occur.

Another important function of SSD firmware is to manage thermal throttling, which is the process by which the drive reduces its performance in order to prevent overheating. This can help to protect the drive from damage and extend its lifespan.

#### CHAPTER 2 UNDERSTANDING THE ROLE OF FIRMWARE IN SSDS

When we use our devices, they often run multiple programs at the same time. Over time, this can lead to a decrease in system performance and slower operation. One solution to this problem is to replace the hardware with new parts. However, this can be expensive and timeconsuming. A more cost-effective and simpler solution is to update the firmware that the system runs on. Firmware updates can fix bugs, improve performance, and add new features to the device, all without the need to replace any hardware.

Firmware updates for SSDs can be installed by the user and are typically available for download from the manufacturer's website. It is important to keep the firmware of an SSD up to date to get the most out of the drive and to ensure its proper functioning.

Updating the firmware on an SSD can bring several benefits, including improved performance, increased stability, and access to new features. For example, a firmware update may optimize the performance of the drive by improving instruction times, out-of-order execution, branch prediction, and speculative execution time. It may also fix bugs that have developed over time and prevent the need for expensive repairs or bug fixes in the future.

In addition to these benefits, updating the firmware on an SSD can help to prevent the drive from becoming obsolete. By adopting the additional functionalities and capabilities that come with the firmware update, users can ensure that their SSD remains compatible with newer technologies and is able to keep up with changing needs.

Finally, SSD firmware is responsible for managing the mapping of logical block addresses to physical block addresses on the drive. This is necessary because the data on the drive is typically organized into blocks, and the firmware must manage the mapping of these blocks to the actual physical locations on the drive where the data is stored. This is an essential part of the drive's overall performance and reliability.

# Summary

This chapter pulled back the curtain on the unsung hero of SSDs: firmware. Think of it as the conductor of an orchestra, ensuring each instrument (component) plays in harmony to create a beautiful symphony (performance). Firmware's primary job is to manage data storage, retrieval, and safeguarding. It makes sure no single spot on the drive wears out prematurely and reclaims space that's not being used. It even handles tricky maneuvers like reducing the amount of data written, thus extending the drive's lifespan. Firmware is also the brain behind encryption and energy-saving tricks, crucial in today's demanding computing world.

The chapter also highlighted firmware updates, like giving your car a software upgrade. These updates fine-tune the drive's performance, fix bugs, and even add new features without needing to swap parts. They're your SSD's way of staying sharp and relevant, much like updating your phone's software. Lastly, firmware's task of mapping logical data to physical locations was emphasized—the GPS of your SSD, ensuring data arrives at its destination smoothly. This chapter has shown that firmware is the true wizard behind the scenes of SSD engineering.

## **CHAPTER 3**

# The History and Evolution of SSD Firmware

In this chapter, we delve into the historical evolution of solid-state drive (SSD) firmware, tracing its journey from its rudimentary origins to its present-day complexities. Our exploration begins with the early days of SSD technology, when firmware was a modest tool focused on basic interfacing tasks. As time progressed, firmware transitioned into a powerhouse of advanced functionalities. Our analysis concludes by examining the contemporary challenges and innovative solutions that underscore the realm of SSD firmware engineering.

# History

The history of SSD firmware can be traced back to the early days of SSD technology, when the first SSDs were introduced in the late 1970s. At that time, SSD firmware was a relatively simple piece of software that was primarily responsible for interfacing with the host system and translating its commands into actions on the drive.

#### CHAPTER 3 THE HISTORY AND EVOLUTION OF SSD FIRMWARE

Early SSD firmware was focused on ensuring data integrity and reliability. This was important because early SSDs were prone to data loss due to the instability of its memory. To address this issue, early SSD firmware included basic features such as error-correction algorithms. These algorithms were used to detect and correct errors in the data stored on the drive, improving the reliability and integrity of the data.

Over the next several decades, as SSD technology continued to evolve, the firmware also evolved to include more advanced features and capabilities. For example, early SSDs lacked the wear-leveling algorithms that are now commonly found in modern drives, which distribute data evenly across the drive to prevent excessive wear on any one area of the drive.

Similarly, early SSDs did not have the garbage-collection algorithms that are now standard in modern drives, which reclaim unused space on the drive to improve performance. These and other advanced features were gradually added to SSD firmware as the technology matured and the demands on SSDs increased.

Today, SSD firmware is a crucial component of modern storage systems, providing numerous benefits over traditional hard-disk drives (HDDs), such as faster access to data, higher reliability, and lower power consumption. It also enables several advanced features, such as data protection, power management, and error correction, which are essential for maintaining the integrity and performance of the drive.

One of the main challenges in achieving high performance with SSDs is their tendency to become bogged down by random input/output (IO) operations (IO operations are tasks that involve reading or writing data from or to the SSD, such as when you save a file or load a program), which occurs when the drive receives a large number of small, random read and write requests. To address this issue, SSD firmware began to incorporate stream concepts, which involve grouping together related IO requests and processing them as a single, larger request. This can significantly improve the performance of the drive by reducing the number of small IO requests and allowing the drive to operate more efficiently.

Another important aspect of SSD firmware is IO determinism, which refers to the ability of the drive to consistently deliver predictable performance. In the early days of SSDs, the performance of the drive could vary greatly depending on the workload, leading to unpredictable and inconsistent results. Modern SSD firmware includes features such as host cache, which uses system memory to store frequently accessed data, allowing the drive to deliver more consistent and predictable performance.

In summary, the history of SSD firmware reflects the evolution of SSD technology itself. Starting with simple firmware that was primarily responsible for interfacing with the host system, it has gradually evolved to include a wide range of advanced capabilities that are critical for modern storage systems.

## Summary

This chapter has discussed the history and evolution of SSD firmware. We have seen how firmware has evolved from a simple piece of software to a complex and sophisticated piece of technology. We have also seen how firmware has helped to improve the performance, reliability, and efficiency of SSDs.

The chapter has also discussed some of the challenges that SSD firmware faces today. One of the main challenges is the need to improve the performance of SSDs under random IO conditions. Another challenge is the need to improve the IO determinism of SSDs.

Despite these challenges, SSD firmware continues to evolve and improve. As SSD technology continues to develop, we can expect to see even more advanced features and capabilities in the future.

## **CHAPTER 4**

# Basics of Flash Memory

In this chapter, we will discuss different memory types and delve into the world of flash memory, exploring its different types and focusing on two primary types: NAND and NOR flash memory. We will discuss the architecture of NAND flash memory and its fundamental operations, including reading, writing, and erasing data. Understanding these basic operations is crucial to grasp how NAND flash memory functions and how it is utilized in solid-state drive (SSD) firmware. By the end of this chapter, you will have gained valuable insights into the basics of flash memory, enabling you to comprehend its architecture and the fundamental operations it supports.

# **Memory Types**

Flash memory is a type of non-volatile memory that is used in a variety of electronic devices, including SSDs. Non-volatile memory can retain data even when the power is turned off, making it ideal for storing important information.

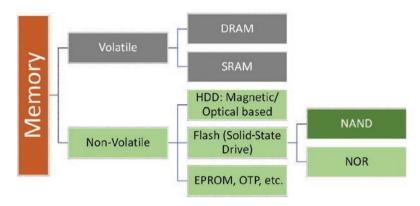

There are several different types of flash memory available, including NOR and NAND, as you can see in Figure 4-1.

#### CHAPTER 4 BASICS OF FLASH MEMORY

Figure 4-1. Memory types

# **NOR Flash Memory**

NOR flash memory is capable of random access, meaning that data can be read or written to any location on the memory chip. It is commonly used in devices that require fast access to small amounts of data. It is possible to read/write one byte of data at a time. Erase operation is in sector wise. NOR flash memory is less dense, meaning it consumes more physical area and costs more than NAND flash memory.

### **Characteristics of NOR Flash Memory**

The following are characteristics of NOR flash memory:

- Cost per bit is high.

- Code execution is easy.

- Capacity is low.

- Write speed is slower.

- Read speed is faster.

- Power consumption on standby is low.

#### **NOR Memory Architecture**

Take a look at the NOR memory architecture in Figure 4-2.

*Figure 4-2.* NOR memory architecture Source: Wikipedia

NOR memory is a type of flash memory that uses NOR gates to store data. The gates are arranged in a grid, with each gate storing a single bit of data. The grid is divided into words, with each word containing a fixed number of bits.

To read data from NOR memory, the controller sends a read command to the memory. The memory then transfers the data from the selected word to the controller.

To write data to NOR memory, the controller sends a write command to the memory. The memory then writes the new data to the selected word.

## NAND Flash Memory

NAND flash memory, however, is a type of flash memory that is optimized for high-capacity storage and fast data transfer. It is commonly used in SSDs and other storage devices, such as USB drives and memory cards. NAND memory is made up of tiny transistors that are arranged in a

#### CHAPTER 4 BASICS OF FLASH MEMORY

grid and can be used to store data in the form of bits (0s and 1s). It is fast and efficient, making it ideal for use in SSDs, and it is also relatively inexpensive and widely available.

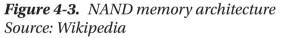

#### NAND Memory Architecture

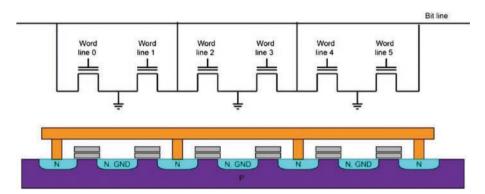

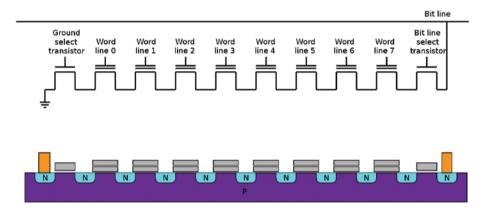

Take a look at the NAND memory architecture in Figure 4-3.

NAND memory is a type of flash memory that uses floating-gate transistors to store data. The transistors are arranged in a grid, with each transistor storing a single bit of data. The grid is divided into pages, with each page containing a fixed number of bits.

To read data from NAND memory, the controller sends a read command to the memory. The memory then transfers the data from the selected page to the controller.

To write data to NAND memory, the controller sends a write command to the memory. The memory then erases the selected page and writes the new data to the page.

# Similarities

NAND and NOR memory are both types of flash memory. They both use transistors to store data, and they both have a grid-like structure.

# Differences

The main difference between NAND and NOR memory is the way that they store data. NAND memory uses floating-gate transistors, while NOR memory uses NOR gates. This difference in the way that they store data affects the performance and the features of the two types of memory.

NAND memory is generally faster than NOR memory, but it is also more expensive. NAND memory is also more durable than NOR memory.

NOR memory is slower than NAND memory, but it is also less expensive. NOR memory is also easier to program than NAND memory.

# Source Line Word Line Control Gate Float Gate N P N

# **A Flash Memory Cell**

Figure 4-4. A flash memory cell

#### CHAPTER 4 BASICS OF FLASH MEMORY

Flash memory, which is used in SSDs, combines the characteristics of ROM (read-only memory) and RAM (random access memory). It can retain information even when there is no power, like ROM, and it can be repeatedly erased and rewritten, like RAM. This is made possible through the use of a special type of transistor in flash memory.

Let's break down how it works in a simplified manner, as follows:

- 1. Typical Transistors: In typical memory transistors, there are three connections: source, drain, and gate. The source is where electricity enters, the drain is where it exits, and the gate controls the flow. When the gate is closed, no current can flow, turning the transistor off and storing a zero (0). When the gate is open, power flows through, activating the transistor and storing a one (1).

- 2. Limitations of Typical Transistors: However, a typical transistor cannot remember its state when the power is switched off. When power is turned back on, it's difficult to determine whether the transistor was on or off before the power was removed.

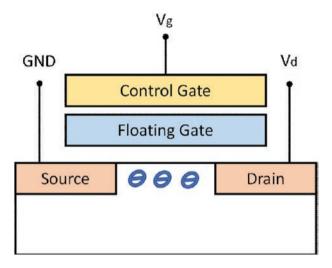

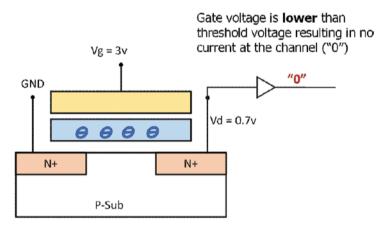

- 3. Flash Memory Transistors: Flash memory transistors have an additional connection called a floating gate. This floating gate is placed on top of the main gate. When the gate is open, electricity seeps through the first gate and remains trapped between the first and second gates, even when the power is off. Refer to Figure 4-5.

- 4. Retaining Information: The floating gate in flash memory allows it to remember its state even when the power is off. If you try to push current

through the transistor, the stored energy prevents it, representing a zero. Clearing the stored energy allows the current to flow, representing a one. This way, the flash transistor retains information regardless of whether the power is on or off.

Figure 4-5. Floating gate NMOS transistor

Figure 4-6. Programming floating gate NMOS transistor

#### CHAPTER 4 BASICS OF FLASH MEMORY

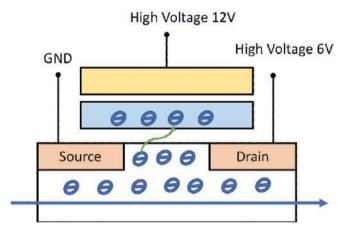

Figure 4-7. Erasing floating gate NMOS transistor

Figure 4-8. Reading floating gate NMOS transistor

| Operation | Gate | Drain | Source | Bulk |

|-----------|------|-------|--------|------|

| Read      | 4.5  | SA    | 0      | 0    |

| Program   | 8.0  | 5.0   | 0      | 0    |

| Erase     | -8.0 | Float | 8.0    | 8.0  |

**Table 4-1.** Cell Node Voltages Required in DifferentMemory Operations

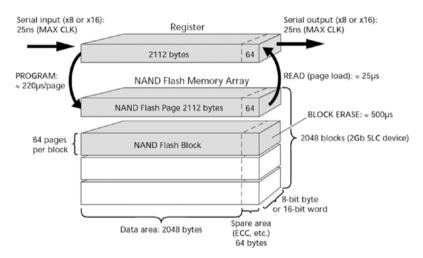

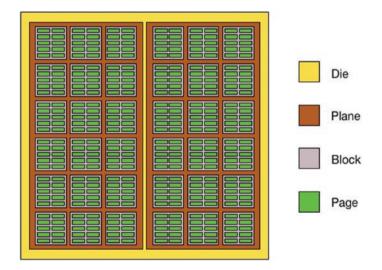

# **NAND Memory Organization**

- The package is the memory chip, which contains one or more dies.

- The die is the smallest unit that can independently execute commands and report status.

- Each die contains one or more planes. Identical, concurrent operations can take place on each plane, although with some restrictions.

- Each plane contains a number of blocks, which are the smallest unit that can be erased. Remember that, as it's really important.

- Each block contains a number of pages, which are the smallest unit that can be programmed.

#### CHAPTER 4 BASICS OF FLASH MEMORY

## Addressing

It is NAND memory addressing. How physical nand can be addressed or accessed by Firmware.

*Figure 4-9. The organizational structure of a NAND flash device Source: Micron Technology Inc.*

*Figure 4-10.* NAND flash die layout Source: AnandTech

# **Erase**

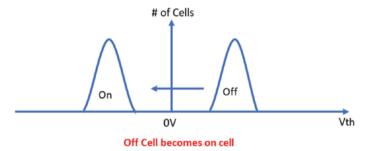

In a flash memory device, the erase operation is responsible for changing the state of a cell from "0" to "1" by removing electrons from the floating gate. It is important to note that a single cell cannot be directly changed from "1" to "0"; instead, the erase operation must be performed on a block-by-block basis. This means that before new data can be written to a block (through the programming process), the block must first be erased to ensure that it is empty. It is worth noting that the erase operation typically has a longer latency than the read and program operations, meaning it can take longer to complete. For example, the read, program, and erase latencies for a Micron 8 GB flash chip are 25  $\mu$ s, 220  $\mu$ s, and 1500  $\mu$ s, respectively. As a result, the erase operation can be a performance bottleneck in NAND flash memories, and various firmware algorithms have been developed to minimize the impact of the long erase latency on overall performance.

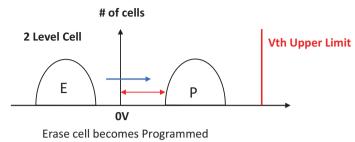

Figure 4-11. Erase level Vth distribution

# Write

The program operation is performed on a page level. This means that the operation targets a specific page of memory on the drive. When the controller of the SSD requests a program operation on the NAND device, it specifies the chip select (CE) and provides the row address of the page

#### CHAPTER 4 BASICS OF FLASH MEMORY

to be targeted. The controller then transfers the data to be programmed to the NAND device and sends a final program command to complete the operation.

It is important to note that a page on an SSD cannot be written more than once without first performing an erase operation. This is because an erase operation is required to clear the page of any existing data before new data can be written to it. As a result, every time a program operation is performed on a page, it must be preceded by an erase operation. This ensures that the page is ready to accept new data and that the program operation is successful.

It is also important to say that pages need to be written in consecutive order within the block; page number 0 is to be written first followed by page 1. Writing out of sequence is not allowed, as violating this rule aggravates the bit error rate. A single block does not need to be written all at once. That is, a block can be written with pages from 0 to 11, and later on with pages from 12 to 32, for example. Generally, pages need to be written as a whole at once, though some memories support so-called *partial page programming*, which allows a subpage of 512 bytes + correlated spare area to be written.

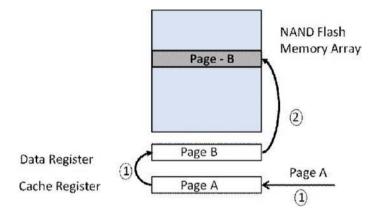

The data to be written will be provided by the host or result from firmware internal data management. Firmware first transfers the data from cache to the NAND internal cache register. Once the data transfer is completed the programming should start; i.e., writing to actual NAND cells.

Figure 4-12. Program level Vth distribution

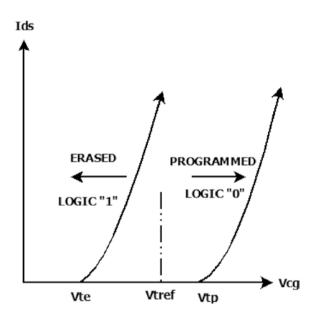

Figure 4-13. Read sensing graph

#### CHAPTER 4 BASICS OF FLASH MEMORY

From the perspective of the NAND chips themselves, the read operation involves activating the appropriate word line to select the desired page of cells, and then reading the data stored in those cells by sensing the voltage levels on the bit lines. The NAND chips are organized into blocks, which are further divided into pages. Each page stores a fixed amount of data, typically 4 KB to 16 KB (or more), depending on the specific NAND device.

To read a specific page, the controller must first locate the block that contains the page and then activate the appropriate word line to select the page within that block. The read operation is typically performed by the SSD's controller, which uses firmware to manage the communication with the NAND chips and handle the necessary data transfer and error correction. The firmware is responsible for optimizing the read performance by minimizing the number of accesses required and maximizing the data transfer rate.

| Operation | Area  | Time (Example) |  |  |

|-----------|-------|----------------|--|--|

| Erase     | Block | 500 us         |  |  |

| Write     | Page  | 220 us         |  |  |

| Read      | Page  | 25 us          |  |  |

Table 4-2. NAND Basic Operations Timings

# Program/Erase Cycle (P/E Cycle)

The program/erase (P/E) cycle is a fundamental aspect of NAND flash memory, which is commonly used in SSDs. NAND flash memory works by storing data in cells that are grouped into blocks. Each cell can store a single bit of data, and a group of cells is needed to store a larger amount of data. To write new data to a cell, the cell must first be erased, which is done by applying a high voltage to the cell. As we already explained, this process is known as the erase cycle. Once the cell has been erased, new data can be written to it using a process called programming, which involves applying a lower voltage to the cell. The process of writing new data to a cell by first erasing it and then programming it with new data is known as the P/E cycle. The P/E cycle is a key factor in the endurance of NAND flash memory, as the erase cycle can cause wear on the cells over time. As a result, NAND flash memory has a limited number of P/E cycles that it can withstand before it begins to degrade. This is known as the endurance of the memory.

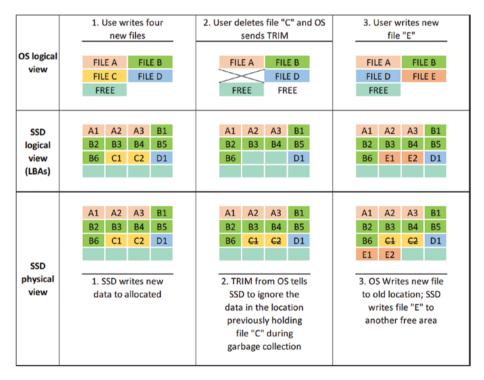

To extend the endurance of NAND flash memory, it is important to minimize the number of P/E cycles that the memory undergoes. One way to do this is to use the TRIM command, which allows the operating system to inform the SSD which data blocks are no longer in use and can be erased. This can reduce the number of P/E cycles by eliminating the need to move invalid data during the garbage-collection process, which is an internal SSD housekeeping operation that manages and maintains available storage space.

The number of bits that can be stored in each cell of a NAND flash memory drive can also affect the maximum number of program/erase (P/E) cycles that the drive can support. Table 4-3 provides an overview of the different types of NAND cells based on the number of bits they can store.

| Cell type               | Bits per cell | Supported P/E cycles |  |  |

|-------------------------|---------------|----------------------|--|--|

| Single-level cell (SLC) | 1             | 100,000              |  |  |

| Multi-level cell (MLC)  | 2             | 10,000 - 30,000      |  |  |

| Triple-level cell (TLC) | 3             | 3,000 - 5,000        |  |  |

| Quad-level cell (QLC)   | 4             | 1,000 - 3,000        |  |  |

Table 4-3. PEC Cycle Based on NAND Cell Type

#### CHAPTER 4 BASICS OF FLASH MEMORY

As the number of bits per cell increases, the number of supported P/E cycles tends to decrease. Single-level cell (SLC) NAND, which can store one bit per cell, generally has the highest endurance, while quad-level cell (QLC) NAND, which can store four bits per cell, has the lowest endurance. It is important to consider the endurance of an SSD when selecting a drive, as a drive with a lower endurance may not be suitable for use in cases that involve a high number of P/E cycles.

# Summary

This chapter has discussed the basics of flash memory, including its different types, architecture, and fundamental operations. We have seen how NAND flash memory works and how it is used in SSDs. We have also seen the different types of operations that can be performed on NAND flash memory, such as erase, program, and read. We have also discussed the P/E cycle, which is a key factor in the endurance of NAND flash memory.

# **CHAPTER 5**

# **3D Vertical NAND**

Now, welcome to the exciting world of 3D vertical NAND! In this chapter, we will cover a cutting-edge technology that has revolutionized the way we store data. 3D vertical NAND is a remarkable advancement in NAND flash memory, allowing us to stack memory cells vertically to increase storage capacity and performance significantly.

You might be wondering how this technology works and what makes it so special. We will walk through the basics of 3D vertical NAND, explaining its unique architecture and how it overcomes the limitations of traditional 2D planar NAND. You'll discover the advantages and benefits of this innovative technology, along with its real-world applications and the impact it has on various industries.

By the end of this chapter, you will have a clear understanding of how 3D vertical NAND works and how it has transformed data storage, making it a technology crucial to modern electronic devices. So, let's dive in and explore the fascinating world of 3D vertical NAND!

# **Evolution of 3D Vertical NAND Technology**

The rapid growth in data traffic globally is pushing the boundaries of NAND flash memory technology. The industry-standard 2D planar NAND technology has inherent limitations when it comes to expanding storage capacity without compromising performance and reliability. This has created a need for innovative solutions to meet the increasing demands for data storage.

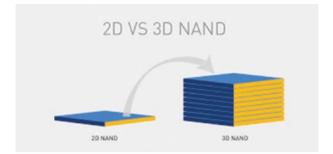

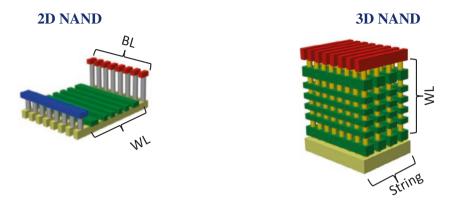

To address these challenges, the industry has introduced a groundbreaking approach known as 3D vertical NAND (V-NAND) flash memory technology. This innovation has revolutionized the design and architecture of NAND flash memory by stacking memory cells vertically in a three-dimensional structure, as opposed to the traditional two-dimensional planar arrangement. This vertical stacking allows for the creation of multiple layers of memory cells, resulting in significantly higher memory capacities (Figure 5-1).

By adopting a 3D V-NAND structure, the industry has overcome the limitations associated with capacity expansion in 2D planar NAND technology. This vertical stacking not only enables higher storage densities but also eliminates performance and reliability issues caused by capacity constraints. With more memory cells packed into each chip, the industry has achieved remarkable advancements in storage capacity while maintaining or even enhancing performance and reliability characteristics.

The vertical stacking of memory cells in 3D V-NAND technology offers several advantages. First, it allows for increased memory capacity within a smaller physical footprint, which is particularly beneficial in applications where space is a constraint. Additionally, the three-dimensional structure enables better control of electrical properties, resulting in improved performance and endurance.

This innovation in flash memory technology has had a significant impact on the storage industry, enabling the development of high-capacity solid-state drives (SSDs) that can handle the ever-growing volumes of data. The adoption of 3D V-NAND technology has facilitated advancements in areas such as cloud computing, data centers, mobile devices, and other storage-intensive applications.

Figure 5-1. 2D vs. 3D NAND comparison block diagram

# Unlocking New Possibilities with Vertical NAND Architecture

Figure 5-2 compares the storage density of 2D planar NAND and 3D V-NAND flash memory. As shown, 3D V-NAND can achieve up to 10x greater storage density than 2D planar NAND. This is because 3D V-NAND stacks memory cells vertically on top of each other, while 2D planar NAND stacks memory cells horizontally on a silicon wafer.

The higher storage density of 3D V-NAND allows for larger capacity NAND chips to be produced. This has made it possible to create NAND flash memory devices such as solid-state drives (SSDs) and USB flash drives with capacities of several terabytes.

Figure 5-2. Bird's-eye view of the V-NAND structure

In the pursuit of fitting more memory cells into a smaller space, the limitations of 2D planar NAND flash memory become evident. The shrinking size makes it challenging for light to penetrate the mask and transfer the desired pattern onto the photoresist, ultimately hindering the patterning process. This inherent limitation restricts the widespread use of 2D planar NAND flash memory in today's demanding memory landscape.

However, 3D V-NAND overcomes these patterning limitations by adopting a vertical architecture. Unlike the close proximity of cells in 2D planar NAND, 3D V-NAND creates a wider gap between each cell, enabling efficient patterning. While the cell-to-cell spacing in traditional planar NAND typically ranges from 15 to 16 nanometers (nm), 3D V-NAND offers an impressive 30nm to 40nm of space between cells, revolutionizing NAND flash technology.

This vertical architecture has opened new doors for memory advancement, allowing for higher capacities and enhanced performance. By overcoming the constraints of patterning, 3D V-NAND flash memory has become a game-changer in the industry, meeting the demands of today's memory-intensive applications.

Figure 5-3. 2D planar NAND vs. 3D Vertical NAND

# **Advantages of 3D Vertical NAND**

3D vertical NAND has several advantages over traditional planar NAND, as follows:

- a. Higher Storage Capacities: The vertical stacking of memory cells enables significant increases in storage capacities. With more layers of cells, 3D

V-NAND offers the potential for greater memory densities, allowing for storage devices with larger capacities.

- b. Improved Performance: 3D V-NAND can deliver enhanced read and write speeds compared to 2D planar NAND. The vertical structure reduces the distance that signals need to travel, resulting in faster data access and transfer rates.

- c. Enhanced Endurance: Vertical NAND architecture improves the endurance of the memory cells. The increased space between cells reduces interference, leading to improved reliability and longevity.

- d. Energy Efficiency: 3D V-NAND technology offers improved energy efficiency, allowing for longer battery life in portable devices and reduced power consumption in data centers.

# **Applications of 3D Vertical NAND**

The advantages offered by 3D vertical NAND make it well suited for various applications, including the following:

- a. Solid-State Drives (SSDs): SSDs equipped with 3D V-NAND deliver high-speed data storage and retrieval, making them ideal for use in laptops, desktops, and enterprise storage solutions. The increased storage capacity enables SSDs to meet the demands of modern data-intensive applications.

- b. Mobile Devices: Smartphones, tablets, and other portable devices benefit from the compact size and high storage capacities of 3D V-NAND. These devices require reliable and fast storage solutions to handle multimedia content, applications, and operating systems.

- c. Data Centers and Cloud Computing: The scalability and performance of 3D V-NAND make it a valuable technology for data centers and cloud computing environments. The increased storage densities and improved reliability contribute to efficient data management and faster processing speeds.

## Understanding 3D Vertical NAND Architecture

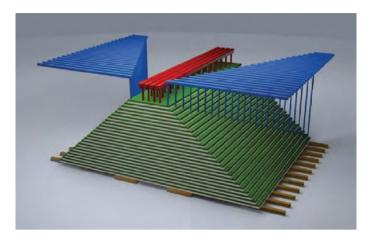

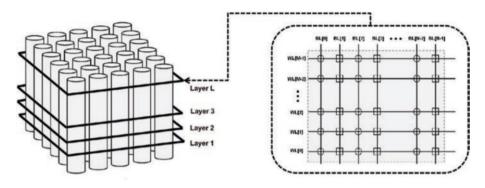

Figure 5-4. 3D vertical NAND layered architecture

The unique architecture of 3D vertical NAND involves intricate vertical cell stacking and layering, which enables higher storage density and better performance. A block consists of vertically stacked layers of NAND flash cells, each consisting of grid of cells connected by Wordlines (WLs) and Bit Lines (BLs).

The vertical cell stacking approach ensures that more memory cells can be packed in a smaller space. This is achieved by placing multiple layers of memory cells on top of each other, making the most efficient use of available silicon area.

Each memory cell in 3D vertical NAND still consists of a transistor and a floating gate, just like in traditional NAND flash memory. However, the arrangement of these components is optimized for vertical stacking.

### Layers and Pages

A 3D vertical NAND chip is composed of multiple layers, and each layer is divided into pages. Within a layer, pages are accessed individually for read and write operations. The vertical stacking of pages allows for greater memory capacity without increasing the chip's physical size.

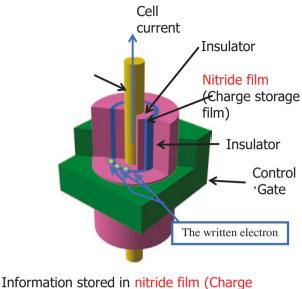

## **Charge Trapping Technology**

In 3D vertical NAND, memory cells use a charge trapping technology, unlike the floating-gate technology found in traditional NAND. Charge trapping stores charge in a non-conductive layer, preventing data loss due to electron leakage, which was a challenge in floating-gate technology. This enhanced data retention capability contributes to the reliability and longevity of 3D vertical NAND.

The 3D vertical NAND cell (also known as a V-NAND cell) is a type of NAND flash memory cell that is stacked vertically on top of other NAND flash memory cells. This allows for significantly greater storage density than traditional 2D planar NAND cells, which are stacked horizontally on a silicon wafer.

As shown in Figure 5-5, the 3D vertical NAND cell consists of three main components:

The charge storage film: This layer is made of a material that can trap electrons. The number of electrons trapped in this layer determines the state of the cell (0 or 1).

The control gate: This gate is used to control the flow of electrons into and out of the charge trap layer.

The channel layer: This layer is made of a semiconducting material that allows electrons to flow through it.

#### 3D Vertical NAND Cell

Trap: insulator)

Cell current (Ic)

#### Figure 5-5. 3D NAND cell

To store a bit of data in a 3D vertical NAND cell, a voltage is applied to the control gate. This causes electrons to flow into or out of the charge trap layer, depending on the desired state of the cell. Once the desired state has been achieved, the voltage is removed and the electrons are trapped in the charge trap layer.

The 3D vertical NAND cell is a highly efficient way to store data. It offers significantly greater storage density than traditional 2D planar NAND cells, while also being more energy-efficient. This makes it the ideal choice for a wide range of applications, including solid-state drives (SSDs), USB flash drives, and mobile devices.

### **Bit Line and Word Line Architecture**

The bit lines and word lines form the essential structure of 3D vertical NAND. Bit lines run vertically through all layers, connecting the memory cells within a column. Word lines, however, run horizontally, connecting the memory cells across a row in each layer.

### **Control and Decoding Circuits**

Control and decoding circuits are responsible for managing the flow of data in 3D vertical NAND. These circuits decode address inputs, control the selection of memory cells during read and write operations, and handle other essential functionalities.

### Memory Cell Size and Density in 3D Vertical NAND Flash Memory Technology

3D vertical NAND (V-NAND) flash memory technology is a type of nonvolatile memory that stacks memory cells vertically to increase storage density and capacity. One of the factors that affects the density and capacity of V-NAND chips is the size of the memory cells. As technology advances, manufacturers can reduce the size of the memory cells to fit more of them in a given area, resulting in higher density and larger capacity NAND chips. However, shrinking the cell size also poses some challenges, such as increased interference and reduced reliability. To overcome these challenges, V-NAND technology uses techniques such as charge trap flash (CTF) and tunnel field-effect transistor (TFET) to improve the performance and endurance of the memory cells. Moreover, V-NAND technology can also use different levels of charge to store multiple bits per cell, such as quad-level cell (QLC) or even higher, to further increase the storage capacity of NAND chips.

# Understanding NAND Cell Types Supported: SLC, MLC, and TLC (QLC)

There are different types of memory cells, including SLC (single-level cell), MLC (multi-level cell), and TLC (triple-level cell). Each cell type comes with its own characteristics, influencing how data is stored, accessed, and managed. We'll discuss the principles of reading, writing, and erasing data from 3D vertical NAND flash.

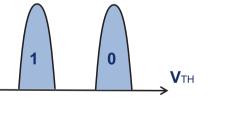

# SLC

3D vertical NAND SLC Vth distribution refers to the distribution of threshold voltages (Vth) of the memory cells in a 3D vertical NAND SLC flash memory device. Vth is a critical parameter that determines the performance and reliability of a NAND flash memory device. A narrow Vth distribution is desirable, as it indicates that all of the memory cells have similar Vth values. This makes it easier to read and write data to the memory cells, and it also reduces the risk of errors.

Single Level Cell (SLC)

Figure 5-6. 3D vertical NAND SLC Vth distribution

• 2 States (1 Erase + 1 Program) = 1 bit of information per cell

# MLC

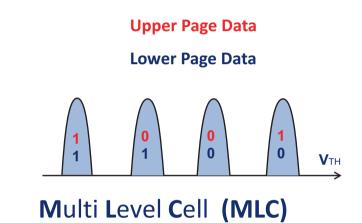

3D vertical NAND MLC Vth distribution refers to the distribution of threshold voltages (Vth) of the memory cells in a 3D vertical NAND MLC flash memory device. MLC NAND flash memory devices can store more than one bit (2-4) of data per memory cell, which requires a wider Vth range than SLC NAND flash memory devices. However, a narrow Vth distribution is still desirable for MLC NAND flash memory devices, as it improves performance and reliability.

Figure 5-7. 3D vertical NAND MLC Vth distribution

- 4 States (1 Erase + 3 Program)

- = 2 bits of information per cell

- = 2x capacity of SLC!

# TLC

**Upper Page Data Middle Page Data Lower Page Data** 0 0 0 0 0 1 1 0 1 0 1 0 0 VTH

### Triple Level Cell (TLC)

Figure 5-8. 3D vertical NAND TLC Vth distribution

8 States (1 Erase + 7 Program)

- = 3 bits of information per cell

- = 1.5x capacity of MLC

- = 3.0x capacity of SLC

# Read and Write Operations in 3D Vertical NAND

3D vertical NAND exhibits remarkable read and write operations owing to its unique vertical architecture. During a read operation, the control gate voltage is adjusted, allowing the flow of current through the memory cell. The resulting current state is then sensed to determine the stored data. The vertical stacking of memory cells enables faster read operations by reducing the distance the current needs to travel, resulting in reduced read latency.

Write operations in 3D vertical NAND involve programming the memory cell to store data. The voltage applied to the control gate elevates the electron energy in the floating gate, causing the charge to be trapped, representing either a 0 or 1. The vertical architecture enhances write performance by reducing the parasitic capacitance between memory cells, enabling faster and more efficient write operations.

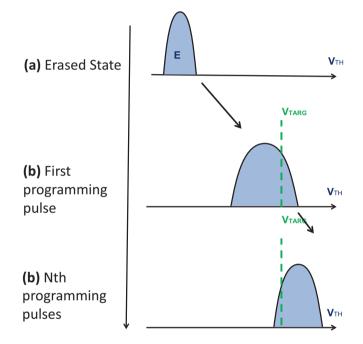

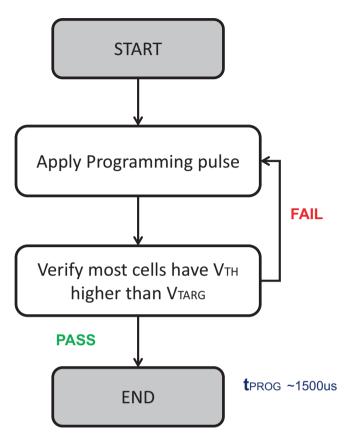

Figure 5-9. 3D vertical NAND SLC incremental programming pulse

*Figure 5-10.* 3D vertical NAND SLC incremental programming pulse flow chart

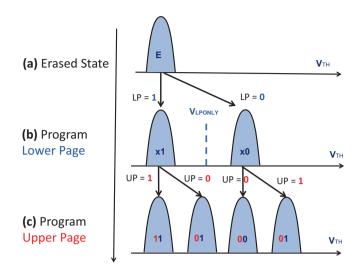

Figure 5-11. 3D vertical NAND MLC program sequence

- Data is programmed to the device one page at a time.

- The cells are either left in the erased state or programmed to an intermediate state, depending on the lower page data.

- An intermediate read determines the previously programmed lower page data, and the cell distribution for the WL is "finalized" using the upper page data.

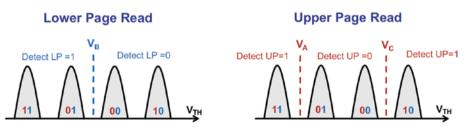

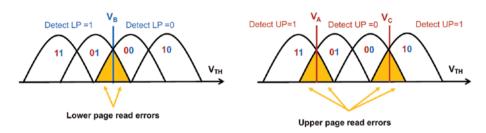

Figure 5-12. Reading data from 3D vertical NAND MLC

- Lower page can be read using a single read voltage (VB).

- Upper page can be read using a pair of read voltages (VA,VC).

- A page read (from NAND cell to NAND cache) typically takes up to 100us.

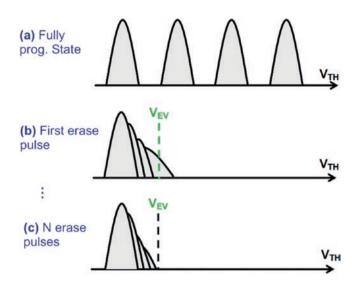

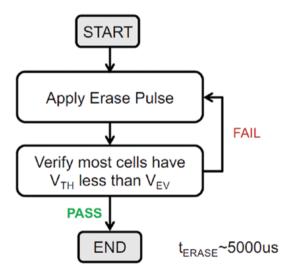

### **Erasing MLC 3D vertical NAND block**

Erasing an MLC 3D vertical NAND block is the process of resetting all of the memory cells in the block to the same state. This is done by applying a high voltage to the block. The high voltage causes electrons to flow out of the charge trap layers in the memory cells, erasing the data.

Erasing MLC 3D vertical NAND blocks is more complex than erasing SLC NAND blocks because of the wider Vth range of MLC memory cells. To ensure that all of the memory cells in an MLC block are properly erased, the erase voltage must be carefully controlled.

There are a number of different methods for erasing MLC 3D vertical NAND blocks. One common method is to use a partial erase scheme. In a partial erase scheme, the erase voltage is gradually increased until all of the memory cells in the block are erased. This method is more energyefficient than erasing the block at a single high voltage, but it takes longer.

Another method for erasing MLC 3D vertical NAND blocks is to use a full erase scheme. In a full erase scheme, the erase voltage is set to a high value for a fixed period of time. This method is faster than a partial erase scheme, but it consumes more energy.

The best method for erasing MLC 3D vertical NAND blocks depends on the specific application. For example, applications that require high performance may be willing to sacrifice some energy efficiency in order to achieve faster erase times.

Figure 5-13. Erasing MLC 3D vertical NAND block

Figure 5-14. Flow Diagram for 3D vertical NAND block erase MLC

# **Endurance and Data Retention Capabilities**

Endurance and data retention are crucial aspects of NAND flash memory. 3D vertical NAND excels in both areas due to its improved memory cell design and materials. The vertical structure reduces crosstalk and interference between memory cells, leading to improved data-retention capabilities. As a result, data stored in 3D vertical NAND remains intact for longer periods, even under challenging conditions.

Additionally, the vertical stacking design contributes to enhanced endurance by reducing wear on individual memory cells. This translates to a higher number of program-erase cycles before memory cell degradation, making 3D vertical NAND a reliable choice for data-intensive applications that require frequent read and write operations.

# Speed and Efficiency Compared to 2D Planar NAND

Compared to traditional 2D planar NAND, 3D vertical NAND offers notable speed and efficiency advantages. The vertical stacking of memory cells results in shorter electrical pathways, reducing data access times and improving overall system performance.

With faster read and write operations, 3D vertical NAND outperforms 2D planar NAND in data access speed, making it an excellent choice for applications requiring real-time data processing. Moreover, the improved efficiency of 3D vertical NAND contributes to lower power consumption, leading to energy savings and prolonged battery life in portable devices.

# Advancements in Storage Capacity with 3D Vertical NAND

One of the most significant achievements of 3D vertical NAND is the substantial advancement in storage capacity. The vertical cell stacking allows for a more efficient use of space, enabling the integration of multiple memory-cell layers within the same footprint.

As a result, 3D vertical NAND-based data storage solutions can achieve much higher capacities compared to traditional 2D planar NAND devices. This breakthrough has enabled the development of solid-state drives (SSDs) and memory modules with unprecedented storage capabilities, catering to the ever-growing demands of data-intensive applications.

# Summary

With this very brief chapter on 3D Vertical NAND, we have covered the basics only. As you delve into this exciting field of advanced memory technology, you will gain a deeper understanding of how 3D vertical NAND is revolutionizing data storage and setting the stage for future innovations in the semiconductor industry. As engineers and developers, your expertise in harnessing the capabilities of 3D vertical NAND will be instrumental in creating next-generation storage solutions that cater to the evolving needs of our data-driven world. Embrace the power of 3D vertical NAND and unlock the endless possibilities it holds for shaping the future of storage technology from here.

### **CHAPTER 6**

# Basic Understanding of NAND Flash Interface

In this chapter, we will examine the fundamental aspects of NAND flash memory and explore how it can be effectively utilized in embedded systems and be made into a product. We will delve into the essential aspects of NAND flash communication, including the commands it supports, data transfer procedures, commands, response packet information, and much more. By understanding the key features of NAND flash, engineers can leverage its power, density, and cost advantages to create efficient and reliable subsystems for various applications, including solid-state drives (SSDs), mobile phones, flash memory cards, USB flash drives, and audio/video players.

NAND flash supports a set of specific commands that facilitate various operations, such as read, write, erase, and status checking. We will thoroughly examine each command, its purpose, and the relevant response packet information. A clear understanding of these commands is crucial for effectively managing data access and storage in NAND flash memory.

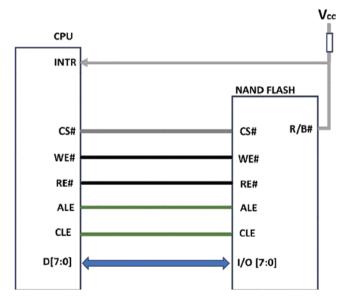

# **Basic NAND IO Interfacing Pin Details**

| PIN      | Description                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| CE#      | Chip enable<br>CE# serves as the chip enable signal for the NAND flash device. When CE# is not<br>asserted (held high), the NAND flash remains in standby mode and does not respond<br>to any control signals. Activating CE# allows the device to operate and respond to<br>commands.                                                                            |  |  |  |  |  |

| WE#      | Write enable<br>WE# is responsible for clocking data, address, or commands into the NAND flash<br>device. When WE# is low, data, addresses, or commands are written to the device,<br>and the relevant information is latched into the internal registers.                                                                                                        |  |  |  |  |  |