## Maurizio Palesi · Masoud Daneshtalab Editors

# Routing Algorithms in Networks-on-Chip

Routing Algorithms in Networks-on-Chip

Maurizio Palesi • Masoud Daneshtalab Editors

## Routing Algorithms in Networks-on-Chip

*Editors* Maurizio Palesi Facoltà di Ingegneria Kore University of Enna Cittadella Universitaria Enna, Italy

Masoud Daneshtalab Department of IT University of Turku Turku, Finland

ISBN 978-1-4614-8273-4 ISBN 978-1-4614-8274-1 (eBook) DOI 10.1007/978-1-4614-8274-1 Springer New York Heidelberg Dordrecht London

Library of Congress Control Number: 2013950182

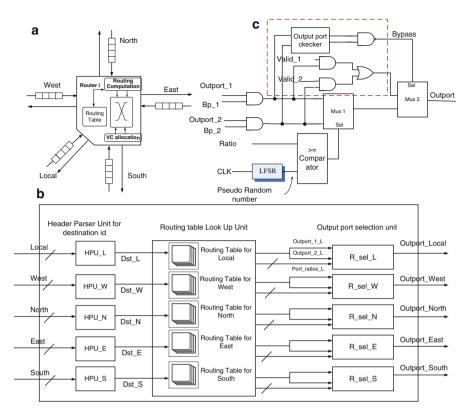

#### © Springer Science+Business Media New York 2014

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed. Exempted from this legal reservation are brief excerpts in connection with reviews or scholarly analysis or material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. Duplication of this publication or parts thereof is permitted only under the provisions of the Copyright Law of the Publisher's location, in its current version, and permission for use must always be obtained from Springer. Permissions for use may be obtained through RightsLink at the Copyright Clearance Center. Violations are liable to prosecution under the respective Copyright Law.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

While the advice and information in this book are believed to be true and accurate at the date of publication, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

### Foreword

In the year 2000 when the idea of Networks on Chip (NoC) was proposed, many people looked at it sarcastically as "bizarre," "too complicated," and "unacceptably inefficient." In a few years they were proved wrong. But even the greatest optimists did not predict that this new paradigm, for designing inter-core connections for multi-core systems using packet-switched communication, will get unanimous endorsement from academicians as well as semiconductor industries in just a matter of 10 years. But it has happened with the announcement of NoC-based 48-core chip by Intel. Now annually there are many international workshops and special track sessions held in important international conferences specifically dealing with issues related to NoC architecture. Within the NoC architecture area, new ideas in routing algorithm design continue to dominate the research publications. During the earlier years, routing algorithm proposals attempted communication performance improvement by maximizing routing adaptivity (while avoiding any possibility of deadlock) and by reducing congestion in general or application-specific contexts. Recently, researchers have expanded the scope of routing algorithm design by including fault tolerance and lowering power consumption as added objectives along with high performance. Motivated by advances in new technologies, proposals of routing algorithms for 3D architectures and mixed electro-optical or pure optical NoCs have also started appearing in literature.

As is obvious from research publications in various conferences and workshops, NoC is becoming an important topic of research and postgraduate teaching in universities all over the globe. Routing algorithm design is a challenging topic for researchers since it provides the possibility of graph theoretic analysis of any proposed new solution. Thanks to the availability of free NoC simulators, this area provides the possibility of concrete and speedy experimental evaluation of new ideas in NoC routing. Availability of ASIC design tools and FPGA prototyping tools also allows evaluation of cost and power consumption implications of the new ideas. Research in the area of routing algorithms is still flourishing and by no means has reached the saturation point. This book, entitled *Routing Algorithms in Networkson-Chip*, is a collection of papers describing representative solutions to important aspects and issues related to routing algorithms. This collection does not claim to include best solutions for any aspect of routing algorithms, nor does it claim a complete coverage of topics related to this important area of NoC architecture. But the book does provide a good source of reference to postgraduate students and researchers getting started in this exciting area.

For many years, both Maurizio Palesi and Masoud Daneshtalab have been very active in research related to various aspects of NoC architecture design in general, and design of routing algorithms in particular. They have made significant and distinctive contributions in the area of routing algorithms. Their contributions, through the organization of NoC-related workshops and special sessions in international conferences, as well as through special issues for various international journals, are well known and highly appreciated by the NoC community. The contacts and knowledge gained by them through these experiences have placed them in a unique position to put together this excellent collection of papers in a book form.

The book is organized in six logical parts such that each part contains papers related to a common theme. For example, Part I contains papers proposing ideas to improve routing performance in NoC platforms. Similarly, Part II collects ideas related to multicast routing in NoC platforms. There are parts, each with multiple chapters, dealing with fault tolerance routing in NoC, power/energy-aware routing, and routing for 3D and optical NoC. The single chapter in the last part describes an industrial case study of routing algorithm in a tera-scale architecture. This organization makes the book directly useable as a reference or as a textbook in a special topic graduate course.

I recommend this book to all those who are new to the area of NoC architecture and NoC routing and want to understand the basic concepts and learn about important research issues and problems in this area. The book will also be useful as a reference source to established research groups as well as industry involved in NoC research. I feel this book will make an important contribution in promoting education and research in NoC architecture.

Jönköping University, Jönköping, Sweden Shashi Kumar

## Preface

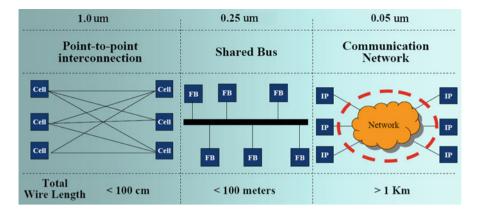

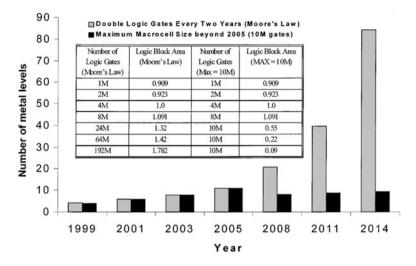

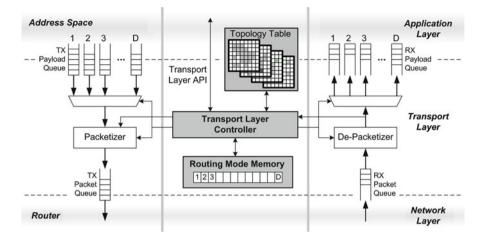

Modern Systems-on-Chip (SoCs) today contain hundreds of Intellectual Properties (IPs)/cores, including programmable processors, coprocessors, accelerators, application-specific IPs, peripherals, memories, reconfigurable logic, and even analog blocks. We have now entered the so-called many-core era. The International Technology Roadmap for Semiconductors foresees that the number of Processing Elements (PEs) that will be integrated into an SoC will be in the order of thousands by 2020. As the number of communicating elements increases, there is a need for an efficient, scalable, and reliable communication infrastructure. As technology geometries shrink to the deep submicron regime, however, the communication delay and power consumption of global interconnections become the major bottleneck. The Network-on-Chip (NoC) design paradigm, based on a modular packet-switched mechanism, can address many of the on-chip communication issues, such as performance limitations of long interconnects and integration of a large number of PEs on a chip.

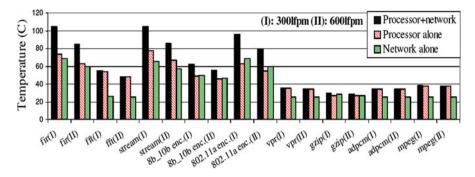

The overall performance of a network depends on several network properties such as topology, routing algorithm, flow control, and switching technique. This book is focused on routing algorithms. The routing algorithm has a strong impact on several nonfunctional requirements of an NoC-based system. Performance, reliability, energy consumption, power dissipation, thermal aspects, and fault tolerance represent just a short list of the major common metrics affected by the routing algorithm.

The scientific literature related to NoC architectures and design methodologies is mostly dominated by works that address issues concerning the routing algorithms. Unfortunately, although the topic is so important and so widely discussed in the NoC community, there is a lack of structured resources (i.e., books, articles, etc.) aimed at organizing the great deal of literature and information on routing algorithms used in the NoC-based systems. The goal of this book is to provide a unified platform for students (master's, Ph.D.), researchers (from both academy and industry), and practitioners for building the basis of routing algorithms for NoC-based systems as well as providing in-depth discussions on advanced solutions applied (and to be applied) in the current and the next generation of NoC-based many-core SoCs. After a brief introduction on the basic concepts of on-chip networks, routing algorithms for NoC architectures will be presented and discussed at different abstraction levels – starting from the algorithmic level to their actual circuital implementation. The impact on current and future key design objectives, namely, power dissipation, energy consumption, thermal aspects, reliability, and performance, will be analyzed and discussed.

This book is organized based on the key problems which affect the current and (may also affect) the next generation of many-core SoCs by putting emphasis on the role played by the routing algorithm. The book is organized into six parts, each of them aimed at presenting a selection of routing algorithms specifically designed for addressing the key issues which characterize the many-core era. The six parts will cover the following macro-topics: Performance Improvement, Multicast Communication, Fault Tolerance and Reliability, Power/Energy and Thermal Issues, Emerging Technologies, and Industrial Case Study.

The book can be used as a reference for university (post)graduate courses and by Ph.D. students, as well as for advanced courses on SoCs. The audience of the book is not limited to various NoC-related research groups; it also might be attractive for faculty and students from other fields when high-performance computing, supercomputers, and many-core systems become the key elements. In fact, routing algorithms play an important role for these elements. As there is much literature related to this subject, we attempt to collect and adjust the state-of-the-art research results, which have been recently published, into the chapters.

Chapter 1 provides the basic concepts of on-chip networks, including network topologies, switching techniques, and routing algorithms. Such topics represent the conceptual bases exploited by the strategies, the mechanisms, and the methodologies discussed in the rest of the book.

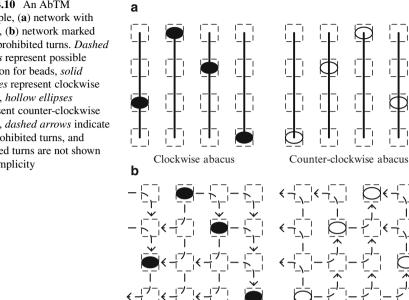

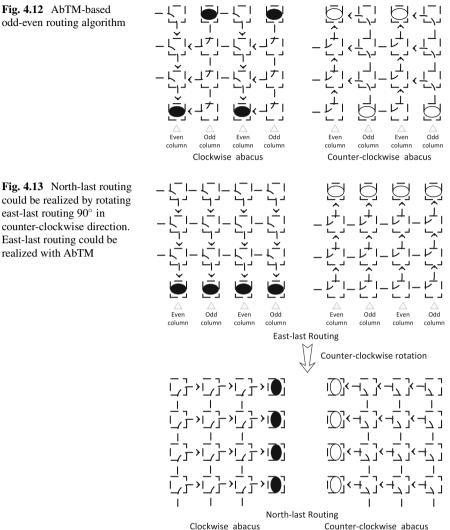

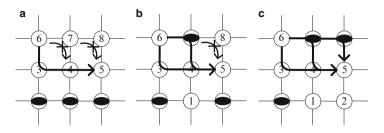

The first part of the book consists of a set of chapters related to performance improvement. Chapter 2 presents a system-level framework for designing minimal deterministic routing algorithms for NoCs that are customized for a set of applications. Chapter 3 studies deadlock detection and recovery strategy in NoCs as opposed to deadlock avoidance. Chapter 4 discusses the abacus turn model which allows to keep the network deadlock-free by dynamically applying forbidden turns. Chapter 5 investigates routing algorithms based on learning approaches for balancing the traffic over the network.

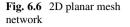

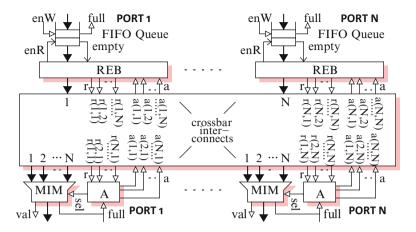

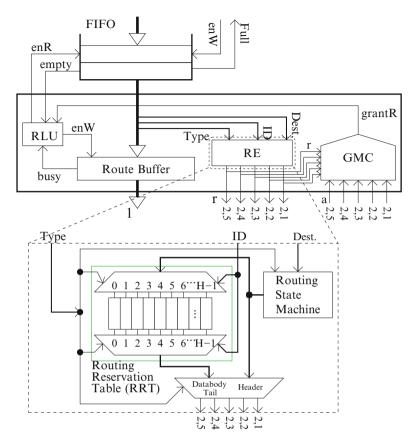

The second part of the book focuses on multicast communication. Chapter 6 presents a new method and concept for implementing efficient and deadlock-free tree-based multicast routing algorithms. Chapter 7 addresses how to implement unicast and multicast routing efficiently in 2D and 3D mesh networks.

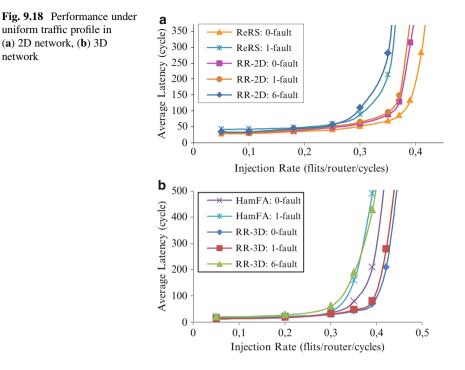

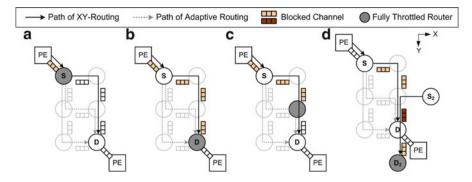

Fault tolerance and reliability are discussed in the third part of the book. Chapter 8 presents a fault-tolerant routing algorithm that keeps the negative effect of faulty components on the NoC power and performance as low as possible. Chapter 9 provides extensive knowledge on how to develop a fault-tolerant routing algorithm based on the characteristics of a system.

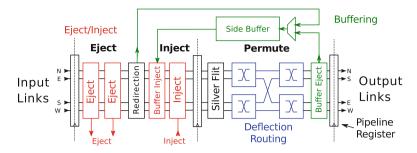

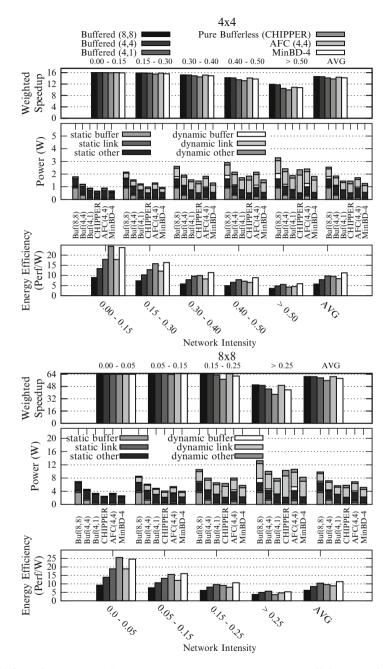

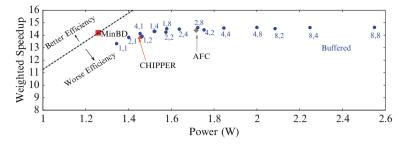

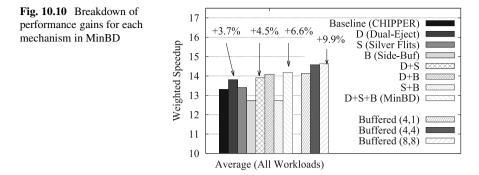

The fourth part of the book addresses power, energy, and thermal issues. Chapter 10 presents the use of bufferless deflection routing for removing input buffers which

are responsible for a significant fraction of the total power budget. Chapter 11 proposes a routing algorithm to reduce the hotspot temperature for application-specific NoCs.

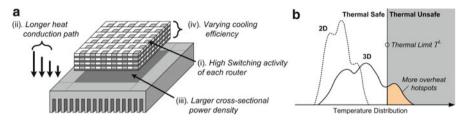

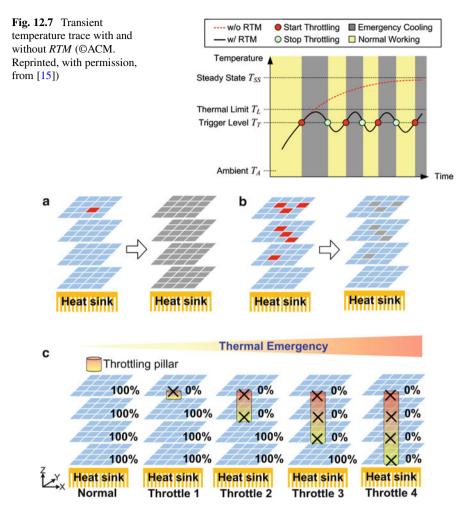

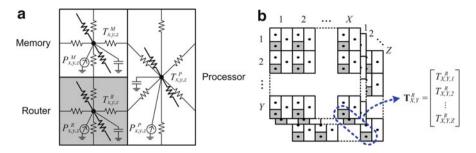

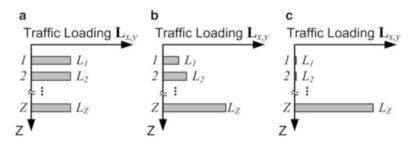

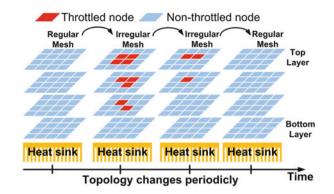

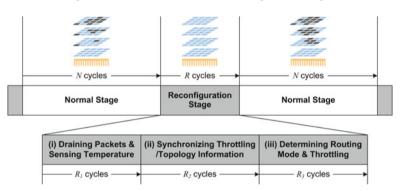

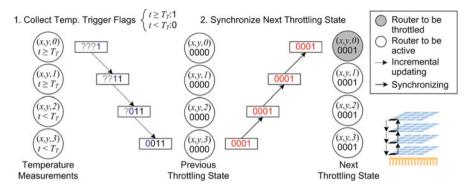

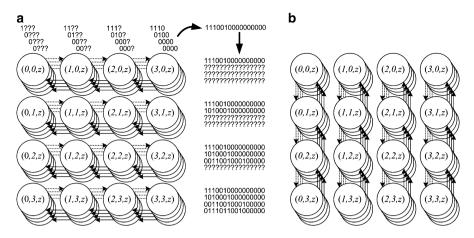

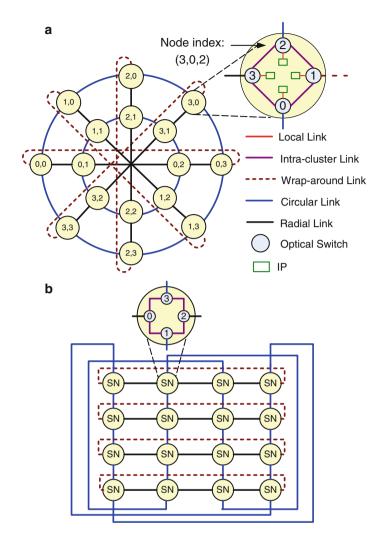

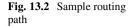

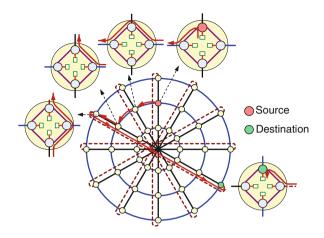

Emerging technologies are explored in the fifth part of the book. Chapter 12 introduces some design concepts of traffic- and thermal-aware routing algorithms in 3D NoC architectures, which aim at minimizing the performance impact caused by the run-time thermal managements. A new architecture for nanophotonic NoCs which consists of optical data and control planes is proposed in Chap. 13.

Finally, in the last part of the book (Chap. 14), an industrial case study illustrates a comprehensive approach in architecting (and micro-architecting) a scalable and flexible on-die interconnect and associated routing algorithms that can be applied to a wide range of applications in an industry setting.

Enna, Italy Turku, Finland Maurizio Palesi Masoud Daneshtalab

## Acknowledgments

"Life is like riding a bicycle. To keep your balance you must keep moving." "Imagination is more important than knowledge. Knowledge is limited. Imagination encircles the world." – Albert Einstein

A collective work of this nature is not possible without a considerable amount of mutual support. For that, we would like to express our gratitude to all the contributing authors for their hard work and cooperation. We would also like to thank the Springer staff involved in the publication of this book.

Maurizio Palesi would like to pay special thanks to his wife, Cristina Galvagno, for constant support and encouragement and for taking care of Alberto (their son) especially as the deadlines approached.

Masoud Daneshtalab would like to express his deepest gratitude to his wonderful wife, Masoumeh Ebrahimi, for her excellent guidance and patience. Without her love, encouragement, and patience, he would not be able to finish this work. She is always the first one he would go to whenever he needs support, and the first one to share his happiness on his success. Finally, Masoud would like to thank his mother, Mahnaz, for her constant love, support, and prayers.

"Let yourself be drawn by the stronger pull of that which you truly love"

"Two there are who are never satisfied – the lover of the world and the lover of knowledge" – Rumi

## Contents

| 1    | Basic Concepts on On-Chip Networks<br>Masoud Danashtalab and Maurizio Palesi                                                                            | 1   |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Part | t I Performance Improvement                                                                                                                             |     |

| 2    | A Heuristic Framework for Designing and Exploring<br>Deterministic Routing Algorithm for NoCs<br>Abbas Eslami Kiasari, Axel Jantsch, and Zhonghai Lu    | 21  |

| 3    | <b>Run-Time Deadlock Detection</b><br>Ra'ed Al-Dujaily, Terrence Mak, Fei Xia, Alex Yakovlev,<br>and Maurizio Palesi                                    | 41  |

| 4    | <b>The Abacus Turn Model</b><br>Binzhang Fu, Yinhe Han, Huawei Li, and Xiaowei Li                                                                       | 69  |

| 5    | Learning-Based Routing Algorithms for On-Chip Networks<br>Masoumeh Ebrahimi and Masoud Daneshtalab                                                      | 105 |

| Part | t II Multicast Communication                                                                                                                            |     |

| 6    | <b>Efficient and Deadlock-Free Tree-Based Multicast</b><br><b>Routing Methods for Networks-on-Chip (NoC)</b><br>Faizal Arya Samman and Thomas Hollstein | 129 |

| 7    | Path-Based Multicast Routing for 2D and 3D Mesh Networks<br>Masoumeh Ebrahimi, Masoud Daneshtalab, Pasi Liljeberg,<br>Juha Plosila, and Hannu Tenhunen  | 161 |

#### Part III Fault Tolerance and Reliability

| 8   | <b>Fault-Tolerant Routing Algorithms in Networks On-Chip</b><br>Reyhaneh Jabbarvand Behrouz, Mehdi Modarressi,<br>and Hamid Sarbazi-Azad                        | 193 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 9   | Reliable and Adaptive Routing Algorithms for 2D and 3D<br>Networks-on-Chip<br>Masoumeh Ebrahimi                                                                 | 211 |

| Par | t IV Power/Energy and Thermal Issues                                                                                                                            |     |

| 10  | <b>Bufferless and Minimally-Buffered Deflection Routing</b><br>Chris Fallin, Greg Nazario, Xiangyao Yu, Kevin Chang,<br>Rachata Ausavarungnirun, and Onur Mutlu | 241 |

| 11  | A Thermal Aware Routing Algorithm<br>for Application-Specific Network-on-Chip<br>Zhiliang Qian and Chi-Ying Tsui                                                | 277 |

| Par | t V Emerging Technologies                                                                                                                                       |     |

| 12  | Traffic- and Thermal-Aware Routing Algorithms for 3D<br>Network-on-Chip (3D NoC) Systems<br>Kun-Chih Chen, Chih-Hao Chao, Shu-Yen Lin,<br>and An-Yeu (Andy) Wu  | 307 |

| 13  | Scalable Architecture for All-Optical Wavelength-Routed<br>Networks-on-Chip<br>Somayyeh Koohi and Shaahin Hessabi                                               | 339 |

| Par | t VI Industrial Case Study                                                                                                                                      |     |

| 14  | On Chip Network Routing for Tera-Scale Architectures                                                                                                            | 379 |

| 14 | On Chip Network Routing for Tera-Scale Architectures | 379 |

|----|------------------------------------------------------|-----|

|    | Aniruddha S. Vaidya, Mani Azimi, and Akhilesh Kumar  |     |

## Chapter 1 Basic Concepts on On-Chip Networks

Masoud Danashtalab and Maurizio Palesi

**Abstract** As the number of cores integrated into a System-on-Chip increases, the role played by the communication system becomes more and more important. The Network-on-Chip design paradigm is today recognised as the most viable communication infrastructure to deal with the scalability issues which characterise the ultra-deep sub-micron silicon era. In this chapter, some of the most important concepts in the context of on-chip networks will be reviewed. Basic concepts including, network topologies, switching techniques, and routing algorithms will be recalled. Such topics represent the conceptual bases exploited by the strategies, the mechanisms, and the methodologies discussed in the subsequent chapters.

#### 1.1 Introduction

Programmable chips, like microprocessors, were originally developed with a single computational core. Such chips could execute program instructions in sequence and with a speed proportional to the clock frequency. Thus, increasing the clock frequency was the most common way to improve the overall performance of a chip. Unfortunately, increasing the clock frequency of a chip has several drawbacks. One of the most important concern is related to the increase in power dissipation which in turn determines the operational temperature of the chip. High clock frequency results in high temperature that has to be dissipated in a small surface of a few square centimeters. Temperature also impacts the system reliability as every 10 °C increase in operating temperature roughly doubles failure rate of the components.

M. Danashtalab (🖂)

University of Turku, Turku, Finland e-mail: masdan@utu.fi

M. Palesi Kore University, Enna, Italy e-mail: maurizio.palesi@unikore.it

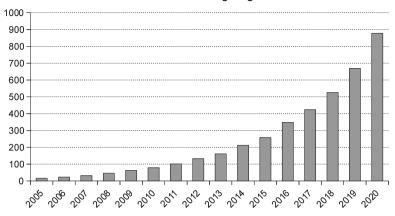

Number of Processing Engines

Fig. 1.1 Expected number of processing elements into a SoC [20]

The increasing demand in computational power of current and next generation applications cannot be "simply" provided by increasing the clock frequency. To overcome the limitation in increasing the clock frequency, modern chips are designed with multiple parallel computational cores able to work in parallel but with a reduced clock frequency. Thus, although instructions are executed slower than in a single core microprocessor running at higher clock frequency, they can be executed in parallel.

As the number of cores integrated into a single silicon chip increases (Fig. 1.1), the on-chip communication related issues are becoming more and more relevant than the computational related issues. That is, we can have all the computational horsepower we need (simply by increasing the number of computational cores) but, at the same time, there is a need for an efficient communication infrastructure for orchestrating the interaction between them.

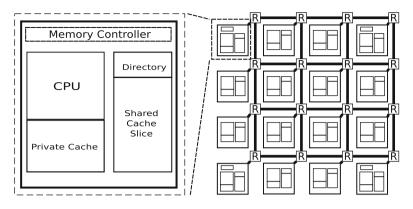

The Network-on-Chip (NoC) design paradigm is currently considered as the most viable solution to deal with communication issues which affect the next generation of many-core System-on-Chip (SoC). A NoC can be imagined as a computer network in which computers are replaced by cores into the chip. In which information travels through the micronetwork in the form of packets traversing on-chip links and routed by on-chip routers.

NoCs are emerged as a highly scalable, reliable, and modular interconnect fabric for MPSoCs [2,8,21,22]. However, the network fabric takes up a substantial portion of system power budget [26]. As power is one of the most important issues in billion-transistor chips, in addition to network delay and area, the interconnect power consumption should be taken into consideration. Therefore, NoCs should be accommodated into the limited silicon area using efficient topology, routing algorithm, and router implementation.

In this chapter, basic concepts of NoCs including network topologies, switching techniques, flow control mechanisms, virtual channels, output selection, routing algorithms, and a general NoC architecture are presented.

#### **1.2** Network Topology

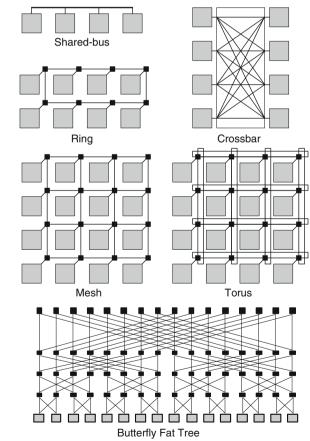

The network topology is the study of the arrangement and connectivity of the routers. In other words, it defines the various channels and the connection pattern that are available for the data transfer across the network. Performance, cost, and scalability are the important factors in the selection of the appropriate topology. Shared-Bus, Crossbar, Butterfly Fat-Tree, Ring, Torus, and 2D-Mesh are the most popular topologies for on-chip interconnects which have been commercially used [14, 21].

Direct networks have at least one processing element (PE) attached to each router of the network so that routers may regularly spread between PEs. This helps to simplify the physical implementation. The shared-bus, ring, and 2D mesh/torus topologies (Fig. 1.2) are examples of direct networks, and provide tremendous improvement in performance, but at a cost of hardware overhead, typically increasing as the square of the number of PEs. On the other hand, indirect

Fig. 1.2 Network topologies of Shared-bus, Ring, Crossbar, Mesh, Torus, and Butterfly

networks have a subset of routers which are not connected to any PE. All treebased topologies where PEs are connected only to the leaf routers (e.g., the butterfly topology) as well as crossbar switch (Fig. 1.2) are indirect networks.

The shared-bus topology is the simplest using a common shared link common to all PEs where they compete for exclusive access to the bus. For communication intensive applications, it is necessary to overcome the bandwidth limitations of the shared-bus topology and move to scalable networks. However, this topology scales very poorly as the number of PEs increases. A small modification to the sharedbus topology to allow more concurrent transactions is to create the ring topology where every PE has exactly two neighbors. In this topology, messages hop along intermediate PEs until they arrive at the final destination. This causes the ring to saturate at a low injection rate for most traffic patterns. The crossbar topology is a fully connected one which allows every PE to directly communicate with any other PE.

The fat-tree topologies suffer from the fact that the number of routers exceeds the number of PEs, when the amount of PEs increases. This incurs an important network overhead. For the on-chip interconnects the network, overhead is more critical than for the off-chip networks and the design scalability is more essential. Mesh and torus networks are widely used in multiprocessor architectures because of their simple connection and easy routing provided by adjacency. Both torus and mesh topologies are fully scalable. Although torus provides a better performance, the regularity, better utilization of links, and lower network overhead are some of the preferences for mesh. That is, the mesh topology is more economic scheme since the routers on the borders are smaller. In sum, each topology has its own advantages and disadvantages.

#### **1.3** Switching Mechanism

The switching mechanism determines how messages traverse a route in a network. The goal is to effectively share the network resources among messages traversing the network. Basically, circuit switching and packet switching form the two extremes of switching mechanisms.

In circuit switching, a connection from a source to a destination is established prior to the transmission of data and exclusively reserved until the message is completely transferred (e.g., as in telephone networks that set up a circuit through possibly many routers for each call). This mechanism has low delay and guarantees bandwidths, but suffers from channel utilization, low throughput, and long initialization time to setup a connection.

Packet switching is an alternative mechanism where data is not transmitted on a predefined circuit. A message can be divided into packets which share channels with other packets. Each packet consists of a header which contains routing and control information, data payload, and possibly a tail. The data payload follows the channel reserved by a header while the tail releases the channel reservation. Packets are individually and independently routed through the network, and at the destination

the packets are assembled into the original message. If a message is divided into several packets, the order of packets at arrival PE must be the same as departure. Therefore, in-order delivery is an essential part that should be supported by onchip networks. The packet switching mechanism improves channel utilization and network throughput.

In the packet switching domain, buffered flow control defines the mechanism that deals with the allocation of channels and buffers for the packets traversing between source and destination. The flow control mechanism is necessary when two or more packets compete to use the same channel, at the same time. Commonly three different buffered flow control strategies are used: store-and-forward, virtual cut through, and wormhole. When these mechanisms are implemented in on-chip networks, they have different performance metrics along with different requirements on hardware resources.

#### 1.3.1 Store-and-Forward

Store-and-forward is the simplest flow control mechanism [14]. In this approach, each router along the path stores the entire packet in the buffer and then, the packet is forwarded to a selected neighboring router if the chosen neighboring router has enough empty buffering space available to hold the whole packet. This mechanism requires a large amount of buffering space (at least the size of the largest packet) in each router of the network, which can increase the cost dramatically. On top of that, network latency increases significantly because a packet cannot be forwarded to the next router until the whole packet is received and stored in the current router. Consequently, the store-and-forward approach is impractical in large-scale NoCs.

#### 1.3.2 Virtual Cut-Through

The virtual cut-through mechanism [14] was proposed to address the large network latency problem in the store-and-forward strategy by reducing the packet delays at each routing stage. In this approach, one packet can be forwarded to the next stage before it is entirety received by the current router which reduces the store-and-forward delays. However, when the next stage router is not available, similar to the store-and-forward mechanism, the virtual cut-through approach also requires a large buffering space at each router to store the whole packet.

#### 1.3.3 Wormhole

In this mechanism, a packet is divided into smaller segments called FLITs (FLow control digIT) [27]. Then, the flits are routed through the network one after another in a pipelined fashion. The first flit in a packet (header) reserves the channel of each

router, the body (payload) flits will then follow the reserved channel, and the tail flit will later release the channel reservation. The wormhole mechanism does not require the complete packet to be stored in the router while waiting for the header flit to route to the next stages. One packet may occupy several intermediate routers at the same time. That is, the wormhole approach is similar to the virtual cut-through, but here the channel and buffer allocation is done on a flit-basis rather than packetbasis. Accordingly, the wormhole approach requires much less buffer space, thus, enabling small, compact and fast router designs. Because of these advantages, the wormhole mechanism is an ideal flow control candidate for on-chip networks.

#### **1.4 Virtual Channels**

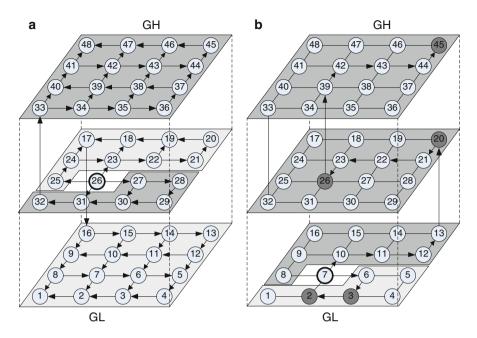

There is a possibility of blocking in the wormhole network when a packet reserves a channel along a path which is prevented to be used by other packets. The use of Virtual Channels (VCs) overcomes the problem of blockages in the wormhole network via allowing blocked packets to be passed by other packets. This is accomplished by assigning several VCs, each with a separate flit queue, to each physical channel. For each VC, when the header flit arrives, a buffer will be assigned to the incoming packet, and is reserved until the trailer flit is transmitted. If a packet holding a VC gets blocked, other packets from other VCs can still traverse the physical channel.

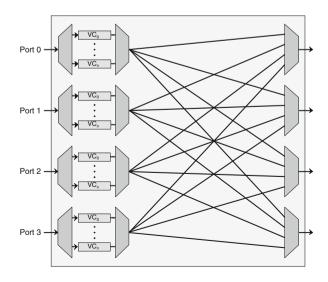

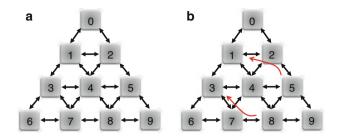

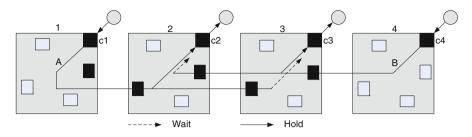

As depicted in Fig. 1.3, at an input port the incoming flits are stored in distinct channel buffers which are multiplexed together again onto the output ports. If one of the channels is blocked, the other channels can access the outputs. VCs were introduced to solve the deadlock avoidance problem and to improve network latency

**Fig. 1.3** A typical router using VCs

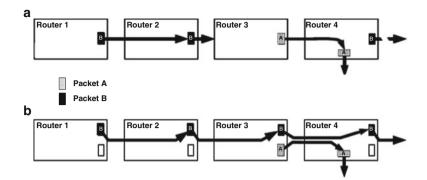

Fig. 1.4 Using VC for avoiding deadlock

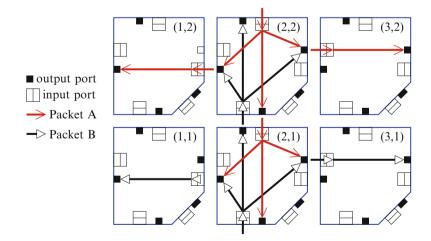

and throughput. Figure 1.4a shows how a packet *A* blocked between routers 3 and 4 which also blocks the packet *B* when the network is not equipped with VCs. As illustrated in Fig. 1.4b, using VCs allows dual utilization of the physical channel between routers 3 and 4 where the packet *B* can pass the router 3. However, although employing VCs improves the performance and reduces Head-of-Line blocking (HoL) efforts in the network, it increases design complexity of the link controller and flow control mechanisms.

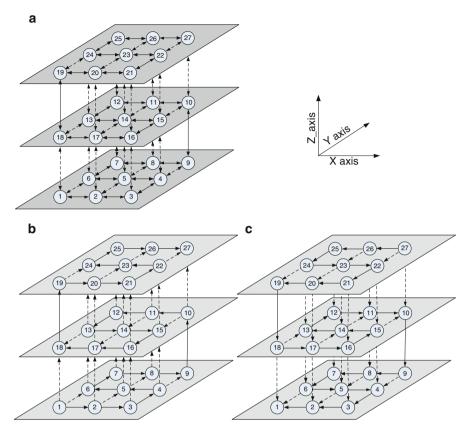

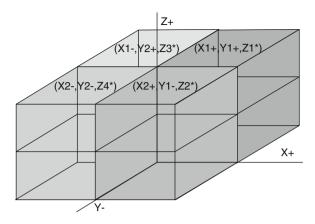

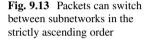

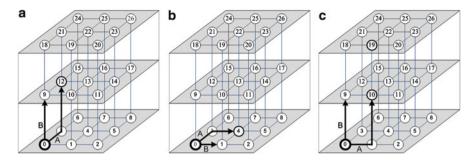

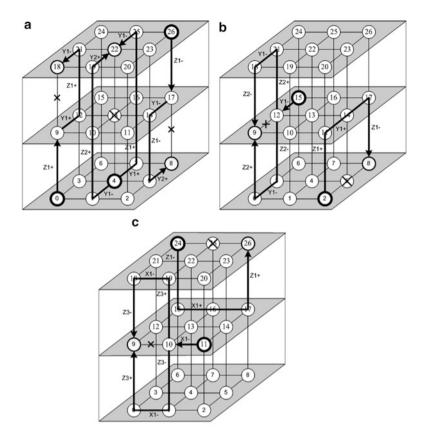

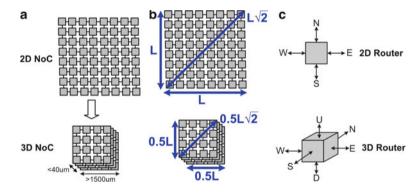

#### 1.5 Network Dimension

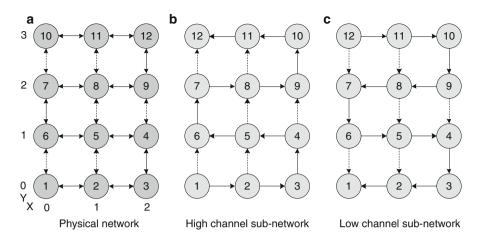

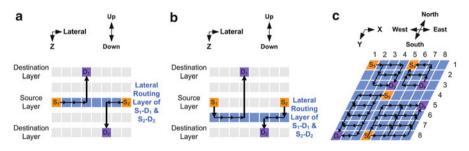

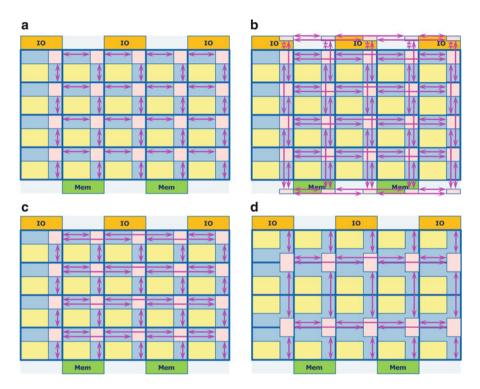

The NoC design is commonly discussed in the form of two-dimensional (2D) and three-dimensional (3D) architectures. As shown in Fig. 1.5a, in 2D NoCs design, all switches are laid down in a single layer and connected to each other via intralayer connections. In 3D NoCs (Fig. 1.5b), layers are stacked on top of each other via inter-layer connections instead of being spread across a 2D plane [4, 17, 31]. Each layer can use different technology, topology, clock frequency, etc. In recent years, through-silicon-via (TSV) has attracted a lot of attention to be employed for the inter-layer connections (vertical channels). TSVs enable faster and more power efficient inter-layer communication across multiple stacked layers. Figure 1.5 illustrates a 2D and 3D network with almost similar numbers of cores.

#### 1.6 Output Scheduling

When multiple packets request for an output port, the need of an output scheduling algorithm that determines the priority order of candidate packets to advance emerges. In fact, the scheduler gives a priority order to each packet, and then the

Fig. 1.5 (a) 2D NoC (b) 3D NoC

output ports select the highest-ordered packets to be forwarded. There is a variety of solutions with different implementation complexity and different performance characteristics e.g. round-robin, first-come first-served. The starvation prevention is the main concern that must be considered in the scheduler. Starvation is the situation in which low priority packets cannot get access to output ports as high priority packets always win the arbitration. The arbitration policy can be based on the roundrobin or the packet priority scheme. Round-robin provides a fair scheduling by serving packets in a circular manner, so that it is starvation-free. However, packet prioritization might be needed in the network for the quality of service or it can be used for increasing the overall performance. On the other hand, prioritization schemes may lead to starvation in the network. A proper resource assignment can avoid starvation while packets have different priorities.

#### **1.7 Routing Algorithm**

Routing is the process that is used to forward the packets along appropriate directions in the network between a source and a destination.

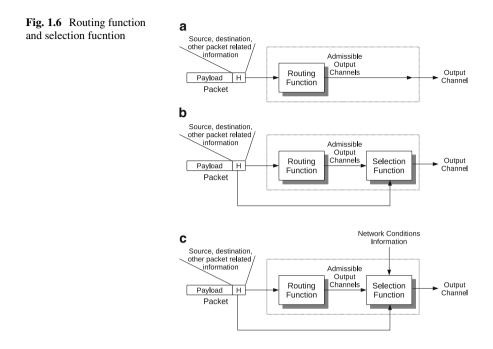

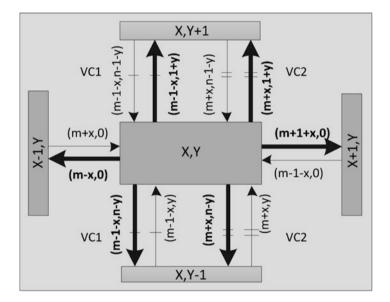

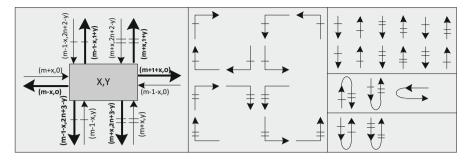

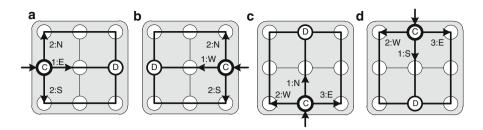

In general, a routing algorithm can be seen as the cascade of two main blocks which implement the *routing function* [5, 6, 18, 32] and the *selection function* [1, 19, 29, 34] as shown in Fig. 1.6. First, the routing function computes the set of admissible output channels towards which the packet can be forwarded to reach the destination. Then, the selection function is used to select one output channel from the set of admissible output channels returned by the routing function. In a router implementing a deterministic routing algorithm (Sect. 1.7.2), the selection block is not present since the routing function returns only a single output port (see Fig. 1.6a). In a router implementing an oblivious routing algorithm (Sect. 1.7.2) the selection block takes its decision based solely on the information provided by the header flit (see Fig. 1.6b). Finally, network status information (e.g., link utilization and buffer occupation) are exploited by the selection function of a router implementing an adaptive routing algorithm (Sect. 1.7.2) (see Fig. 1.6c).

Routing algorithms not only affect the transmission time but also can impact the power consumption and congestion conditions in the network.

#### 1.7.1 Source Versus Distributed Routing

Routing can be utilized either at the source router or with a distributed manner by routers along the path. In the source routing scheme the entire route of a packet is decided by the source router stacking the exact router-to-router itinerary of a packet in the header. As the packet traverses in the network this information is used by each router on the path to navigate the packet towards the destination. This scheme is a simple solution for on-chip networks while the problem of the routing information overhead is the drawback of this scheme, i.e. for a network with a diameter of k, each packet requires at most k routing information stacked on the header of the packet. Accordingly, if the network grows, the header overhead becomes significant which is impractical for on-chip networks. In contrast, in the distributed routing approach the routing decision is taken by the individual routers depending on different parameters while the header of a packet has to include only the destination address. Each intermediate router examines the destination address (sometimes source address is also needed) and decides along which channel to forward the packet. However, the router complexity of the latter scheme is higher than the former scheme.

#### 1.7.2 Deterministic Versus Adaptive Routing

Distributed routing scheme can be classified as *deterministic*, *oblivious*, and *adap*tive. Deterministic routing algorithms route packets in a fixed path between the source and destination routers. Implementations of deterministic routing algorithms are simple but they are not able to balance the load across the links in non-uniform or bursty traffic [3,9]. Oblivious and adaptive routing algorithms are proposed to address these limitations. In oblivious routing, multiple paths from the source to the destination are possible and the selection of the routing path does not depend on the current status of the network. By better distributing load across links, adaptive algorithms improve the network performance and also provide tolerance if link or router failure occurs. In adaptive routing algorithms, the path of a packet from the source to the destination is determined by network conditions. An adaptive routing algorithm decreases the probability of passing a packet from a congested or malfunction link. While deterministic routing algorithms are the best choices for uniform or regular traffic patterns, the adaptive schemes are preferable in the presence of irregular traffic (non-uniform or bursty traffic) or in networks with unreliable routers and links. Furthermore, since packets may arrive at the destination from different paths and with different latencies, an adaptive routing could not guarantee the order of packets. To achieve in-order delivery property, a reordering module is required. These requirements increase both design complexity, and likely communication latency.

#### 1.7.3 Minimal Versus Non-minimal Routing

Adaptive routing algorithms can be either minimal or non-minimal [15]. Minimal routing algorithms allow only the shortest paths to be chosen, while non-minimal routing algorithms also allow longer paths. Besides, a minimal fully adaptive routing algorithm can route packets along any shortest path adaptively; and a minimal partially adaptive routing algorithm cannot route packets along every shortest path.

#### 1.7.4 Unicast and Multicast Routing Protocols

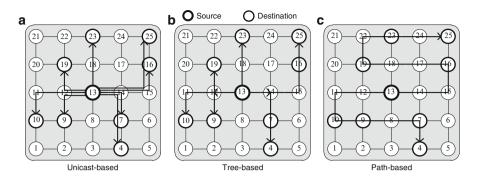

The communication in on-chip networks can be either unicast (one-to-one) or multicast/broadcast (one-to-many) [10, 16, 24]. In the unicast communication, a packet (message) is sent from a source router to a single destination router, while in the multicast communication a packet is transmitted from a source router to an arbitrary set of destination routers. Thus, the former is a special case of the latter.

Fig. 1.7 An example of deadlock

The multicast communication is frequently employed in many applications of MPSoC such as replication [25], barrier synchronization [33], cache coherency in distributed shared-memory architectures [23], and clock synchronization [11]. Although the multicast communication can be implemented by multiple unicast communications, it produces a significant amount of unnecessary traffic increasing the latency and congestion in the network [24].

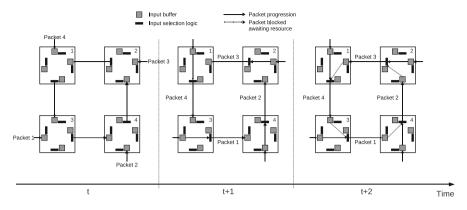

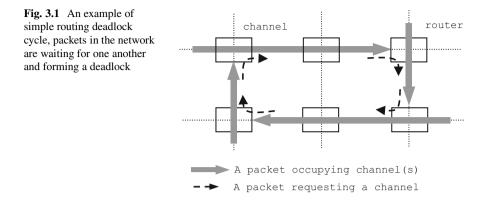

#### 1.7.5 Deadlock and Livelock

Figure 1.7 shows an example of deadlock situation [28] occurring when, at the same time t, four packets Packet 1, Packet 2, Packet 3, and Packet 4 present at the west port of router 3, south port of router 4, east port of router 2, and north port of router 1 respectively. Destinations of the packets are two hops counterclockwise: Packet 1 is destined to node 2, Packet 2 to node 1, Packet 3 to node 3, and Packet 4 to node 4. Assuming a routing function which returns the output port to reach the destination in a minimal hop count favouring counterclockwise direction, at time t + 1 the input logic of router 3 selects the west input creating a shortcut between the west input port and the east output port. Based on wormhole rules, such a shortcut is maintained until all the flits of Packet 1 have traversed router 3. At the same time, a shortcut from south input port of router 4 with its north output port is created. Similarly, a shortcut between east input port to west output port, and from north input port to south output port are created at time t + 1 in router 2 and router 1 respectively. At time t + 2, the first flit of Packet 1 is stored into the west input buffer of router 4. The routing function determines that the flit has to be forwarded to the north output port, but this port is already assigned for forwarding the flits of Packet 2. Thus, the first flit of Packet 1 is blocked in the west input buffer of router 4. Similarly, the first flit of Packet 2 is blocked in the south input port of router 2, the first flit of Packet 3

is blocked in the east input port of router 1, and the first flit of Packet 4 is blocked in the north input port of router 3. Assuming 1 flit input buffer size, the flits of the four packets cannot advance and, consequently, there is a deadlock.

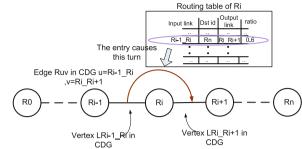

A common way to verify the deadlock freedom property of a routing function is by means of Duato's theorem [12] which is an extension of Dally and Seitz theorem [7] for adaptive routing functions. It is based on the analysis of the channel dependency graph (CDG) associated to the routing function and the network topology. Specifically, the following definitions are needed to introduce the theorem.

**Definition 1.** A *Topology Graph* TG = G(P,L) is a directed graph where each vertex  $p_i$  represents a node of the network and each directed arc  $l_{ij} = (p_i, p_j)$  represents a physical unidirectional link connecting node  $p_i$  to node  $p_j$ .

Let  $L_{in}(p)$  and  $L_{out}(p)$  be the set of input links and output links for node p respectively. Mathematically:

$$L_{in}(p) = \{l \mid l \in L \land dst(l) = p\},$$

$$L_{out}(p) = \{l \mid l \in L \land src(l) = p\}.$$

where src(l) and dst(l) indicate the source and the destination network node of the link *l*.

**Definition 2.** A *Routing Function* for a node  $p \in P$ , is a function  $R(p) : L_{in}(p) \times P \rightarrow \mathcal{O}(L_{out}(p))$ . R(p)(l,q) gives the set of output links of node p that can be used to send a message received from the input link l and whose destination is  $q \in P$ .

The  $\wp$  indicates a power set. We indicate with *R* the set of all routing functions:  $R = \{R(p): p \in P\}.$

**Definition 3.** Given a topology graph TG(P,L) and a routing function R, there is a *direct dependency* from  $l_i \in L$  to  $l_j \in L$  if  $l_j$  can be used immediately after  $l_i$  by messages destined to some node  $p \in P$ .

**Definition 4.** A *Channel Dependency Graph* CDG(L,D) for a topology graph TG, and a routing function R, is a directed graph. The vertices of CDG are the links of TG. The arcs of CDG are the pair of links  $(l_i, l_j)$  such that there is a direct dependency from  $l_i$  to  $l_j$ .

Based on the above definitions, the following theorem gives a sufficient condition for deadlock freedom.

**Theorem 1 (Duato's Theorem [12]).** A routing function *R* for a topology graph *TG* is deadlock-free if there are no cycles in its channel dependency graph CDG.

Livelock is a condition where a packet keeps circulating within the network without ever reaching its destination. It is the result of using a non-minimal adaptive routing algorithm. A livelock free routing algorithm has to guarantee forward progress of each packet, where after each hop the packet is in one step closer to its destination.

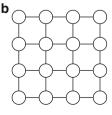

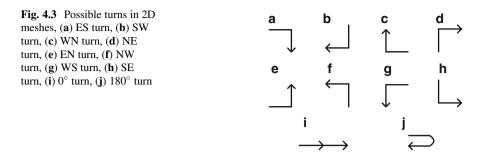

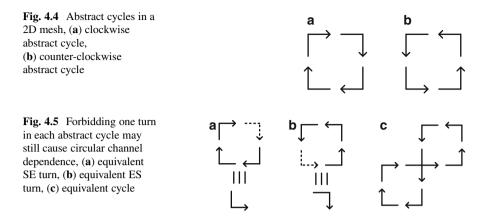

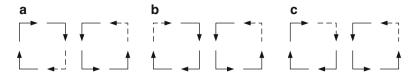

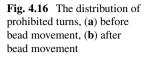

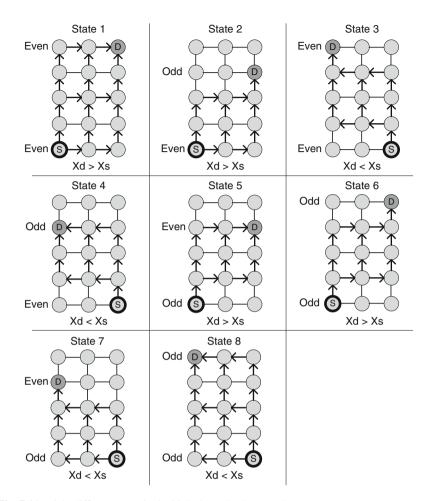

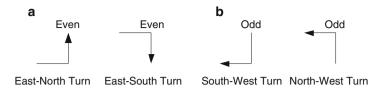

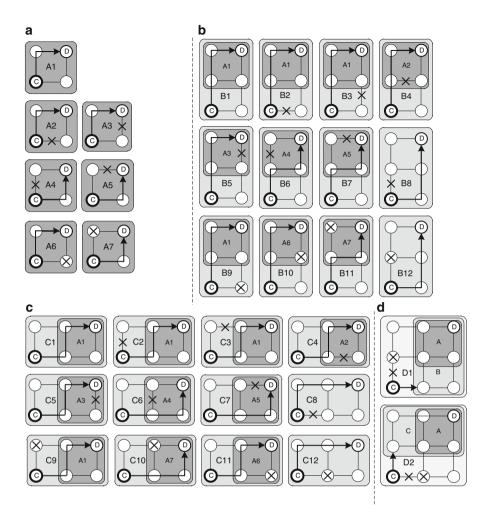

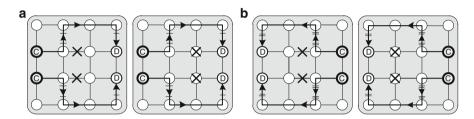

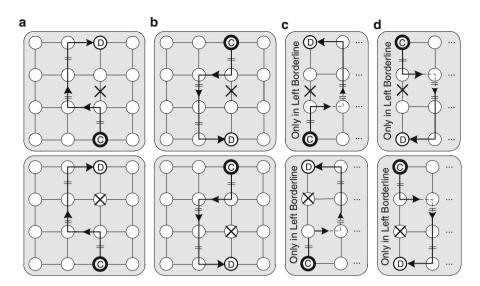

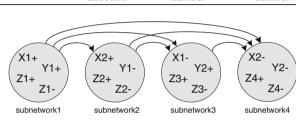

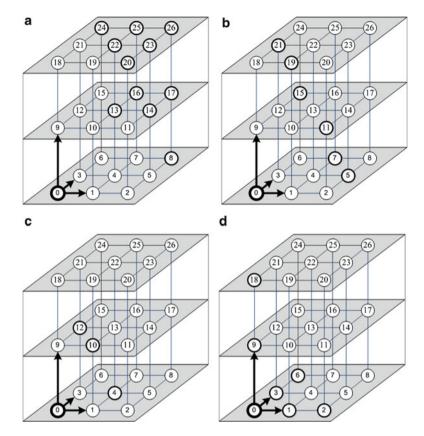

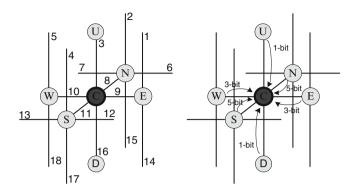

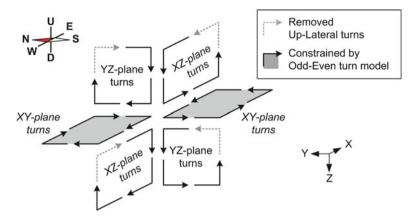

#### 1.7.6 Turn Model Routing

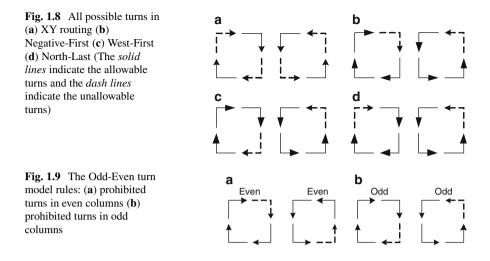

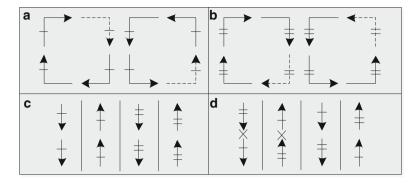

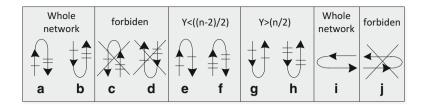

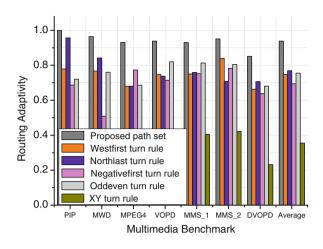

Turn Model routing scheme based on wormhole switching mechanism provides deadlock and livelock freedom in the two-dimensional mesh topology [6, 18]. This model is also chosen as a representative of minimal and partial adaptive routing. In the turn model, deadlock can be avoided by prohibiting just enough turns to break all the cycles. Four well-known turn models are XY, Negative-First (NF), West-First (WF) and North-Last (NL) as shown in Fig. 1.8. Although the XY routing algorithm prohibits four turns to avoid deadlock, the other models avoid only two turns out of eight turns.

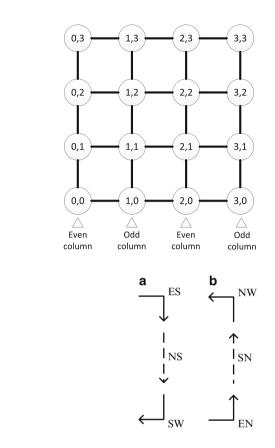

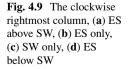

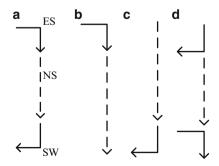

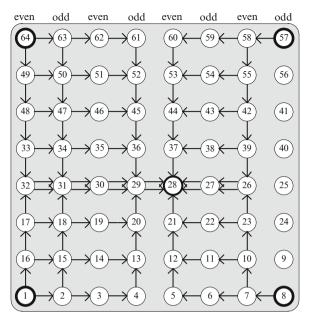

The Odd-Even model is one of the most popular partial adaptive wormhole routing algorithms in 2D mesh on-chip interconnection network [6] without virtual channels. Unlike the turn model which prohibits certain turns in all locations of the network, in the Odd-Even model some turns are restricted only in even columns and some other turns are prohibited in odd columns. Therefore, the degree of adaptiveness provided by this model is higher than the other turn models. Odd-Even rules can be described by the following rules:

Rule 1: East turns cannot be taken in even columns (Fig. 1.9a).

Rule 2: North turns cannot be taken in odd columns (Fig. 1.9b).

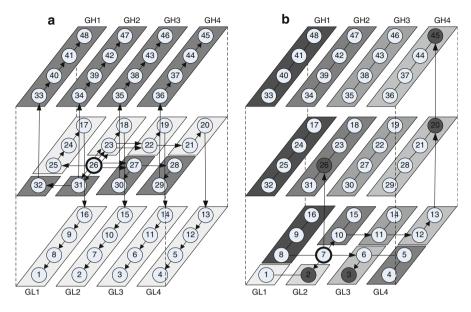

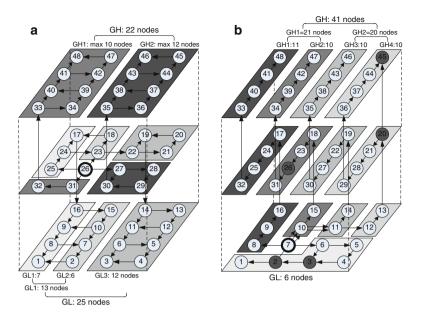

#### 1.7.7 Application Specific Routing Algorithms

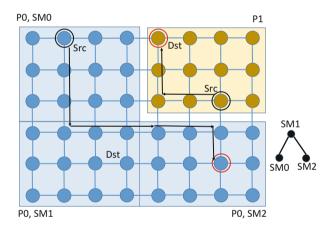

In the embedded systems scenario, unlike general networks, the computational as well as communication requirements of the applications can be very well characterized. Specifically, it is known which pairs of cores in the NoC system

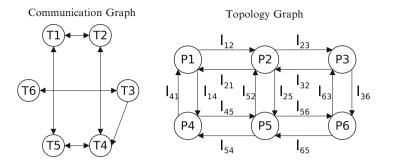

Fig. 1.10 Communication graph and topology graph

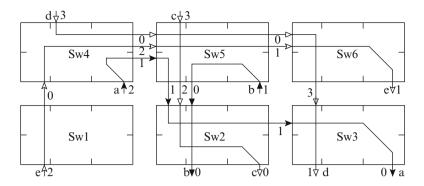

communicate and which do not. By off-line profiling and analysis, one can also estimate some quantitative information like communication bandwidth requirements between communicating pairs. After the applications have been mapped and scheduled on the NoC platform, information about communications which are never concurrent is also available. The APplication Specific Routing Algorithms (APSRA) methodology [30] allows a specific application to generate high efficient routing algorithms tailored. The basic idea behind APSRA is computing the channel dependency graph (*CDG*) [13] by considering just the direct channel dependencies generated by the communicating cores. Such *CDG*, called application specific *CDG* (*ASCDG*), will contain less cycles than the *CDG*. For this reason, there will be less cycles to be removed (i.e., less prohibited turns) with a consequent reduction of the impact on the adaptivity of the routing function.

Let us consider the communication graph and the topology graph depicted in Fig. 1.10. For the sake of simplicity, let us consider that the task  $T_i$  is mapped on node  $P_i$ , i = 1, 2, ..., 6.

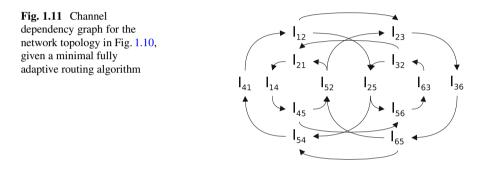

The *CDG* [13] for a minimal fully adaptive routing algorithm is shown in Fig. 1.11. Since it contains several cycles, Duato's theorem [13] cannot assure deadlock freedom for minimal fully adaptive routing for this topology. To make the routing deadlock free, it is necessary to break all cycles of the *CDG*. Breaking a cycle by means of a dependency removal results in restricting the routing function and consequently loss of adaptivity. As the cycles to be removed are many, the adaptivity of the resulting deadlock free routing algorithm will be strongly reduced.

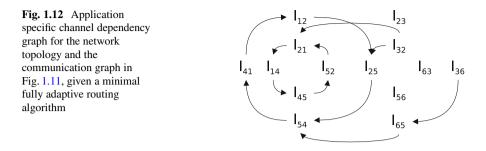

However, if communication information is considered, several cycles of the *CDG* can be safely removed without any impact on the adaptivity of the routing algorithm. For example, study the dependency  $l_{1,2} \rightarrow l_{2,3}$ . Such a dependency is present in the *CDG* but it is not present in the *ASCDG*. In fact, channels  $l_{1,2}$  and  $l_{2,3}$  can be used in sequence only for the communications  $T_1 \rightarrow T_3$ ,  $T_1 \rightarrow T_6$ , and  $T_4 \rightarrow T_3$  which are not present in the communication graph. If we analyze the rest of the dependencies taking into consideration in the communication graph, we find that several dependencies can be safely removed without the need of restricting the routing function. The resulting *ASCDG* is shown in Fig. 1.12. It has been obtained from the *CDG* by removing all the dependencies which cannot be activated by the communication graph.

Although the number of cycles is reduced to two for the *ASCDG*, we still have a possibility of deadlock. To handle this, we can simply break the cycles as follows. The application specific channel dependency  $l_{4,1} \rightarrow l_{1,2}$  is due to the communication  $T4 \rightarrow T2$ . Such communication can be realized by both paths  $P4 \rightarrow P5 \rightarrow P2$  and  $P4 \rightarrow P1 \rightarrow P2$ . If the routing function is restricted in such a way that the latter path is prohibited, the application specific channel dependency  $l_{4,1} \rightarrow l_{1,2}$  does not exist any longer. In a similar way it is possible to break the second cycle, for instance, by removing the dependency  $l_{1,4} \rightarrow l_{4,5}$  due to communication  $T1 \rightarrow T5$ .

#### **1.8 Performance Metrics**

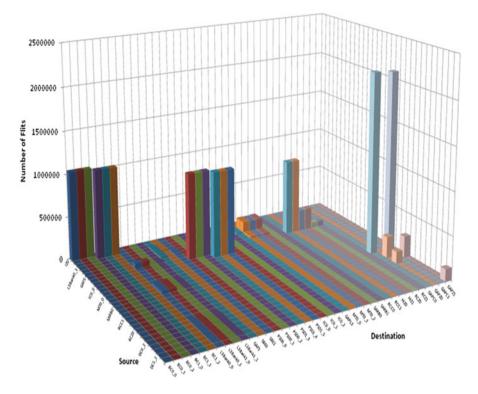

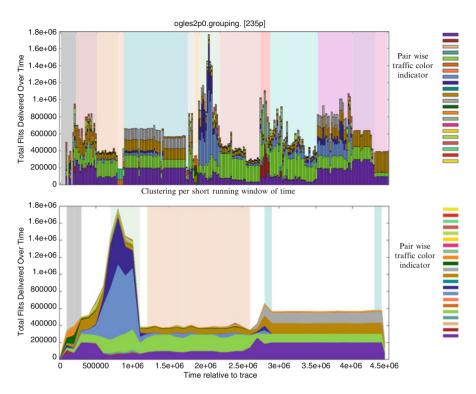

Many metrics have been used for estimating, evaluating and comparing the performance of NoCs. These metrics include different versions of latency (e.g., spread, minimum, maximum, average and expected), various versions of throughput, jitter in latency, jitter in throughput etc. The most common metrics used are the *average delay* and *average throughput*. The average delay, is the mean of the average communication delay over all the communications. The average communication delay is the average delay experimented by the packets of the communication to reach their destinations. The packet delay is the time elapsed from the instant in which the header of the packet is injected into the network, to the instant in which the tail of the packet (i.e., the tail flit) reaches the destination. The average throughput is the mean of the throughput over all the destination nodes. That is, the average number of packets received by the destination in the time unit.

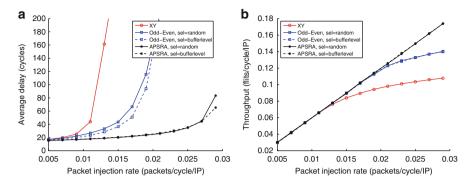

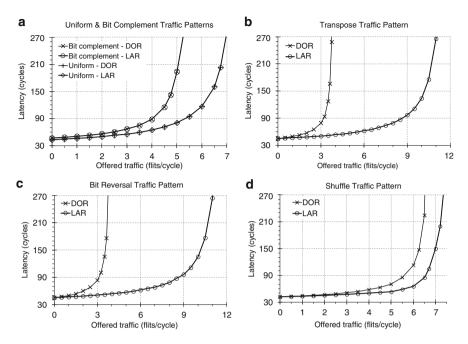

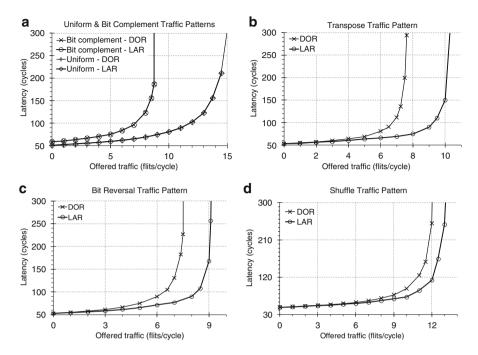

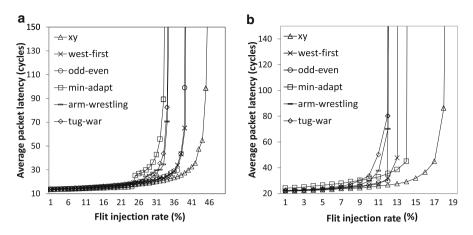

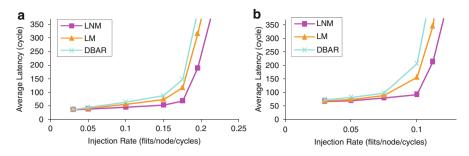

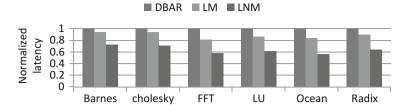

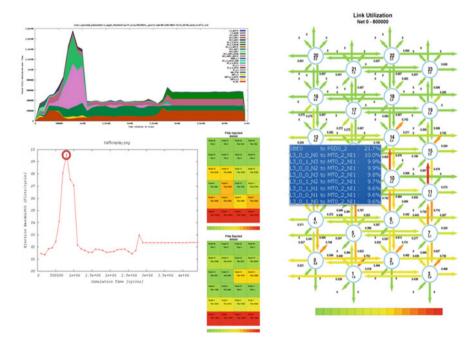

Fig. 1.13 Delay variation (a) and throughput variation (b) under Transpose 2 traffic

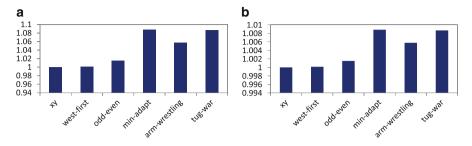

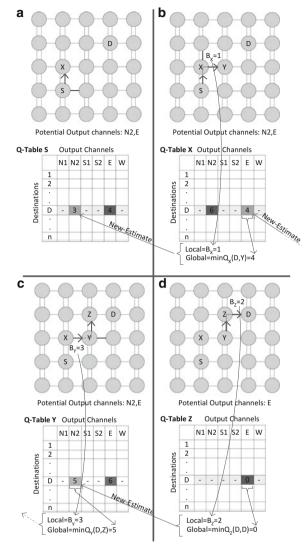

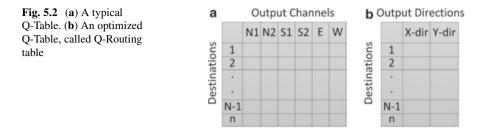

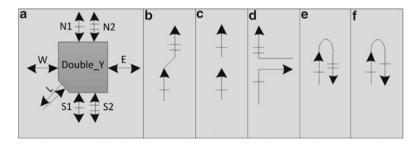

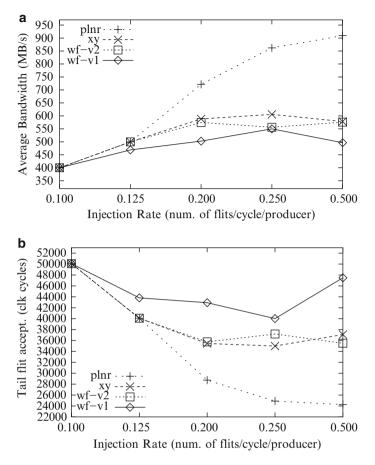

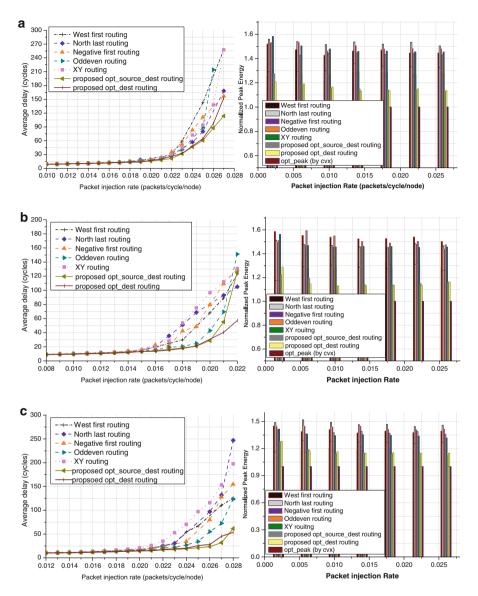

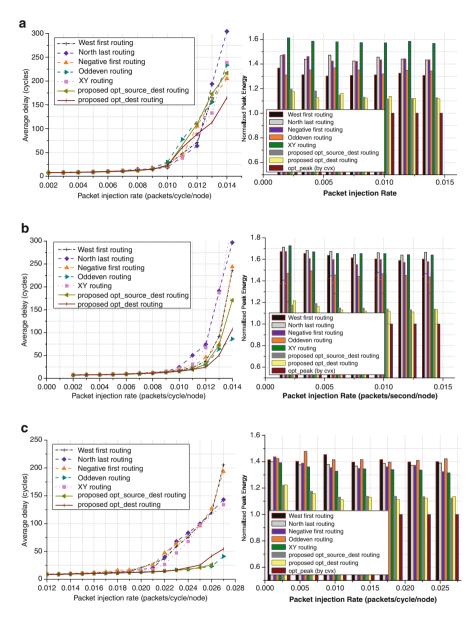

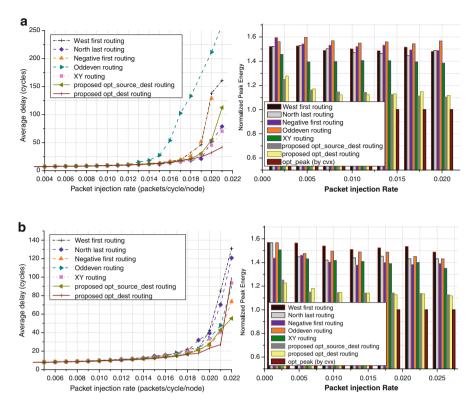

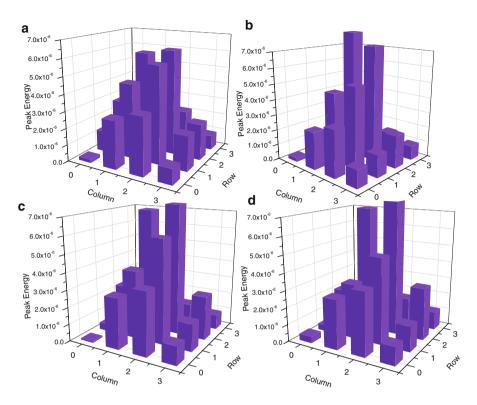

Usually, the average delay and the average throughput are reported by means of a diagram for different packet injection rates. An example of such a diagrams is shown in Fig. 1.13. The figure shows the delay variation and throughput variation under *Transpose 2* [9] traffic scenarios for different routing functions (XY, Odd-Even [6], and APSRA [30]) and different selection policies (random, buffer-level [30]).

#### 1.9 Summary

In this chapter, several important concepts in the domain of NoC design were presented. We have discussed various topologies for direct and indirect networks. Different switching, flow control mechanisms along with using virtual channels, routing schemes, output selection technique, and a general network-on-chip architecture were also described. These concepts presented here are further mentioned in various places in the rest of this book.

#### References

- G. Ascia, V. Catania, M. Palesi, D. Patti, Implementation and analysis of a new selection strategy for adaptive routing in networks-on-chip. IEEE Trans. Comput. 57(6), 809–820 (2008)

- L. Benini, G.D. Micheli, Networks on chips: a new SoC paradigm. IEEE Comput. 35(1), 70–78 (2002)

- 3. D.P. Bertsekas, R.G. Gallager, Data Networks (Prentice Hall, Englewood Cliffs, 1992)

- C.-H. Chao, K.-Y. Jheng, H.-Y. Wang, J.-C. Wu, A.-Y. Wu, Traffic- and thermal-aware run-time thermal management scheme for 3D NoC systems, in *ACM/IEEE International Symposium on Networks-on-Chip*, Grenoble, 2010, pp. 223–230

- A.A. Chien, J.H. Kim, Planar-adaptive routing: low-cost adaptive networks for multiprocessors. J. ACM 42(1), 91–123 (1995)

- 1 Basic Concepts on On-Chip Networks

- 6. G.-M. Chiu, The odd-even turn model for adaptive routing. IEEE Trans. Parallel Distrib. Syst. **11**(7), 729–738 (2000)

- W.J. Dally, C. Seitz, Deadlock-free message routing in multiprocessor interconnection networks. IEEE Trans. Comput. C(36), 547–553 (1987)

- 8. W.J. Dally, B. Towles, Route packets, not wires: on-chip interconnection networks, in *ACM/IEEE Design Automation Conference*, Las Vegas, 2001, pp. 684–689

- W.J. Dally, B. Towles, *Principles and Practices of Interconnection Networks* (Morgan Kaufmann, San Francisco, 2004)

- M. Daneshtalab, M. Ebrahimi, T.C. Xu, P. Liljeberg, H. Tenhunen, A generic adaptive pathbased routing method for MPSoCs. Elsevier J. Syst. Archit. 57(1), 109–120 (2011)

- M.M. de Azevedo, D. Blough, Fault-tolerant clock synchronization of large multicomputers via multistep interactive convergence, in *International Conference on Distributed Computing Systems*, Hong Kong, 1996, pp. 249–257

- 12. J. Duato, A new theory of deadlock-free adaptive routing in wormhole networks. IEEE Trans. Parallel Distrib. Syst. **4**(12), 1320–1331 (1993)

- 13. J. Duato, A necessary and sufficient condition for deadlock-free routing in wormhole networks. IEEE Trans. Parallel Distrib. Syst. **6**(10), 1055–1067 (1995)

- 14. J. Duato, S. Yalamanchili, L. Ni, *Interconnection Networks: An Engineering Approach* (Morgan Kaufmann, San Francisco, 2002)

- M. Ebrahimi, M. Daneshtalab, F. Fahimeh, P. Liljeberg, J. Plosila, M. Palesi, H. Tenhunen, HARAQ: congestion-aware learning model for highly adaptive routing algorithm in on-chip networks, in ACM/IEEE International Symposium on Networks-on-Chip, Copenhagen, May 2012, pp. 19–26

- M. Ebrahimi, M. Daneshtalab, P. Liljeberg, J. Plosila, J. Flich, H. Tenhunen, Path-based partitioning methods for 3d networks-on-chip with minimal adaptive routing. IEEE Trans. Comput. 99, pp. 1, doi: 10.1109/TC.2012.255

- M. Ebrahimi, M. Daneshtalab, P. Liljeberg, J. Plosila, H. Tenhunen, Cluster-based topologies for 3D networks-on-chip using advanced inter-layer bus architecture. Elsevier J. Comput. Syst. Sci. 79(4), 475–491 (2013)

- C.J. Glass, L.M. Ni, The turn model for adaptive routing. J. Assoc. Comput. Mach. 41(5), 874–902 (1994)

- J. Hu, R. Marculescu, DyAD smart routing for networks-on-chip, in ACM/IEEE Design Automation Conference, San Diego, 7–11 June 2004, pp. 260–263

- 20. ITRS 2011 edition, International Technology Roadmap for Semiconductors (2011). http:// www.itrs.net/

- 21. A. Jantsch, H. Tenhunen (eds.), Networks on Chip, chapter 1 (Kluwer Academic, Boston, 2003)

- S. Kumar, A. Jantsch, J.-P. Soininen, M. Forsell, M. Millberg, J. Oberg, K. Tiensyrja, A. Hemani, A network on chip architecture and design methodology, in *IEEE Computer Society Annual Symposium on VLSI*, Pittsburg, p. 117, 2002

- K. Li, R. Schaefer, A hypercube shared virtual memory, in *International Conference on Parallel Processing*, University Park, 1989, pp. 125–132

- X. Lin, L.M. Ni, Multicast communication in multicomputer networks. IEEE Trans. Parallel Distrib. Syst. 4, 1105–1117 (1993)

- P.K. McKinley, H. Xu, E.T. Kalns, L.M. Ni, CompaSS: efficient communication services for scalable architectures, in *International Conference on Supercomputing*, Washington, D.C., 1992, pp. 478–487

- G.D. Micheli, L. Benini, Powering networks on chips: energy-efficient and reliable interconnect design for SoCs, in *International IEEE Symposium on Systems Synthesis*, Montréal, 2001, pp. 33–38

- P. Mohapatra, Wormhole routing techniques for directly connected multicomputer systems. ACM Comput. Surv. 30(8), 374–410 (1998)

- L.M. Ni, P.K. McKinley, A survey of wormhole routing techniques in direct networks. IEEE Comput. 26, 62–76 (1993)

- E. Nilsson, M. Millberg, J. Oberg, A. Jantsch, Load distribution with the proximity congestion awareness in a network on chip, in *Design, Automation and Test in Europe*, Washington, D.C., 2003, pp. 1126–1127

- M. Palesi, R. Holsmark, S. Kumar, V. Catania, Application specific routing algorithms for networks on chip. IEEE Trans. Parallel Distrib. Syst. 20(3), 316–330 (2009)

- D. Park, S. Eachempati, R. Das, A. Mishra, Y. Xie, N. Vijaykrishnan, C.R. Das, MIRA: a multilayered on-chip interconnect router architecture, in *International Symposium on Computer Architecture*, Beijing, 2008, pp. 251–261

- 32. J. Upadhyay, V. Varavithya, P. Mohapatra, A traffic-balanced adaptive wormhole routing scheme for two-dimensional meshes. IEEE Trans. Comput. **46**(2), 190–197 (1997)

- H. Xu, P.K. McKinley, E.T. Kalns, L.M. Ni, Efficient implementation of barrier synchronization in wormhole-routed hypercube multicomputers. J. Parallel Distrib. Comput. 16, 172–184 (1992)

- T.T. Ye, L. Benini, G.D. Micheli, Packetization and routing analysis of on-chip multiprocessor networks. J. Syst. Archit. 50(2–3), 81–104 (2004)

## Part I Performance Improvement

## Chapter 2 A Heuristic Framework for Designing and Exploring Deterministic Routing Algorithm for NoCs

Abbas Eslami Kiasari, Axel Jantsch, and Zhonghai Lu

**Abstract** In this chapter, we present a system-level framework for designing minimal deterministic routing algorithms for Networks-on-Chip (NoCs) that are customized for a set of applications. To this end, we first formulate an optimization problem of minimizing average packet latency in the network and then use the simulated annealing heuristic to solve this problem. To estimate the average packet latency we use a queueing-based analytical model which can capture the burstiness of the traffic. The proposed framework does not require virtual channels to guarantee deadlock freedom since routes are extracted from an acyclic channel dependency graph. Experiments with both synthetic and realistic workloads show the effectiveness of the approach. Results show that maximum sustainable throughput of the network is improved for different applications and architectures.

#### 2.1 Introduction

Thanks to high performance and low power budget of ASICs (application specific integrated circuits), they have been common components in the design of embedded systems-on-chip. Advances of semiconductor technology facilitate the integration of reconfigurable logic with ASIC modules in embedded systems-on-chip. Reconfigurable architectures are used as new alternatives for implementing a wide range of computationally intensive applications, such as DSP, multimedia and computer vision applications [1]. In the beginning of the current millennium, network-on-chip (NoC) emerged as a standard solution in the on-chip architectures [10, 11].

A.E. Kiasari (🖂) • A. Jantsch • Z. Lu

KTH Royal Institute of Technology, Stockholm, Sweden e-mail: kiasari@kth.se

In network-based systems, the performance of the communication infrastructure is critical, as it can represent the overall system performance bottleneck. The performance of networks depends heavily on the routing algorithm effectiveness, since it impacts all network metrics such as latency, throughput, and power dissipation.

Routing algorithms are generally categorized into deterministic and adaptive. A deterministic routing algorithm is oblivious of the dynamic network conditions and always provides the same path between a given source and destination pair. In contrast, in adaptive routing algorithms, besides source and destination addresses, network traffic variation plays an important role for selecting channels to forward packets. However, adaptive routing may cause packets to arrive out-of-order since they may be routed along different paths. The re-order buffers needed at the destination for ordering the packets impose large area and power on system [18]. Deterministic routers not only are more compact and faster than adaptive routers [5], but also guarantee in-order packet delivery. Therefore, it is not surprising that designers would like to use deterministic routing algorithms in the NoCs which suffer from limited silicon resources. However, in deterministic routing a packet cannot use alternative paths to avoid congested channels along its route; this leads to degraded performance of the communication architecture at high levels of network throughput.

A well-designed routing algorithm utilizes the network resources uniformly as much as possible and avoids the congested channels, even in the presence of nonuniform traffic patterns, which are usual in the embedded systems. In this chapter, we propose a system-level Latency-Aware Routing (LAR) framework for designing minimal deterministic routing algorithms for network-based platforms. Especially, LAR is appropriate for reconfigurable embedded systems-on-chip which host several applications with high computational requirements and static workloads. To the best of our knowledge, the proposed framework is the first one to deal with traffic burstiness. Before the execution of a new application, the routing tables are configured with pre-computed routes, as well as other components in the system. After selecting the route and adding it to the packet, no further time is needed on routing at the intermediate nodes along the path. Due to advantages of table-based routing, it is one of the most widely used routing methods for implementing deterministic routing algorithm, e.g., IBM SP1 and SP2 [5].

LAR uses a recently proposed analytical model in [14] to calculate the average packet latency in the network. The results obtained from simulation experiments confirm that the proposed routing framework can find efficient routes for various networks and workloads.

The rest of the chapter is organized as follows. We start by reviewing previous studies in Sect. 2.2. The proposed heuristic framework is proposed in Sect. 2.3. Experimental results in Sect. 2.4 show that our proposed approach can improve the system performance. Finally, concluding remarks are given in Sect. 2.5.

### 2.2 Related Work

Turn model for designing partially adaptive routing algorithms for mesh and hypercube networks was proposed in [9]. Prohibiting minimum number of turns breaks all of the cycles and produces a deadlock-free routing algorithm. Turn model was used to develop the Odd-Even adaptive routing algorithm for meshes [4]. This model restricts the locations where some turns can be taken so that deadlock is avoided. In comparison with turn model, the degree of routing adaptivity provided by the Odd-Even routing is more even for different source-destination pairs.

DyAD routing scheme, which combines deterministic and adaptive routing, is proposed in [12] for NoCs, where the router works in deterministic mode when the network is not congested, and switches to adaptive mode when the network becomes congested. In [23] the authors extend routers of a network to measure their load and to send appropriate load information to their direct neighbors. The load information is used to decide in which direction a packet should be routed to avoid hot-spots. Recently, the authors in [19] present APSRA, a methodology to develop adaptive routing algorithms for NoCs that are specialized for an application or a set of concurrent applications. APSRA exploits the application-specific information regarding pairs of cores that communicate and other pairs that never communicate in the NoC platform to maximize communication adaptivity and performance.

Since all of these approaches are based on adaptive routing, they suffer from outof-order packet delivery. Our proposed routing framework overcomes this problem while it minimizes the average packet latency across the network.

An application-aware oblivious routing is proposed in [14] that statically determines deadlock-free routes. The authors presented a mixed integer-linear programming approach and a heuristic approach for producing routes that minimize maximum channel load. However, in case of realistic workload, they did not study the effect of task mapping on their approach. Also, we have addressed the congestion-aware routing problem in [15]. With the analysis technique, we first estimated the congestion level in the network, and then embedded this analysis technique into the loop of optimizing routing paths so as to find deterministic routing paths for all traffic flows while minimizing the congestion level in the network. Since this framework cannot capture the traffic burstiness, in this work we utilize an analytical model [14] to deal with traffic burstiness.

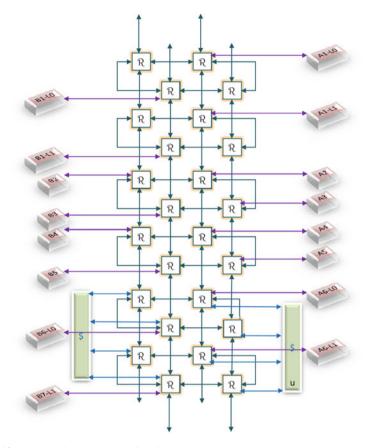

#### 2.3 LAR Framework

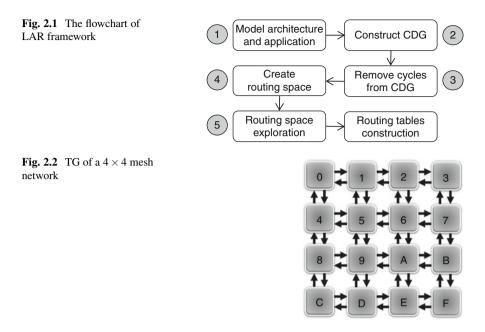

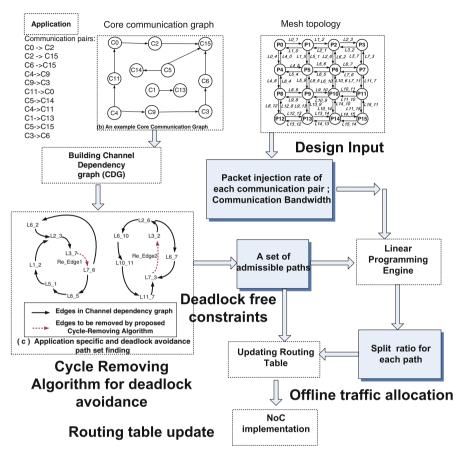

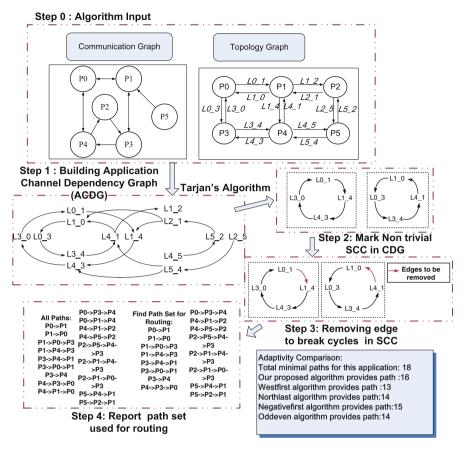

The LAR framework consists of five steps as its flowchart is shown in Fig. 2.1. At first, we represent the architecture and application using *topology graph* (TG) and *communication graph* (CG), respectively. Then we construct the *channel dependency graph* (CDG) based on TG and CG. In the third step, an acyclic CDG is extracted by deleting some edges from CDG to guarantee the deadlock freedom.

After that, we find all possible shortest paths for each flow to create the routing space. Finally, we formulate an optimization problem over the routing space and solve it. In the following subsections, each step is described in detail.

### 2.3.1 Model Architecture and Application

In order to characterize network performance, a network model is essential. As shown in Fig. 2.2, a directed graph, which is called *Topology Graph (TG)*, can represent the topology of an NoC architecture. Vertices and edges of TG show nodes and links of the NoC, respectively. Every node in TG contains a core and a wormhole-switched router. Such cores are local computing or storage regions, which may contain a processor, a DSP core, a configurable hardware, a high-bandwidth I/O controller, or a memory block. Each core is equipped with a Resource Network Interface (RNI). The RNI translates data between cores and routers by packing/unpacking data packets and also manages the packet injection process. Packets are injected into the network on injection channel and leave the network from ejection channel. We consider the general reference architecture for routers [7], where a routing logic determines the output channel over which the packet advances. Routing is only performed with the head flit of a packet. After routing phase, a crossbar switch handles the connections among input and output channel.

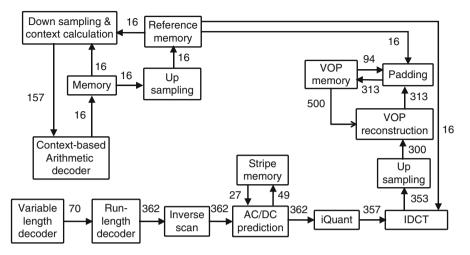

An application can be modeled by a graph called *Communication Graph* (CG). CG is a directed graph, where each vertex represents one selected task, and each

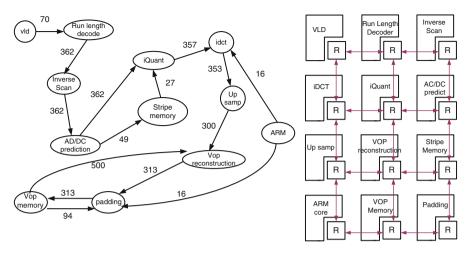

Fig. 2.3 CG of a video object plane decoder (VOPD) application [24]

directed arc represents the communication volume from source task to destination task. As an example, the CG of a video object plane decoder (VOPD) is shown in Fig. 2.3 [24]. Each node in the CG corresponds to a task and the numbers near the edges represent the bandwidth (in MBytes/s) of the data transfer, for a 30 frames/s MPEG-4 movie with  $1,920 \times 1,088$  resolution [24].

#### 2.3.2 Construct Channel Dependency Graph

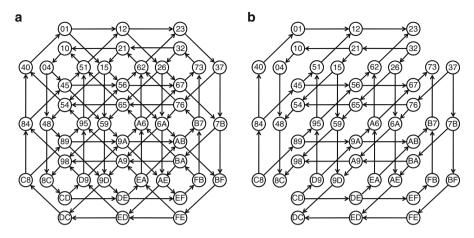

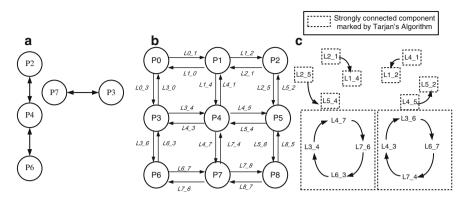

Dally and Seitz simplified designing deadlock-free routing algorithms with a proof that an acyclic channel dependency graph (CDG) guarantees deadlock freedom [6]. Each vertex of the CDG is a channel in TG. For instance, vertex 01 in Fig. 2.4 corresponds to the channel from node 0 to node 1 in Fig. 2.2. There is a directed edge from one vertex in CDG to another if a packet is permitted to use the second channel in TG immediately after the first one. To find the edges of a CDG, we use the *Dijkstra's algorithm* to find all shortest paths between source and destination of any flows in corresponding TG. CDG of a  $4 \times 4$  mesh network (Fig. 2.2) under minimal fully adaptive routing is shown in Fig. 2.4a, when any two nodes have the need to communicate such as in the uniform traffic pattern.

#### 2.3.3 Remove Cycles from CDG

Traditional routing algorithms, such as *dimension-order routing* (DOR) and turn model, extract an acyclic CDG by systematically removing some edges from the CDG regardless of the traffic pattern. This may result in poor performance of

Fig. 2.4 The CDG of  $4 \times 4$  mesh network for minimal fully adaptive routing under (a) uniform and (b) transpose traffic patterns

**Table 2.1** Number of cyclesin CDG of mesh networks

|                     | Number of cycles in |

|---------------------|---------------------|

| TG                  | corresponding CDG   |

| Mesh $(2 \times 2)$ | 2                   |

| Mesh $(2 \times 3)$ | 8                   |

| Mesh $(3 \times 3)$ | 292                 |

| Mesh $(3 \times 4)$ | 14,232              |

| Mesh $(4 \times 4)$ | 6,982,870           |

| Mesh $(4 \times 5)$ | 3,656,892,444       |

routing algorithm due to prohibition of unnecessary turns. For instance, as shown in Fig. 2.4b, there is no cycle in CDG of  $4 \times 4$  mesh network under transpose traffic pattern, which the node in row *i* and column *j* sends packets to the node in row *j* and column *i*. However, traditional routing algorithms conservatively remove some edges from the CDG.

We modify the *depth-first-search* (*dfs*) algorithm to find cycles in a given CDG. Since we want to remove minimum number of edges, we delete an edge from the CDG which is shared among more cycles. Note that, this edge is removed if the reachability of all flows is guaranteed. For example, in a CDG of  $4 \times 4$  mesh network, shown in Fig. 2.4a, there are 6,982,870 cycles and the edge from vertex 40 to vertex 01 is shared among 5,041,173 cycles. Thus by removing this edge from the CDG, the number of cycles is considerably reduced to 1,941,697. These steps are repeated again while there is no cycle in the CDG. Table 2.1 shows the numbers of cycles found by LAR in the CDG of different mesh networks. As it can be vividly seen, number of cycles is exponentially grown with the size of the TG and it takes a long time to find all cycles in the CDG. Hence, we find cycles in the CDG till certain number of cycles, and then remove an edge from the CDG which is shared among more cycles.

#### 2.3.4 Create Routing Space (RS)

In this step, we apply Dijkstra's algorithm to the acyclic CDG to find all shortest paths between source and destination of flows in corresponding TG and create a set of *f* flows  $RS = \{F_1, F_2, \dots, F_f\}$  where *f* is the number of all flows in the system.  $F_i = (\lambda_i, C_{A_i}, n_i, P_i)$ , where  $\lambda_i$  is the average packet generation rate and  $C_{A_i}$  is the coefficient of variation (CV) of packet interarrival time for flow *i*. We remind that the relationship between CV of random variable *X* and its moments is represented by  $C_X^2 = \overline{x^2}/\overline{x^2} - 1$ . In [14], we show that CV of a random variable reflects the burstiness intensity very well.  $n_i$  is the number of available shortest paths for flow *i*.

Usually more than one shortest path is available between two nodes  $(n_i > 1)$  in the routing space *RS*, so it is reasonable to choose a path such that the average packet latency is minimized. In the next subsection, we formulate an optimization problem over *RS* to find a suitable route for each flow and then use the simulated annealing heuristic to solve this problem.

#### 2.3.5 Routing Space Exploration

#### 2.3.5.1 Define Optimization Problem

In this subsection, we define an optimization problem to explore the routing space of *RS*. It is essential to define *decision variables* and *objective functions* in formulating an optimization problem. Our goal is to select a path for flow i  $(1 \le i \le f)$  among  $n_i$  available paths to minimize the average packet latency. Therefore, we define  $X = \{x_1, x_2, \ldots, x_f\}$  as decision variables in the space of *RS* where  $x_i$  refers to a path number for flow i  $(1 \le x_i \le n_i)$  and the average packet latency as objective function.

The use of simulation experiments makes the task of searching for efficient designs computationally intensive and does not scale well with the size of networks since the search space of such a problem increases dramatically with the system size. Therefore, it is simply impossible to use the simulation in optimization loops. In the following subsection, we use an efficient analytical model to find nearly optimal solutions in reasonable time.

#### 2.3.5.2 Analytical Latency Model

If the performance of a routing algorithm is measured in terms of average packet latency, then maximizing the performance means, in fact, minimizing the endto-end packet latency. In this section, we briefly review a recently proposed analytical performance model which estimates the average packet latency in on-chip networks [14]. In a wormhole switched network, the end-to-end delay of a packet consists of two parts: the latency of the head flit and the latency of the body flits which follow the header flit in a pipelined fashion. The average latency of the head flit can be computed as the sum of delays at each hop, clearly, the link delays the head flit experienced and the residence times of the head flit in each of the routers along the path. Therefore, generally the only unknown parameter for computing the average packet latency is the mean waiting time for a packet from input channel *i* to output channel *j* in router  $N(W_{i \rightarrow j}^N)$ . Using a G/G/1 priority queueing model, we estimated this value by [14]

$$W_{i \to j}^{N} = \begin{cases} \frac{\rho_{j}^{N} \left( C_{A}^{2} + C_{S_{j}^{N}}^{2} \right)}{2 \left( \mu_{j}^{N} - \lambda_{1 \to j}^{N} \right)}, & i = 1, \\ \frac{\lambda_{j}^{N} \left( C_{A}^{2} + C_{S_{j}^{N}}^{2} \right)}{2 \left( \mu_{j}^{N} - \sum_{k=1}^{i-1} \lambda_{k \to j}^{N} \right)^{2}}, & 2 \le i \le p \end{cases}$$

$$(2.1)$$

where the variables are listed in Table 2.2 along with other parameters used in this chapter. Therefore, to compute the  $W_{i \rightarrow j}^N$  we have to calculate the arrival rate from  $IC_i^N$  to  $OC_j^N(\lambda_{i \rightarrow j}^N)$ , and also first and second moments of the service time of  $OC_j^N(\bar{S}_j^N, (\bar{S}_j^N)^2)$ . In the following two subsections, packet arrival rate and channel service time are computed.

Assuming the network is not overloaded, the arrival rate from  $IC_i^N$  to  $OC_j^N$  can be calculated using the following general equation

$$\lambda_{i \to j}^{N} = \sum_{S} \sum_{D} \lambda^{S} \times P^{S \to D} \times R\left(S \to D, IC_{i}^{N} \to OC_{j}^{N}\right)$$

(2.2)

In Eq. 2.2, the routing function  $R(S \to D, IC_i^N \to OC_j^N)$  equals 1 if a packet from  $IP^S$  to  $IP^D$  passes from  $IC_i^N$  to  $OC_j^N$ ; it equals 0 otherwise. Note that we assume a deterministic routing algorithm, thus the function of  $R(S \to D, IC_i^N \to OC_j^N)$  can be predetermined, regardless of topology and routing algorithm. After that, the average packet rate to  $OC_j^N$  can be easily determined as

$$\lambda_j^N = \sum_i \lambda_{i \to j}^N \tag{2.3}$$

After estimating the packet arrival rates, now we focus on the estimation of the moments of channel service times. At first, we assign a positive integer index to each output channel. Let  $D_j^N$  be the set of all possible destinations for a packet which passes through  $OC_j^N$ . The index of  $OC_j^N$  is equal to the maximum of distances among *N* and each *M* where  $M \in D_j^N$ . Obviously, the index of a channel is between 1

| t <sub>r</sub>                           | Time spent for packet routing decision (cycles)                                                                    |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| ts                                       | Time spent for switching (cycles)                                                                                  |

| $t_w$                                    | Time spent for transmitting a flit between two adjacent routers (cycles)                                           |

| т                                        | Average size of packets (flits)                                                                                    |

| $L_b$                                    | The latency of body flits                                                                                          |

| $L^{S \rightarrow D}$                    | Average packet latency from $IP^S$ to $IP^D$ (cycles)                                                              |

| L                                        | Average packet latency in the network (cycles)                                                                     |

| $IP^N$                                   | The IP core located at address N                                                                                   |

| $R^N$                                    | The router located at address N                                                                                    |

| $IC_i^N$                                 | The <i>i</i> th input channel in router $R^N$                                                                      |

| $OC_i^N$                                 | The <i>j</i> th output channel in router $R^N$                                                                     |

| $OC_j^N$<br>$IB_i^N$                     | Capacity of the buffer in $IC_i^N$ (flits)                                                                         |

| $OB_j^N$                                 | Capacity of the buffer in $OC_i^N$ (flits)                                                                         |

| $P^{S \to D}$                            | Probability of a packet is generated in $IP^S$ and is delivered to $IP^D\left(\sum_{S}\sum_{D}P^{S\to D}=1\right)$ |

| $\lambda^N$                              | Average packet injection rate of $IP^N$ (packets/cycle)                                                            |

| $\lambda_{i \rightarrow i}^{N}$          | Average packet rate from $IC_i^N$ to $OC_j^N$ (packets/cycle)                                                      |

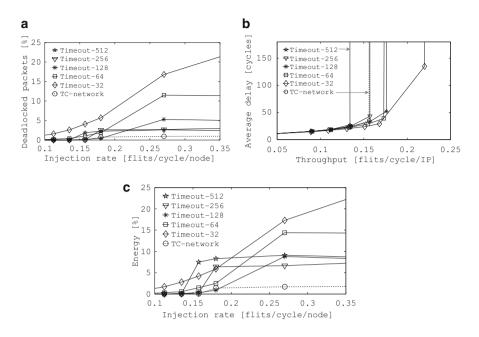

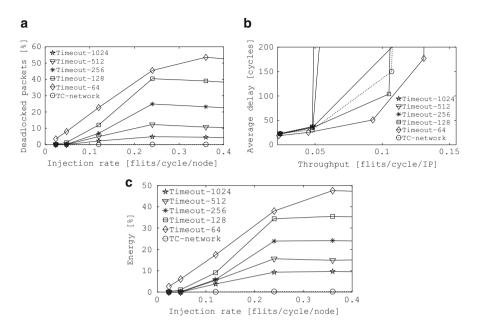

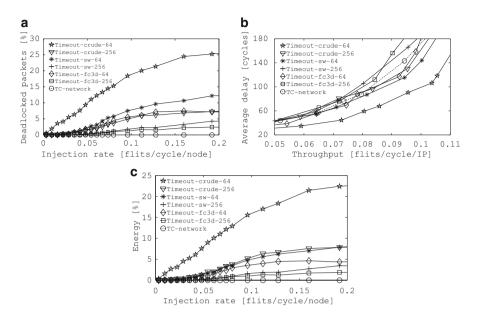

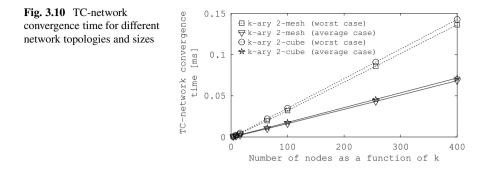

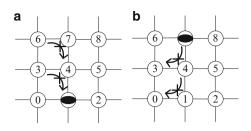

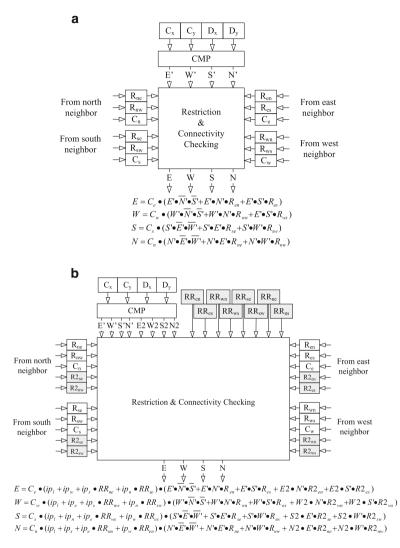

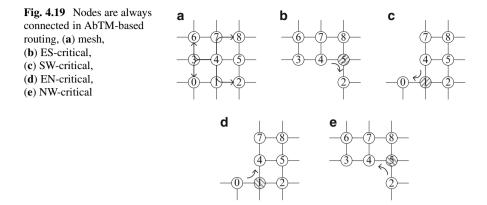

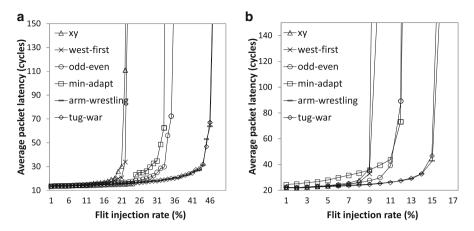

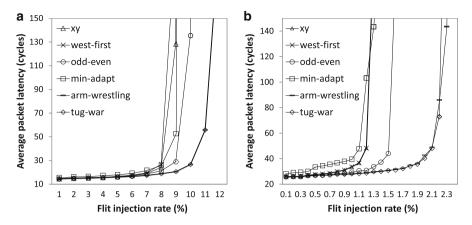

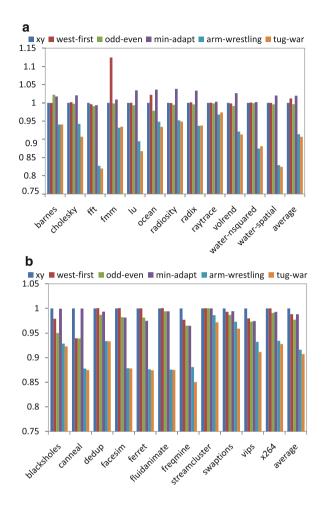

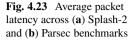

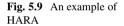

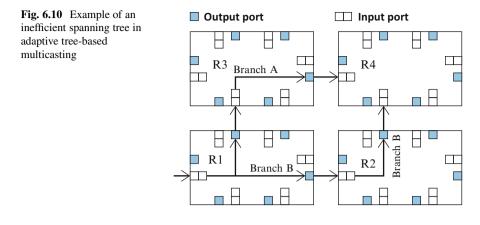

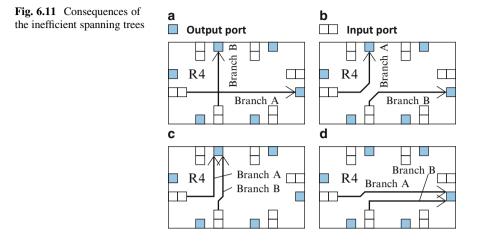

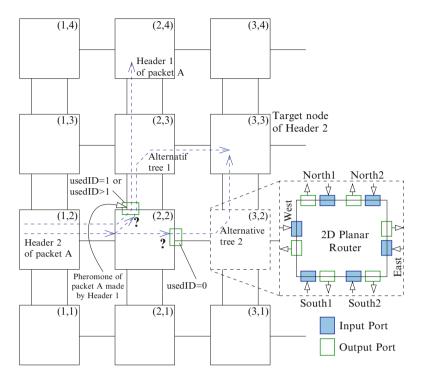

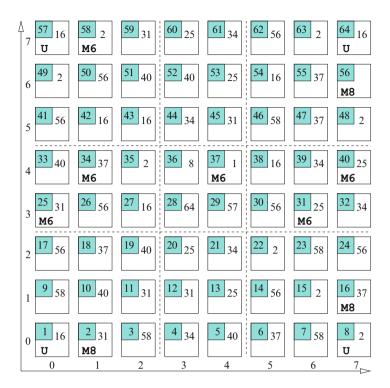

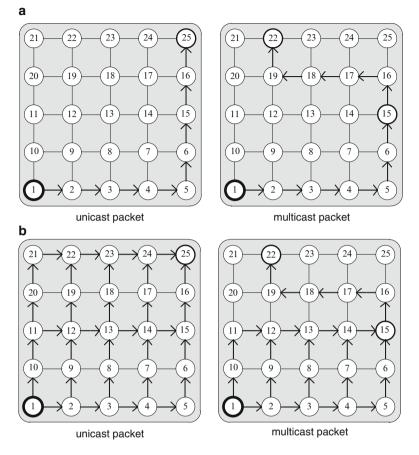

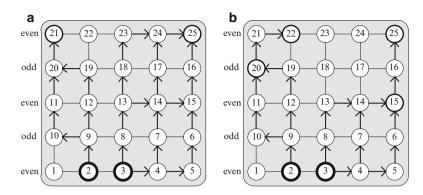

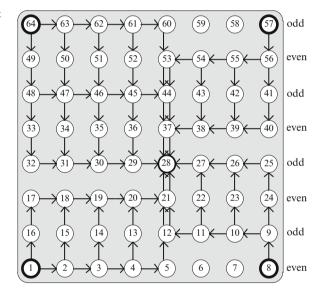

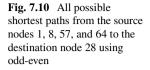

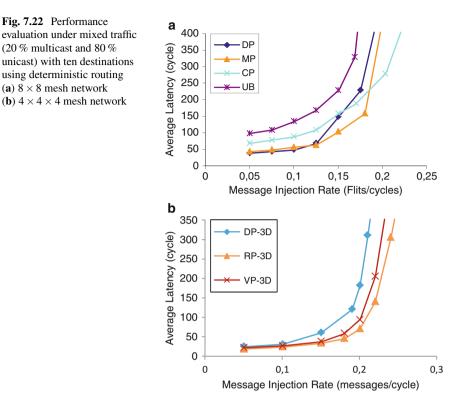

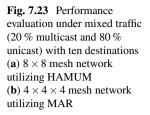

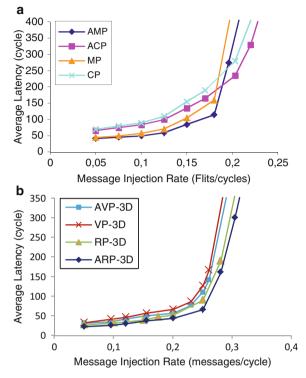

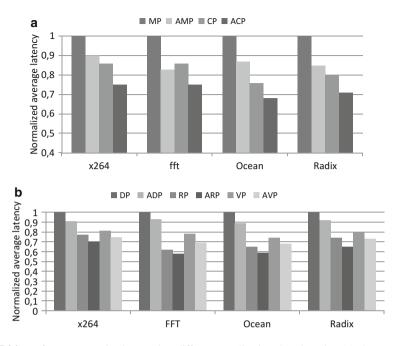

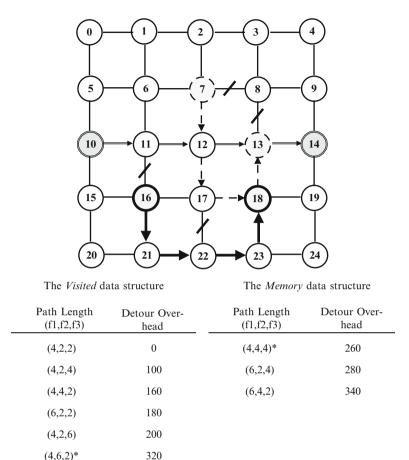

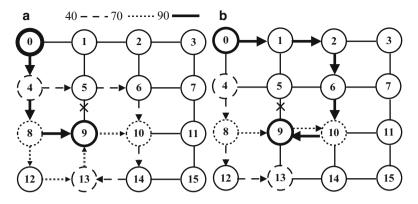

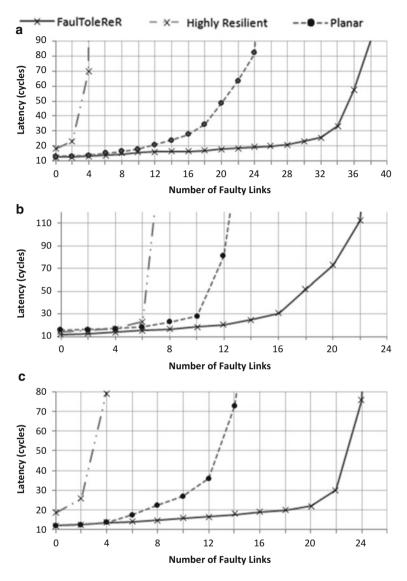

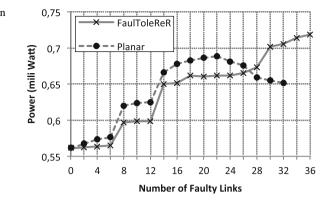

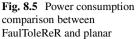

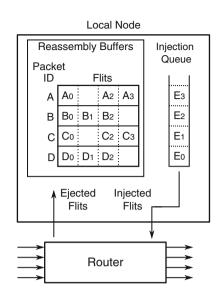

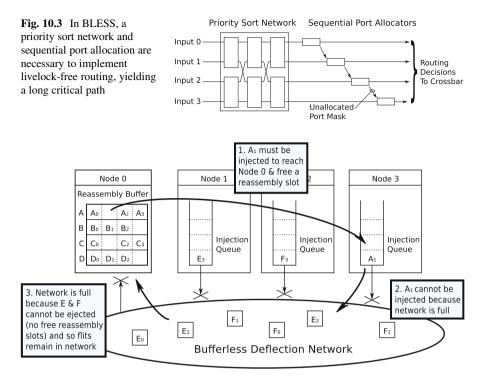

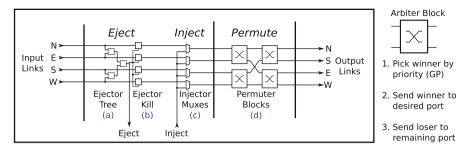

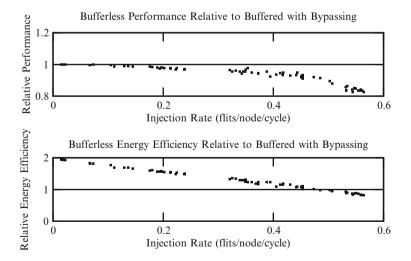

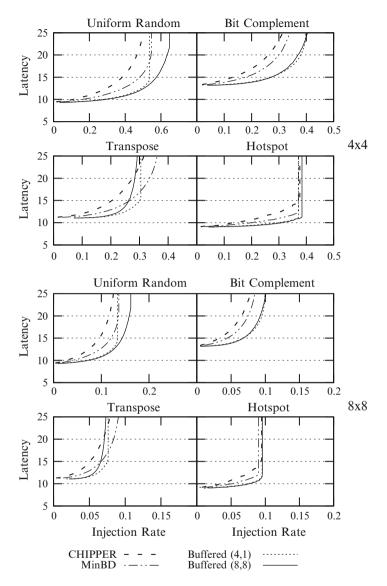

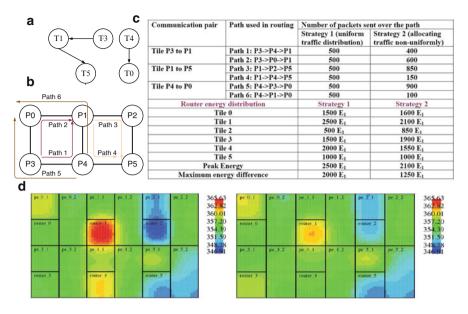

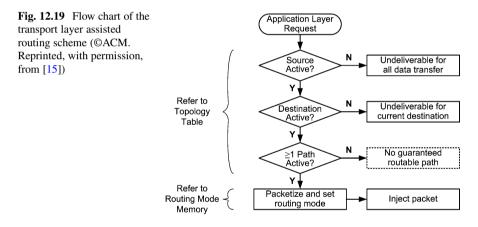

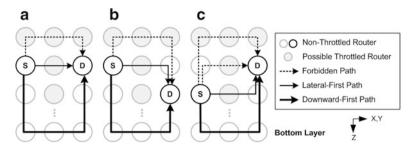

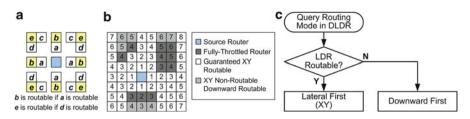

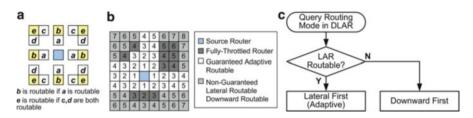

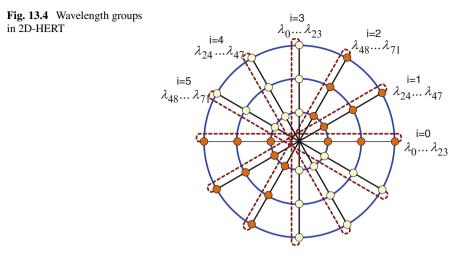

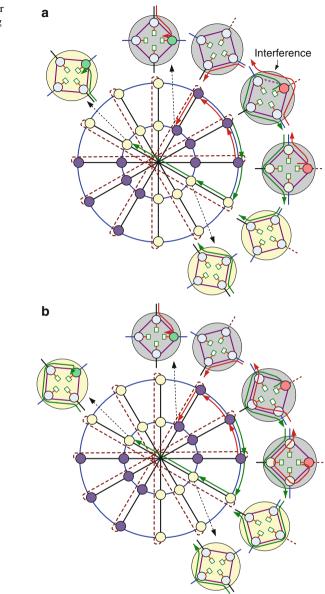

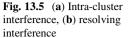

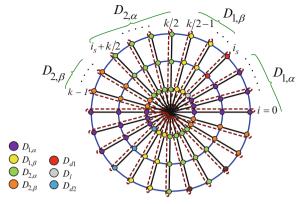

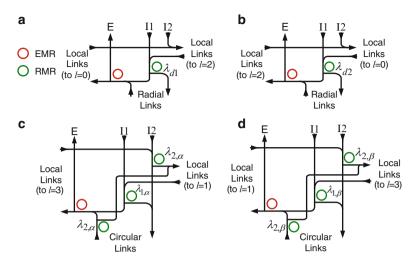

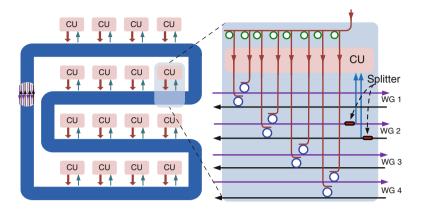

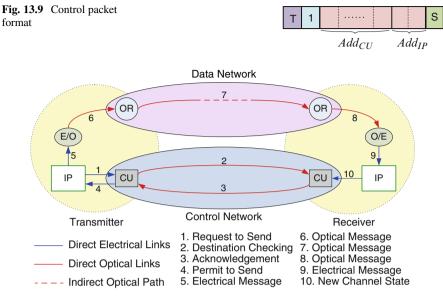

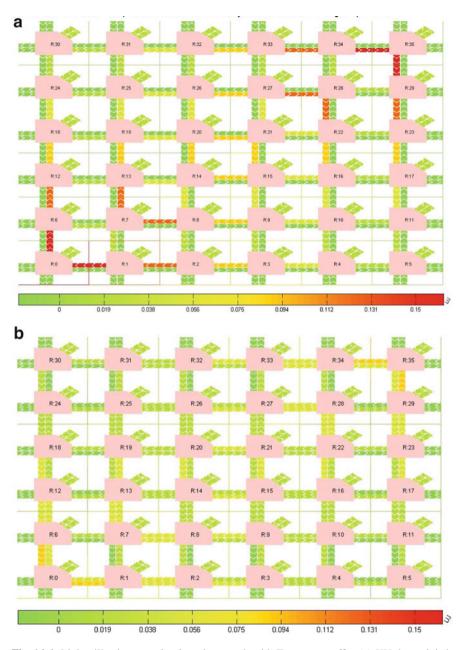

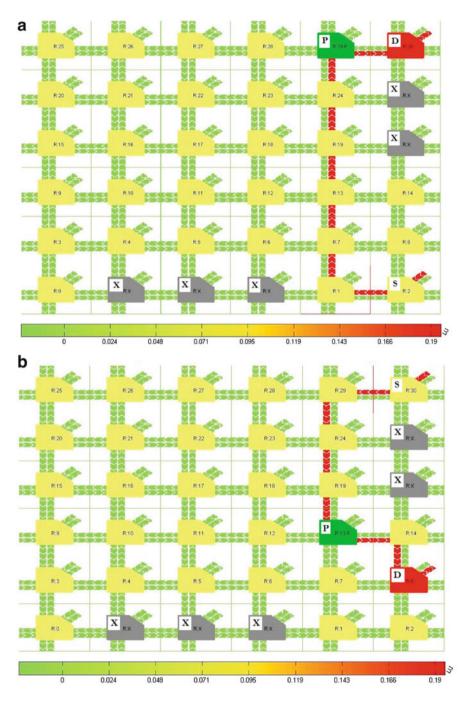

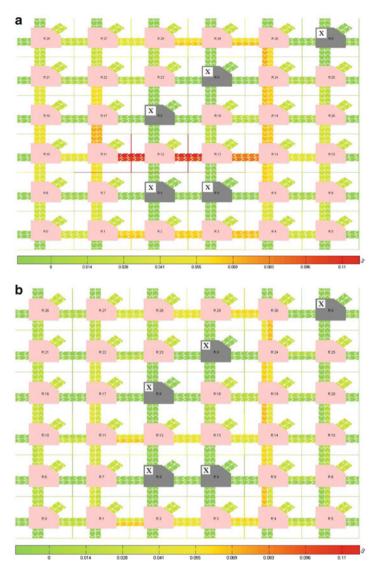

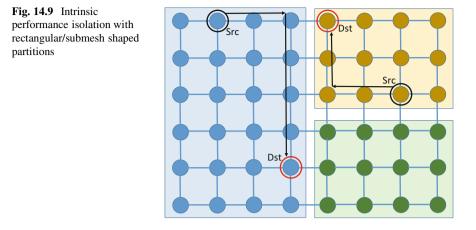

| $\lambda^N_{i ightarrow j}\ \lambda^N_j$ | Average packet rate to $OC_i^N$ (packets/cycle)                                                                    |