# Frank Kienle

# Architectures for Baseband Signal Processing

Architectures for Baseband Signal Processing

Frank Kienle

# Architectures for Baseband Signal Processing

Frank Kienle Department of Electrical Engineering TU Kaiserslautern Kaiserslautern Germany

ISBN 978-1-4614-8029-7 ISBN 978-1-4614-8030-3 (eBook) DOI 10.1007/978-1-4614-8030-3 Springer New York Heidelberg Dordrecht London

Library of Congress Control Number: 2013940940

© Springer Science+Business Media New York 2014

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed. Exempted from this legal reservation are brief excerpts in connection with reviews or scholarly analysis or material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. Duplication of this publication or parts thereof is permitted only under the provisions of the Copyright Law of the Publisher's location, in its current version, and permission for use must always be obtained from Springer. Permissions for use may be obtained through RightsLink at the Copyright Clearance Center. Violations are liable to prosecution under the respective Copyright Law. The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

While the advice and information in this book are believed to be true and accurate at the date of publication, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

For Nadine, Mara and Amelie

## Preface

Mobile communication devices like smart phones or tablet PCs enable us to consume information at every location and at every time. The rapid development of new applications and new services and the demand to access data in real time create an increasing throughput demand. The data have to be transmitted reliably to ensure the desired quality of service. Furthermore, an improved utilization of the bandwidth is desired to reduce the cost of transmission. All these demands lead to an increased complexity of the algorithms employed in wireless transceivers. In addition, the hardware realization of mobile transceivers has to feature a small area and power profile to reduce fabrication costs and to increase the user convenience. The rapid technology improvements of the chip industry allow the integration of more and more functionality on every chip.

Dealing with the increase of algorithmic complexity and required data throughput poses a big problem for the algorithm designer and the chip designer. An algorithm designer needs to understand the impact of his design decisions on the chip complexity, while a chip designer needs to understand the employed algorithms to enable an efficient implementation. Thus, a comprehensive understanding of algorithmic and architectural constraints becomes mandatory and has to be considered within educational programs, as well.

This manuscript addresses students in electrical engineering, computer engineering, and computer science with an interest in the field of communications engineering, architectures, and microelectronic design. An according lecture is given at the University of Kaiserslautern and the Karlsruhe Institute of Technology, both Germany. The manuscript puts a special focus on implementation aspects and implementation constraints of individual components that are needed in transceivers for current standards like UMTS, LTE, WiMAX, and DVB-S2. The application domain is the so-called outer receiver, which comprises the channel coding, interleaving stages, modulator, and multiple antenna transmission. Within a receiver device, the task of the outer receiver is to transmit information at the highest practical rate, as reliably as required by the application, i.e., voice or data transmission. Throughout the manuscript, the focus lies on advanced algorithms that are actually in use in modern communications systems. Their basic principles are always derived with a focus on the resulting communications and implementation performance.

Kaiserslautern, December 2012

Frank Kienle

#### Acknowledgments

This manuscript results from my work as 'Akademischer Rat' from 2008 until 2012 at the Microelectronic System Design Research Group at the University of Kaiserslautern. I would like to thank at least some of the numerous people who have in some way contributed to this work.

Especially, I would like to thank my mentor Prof. Dr.-Ing. Norbert Wehn for the opportunity to work in the interesting field of digital communication systems and VLSI design, for the numerous insightful and hot discussions.

I am very grateful for the colleagues I had the chance to work within the Microelectronic System Design Research Group: Michael J. Thul, Timo Vogt, Christian Neeb, Torben Brack, Daniel Schmidt, Matthias May, Timo Lehnigk-Emden, Matthias Alles, Christian Brehm, Christian de Schryver, Thomas Ilnseher, Christina Gimmler-Dumont, Christian Weis, and our secretary Martina Jahn. It is the team spirit that makes this group successful.

Especially, I would like to thank my wife, children, and parents for their encouragement and continuous support during my work.

# Contents

| 1 | Intr | oduction                                           | 1  |

|---|------|----------------------------------------------------|----|

|   | 1.1  | Application: Outer Receiver                        | 8  |

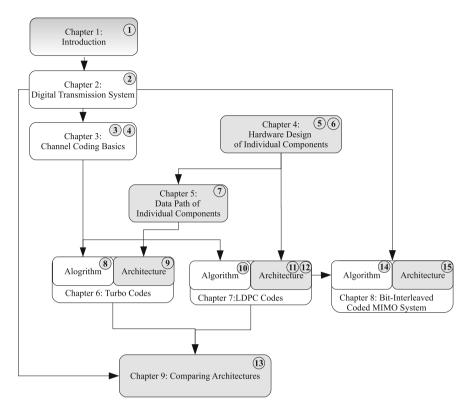

|   | 1.2  | Dependencies and Overview of Chapters              | 11 |

|   | Refe | prences                                            | 14 |

| 2 | Digi | tal Transmission System.                           | 17 |

|   | 2.1  | Channel Model                                      | 19 |

|   | 2.2  | Digital Modulator and Demodulator.                 | 24 |

|   | 2.3  | Channel Capacity                                   | 28 |

|   | 2.4  | Multiple Antenna Systems                           | 32 |

|   | Refe | prences                                            | 35 |

| 3 | Cha  | nnel Coding Basics                                 | 37 |

|   | 3.1  | Overview Channel Coding                            | 38 |

|   | 3.2  | Linear Block Codes                                 | 39 |

|   | 3.3  | General Decoding Problem                           | 42 |

|   |      | 3.3.1 Maximum Likelihood (ML) Decoding             | 42 |

|   |      | 3.3.2 ML Decoding by Solving IP Problems           | 44 |

|   |      | 3.3.3 Symbol-by-Symbol MAP Decoding                | 49 |

|   |      | 3.3.4 Max-Log-MAP Approximation                    | 51 |

|   | 3.4  | Convolutional Codes                                | 52 |

|   |      | 3.4.1 ML Decoding of Convolutional Codes           | 55 |

|   |      | 3.4.2 Max-Log-MAP Decoding of Convolutional Codes  | 58 |

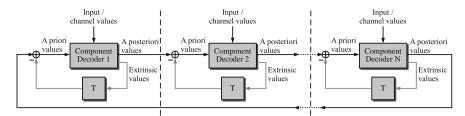

|   | 3.5  | Soft-Input Soft-Output (SISO) Decoder              | 62 |

|   | Refe | prences                                            | 64 |

| 4 | Har  | dware Design of Individual Components              | 67 |

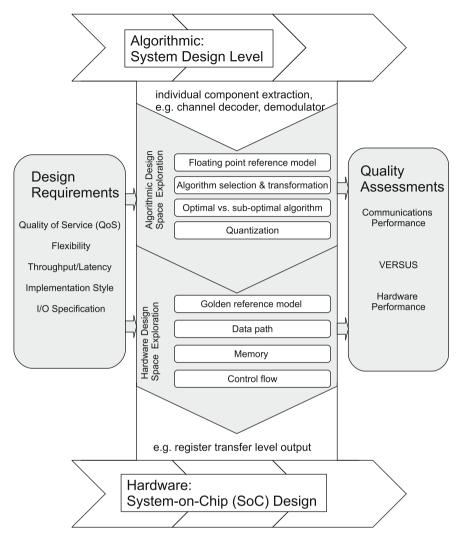

|   | 4.1  | Design Flow                                        | 68 |

|   |      | 4.1.1 Algorithmic Design Space Exploration         | 68 |

|   |      | 4.1.2 Hardware Design Space Exploration            | 70 |

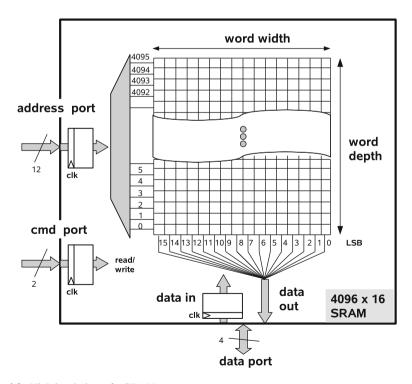

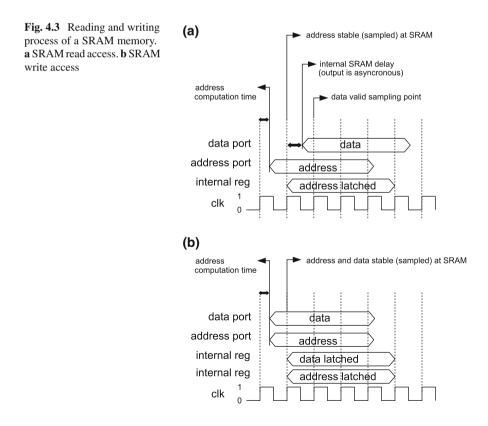

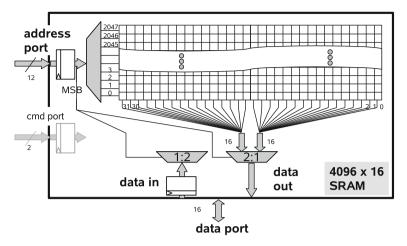

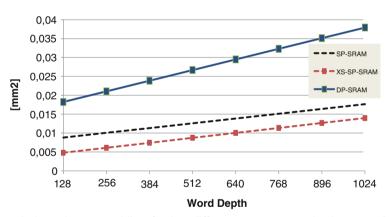

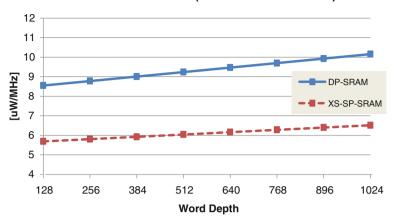

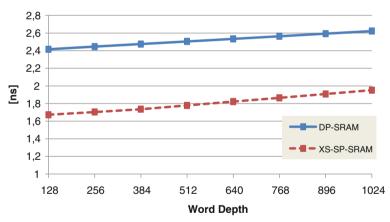

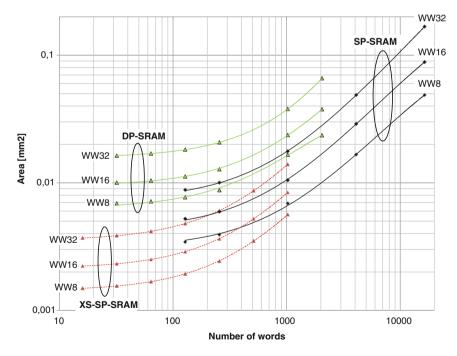

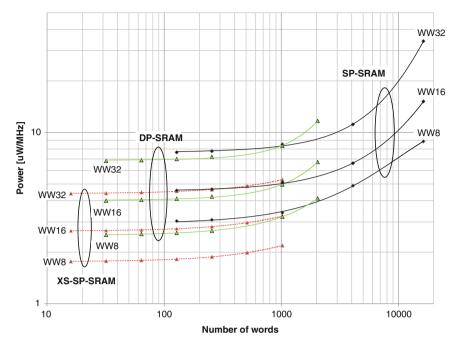

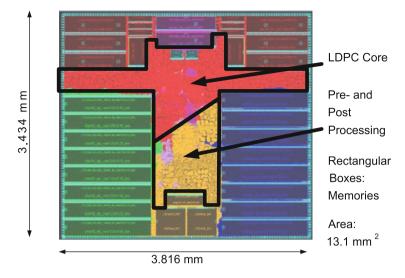

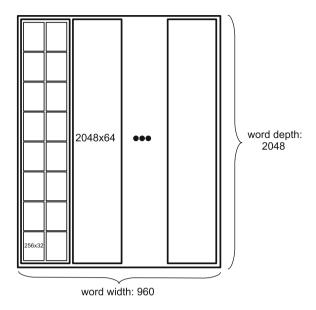

|   | 4.2  | SRAM Memories                                      | 73 |

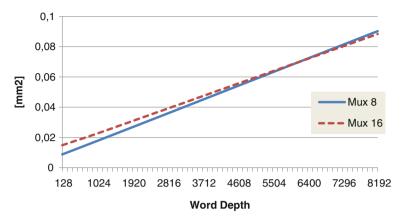

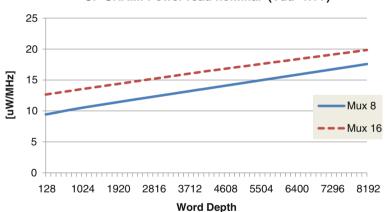

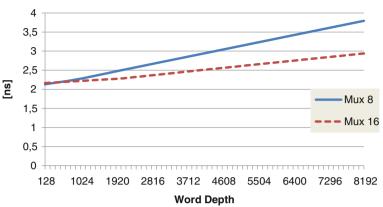

|   |      | 4.2.1 SRAM Design Space Exploration                | 76 |

|   |      | 4.2.2 Exemplary SRAM Data: Area, Power, Cycle Time | 79 |

|   |      |                                                    |    |

|   |      | 4.2.3 Importance of Memory Exploration         | 84  |

|---|------|------------------------------------------------|-----|

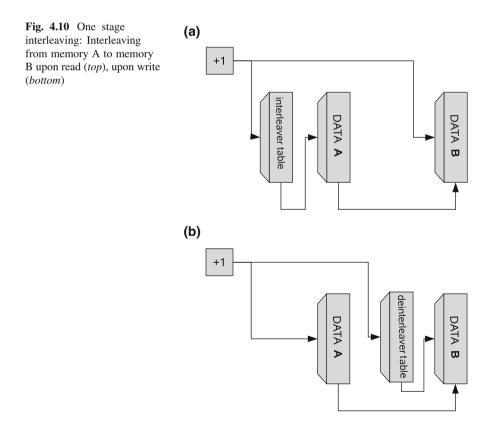

|   | 4.3  | Individual Component: Interleaver              | 87  |

|   |      | 4.3.1 Interleaver Types                        | 87  |

|   |      | 4.3.2 Hardware Realization                     | 90  |

|   | Refe | erences                                        | 95  |

| 5 | Data | a Path of Individual Components                | 97  |

|   | 5.1  | Data Flow to Data Path Example                 | 98  |

|   |      |                                                | 100 |

|   |      |                                                | 104 |

|   |      |                                                | 106 |

|   | 5.2  |                                                | 108 |

|   |      |                                                | 109 |

|   |      |                                                | 111 |

|   |      | 1                                              | 112 |

|   | Refe | • •                                            | 116 |

|   |      |                                                |     |

| 6 |      |                                                | 117 |

|   | 6.1  |                                                | 117 |

|   | 6.2  | 8                                              | 120 |

|   |      |                                                | 122 |

|   |      |                                                | 125 |

|   |      |                                                | 128 |

|   | 6.3  |                                                | 131 |

|   |      |                                                | 131 |

|   |      |                                                | 135 |

|   |      | 6.3.3 Dependencies of Architectural Parameters | 142 |

|   | Refe | prences                                        | 144 |

| 7 | Low  | -Density Parity-Check Codes                    | 147 |

|   | 7.1  |                                                | 147 |

|   | 7.2  |                                                | 150 |

|   | 7.3  |                                                | 155 |

|   |      |                                                | 155 |

|   |      |                                                | 158 |

|   |      |                                                | 160 |

|   | 7.4  |                                                | 163 |

|   |      |                                                | 164 |

|   |      |                                                | 166 |

|   |      | 1                                              | 169 |

|   |      |                                                | 172 |

|   | 7.5  |                                                | 176 |

|   | Refe | 6                                              | 180 |

|   |      |                                                |     |

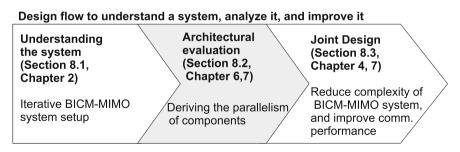

| 8  | Bit-  | Interlea | aved Coded MIMO System                         | 185                                                  |

|----|-------|----------|------------------------------------------------|------------------------------------------------------|

|    | 8.1   | State-   | of-the-Art BICM-MIMO Systems                   | 187                                                  |

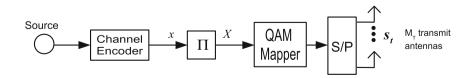

|    |       | 8.1.1    | MIMO Transmitter                               | 187                                                  |

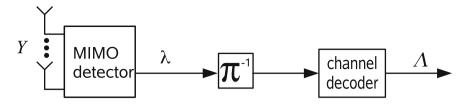

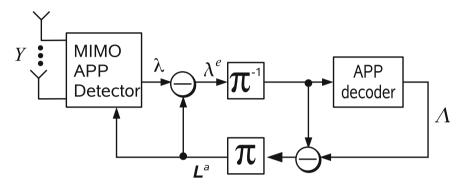

|    |       | 8.1.2    | BICM-MIMO Receiver                             | 188                                                  |

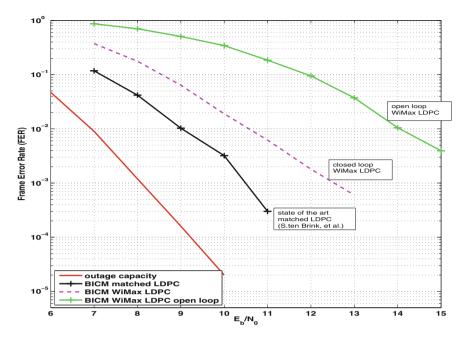

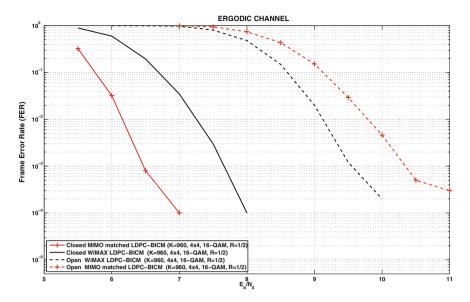

|    |       | 8.1.3    | Communications Performance of State-of-the-Art |                                                      |

|    |       |          | Systems                                        | 194                                                  |

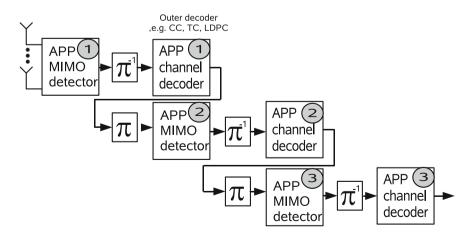

|    | 8.2   | Archit   | ecture Feasibility BICM-MIMO                   | 197                                                  |

|    | 8.3   |          | Architecture-Algorithm Design                  | 201                                                  |

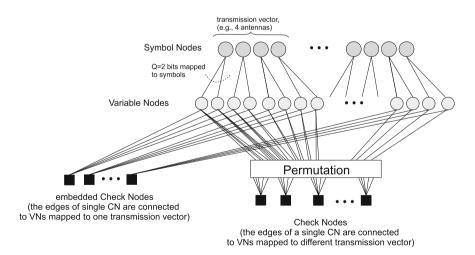

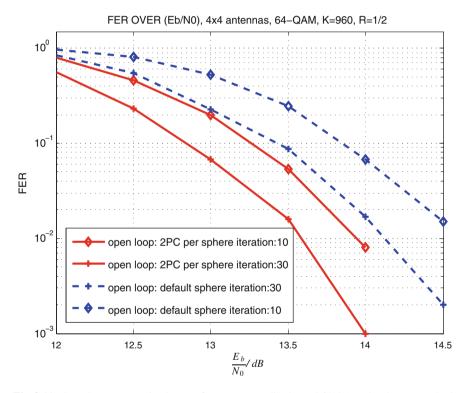

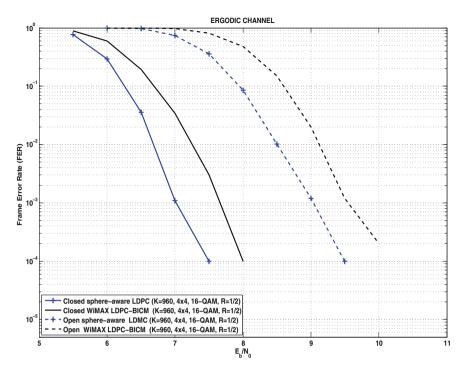

|    |       | 8.3.1    | Sphere Decoder Aware Bit Interleaver Design    | 204                                                  |

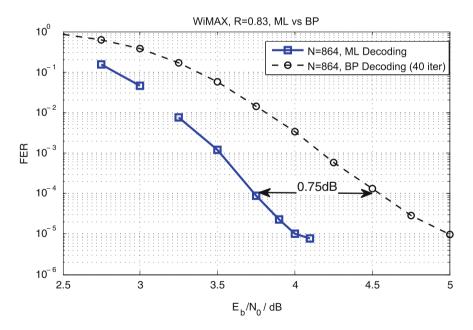

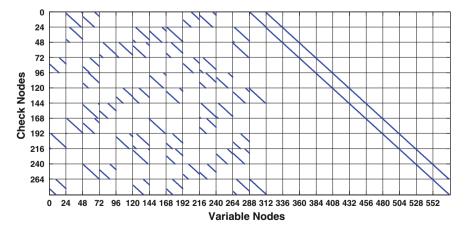

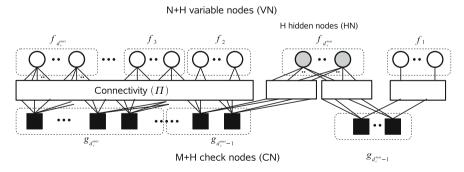

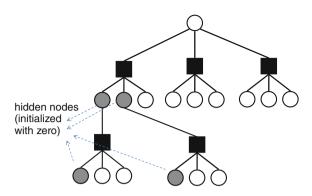

|    |       | 8.3.2    | Sphere Decoder Aware LDPC Code Design          | 207                                                  |

|    | Refe  | erences  | ·····                                          | 209                                                  |

| •  | G     |          |                                                |                                                      |

| 9  |       |          | Architectures                                  |                                                      |

|    | 9.1   |          | ence Designs                                   |                                                      |

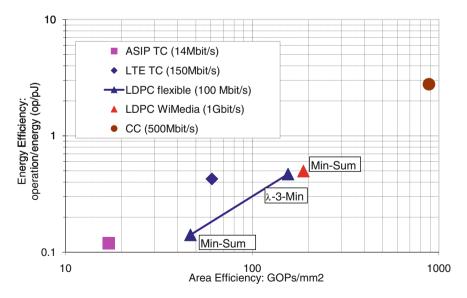

|    | 9.2   |          | le Metrics                                     | 187<br>187<br>188<br>194<br>197<br>201<br>204<br>207 |

|    | 9.3   |          | ach for Design Space Exploration               |                                                      |

|    |       | 9.3.1    | Implementation Driven Design Space Exploration |                                                      |

|    |       | 9.3.2    | Communications Performance Driven Exploration  |                                                      |

|    | 9.4   | 1        | arison of Published Decoder Architectures      |                                                      |

|    |       | 9.4.1    | Technology Parameters                          | 224                                                  |

|    |       | 9.4.2    | Communications Performance                     | 227                                                  |

|    |       | 9.4.3    | VLSI Efficiency and Communications Performance |                                                      |

|    |       |          | at Once                                        | 228                                                  |

|    | Refe  | erences  |                                                | 229                                                  |

| Aŗ | pend  | ix A: C  | Channel Coding Data                            | 233                                                  |

| Ap | pend  | ix B: C  | Communications Performance Results             | 237                                                  |

|    |       |          |                                                |                                                      |

| Aŗ | opend | ix C: P  | Probability Terms                              | 243                                                  |

| Aŗ | pend  | ix D: 4  | -AM Demodulator                                | 249                                                  |

| In | dex . |          |                                                | 257                                                  |

# Acronyms

#### **Mathematical Terms**

| <i>A</i> ,                                                                                | Bold capital letters represent matrices                                |

|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| <i>a</i> <sub><i>i</i></sub> ,                                                            | Bold lowercase letters with index represent column vectors of a matrix |

| <i>x</i> ,                                                                                | Bold lowercase letters represent vectors                               |

| $A_{ij}$                                                                                  | Entry of row <i>i</i> and column <i>j</i> of matrix <i>A</i>           |

|                                                                                           | Element $i$ of vector $\mathbf{x}$                                     |

| $egin{array}{l} x_i & x_i \ oldsymbol{Q}^T & oldsymbol{Q}^H \ oldsymbol{Q}^H \end{array}$ | Transpose of $Q$                                                       |

| $Q^{\scriptscriptstyle H}$                                                                | Hermitian transpose of $Q$                                             |

| $\Re\{x\}$                                                                                | Real part of complex value x                                           |

| $\Im\{x\}$                                                                                | Imaginary part of complex value x                                      |

| LSB                                                                                       | Least significant bit is always located at the most right position     |

# **Basic Transmission System**

| $\mu$                                                       | Mean value                             |

|-------------------------------------------------------------|----------------------------------------|

| $\mu \sigma^2$                                              | Variance                               |

| σ                                                           | Standard deviation                     |

| $N_0$                                                       | One-sided noise power spectral density |

| $E_b$                                                       | Energy per information bit             |

| $E_S$                                                       | Energy per coded symbol                |

| $SNR = E_S / N_0$                                           | Signal-to-noise ratio                  |

| $\sigma^2 = N_0$                                            | Real-valued channel                    |

| $\sigma^2 = \frac{N_0}{2}$                                  | Per complex dimension                  |

| $\frac{E_b}{N_0} = \log_2(Q) \cdot R \cdot \frac{E_s}{N_0}$ | Information bit to noise ratio         |

| С                                                           | Channel capacity                       |

| W                                                           | Bandwidth                              |

| Ν                                                           | Codeword length                        |

| $N_s$                                                       | Number of symbols (modulated codeword) |

| K                                                           | Number of information bits             |

| М                                   | Number of parity bits                                   |

|-------------------------------------|---------------------------------------------------------|

| i,k                                 | Time or step indices                                    |

| u                                   | Information vector                                      |

| $u_k$                               | Information bit at position k                           |

| û                                   | Estimated information bits                              |

| x                                   | Codeword                                                |

| $x_k$                               | Coded bit at position k                                 |

| S                                   | Transmitted symbol vector after mapping (BPSK, QPSK,    |

|                                     | 16-QAM,)                                                |

| s <sub>k</sub>                      | Transmitted symbol at time step $k$                     |

| n                                   | Gaussian noise vector                                   |

| у                                   | Received vector                                         |

| $y_k$                               | Received symbol at position k                           |

| $P(\ldots) \\ P_{\mathbf{x}}^{(x)}$ | Probability of ()                                       |

| $P_{\rm x}^{(x)}$                   | The probability that the random variable X takes on the |

|                                     | value x                                                 |

| $Q \\ 2^Q$                          | Number of bits per modulated symbol                     |

| $2^Q$                               | Modulation alphabet                                     |

| П                                   | Interleaver                                             |

| $\Pi^{-1}$                          | Deinterleaver                                           |

|                                     |                                                         |

# **Channel Coding and Decoding**

| G                              | Generator matrix of a linear block code                             |

|--------------------------------|---------------------------------------------------------------------|

| Н                              | Parity-check matrix of a linear block code                          |

| R                              | Code rate                                                           |

| $K_c$                          | Constraint length of a convolutional codes                          |

| М                              | Number of memories of a convolutional encoder                       |

| $I_i$                          | Input polynomial <i>i</i>                                           |

| $G_{FB}$                       | Feedbackward polynomial                                             |

| $G_i$                          | Feedforward polynomial <i>i</i>                                     |

| $X_K^{S(i)}$                   | <i>i</i> th systematic bit at trellis step $k$                      |

| $x_k^{p(i)}$                   | <i>i</i> th parity bit at trellis step $k$                          |

| $\hat{S_k^{(m)}}$              | Identifier for the $m$ th state in trellis step $k$                 |

| $\gamma_k^{x_i,x_j+1}$         | Branch metric for a bit pattern $x_i$ , $x_{i+1}$ at trellis step k |

|                                | Forward recursion state metric of $S_k^m$                           |

| $lpha_k^m \ eta_k^m \ eta_k^m$ | Backward recursion state metric of $S_k^m$                          |

| $\lambda^s$                    | APPs of the received systematic part                                |

| $\lambda^p$                    | APPs of the received parity part                                    |

| Λ                              | Maximum a posteriori values expressed in LLRs                       |

| $\Lambda_i$                    | Maximum a posteriori value at position <i>i</i>                     |

| $L^e$                          | Extrinsic information (log-likelihood)                              |

| $L_a$                  | A priori information (log-likelihood)                        |

|------------------------|--------------------------------------------------------------|

| $d_{min}$              | Minimum Hamming distance                                     |

| $(d_v, d_c)$           | Column and row weight of H                                   |

| f                      | Degree distribution of variable nodes                        |

| g                      | Degree distribution of check nodes                           |

| VN                     | Variable node                                                |

| CN                     | Check node                                                   |

| $d_v^{max}$            | Maximum VN degree                                            |

| $d_c^{max}$            | Maximum CN degree                                            |

| $d_c^{max}$<br>$d_v^i$ | Degree of VN at position <i>i</i>                            |

| IN                     | Information (variable) node associated to an information bit |

#### Architectures

| t <sub>cond</sub>         | Technology node and operating conditions w.r.t. PVT settings                                                                            |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| PVT                       | Process, voltage, and temperature settings                                                                                              |

| $t_{cyc}$                 | Cycle time                                                                                                                              |

| $f_{cyc}$                 | Cycle frequency of the design                                                                                                           |

| $\dot{Q_{in}}$            | Quantization of the input data                                                                                                          |

| $Q_{ext}$                 | Quantization of the extrinsic data                                                                                                      |

| iter                      | Number of iterations of the channel decoder (half iterations for turbo decoding)                                                        |

| BL                        | Processed block length, may differ to codeword size                                                                                     |

| WL                        | Window length of the trellis processing                                                                                                 |

| AL                        | Acquisition length, the number of training steps for recursions                                                                         |

| rdx                       | Radix-2 or radix-4 realization of the recursion units                                                                                   |

| $C_N$                     | Latency due to network to realize interleaving                                                                                          |

| Р                         | Parallelization of the decoder architecture: for turbo codes paralleliza-<br>tion of the MAP architecture, for LDPC codes the number of |

| ת                         | concurrently processed edges                                                                                                            |

| $P_{IO}$                  | Parallelization of the input/output                                                                                                     |

| E                         | Number of edges in a Tanner-graph                                                                                                       |

| $T_{payl}$                | Payload throughput, architecture throughput of the information bits in [bit/s]                                                          |

| $T_{latency}$             | Architecture dependent latency                                                                                                          |

| $\delta_{overhead}$       | Additional fixed overhead due to architecture constraints (e.g. fill the                                                                |

|                           | pipeline)                                                                                                                               |

| $\frac{\#cycles}{d_{VN}}$ | Number of cycles required to process one block average variable node                                                                    |

| uvn                       | degree in the Tanner graph (LDPC codes)                                                                                                 |

| $\#\frac{bits}{cycle}$    | Normalized throughput: number of information bits decoded per clock cycle                                                               |

# MIMO

| $\begin{array}{ll} M_R & \text{Number of receive antennas} \\ T & \text{Number of channel uses per codeword} \\ H & \text{Channel matrix, } M_R \times M_T \text{ matrix} \\ Y & \text{Received values, } M_R \times T \text{ matrix} \\ S & \text{Modulated symbols, } M_T \times T \text{ matrix} \\ N & \text{Gaussian noise, } M_T \times T \text{ matrix} \\ y_t & \text{Received vector, column } t \text{ of } Y, t \in [1,T] \\ \chi_t(i) & \text{Received symbol } i \text{ of received vector } y_t, i \in [1,M_r] \\ \lambda & \text{LLRs after demodulator} \\ \lambda^e & \text{LLRs after demodulator} \\ \lambda^a & \text{Channel values, input LLRs for channel decoder, } \Pi\{\lambda^e\} \\ A & \text{APP LLRs after channel decoder} \\ L^e & \text{Extrinsic LLRs of channel decoder, } \Lambda - \lambda^a \\ L^a & \text{A priori LLRs of channel decoder, } \Pi\{L^e\} \\ Q & \text{Orthonormal matrix of QR decomposition of } H \\ R & \text{Upper-triangular matrix of QR decomposition of } H \\ \hat{Y} & \text{Result of } Q^H \cdot Y \\ T_i(S^{(i)}) & \text{Partial (squared) Euclidian Distance (PED) in level } i \text{ of the tree} \\  e_i(S^{(i)}) ^2 & \text{Distance increment for PED} \end{array}$ | $M_T$                       | Number of transmit antennas                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------------------------------------------------------|

| HChannel matrix, $M_R \times M_T$ matrixHChannel matrix, $M_R \times M_T$ matrixYReceived values, $M_R \times T$ matrixSModulated symbols, $M_T \times T$ matrixNGaussian noise, $M_T \times T$ matrixy_tReceived vector, column t of Y, t $\in [1,T]$ $y_t(i)$ Received symbol i of received vector $y_t$ , $i \in [1,M_r]$ $\lambda$ LLRs after demodulator $\lambda^e$ LLRs after demodulator without a priori LLRs, $\lambda - L^a$ $\lambda^a$ Channel values, input LLRs for channel decoder, $\Pi\{\lambda^e\}$ $\Lambda$ APP LLRs after channel decoder $L^e$ Extrinsic LLRs of channel decoder, $\Lambda - \lambda^a$ $L^a$ A priori LLRs of demodulator, $\Pi\{L^e\}$ QOrthonormal matrix of QR decomposition of H $R$ Upper-triangular matrix of QR decomposition of H $\hat{Y}$ Result of $Q^H \cdot Y$ $T_i(S^{(i)})$ Partial (squared) Euclidian Distance (PED) in level i of the tree                                                                                                                                                                                                                                                                                                                                           | $M_R$                       | Number of receive antennas                                           |

| YReceived values, $M_R \times T$ matrixSModulated symbols, $M_T \times T$ matrixNGaussian noise, $M_T \times T$ matrix $y_t$ Received vector, column t of Y, t $\in [1,T]$ $y_t$ Received symbol i of received vector $y_t$ , $i \in [1,M_r]$ $\lambda$ LLRs after demodulator $\lambda^e$ LLRs after demodulator without a priori LLRs, $\lambda - L^a$ $\lambda^a$ Channel values, input LLRs for channel decoder, $\Pi\{\lambda^e\}$ $\Lambda$ APP LLRs after channel decoder $L^e$ Extrinsic LLRs of channel decoder, $\Lambda - \lambda^a$ $L^a$ A priori LLRs of demodulator, $\Pi\{L^e\}$ $Q$ Orthonormal matrix of QR decomposition of $H$ $\hat{Y}$ Result of $Q^H \cdot Y$ $T_i(S^{(i)})$ Partial (squared) Euclidian Distance (PED) in level $i$ of the tree                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Т                           | Number of channel uses per codeword                                  |

| SModulated symbols, $M_T \times T$ matrixNGaussian noise, $M_T \times T$ matrix $y_t$ Received vector, column t of Y, t $\in [1,T]$ $y_t(i)$ Received symbol i of received vector $y_t, i \in [1,M_r]$ $\lambda$ LLRs after demodulator $\lambda^e$ LLRs after demodulator without a priori LLRs, $\lambda - L^a$ $\lambda^a$ Channel values, input LLRs for channel decoder, $\Pi\{\lambda^e\}$ $\Lambda$ APP LLRs after channel decoder $L^e$ Extrinsic LLRs of channel decoder, $\Lambda - \lambda^a$ $L^a$ A priori LLRs of demodulator, $\Pi\{L^e\}$ $Q$ Orthonormal matrix of QR decomposition of $H$ $\hat{Y}$ Result of $Q^H \cdot Y$ $T_i(S^{(i)})$ Partial (squared) Euclidian Distance (PED) in level $i$ of the tree                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | H                           | Channel matrix, $M_R \times M_T$ matrix                              |

| NGaussian noise, $M_T \times T$ matrix $y_t$ Received vector, column t of Y, t $\in [1,T]$ $y_t(i)$ Received symbol i of received vector $y_t, i \in [1,M_r]$ $\lambda$ LLRs after demodulator $\lambda^e$ LLRs after demodulator without a priori LLRs, $\lambda - L^a$ $\lambda^a$ Channel values, input LLRs for channel decoder, $\Pi\{\lambda^e\}$ $\Lambda$ APP LLRs after channel decoder $L^e$ Extrinsic LLRs of channel decoder $L^a$ A priori LLRs of demodulator, $\Pi\{L^e\}$ $Q$ Orthonormal matrix of QR decomposition of H $R$ Upper-triangular matrix of QR decomposition of H $\hat{Y}$ Result of $Q^H \cdot Y$ $T_i(S^{(i)})$ Partial (squared) Euclidian Distance (PED) in level i of the tree                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Y                           | Received values, $M_R \times T$ matrix                               |

| $y_t$ Received vector, column t of Y, t $\in [1,T]$ $y_t(i)$ Received symbol i of received vector $y_t$ , $i \in [1,M_r]$ $\lambda$ LLRs after demodulator $\lambda^e$ LLRs after demodulator without a priori LLRs, $\lambda - L^a$ $\lambda^a$ Channel values, input LLRs for channel decoder, $\Pi\{\lambda^e\}$ $\Lambda$ APP LLRs after channel decoder $L^e$ Extrinsic LLRs of channel decoder, $\Lambda - \lambda^a$ $L^a$ A priori LLRs of demodulator, $\Pi\{L^e\}$ $Q$ Orthonormal matrix of QR decomposition of $H$ $R$ Upper-triangular matrix of QR decomposition of $H$ $\hat{Y}$ Result of $Q^H \cdot Y$ $T_i(S^{(i)})$ Partial (squared) Euclidian Distance (PED) in level $i$ of the tree                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | S                           | Modulated symbols, $M_T \times T$ matrix                             |

| $y_t(i)$ Received symbol $i$ of received vector $y_t, i \in [1, M_r]$ $\lambda$ LLRs after demodulator $\lambda^e$ LLRs after demodulator without a priori LLRs, $\lambda - L^a$ $\lambda^a$ Channel values, input LLRs for channel decoder, $\Pi\{\lambda^e\}$ $\Lambda$ APP LLRs after channel decoder $L^e$ Extrinsic LLRs of channel decoder, $\Pi - \lambda^a$ $L^a$ A priori LLRs of demodulator, $\Pi\{L^e\}$ $Q$ Orthonormal matrix of QR decomposition of $H$ $R$ Upper-triangular matrix of QR decomposition of $H$ $\hat{Y}$ Result of $Q^H \cdot Y$ $T_i(S^{(i)})$ Partial (squared) Euclidian Distance (PED) in level $i$ of the tree                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | N                           | Gaussian noise, $M_T \times T$ matrix                                |

| $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $\mathbf{y}_t$              | Received vector, column t of Y, $t \in [1,T]$                        |

| $\lambda^{e} \qquad \text{LLRs after demodulator without a priori LLRs, } \lambda - L^{a}$ $\lambda^{a} \qquad \text{Channel values, input LLRs for channel decoder, } \Pi\{\lambda^{e}\}$ $\Lambda \qquad \text{APP LLRs after channel decoder}$ $L^{e} \qquad \text{Extrinsic LLRs of channel decoder, } \Lambda - \lambda^{a}$ $L^{a} \qquad \text{A priori LLRs of demodulator, } \Pi\{L^{e}\}$ $Q \qquad \text{Orthonormal matrix of QR decomposition of } H$ $R \qquad \text{Upper-triangular matrix of QR decomposition of } H$ $\hat{Y} \qquad \text{Result of } Q^{H} \cdot Y$ $T_{i}(S^{(i)}) \qquad \text{Partial (squared) Euclidian Distance (PED) in level } i \text{ of the tree}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $y_t(i)$                    | Received symbol <i>i</i> of received vector $y_t$ , $i \in [1, M_r]$ |

| $\begin{array}{lll} \lambda^{a} & \text{Channel values, input LLRs for channel decoder, } \Pi\{\lambda^{e}\}\\ \Lambda & \text{APP LLRs after channel decoder}\\ L^{e} & \text{Extrinsic LLRs of channel decoder, } \Lambda - \lambda^{a}\\ L^{a} & \text{A priori LLRs of demodulator, } \Pi\{L^{e}\}\\ Q & \text{Orthonormal matrix of QR decomposition of } H\\ R & \text{Upper-triangular matrix of QR decomposition of } H\\ \hat{Y} & \text{Result of } Q^{H} \cdot Y\\ T_{i}(S^{(i)}) & \text{Partial (squared) Euclidian Distance (PED) in level } i \text{ of the tree} \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                             | LLRs after demodulator                                               |

| $\Lambda$ APP LLRs after channel decoder $L^e$ Extrinsic LLRs of channel decoder $L^a$ A priori LLRs of demodulator, $\Pi\{L^e\}$ $Q$ Orthonormal matrix of QR decomposition of $H$ $R$ Upper-triangular matrix of QR decomposition of $H$ $\hat{Y}$ Result of $Q^H \cdot Y$ $T_i(S^{(i)})$ Partial (squared) Euclidian Distance (PED) in level $i$ of the tree                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\lambda^e$                 | LLRs after demodulator without a priori LLRs, $\lambda - L^a$        |

| $L^e$ Extrinsic LLRs of channel decoder, $\Lambda - \lambda^a$ $L^a$ A priori LLRs of demodulator, $\Pi\{L^e\}$ $Q$ Orthonormal matrix of QR decomposition of $H$ $R$ Upper-triangular matrix of QR decomposition of $H$ $\hat{Y}$ Result of $Q^H \cdot Y$ $T_i(S^{(i)})$ Partial (squared) Euclidian Distance (PED) in level $i$ of the tree                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $\lambda^a$                 | Channel values, input LLRs for channel decoder, $\Pi{\lambda^e}$     |

| $L^a$ A priori LLRs of demodulator, $\Pi\{L^e\}$ $Q$ Orthonormal matrix of QR decomposition of $H$ $R$ Upper-triangular matrix of QR decomposition of $H$ $\hat{Y}$ Result of $Q^H \cdot Y$ $T_i(S^{(i)})$ Partial (squared) Euclidian Distance (PED) in level $i$ of the tree                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Λ                           | APP LLRs after channel decoder                                       |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | $L^{e}$                     | Extrinsic LLRs of channel decoder, $\Lambda - \lambda^a$             |

| $R$ Upper-triangular matrix of QR decomposition of $H$ $\hat{Y}$ Result of $Q^H \cdot Y$ $T_i(S^{(i)})$ Partial (squared) Euclidian Distance (PED) in level $i$ of the tree                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $L^a$                       | A priori LLRs of demodulator, $\Pi\{L^e\}$                           |

| $ \hat{Y} 	ext{ Result of } Q^H \cdot Y \\ T_i(S^{(i)}) 	ext{ Partial (squared) Euclidian Distance (PED) in level i of the tree } $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                             | Orthonormal matrix of QR decomposition of $H$                        |

| $T_i(\mathbf{S}^{(i)})$ Partial (squared) Euclidian Distance (PED) in level <i>i</i> of the tree                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                             | Upper-triangular matrix of QR decomposition of H                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Ŷ                           | Result of $Q^H \cdot Y$                                              |

| $ e_i(\mathbf{S}^{(i)}) ^2$ Distance increment for PED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $T_i(\boldsymbol{S}^{(i)})$ | Partial (squared) Euclidian Distance (PED) in level $i$ of the tree  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                             | Distance increment for PED                                           |

## Chapter 1 Introduction

Practically all modern communication systems, like digital video broadcasting (DVB), wireless local area networks (WLAN), and all mobile cellular standards currently in use, transmit information in digital form. The shift from analog transmission to digital transmission in practical applications and products was fueled by the rapid development of integration densities of digital circuits. Today's so called very-large-scale integration(VLSI) processes allow millions (or even billions) of transistors to be integrated in one single chip. The development of new communication systems and the rapid progress of chip technology lead to ever more complex systems. With every system generation, larger integration densities allow to integrate a widened set of functionalities into these systems, which in turn drives the development of larger integration densities. Transceivers of future cellular standards will have to support virtually all existing wireless standards, shall provide a throughput of up to 1 Gbit/s, and all that within the limited power budget of a mobile phone.

Both domains, chip design and communication systems, show a rapid growth in complexity. Every designer of such a system-on-a-chip (SoC) is required to have a comprehensive, interdisciplinary understanding of both domains, which are typically thought as separate major subjects in university courses. To achieve efficient designs—efficient in terms of constraints posed by the application and in terms of chip design, e.g. area and power consumption—it is of increasing importance that engineers learn to bridge these two distinct engineering domains.

Many good text books exist in the area of hardware design, e.g. [1–4], as well as in the field of digital communication systems, e.g. [5–9]. The list of good references is far from being complete, for both areas. However, it is difficult to find a text book which covers both domains, the algorithm design—even when it does not specialize in communication systems—and the hardware design. This manuscript tries to fill this void and bridge the two domains, using the so called outer receiver of a digital communication system as an exemplary application.

The next sections give an overview of the basic trends in VLSI technology as well as in wireless communications, followed by the introduction of the application example which is used throughout the manuscript. The terms chip or integrated circuit (IC) are general expressions, which just refer to an electronic circuit based on semiconductor materials. One very important semiconductor material is silicon, which is why the IC manufacturers are often called as well the silicon industry. One important property of a semiconductor material is that it is possible to change its conductivity by inserting positively or negatively charged atoms into the material, a process which is called doping.

Every structural element within an integrating circuit is thus composed of a different combination of doped semiconductor materials. Additional materials are utilized as well during chip fabrication, as for example highly conductive materials and isolation materials. Very-large-scale integration (VLSI) is the current integration technique which enables the instantiation of millions of transistors on one chip. The basic idea here is the repeated usage of regular structures to ensure a homogeneous fabrication process.

One of the most important logic families is called complementary metal oxide semiconductor (CMOS) logic. A CMOS structure is typically composed of two 'complementary' metal-oxide-semiconductor field-effect transistors (MOSFET). Fabrication processes for highly integrated CMOS circuits—so called CMOS processes—are thus a good indicator of technological progress.

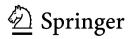

Figure 1.1 shows the development trends of CMOS processes over the years. The y-axis shows the maximum number of transistors that can be integrated in one chip and the minimum gate length in  $\mu$  m for a MOSFET, which can be seen as the minimum geometric object size in an integrated circuit. The future trend for process

Fig. 1.1 Old and current trends in semiconductor integration densities, for future trends see [10]

shrinking is given by the International Technology Road Map for Semiconductors (ITRS) [10], which is a partnership network of semiconductor manufacturers. The ITRS road map comprises the common assumption of the manufactures about the future trends and challenges for the chip technology.

The terms CMOS and MOSFET are not explained in detail here. The important message of Fig. 1.1 is that the current technology progress still follows Moore's law of integrated circuits, which states that the number of transistors that can be placed on a given area doubles approximately every 2 years [11].

Special care has to be taken when evaluating VLSI efficiency characteristics like area and power consumption. For every given technology node, e.g. 40 nm, there are different fabrication processes. A process developer like the Taiwan Semiconductor Manufacturing Company (TSMC) can provide a so called low power process or a high performance process. Note, that more process types are possible. The differences of some important implementation figures of an ARM [12] processor for two different processes are shown exemplary in Table. 1.1. We highlight here three important aspects about power, area, and performance.

- Power consumption: For the power consumption of a chip we have to distinguish between dynamic power consumption and static power consumption. Dynamic power consumption refers to the case when the processor is working. The static power consumption is of importance when the processor is idle. A low power process is often a low leakage process which optimizes the static power consumption. A mobile phone is one typical example of a device which is in idle mode for most of the time. Thus, a low power process is utilized. However, under the same usage conditions (voltage, work load, temperature), the dynamic power consumption of a circuit fabricated in a low power process.

- Area: The area for different process types does not change for these two process variants. Furthermore, it can be seen that 50 % the overall area of this ARM device is in determined by memories. For future devices it is assumed that the area for memories will more and more determine the entire area. Thus, for area comparison it is always important to specify the storage capabilities as done in Table. 1.1.

|                                        | ARM Cortex-A5 Perfo  | rmance, Power, Area        |

|----------------------------------------|----------------------|----------------------------|

|                                        | TSMC 40LP            | TSMC 40G                   |

| Process type/Nominal voltage           | Low leakage, 1.1.V   | Performance, 1.0 V         |

| Frequency (optimized)                  | 530-600 MHz          | ≥1 GHz                     |

| Area excluding RAMs/cache              | $0.27  \text{mm}^2$  | $0.27  \text{mm}^2$        |

| Area with 16 kbyte RAMs/16 kbyte cache | $0.53 \mathrm{mm}^2$ | $0.53\mathrm{mm}^2$        |

| Dynamic power                          | 0.12 mW/MHz          | $\leq 0.08  \text{mW/MHz}$ |

Table 1.1 Difference between a low power process and a high performance process, both at a 40 nm technology node [13]

• Performance: The performance is often measured in operations or instructions per second. This number depends of course on the achieved frequency which largely differs between these two process variants.

Table. 1.1 describes the influence of the process type for one ARM processor which will be embedded in a larger system. The ARM processor is a programmable device and, thus, offers a large flexibility with respect to a given application.

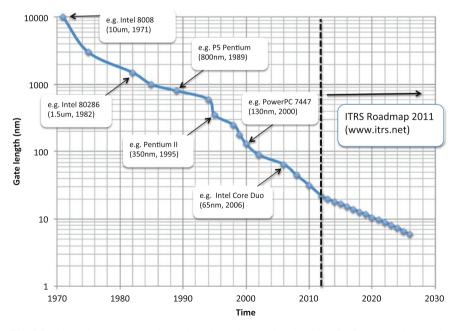

A processor is only one implementation possibility, however, many different implementation styles are possible. With the term 'implementation styles' we refer to the choice of different hardware platforms and thus different possibilities with respect to area efficiency, power efficiency, and flexibility. The implementation style is one major decision which has to be done early during product development.

General purpose processors (GPP) provide the highest flexibility, however, with the highest power consumption compared to other implementation styles. ASICs are up to 5 orders of magnitude more power and area efficient than GPPs. An applicationspecific integrated circuit (ASIC) provides the highest performance and lowest energy consumption. ASICs are designed for one specific task and are optimized with respect to the required performance. An overview figure is presented in Fig. 1.2, with the area efficiency depicted on the x-axis and the energy efficiency on the y-axis, respectively. Here, area efficiency is defined as operations per seconds (given in mega operations

Fig. 1.2 Comparison of peak performance, power efficiency, and flexibility of different implementation styles, derived from [14]

per seconds or Mops) divided by area, while energy efficiency is defined as power consumption divided by number of operations per second.

Many different implementation styles exist between the two extremes, with respect to their power and area efficiency. For example digital signal processors (DSP) or application specific instruction-set processors (ASIP). A DSP is a processor with an instruction set optimized to perform operations for digital signal processing applications. A DSP is typically designed with a wide scope of applications in mind and the same DSP could be for example used efficiently for video processing as well as for processing tasks within a digital communication receiver. The goal of an ASIP design is to provide just enough flexibility to cover the flexibility requirements of a given application domain. It has thus an optimized instruction set to provide maximum performance at a minimum area and energy budget.

All implementation styles presented so far have a special architecture in mind, which is implemented utilizing a VLSI fabrication process. Once fabricated we cannot change the design anymore. One hardware platform which allows a reconfiguration even after fabrication is a field-programmable gate array (FPGA). FPGAs are integrated circuits which can be configured by a designer and, thus, offer huge flexibility. It is possible to map practically every architecture—e.g., an application specific design, the architecture of a general purpose processor, or an ASIP—onto an FPGA. A certain architecture mapped onto FPGAs will always have an inferior area and power efficiency compared to a direct VLSI realization. FPGAs are often utilized for rapid prototyping or smaller product series.

With every new technology process every implementation style moves as well with respect to their power efficiency and as well their peak performance. For example the required processing in a mobile phone to perform a voice call was realized in the year 2000 by dedicated hardware (ASIC). With the rapid progress in technology a phone call today is typically processed by an embedded GPU, e.g. ARM core, within a smart phone. Thus, a hardware designer implementing an identical application may have to deal with different implementation styles when moving to the next technology node.

#### **Trends in Communication Standards**

For communication systems we typically have to distinguish between different transport media over which communication takes place. There is a difference for transmissions via optical, wireline or wireless communication channels. Many more different transport media exist. The one thing uniting them is that for all of these communication media a trend to higher throughput demands can be observed. This trend for higher data throughputs is driven by requests to access data at every place, every time, and very importantly often in real time. In the following we will highlight the trends in mobile communications.

Mobile phone communications are one major technological part of our daily lives. The number of acronyms for telecommunication standards is immense, which can be seen just by looking at the advertisement from mobile communication providers. We have to distinguish between the standardization bodies, the organizing parties, and the resulting technology generations. All of these parts exists with different naming and acronyms within Europe, north America, and Asian regions. In the following we will mainly focus on the European region.

- Standardization bodies: ETSI is responsible for standardizing information and communication technologies (ICT) in Europe. ETSI stands for European Telecommunications Standards Institute and is an independent, non-profit, standardization organization in the telecommunications industry.

- Organizing bodies: The International Telecommunication Union (ITU) is an agency of the United Nations responsible for the ICT domain and coordinates, e.g. standardization activities and as well the harmonization of international frequency-spectrum. The 3rd Generation Partnership Project (3GPP) is an association of companies, ranging from telecommunication providers to chip manufacturers. The task of the 3GPP initiative is to define and evolve the generations of mobile standards.

- Mobile standards generation: Every mobile standard generation stands for an evolution in employed techniques with respect to an efficient frequency usage and an increased throughput. The 2nd generation, for example, was the first digital cellular technology and already defined in 1989. The 3rd generation was released in 1999, the 4th generation in 2008. Each generation is still further evolved with the objective of being compatible to older generations but achieving increased data throughput. The list of acronyms is large and not all will be explained in this text, e.g. 2nd generation evolution (GSM → GPRS → EDGE → EDGE advanced), 3rd generation evolution (UMTS → HSPA → HSPA advanced) 4th generation evolution (LTE → LTE advanced).

One of the most successful, nowadays global, telecommunication standards is GSM (Global System for Mobile Communications), The world wide coverage of GSM is already larger than 70%, i.e. more than 70% of all people world wide have access to this mobile network, see www.gsma.com. GSM belongs to the 2nd generation of mobile communications systems and has a defined throughput of only 2kbit/s. New features and applications led to the demand of higher throughput, thus the third generation of mobile communication standards was developed. The 3rd Generation Partnership Project (3GPP) had the task to evolve the GSM standard to a 3rd generation telecommunication standard. It is worth noting that the 3GPP was just one initiative towards the 3rd generation organized in Europe, which fulfilled requirements defined by the ITU. In Europe the first 3rd generation was denoted UMTS (universal mobile telecommunication standard) and was released in the year 1999. The documents describing these standard are often denoted as Release99. Starting form this basic definition new evolved standards were developed, as for example the High speed packet access (HSPA) with higher throughput requirements, e.g. released in 2005 and 2008. In 2008 a revised mobile communications standard with new features was released, as well as a further branch, which is called long term evolution (LTE) or often as well 3.5th or sometimes directly the 4th generation.

| 1                         |      |      |      |        |       |       |

|---------------------------|------|------|------|--------|-------|-------|

| Year                      | 1995 | 2000 | 2005 | 2010   | 2015  | 2020  |

| Cellular standard         | 2G   | 3G   | 3.5G | pre-4G | 4G    | 5G    |

|                           | GSM  | UMTS | HSPA | LTE    | LTE-A |       |

| Downlink bitrate (Mbit/s) | 0.01 | 0.1  | 1    | 10     | 100   | 1000  |

| Workload (GOPS)           | 0.1  | 1    | 10   | 100    | 1000  | 10000 |

| CMOS (ITRS, nm)           | 350  | 180  | 90   | 50     | 22    | 7.4   |

| Battery energy (Wh)       | 1    | 2    | 3    | 4      | 5     | 6     |

| Phone CPU clock (MHz)     | 20   | 100  | 200  | 500    | 1000  | 2000  |

| Phone CPU power (W)       | 0.05 | 0.05 | 0.1  | 0.2    | 0.3   | 0.5   |

| PC CPU power (W)          | 5    | 20   | 100  | 200    | 200   | 300   |

Table 1.2

Mobile phone trends in 5-year intervals, table adapted from [16]

For mobile communication systems we have to distinguish between the so called uplink and downlink communications. For mobile communication typically base station handles all mobile communications within a specific area. The base station serves as a central hub in which all mobile devices have to be registered. An uplink defines the communication link from a mobile terminal to a base station while the downlink defines the communication from a base station to a mobile terminal.

Table. 1.2 shows the currently assumed mobile communication trends in 5-year intervals. The standard documents for the different releases and thus years of approval can be found at www.3gpp.org. It can be seen that the throughput demands of a new generation is rapidly increasing, with an approximative increase of 10 times within 5 years teme interval. Note that an identical trend can be seen as well for wireline communications, as shown in [15].

The presented table shows the trend for the data rates, it tells us nothing about the new techniques and algorithms which have to be realized to enable this throughput increase.

#### **Design Challenges**

Table 1.2 is adapted form [16] and comprises three important aspects: the trend in CMOS technology, the trend for downlink throughputs, and the trend of the workload caused by the employed algorithms for transmission and reception.

The trend in downlink throughput and CMOS integration was already described. Here, additional information is given, like the clock frequency and the power consumption of the CPUs in a personal computer (PC) and a mobile phone. This is related to the already discussed implementation styles, where one is optimized for high performance, the other for low power applications, respectively.

Especially for mobile phones it is assumed that the total battery energy given in [Wh] will increase only moderately over the years, while the workload demand is increasing rapidly. One reason is the already mentioned increased throughput demand, which is also linked to the number of pixels that can be displayed on modern high resolution screen.

The major bottleneck will be the productivity of a designer. The designer has to map a complex algorithm down to an architectural design. A typical top down design flow, may result in an inefficient VLSI performance as measured by chip area and power consumption. Top down means the separation of algorithm designer and hardware designer in terms of programming or design language. The algorithm designer programs the basic functionality in C, C++, or Matlab. Taking the resulting program, the hardware designer utilizes a design language like VHDL or Verilog, for the architecture design. This clear separation of algorithm and hardware design may lead to inefficient designs and results as well in-productivity in terms of design time.

Two promising approaches to enhance the productivity are summarized: The first possibility is the introduction of so called high-level synthesis, a research domain which has received a lot of attention in recent years. A tool featuring high-level synthesis will improve the productivity, since the design will be described in a high-level language, e.g. C++ or Java. The mapping to an architecture will be done automatically. This will be a big benefit for the designer, since designing an architecture in VHDL is time consuming as well as error prone, due to the fact that the reference system is programmed in another language than the architectural description. It is like writing assembler compared to writing C. However, the inherent parallelism of a hardware design poses big challenges for the high-level design flow and sometimes as well for the designer. A second possibility to close the productivity gap can be already observed during the standardization process of LTE or DVB-S2 standard. In these standards, algorithmic parts were introduced with an efficient implementation strategy in mind. The mapping from algorithmic level down to hardware is then predefined and will, thus, result in efficient designs.

Both methods to improve the productivity require knowledge of the application as well as a basic understanding of hardware design. For the sake of simplicity we focus in this manuscript on individual components within a larger receiver realization. Already for a simple component design a comprehensive understanding of algorithm and architecture becomes mandatory to achieve efficiency in communications performance and VLSI performance. The next section gives an overview of the application which serves as an example throughout the rest of this manuscript.

#### **1.1 Application: Outer Receiver**

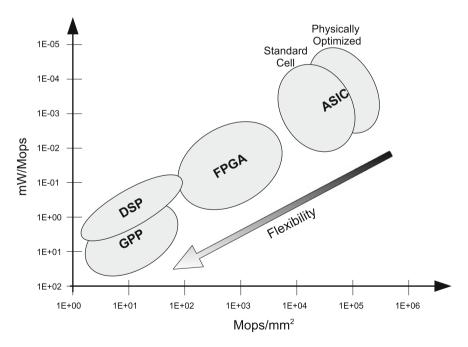

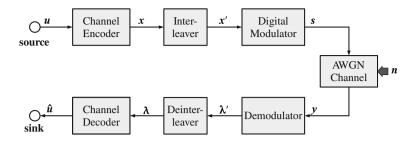

Designing a transceiver or receiver of a digital transmission system requires an abstract model of the transmission chain. The model of the digital transmission chain approximates the real world behavior of sending information from one point to some other physical location, as shown in Fig. 1.3. The transmission of information form one source to one sink is typically denoted as point-to-point communication. The research of the basics of discrete information processing has started mainly with the

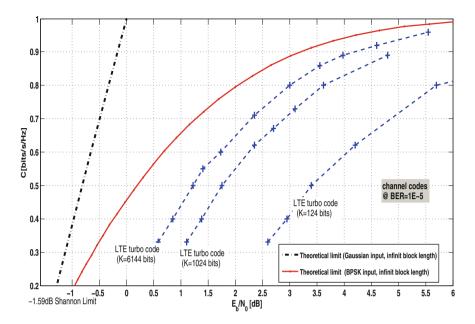

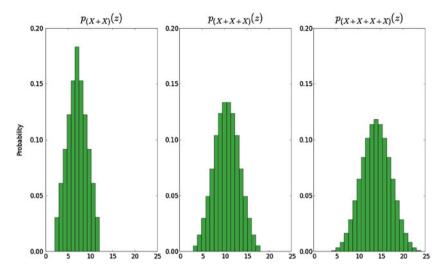

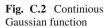

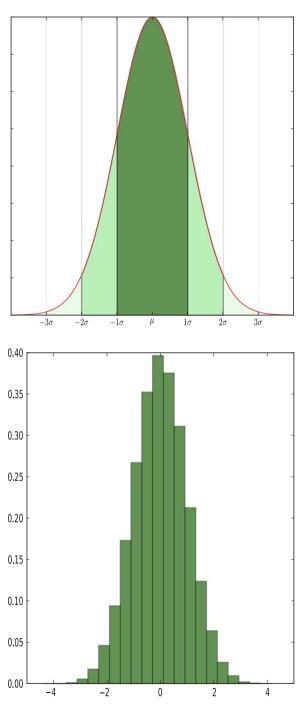

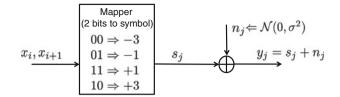

Fig. 1.3 Transmission system, only the outer transceiver part is discussed in the following chapters