# Konstantinos Markantonakis Keith Mayes *Editors*

# Secure Smart Embedded Devices, Platforms and Applications

Secure Smart Embedded Devices, Platforms and Applications

Konstantinos Markantonakis Keith Mayes Editors

# Secure Smart Embedded Devices, Platforms and Applications

Foreword by Fred Piper

*Editors* Konstantinos Markantonakis Keith Mayes Information Security Group Smart Card Centre Royal Holloway University of London Egham, Surrey UK

ISBN 978-1-4614-7914-7 ISBN 978-1-4614-7915-4 (eBook) DOI 10.1007/978-1-4614-7915-4 Springer New York Heidelberg Dordrecht London

Library of Congress Control Number: 2013939824

© Springer Science+Business Media New York 2014

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed. Exempted from this legal reservation are brief excerpts in connection with reviews or scholarly analysis or material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. Duplication of this publication or parts thereof is permitted only under the provisions of the Copyright Law of the Publisher's location, in its current version, and permission for use must always be obtained from Springer. Permissions for use may be obtained through RightsLink at the Copyright Clearance Center. Violations are liable to prosecution under the respective Copyright Law. The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

While the advice and information in this book are believed to be true and accurate at the date of publication, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

I would like to dedicate this book to the memory of my father, Georgios Markantonakis. Thank you dad! Konstantinos Markantonakis

I would like to dedicate this book to my family and friends, and to people who succeed despite disadvantage

Keith Mayes

## Foreword

This is the second book to be co-edited by Keith Mayes and Konstantinos Markantonakis. The first, *Smartcards, Tokens, Security and Applications* was published in 2008 and this volume is a natural 'companion' of that earlier publication and greatly expands on the range of content. Both are the result of experiences gained in managing the Smart Card Centre (SCC) at Royal Holloway, University of London.

The SCC, which was founded 10 years ago by Vodafone and Giesecke & Devrient, and has since been supported by numerous other companies, teaches a specialist module to students studying for the M.Sc. in Information Security. That module, which has the same title as their first book, focuses strongly on the relevant technical, practical and security issues.

Just as with the earlier book, the editors have produced an informative volume that is easy to read and its wide range of topics, which includes RFID, NFC, Mobile communications and wireless sensor nodes, (to list only a few), will appeal to a much wider audience than the Masters students at whom it is primarily aimed. This wider audience is likely to extend to researchers and experts form industry and governments. The two editors are both active researchers and their enthusiasm for research adds extra interest to a fascinating area.

It is clear that technology has advanced enormously over the years, although the fundamentals of Information Security may not have changed very much. Whether we are dealing with pencil and paper or advanced super computers, the motivation for fraud or security attacks and many of the reasons why vulnerabilities exist still have very human origins. Perhaps the biggest change is that people have transformed from being occasional users of technology to being dependent upon it and its underlying security properties. We also have generations that have grown up with the computer, mobile phone and Internet connectivity as essentials for life and they consume services and share personal data with carefree enthusiasm, whereas older heads might worry about how the technology works, who controls the system and data etc. In response to this it is certainly possible to focus on the security of something "big" like the Internet, but is very important to remember that much of what we rely on to keep us and our data and activities secure, is a collection of increasingly complex smaller devices. For example, the mobile phone is really a concept and what we actually buy and use is an electronic assembly with

processors, memories, security modules, displays, batteries, speakers etc. We could almost describe a car in the same way as it only functions correctly because a large number of embedded electronic modules, processors, sensors and communications links work as they should. Therefore if we are to fully understand the threats to modern systems and services, and then to help protect against them, we should keep abreast of developments in embedded systems. A textbook on secure smart embedded devices, platforms and applications would therefore seem a welcome addition to the bookshelf.

Fred Piper Founder, Director of the Information Security Group Royal Holloway, University of London

## Preface

As we progress into the twenty-first century it seems that the pace of technological advance shows no sign of slowing. We are in fact becoming increasingly dependent on technology in our normal day-to-day lives, which means that we are critically reliant on the security of systems and services that are built upon this technology. In exploring this issue within a textbook, one could consider the highlevel design aspects or concentrate more on the nuts and bolts of security systems. This book focuses mainly on the latter approach, as the editors and authors felt there was no introductory overview that covered a sufficient breadth of available technology and related issues. Generally speaking, a complex system is made up of smaller components such as devices, processors, security modules, memories etc. and knowing which of these can be trusted (and to what extent) to resist attacks and misuse, is critical to the security of the complete system. For example, a very sophisticated and expensive car might be reliant on a tiny embedded device (chip) in the engine management system, for it to start and for protection against theft. It is hoped that this book will help to clarify the role of embedded devices, their capabilities, and how best to exploit them in secure system designs.

#### Structure of the Book

The book consists of 24 chapters organised in four sections. Part I introduces some typical embedded devices and hardware, before some more generic information on security issues is provided in Part II. The Part III (which is the largest section) considers a wide range of application aspects and considerations. Part IV is provided for readers who are interested in application development for embedded devices. The chapters are written as self-contained texts, from a range of expert authors and can be read individually or in the book order. The chapters are briefly introduced below.

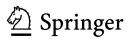

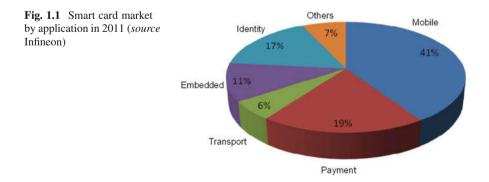

Part I: Chapter 1 provides an overview of smart cards and (RFID), their security capabilities and attack resistance, and their widespread use within a range of security sensitive applications. Chapter 2 then introduces Digital Signal Processor

devices which are widely used in modern devices, such as mobile phones. Chapter 3 relates the historical development of microprocessor and microntroller chips and goes onto cover the specialist design of secure embedded microcontrollers. Chapter 4 introduces a specific type of secure controller, the Trusted Platform Module (TPM) and its mobile equivalent, that are intended to ensure (amongst other things) the safe boot up of a computing platform, so it is a reliable platform on which to load applications. Chapter 5 considers the Very Large Scale Integration (VLSI) approach to the design of electronic hardware and the potential for security attacks and associated countermeasures.

Part II: Chapter 6 provides a general recap on information security best practices. Although we are focussing on embedded devices we must not forget that without a secure theoretical design the implementation security will be fundamentally flawed. Chapter 7 illustrates how a theoretically sound security design can be undermined by a poor implementation that lacks attack resistance. The chosen attack target is the smart card; however the principles are applicable to most embedded security devices. Chapter 8 considers the Graphics Processing Unit (GPU), a processing platform that is often overlooked for its security capabilities. It can be used as a cryptographic processor; however it is also a target for malware and general misuse. Chapter 9 focuses on the FPGA, which has been exploited both to protect and to attack security systems. The discussion also extends to the protection of valuable Intellectual Property loaded into FPGAs used in commercial systems.

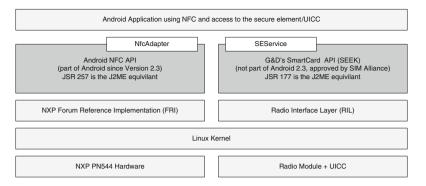

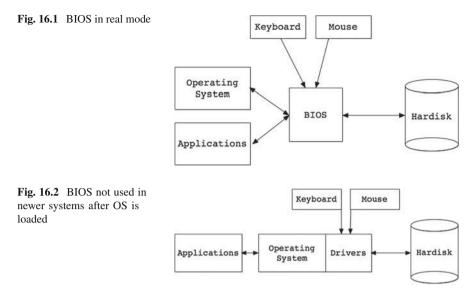

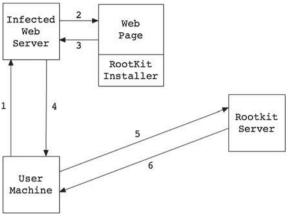

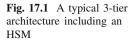

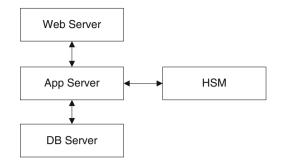

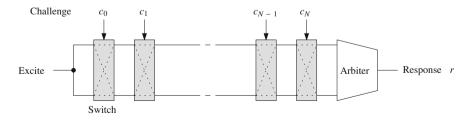

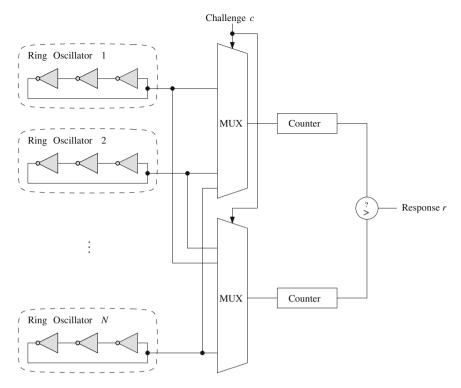

Part III: Chapter 10 considers a range of options for providing mobile communications security controllers. It begins with the conventional Subscriber Identity Module (SIM) and the associated personalisation, management and usage processes, but goes on to consider other possibilities, including software SIMs and TPMs. The action taken by a mobile device depends not just on the security controller, but the validity of the data that it receives, which increasingly can include a representation of physical location. Chapter 11 discusses practical approaches to location estimation, highlighting the possible security vulnerabilities. Car Satellite Navigation systems are just one obvious example of this; however as discussed in Chap. 12 motor vehicles are packed with processing technology that has important safety and security aspects. By contrast, payment card systems tend not to have such emphasis on safety, but they are required to safeguard significant financial transactions. The potential to undermine the payment terminals is discussed in Chap. 13 with reference to published attacks. Another technology where the misuse may have both safety and security implications is the (WSN) which is described in Chap. 14. For example, if a sensor value is modified, replaced or blocked the resulting effect could be serious and/or costly if the system was used for say telemedicine or metering. In fact a number of sensing and terminal solutions are proposed around mobile devices and this seems to be expanding with the arrival of (NFC) Technology. Chapter 15 considers NFC and its security in detail, and how the phone (or laptop, PDA, tablet) may emulate an RFID, or act as an RFID reader, or communicate with other NFC phones over a close proximity link. Although NFC includes a Security Element (SE) some aspects of the functionality are reliant on the phone platform security, which has vulnerabilities similar to conventional PCs. To clarify this problem, Chap. 16 provides a recap on BIOS and Rootkit infections on computing platforms. Specialist computing/server equipment can get around this problem to some extent by the use of security hardened peripheral devices for sensitive processing. These are commonly known as Hardware Security Modules (HSM), and are discussed in Chap. 17. Such devices are normally required to be formally security evaluated and the Common Criteria approach to this is outlined in Chap. 18. In Chap. 19 there is a description of Physically Uncloneable Functions (PUFs) that have generated significant academic interest and then in Chap. 20 there is an overview of SCADA systems security that has generated significant industry concerns.

Part IV: Chapter 21 provides an overview of the PIC family of microcontrollers that are intended for general-purpose non tamper-resistant implementations; however they are often used as clone platforms, as well as for research experiments. More secure implementations are commonly implemented on Java Card platforms and the programming aspects are introduced in Chap. 22. Java has also been a preferred approach for mobile phone platforms and this approach plus important APIs are described in Chap. 23. Finally, for readers interested in experimenting with Wireless Sensor Nodes, some practical guidance on available platforms is presented in Chap. 24.

The ISG Smart Card Centre Royal Holloway, University of London www.scc.rhul.ac.uk; www.isg.rhul.ac.uk Keith Mayes Konstantinos Markantonakis

## ISG Smart Card Centre—Members Message

The (SCC) was established more than 10 years ago at Royal Holloway, University of London. The primary objective was to create a World-Wide Centre of Excellence for training and research in the field of Smart Cards, applications and related technologies. Over the years this has expanded into RFID, NFC, mobile devices and general embedded/implementation system security. Following the success of its first textbook in 2008 (Mayes and Markantonakis (eds), *Smart Cards, Tokens, security and Applications,* Springer) it was felt that this new book was now needed to cover more aspects of Secure Embedded Devices.

The SCC is part of the World renowned Information Security Group (ISG) that is one of the oldest and largest such groups and is one of the UKs Cyber Security Academic Centres of Excellence, with alumni of over 2,000 M.Sc./Ph.D. postgraduates. The SCC in common with ISG principles is very strongly engaged with industry, focussing on responsible research into real world projects of significant impact, and actively engaging industry experts into postgraduate training, research and publication.

As representing the range of supporting industrial members, we are pleased to be associated with the work and publications of the SCC.

Orange Labs (UK) Transport for London UK Cards Association ITSO

# Acknowledgments

This book would not have been possible without the help and support of a number of organisations and individuals. Firstly we would like to thank Orange Labs (UK), Transport for London, The UK Cards Association, ITSO and Royal Holloway, University of London for their tremendous support of the ISG Smart Card Centre. We owe an enormous debt of gratitude to all chapter authors and reviewers for their expert contributions and patient co-operation. We would also like to extend our thanks to Fred Piper for writing the foreword. Last, but certainly not least, we must thank Raja Naem Akram for his tremendous efforts in helping to bring this book to print and to Sheila Cobourne for proof reading on an epic scale.

# Contents

#### Part I Embedded Devices

| 1 | An I  | ntroduc  | tion to Smart Cards and RFIDs                     | 3  |

|---|-------|----------|---------------------------------------------------|----|

|   | Keitł | n Mayes  | and Konstantinos Markantonakis                    |    |

|   | 1.1   | Introdu  | uction                                            | 3  |

|   | 1.2   |          | cation Requirements                               | 5  |

|   |       | 1.2.1    | Mobile Communications                             | 5  |

|   |       | 1.2.2    | Banking Cards                                     | 7  |

|   |       | 1.2.3    | Passports                                         | 8  |

|   |       | 1.2.4    | Satellite Pay-TV                                  | 9  |

|   |       | 1.2.5    | Transport Ticketing                               | 10 |

|   |       | 1.2.6    | Product Tagging.                                  | 11 |

|   |       | 1.2.7    | Comparing Requirements                            | 12 |

|   | 1.3   | Contac   | ct and Contactless Smart Cards/RFIDs              | 13 |

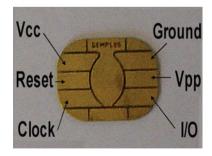

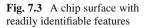

|   |       | 1.3.1    | Cards with Contacts                               | 13 |

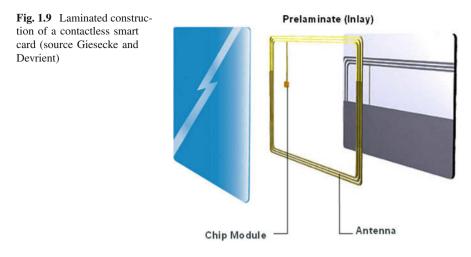

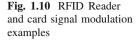

|   |       | 1.3.2    | Contactless Smart Cards/RFIDS                     | 14 |

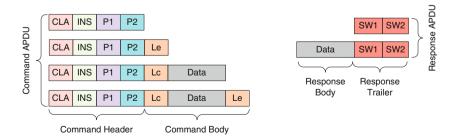

|   |       | 1.3.3    | APDU Communication                                | 15 |

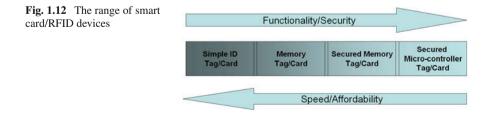

|   | 1.4   | The R    | ange of Smart Card Devices                        | 16 |

|   |       | 1.4.1    | Simple ID Tag/Card                                | 16 |

|   |       | 1.4.2    | Memory Tag/Card                                   | 17 |

|   |       | 1.4.3    | Secured Memory Tag/Card                           | 17 |

|   |       | 1.4.4    | Secured Microcontroller ID/Tag                    | 18 |

|   | 1.5   | The In   | nportance of Providing Attack/Tamper-Resistance   | 19 |

|   | 1.6   | Mobile   | e and NFC                                         | 20 |

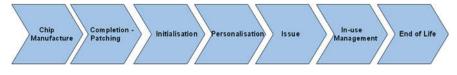

|   | 1.7   | Conve    | ntional Smart Card Lifecycle Management Processes | 21 |

|   | 1.8   | Conclu   | usion                                             | 23 |

|   | Refe  | rences . |                                                   | 24 |

| 2 | Emb   | edded E  | DSP Devices                                       | 27 |

|   | Seren | ndra Red | ldy                                               |    |

|   | 2.1   | Overvi   | iew                                               | 28 |

|   | 2.2   | Digital  | l Signal Processing                               | 29 |

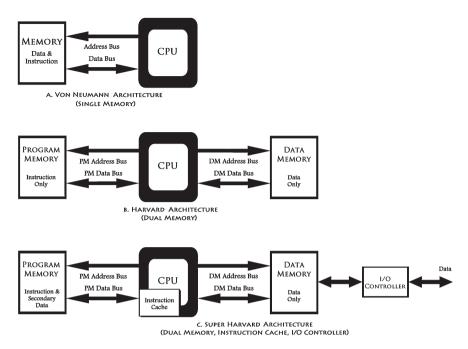

|   |      | 2.2.1 The DSP Processor                                 | 30 |

|---|------|---------------------------------------------------------|----|

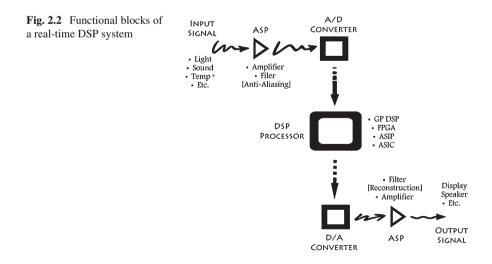

|   |      | 2.2.2 The Real-Time DSP System                          | 32 |

|   |      | 2.2.3 The FPGA in DSP                                   | 34 |

|   |      | 2.2.4 The ASIP in DSP                                   | 35 |

|   | 2.3  | Embedded DSP Systems                                    | 36 |

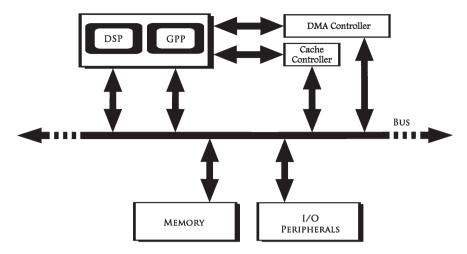

|   |      | 2.3.1 The Embedded DSP Architecture                     | 37 |

|   |      | 2.3.2 The Embedded DSP Processor and RISC               | 40 |

|   |      | 2.3.3 Embedded DSP and Security                         | 42 |

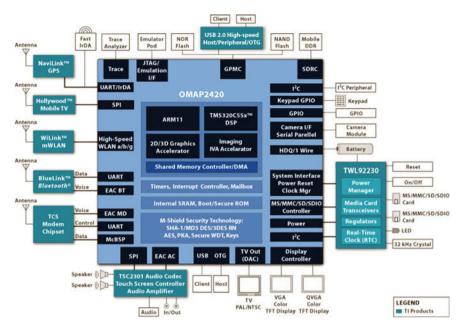

|   |      | 2.3.4 Embedded DSP and the Mobile Phone                 | 44 |

|   | 2.4  | Discussion                                              | 46 |

|   | Refe | rences                                                  | 46 |

| 3 | Mici | roprocessors and Microcontrollers Security              | 49 |

|   |      | s Shire                                                 |    |

|   | 3.1  | Microcontrollers and Microprocessors Security Needs     | 49 |

|   | 3.2  | Historical Development.                                 | 51 |

|   | 3.3  | The Microprocessor                                      | 52 |

|   |      | 3.3.1 32 Bit Microprocessor Designs                     | 53 |

|   |      | 3.3.2 64 Bit Microprocessor Designs                     | 54 |

|   |      | 3.3.3 RISCs and ARM                                     | 54 |

|   | 3.4  | Security Design of Embedded CPU Architectures           | 56 |

|   |      | 3.4.1 Security of Embedded CPU Memory                   | 61 |

|   |      | 3.4.2 Security of Embedded CPU Interfaces               | 64 |

|   | 3.5  | Advanced Chip Design                                    | 65 |

|   | 3.6  | Conclusion.                                             | 67 |

|   | Refe | rences                                                  | 68 |

|   |      |                                                         |    |

| 4 |      | Introduction to the Trusted Platform Module             |    |

|   |      | Mobile Trusted Module                                   | 71 |

|   | Raja | Naeem Akram, Konstantinos Markantonakis and Keith Mayes |    |

|   | 4.1  | Introduction                                            | 71 |

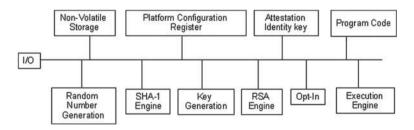

|   | 4.2  | The Trusted Platform Module                             | 72 |

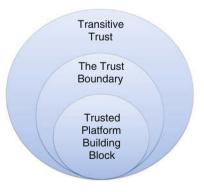

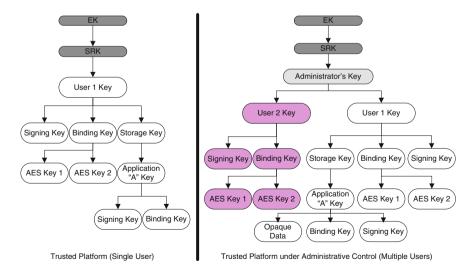

|   |      | 4.2.1 Trusted Platform Framework                        | 72 |

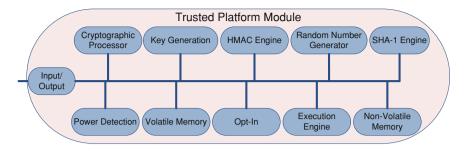

|   |      | 4.2.2 Basic Architecture                                | 73 |

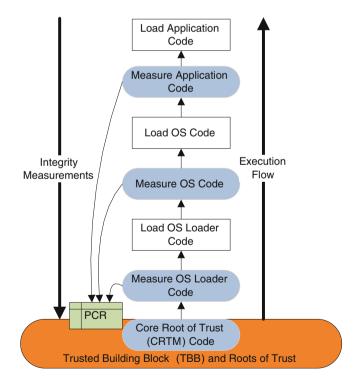

|   | 4.3  | TPM Operations                                          | 76 |

|   |      | 4.3.1 TPM Endorsement Key                               | 76 |

|   |      | 4.3.2 TPM Ownership                                     | 77 |

|   |      | 4.3.3 Attestation Identity Keys                         | 78 |

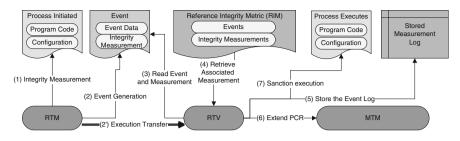

|   |      | 4.3.4 Measurement and Reporting Operations              | 79 |

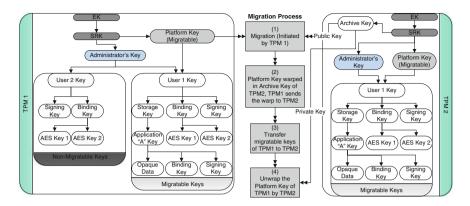

|   |      | 4.3.5 Migration Model                                   | 83 |

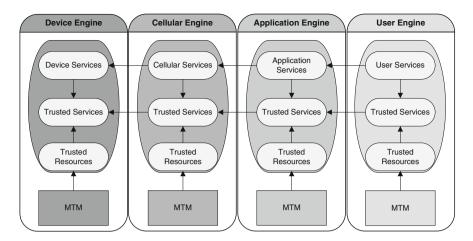

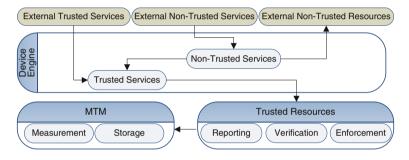

|   | 4.4  | The Mobile Trusted Module                               | 85 |

|   |      | 4.4.1 Basic Architecture and Operations                 | 85 |

|   | 4.5  | TPM/MTM Technology Contenders                           | 88 |

|   |      | 4.5.1 ARM TrustZone                                     | 88 |

#### Contents

|   |      | 4.5.2 M-Shield                                         | 88  |

|---|------|--------------------------------------------------------|-----|

|   |      | 4.5.3 GlobalPlatform Device                            | 88  |

|   |      | 4.5.4 Trusted Personal Devices                         | 89  |

|   |      | 4.5.5 Secure Element                                   | 89  |

|   |      | 4.5.6 Comparative Analysis of TPM/MTM Technology       |     |

|   |      | Contenders                                             | 89  |

|   |      | 4.5.7 What Lies Ahead?                                 | 91  |

|   | 4.6  | Conclusion                                             | 91  |

|   | Refe | ences                                                  | 92  |

| _ |      |                                                        |     |

| 5 |      | ware and VLSI Designs                                  | 95  |

|   |      | Kirschbaum and Thomas Plos                             |     |

|   | 5.1  | Introduction and Motivation                            |     |

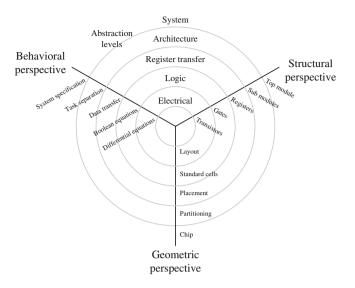

|   | 5.2  | VLSI Design Cycle.                                     | 97  |

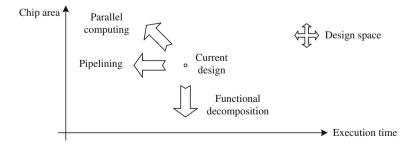

|   | 5.3  | Design Space of Hardware Circuits                      | 100 |

|   | 5.4  | Secure Hardware Design                                 | 102 |

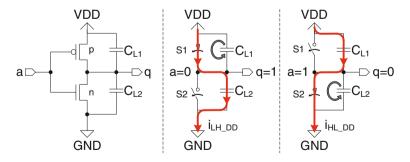

|   |      | 5.4.1 Power Consumption of CMOS Gates                  | 103 |

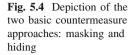

|   |      | 5.4.2 Countermeasures Against Power-Analysis Attacks . | 104 |

|   |      | 5.4.3 Verification of Countermeasures by Means         |     |

|   |      | of Simulations                                         | 107 |

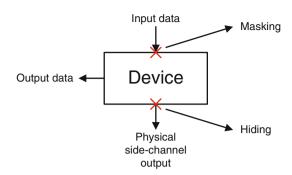

|   | 5.5  | Instruction-Set Extensions                             | 108 |

|   | 5.6  | A 32-Bit Processor with ISEs and SCA Countermeasures   | 110 |

|   | 5.7  | Testability and Security.                              | 112 |

|   | 5.8  | Hardware Trojans                                       | 113 |

|   | 5.9  | Conclusion and Summary                                 | 114 |

|   | Refe | ences                                                  | 115 |

|   |      |                                                        |     |

#### Part II Generic Security and Processing Platforms

| 6 | Info  | rmation | Security Best Practices          | 119 |

|---|-------|---------|----------------------------------|-----|

|   | Keitl | h Mayes | and Konstantinos Markantonakis   |     |

|   | 6.1   | Introdu | action                           | 119 |

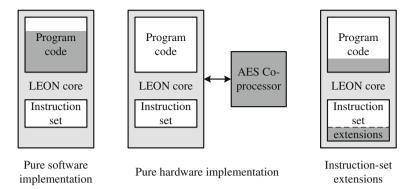

|   |       | 6.1.1   | What is Information Security     |     |

|   |       |         | and Who are the Adversaries?     | 120 |

|   | 6.2   | Securit | ty Objectives                    | 121 |

|   |       | 6.2.1   | Data Assets                      | 122 |

|   |       | 6.2.2   | Critical Functions               | 122 |

|   |       | 6.2.3   | The Range of Security Protection | 122 |

|   | 6.3   | Crypto  | graphic Algorithms               | 123 |

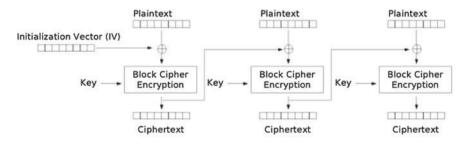

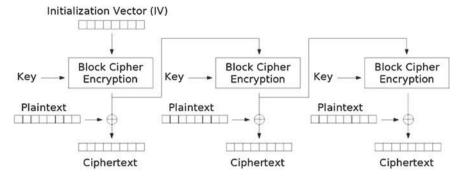

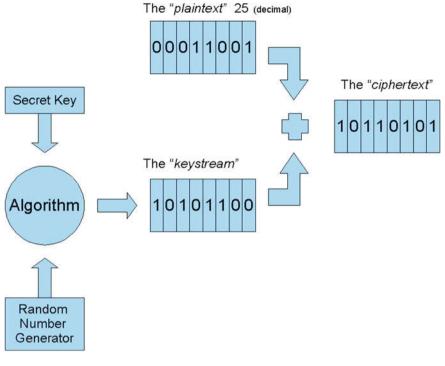

|   |       | 6.3.1   | Symmetric Algorithms             | 124 |

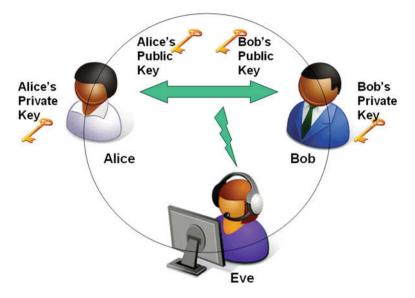

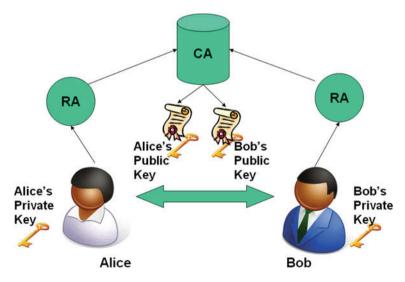

|   |       | 6.3.2   | Asymmetric Algorithms            | 132 |

|   |       | 6.3.3   | Other Algorithms/Modes           | 134 |

|   |       |         |                                  |     |

|   | 6.4  | Key/Trust M    | anagement                            | 135 |

|---|------|----------------|--------------------------------------|-----|

|   |      | 6.4.1 Asyı     | mmetric Key Management               | 136 |

|   |      | 6.4.2 Trus     | t and Management                     | 137 |

|   | 6.5  | Security Eva   | luation and Common Criteria          | 138 |

|   | 6.6  | Handling Im    | perfection                           | 139 |

|   | 6.7  | Case Study t   | he MIFARE Classic                    | 140 |

|   |      | •              | act                                  | 141 |

|   | 6.8  |                | Remarks                              | 142 |

|   | Refe |                |                                      | 143 |

| 7 | Sma  | rt Card Secur  | ity                                  | 145 |

|   | Mich | ael Tunstall   |                                      |     |

|   | 7.1  | Introduction   |                                      | 145 |

|   | 7.2  | Cryptographi   | c Algorithms                         | 147 |

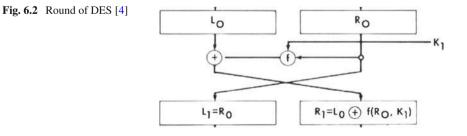

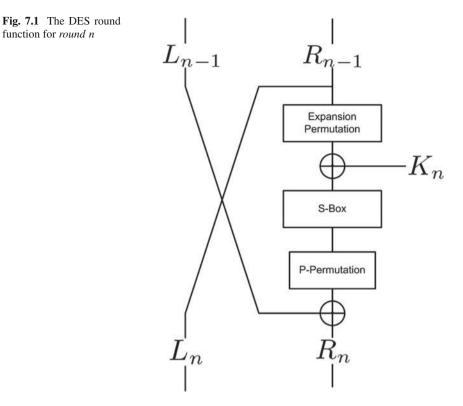

|   |      | 7.2.1 Data     | Encryption Standard                  | 147 |

|   |      |                | ••                                   | 149 |

|   | 7.3  |                | Security Features                    | 152 |

|   |      |                | munication                           | 153 |

|   |      |                | otographic Coprocessors              | 154 |

|   |      | • •            | dom Number Generators                | 154 |

|   |      |                | maly Sensors                         | 155 |

|   |      | 7.3.5 Chip     | Features                             | 155 |

|   | 7.4  |                | l Analysis                           | 157 |

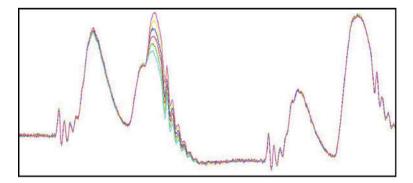

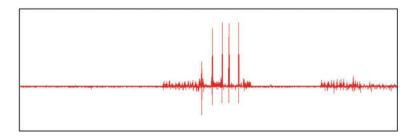

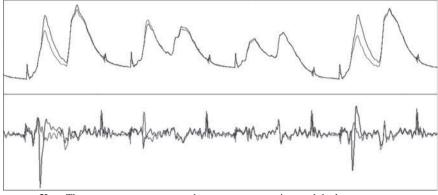

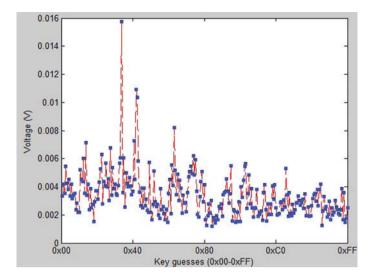

|   |      |                | ing Analysis                         | 157 |

|   |      |                | er Analysis                          | 158 |

|   |      |                | tromagnetic Analysis                 | 163 |

|   |      | 7.4.4 Cou      | ntermeasures                         | 164 |

|   | 7.5  | Fault Analys   | is                                   | 166 |

|   |      | •              | t Injection Mechanisms               | 166 |

|   |      |                | lelling the Effect of a Fault        | 167 |

|   |      |                | ts in Cryptographic Algorithms       | 168 |

|   |      |                | ntermeasures                         | 171 |

|   | 7.6  |                | oftware Design                       | 172 |

|   |      |                | Verification                         | 172 |

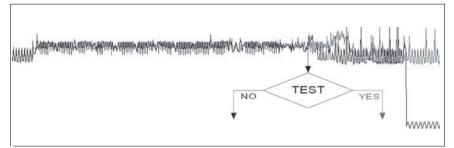

|   |      | 7.6.2 File     | Access                               | 174 |

|   | 7.7  |                | n                                    | 175 |

|   | Refe |                |                                      | 175 |

| 8 | Gra  | hics Processii | ng Units                             | 179 |

|   |      | Schwabe        | -                                    |     |

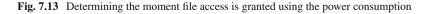

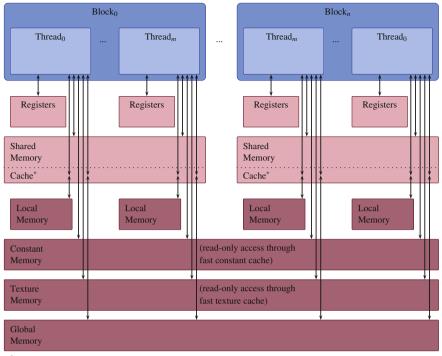

|   | 8.1  | An Introduct   | ion to Modern GPUs                   | 180 |

|   |      | 8.1.1 NVI      | DIA GPUs                             | 180 |

|   |      | 8.1.2 AM       | D GPUs                               | 183 |

|   |      | 8.1.3 Prog     | ramming GPUs in High-Level Languages | 183 |

|   |      | c              |                                      |     |

|      |       | 8.1.4 Programming GPUs in Assembly                   | 185 |

|------|-------|------------------------------------------------------|-----|

|      |       | 8.1.5 GPU Performance Bottlenecks                    | 185 |

|      | 8.2   | GPUs as Cryptographic Coprocessors                   | 187 |

|      |       | 8.2.1 AES on GPUs                                    | 188 |

|      |       | 8.2.2 Asymmetric Cryptography on GPUs                | 190 |

|      | 8.3   | GPUs in Cryptanalysis                                | 192 |

|      | 8.4   | Malware Detection on GPUs                            | 194 |

|      | 8.5   | Malware Targeting GPUs                               | 195 |

|      | 8.6   | Accessing GPUs from Web Applications.                | 196 |

|      | Refer | ences                                                | 197 |

| 9    | A Su  | rvey of Recent Results in FPGA Security              |     |

|      | and I | ntellectual Property Protection                      | 201 |

|      | Franç | ois Durvaux, Stéphanie Kerckhof, Francesco Regazzoni |     |

|      | and F | François-Xavier Standaert                            |     |

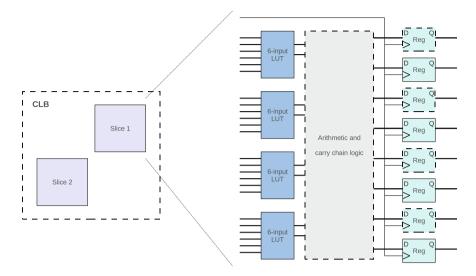

|      | 9.1   | FPGAs: An Overview                                   | 202 |

|      |       | 9.1.1 Structure                                      | 202 |

|      |       | 9.1.2 Design Flow                                    | 204 |

|      |       | 9.1.3 Technologies                                   | 205 |

|      | 9.2   | Security IPs                                         | 205 |

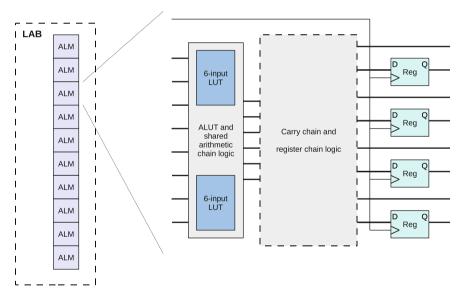

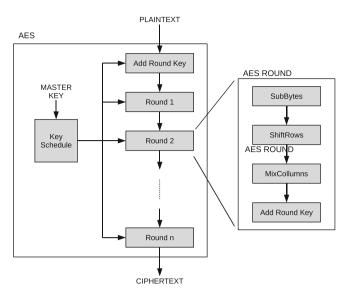

|      |       | 9.2.1 The AES Case                                   | 206 |

|      |       | 9.2.2 Performance Evaluation                         | 209 |

|      |       | 9.2.3 Side-Channel Attacks and Countermeasures       | 210 |

|      |       | 9.2.4 Fault Attacks and Countermeasures              | 212 |

|      | 9.3   | IP Security.                                         | 213 |

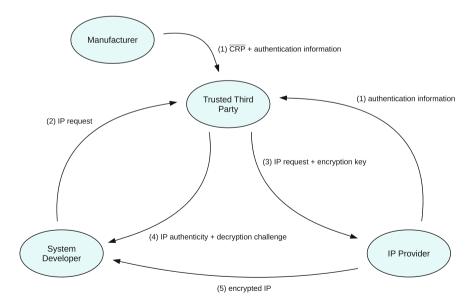

|      |       | 9.3.1 Bitstream Security                             | 213 |

|      |       | 9.3.2 Design Security                                | 214 |

|      | 9.4   | Conclusions                                          | 219 |

|      | Refer | ences                                                | 220 |

|      |       |                                                      |     |

| Part |       | Applications and Platform Embedded Security          |     |

|      |       | Requirements                                         |     |

| 10   |       | le Communication Security Controllers                | 227 |

|      |       | Mayes and Konstantinos Markantonakis                 | 227 |

|      | 10.1  | Introduction                                         | 227 |

|      | 10.2  | An Overview of the SIM.                              | 229 |

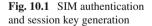

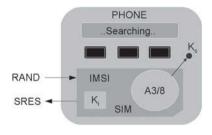

|      | 4.0   | 10.2.1 The SIM in Operation                          | 230 |

|      | 10.3  | Security Analysis                                    | 232 |

|      |       | 10.3.1 Categories of Cellular Usage                  | 232 |

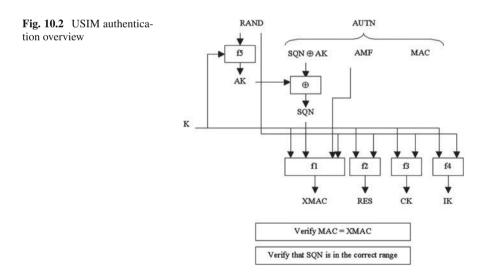

|      |       | 10.3.2 The Roles in Communication Solutions          | 233 |

|      | 10.4  | Security Fundamentals                                | 236 |

|      |       | 10.4.1 Trust Operations                              | 237 |

|    |       | 10.4.2   | Initialisation, Personalisation                |     |

|----|-------|----------|------------------------------------------------|-----|

|    |       |          | and Key Management                             | 238 |

|    |       | 10.4.3   | Authentication/Encryption                      | 238 |

|    |       | 10.4.4   | Management of SIM Data and Application         | 239 |

|    |       | 10.4.5   | Migration                                      | 239 |

|    |       | 10.4.6   | Extended Operations/Value-Added Service        |     |

|    |       |          | Management                                     | 240 |

|    |       | 10.4.7   | NFC Management                                 | 240 |

|    | 10.5  | Generic  | c Attacks on Smart Cards                       | 241 |

|    |       | 10.5.1   | Logical Attacks                                | 241 |

|    |       | 10.5.2   | Physical Attacks                               | 242 |

|    |       | 10.5.3   | Side Channel Attacks                           | 244 |

|    |       | 10.5.4   | Fault Attacks                                  | 246 |

|    |       | 10.5.5   | Summary and Main Points.                       | 246 |

|    | 10.6  | SIM Im   | plementation Options                           | 247 |

|    |       | 10.6.1   | Pure Software SIM                              | 247 |

|    |       | 10.6.2   | Hardware Shared Security Software SIM Solution |     |

|    |       |          | (HS-SSIM)                                      | 249 |

|    |       | 10.6.3   | Standalone HW Security SIM Solution            | 251 |

|    | 10.7  | Trusted  | Platform                                       | 254 |

|    |       | 10.7.1   | Roots of Trust                                 | 255 |

|    |       | 10.7.2   | Authenticated Boot and Secure Storage          | 256 |

|    |       | 10.7.3   | Ownership                                      | 256 |

|    |       | 10.7.4   | Mobile Trusted Platform (MTP)                  | 257 |

|    | 10.8  | Summa    | ry                                             | 260 |

|    |       | 10.8.1   | Value Added Service Management                 | 263 |

|    |       | 10.8.2   | Concluding Remarks                             | 264 |

|    | Refer | ences    |                                                | 265 |

|    |       |          |                                                |     |

| 11 |       |          | mbedded Location Systems                       | 267 |

|    | G. P. | Hancke   |                                                |     |

|    | 11.1  |          | ction                                          | 267 |

|    | 11.2  |          | ded Location Systems                           | 268 |

|    | 11.3  | Security | y and Resilience of Location Information       | 270 |

|    |       | 11.3.1   | Security and Resilience of Position            |     |

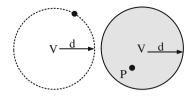

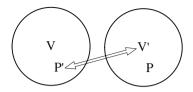

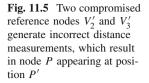

|    |       |          | Estimation Methods                             | 273 |

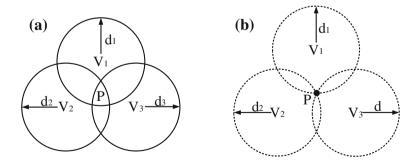

|    | 11.4  |          | g Position Estimation Methods                  | 277 |

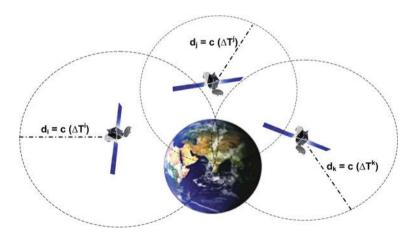

|    | 11.5  | Global   | Navigation Satellite Systems                   | 280 |

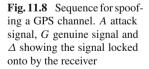

|    |       | 11.5.1   | GPS Security                                   | 280 |

|    |       | 11.5.2   | Future Efforts on Securing GNSS                | 283 |

|    | 11.6  |          | sion                                           | 284 |

|    | Refer | ences    |                                                | 284 |

| 12 | Auto  | motive <b>H</b> | Embedded Systems Applications and Platform     |     |

|----|-------|-----------------|------------------------------------------------|-----|

|    |       |                 | ecurity Requirements.                          | 287 |

|    | Jan P | elzl, Ma        | rko Wolf and Thomas Wollinger                  |     |

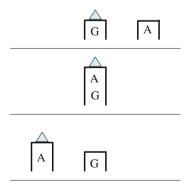

|    | 12.1  | Introdu         | ction: Smart Embedded Platform Automotive      | 287 |

|    |       | 12.1.1          | Smart Communication Platform                   | 289 |

|    |       | 12.1.2          | Smart After-Market Platform                    | 290 |

|    |       | 12.1.3          | Smart Future Platform                          | 290 |

|    | 12.2  | Securit         | y Aspects of Smart Embedded Automotive         |     |

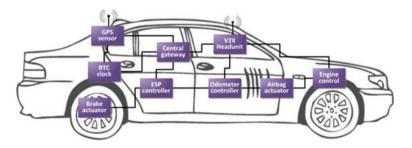

|    |       | Platfor         | ms                                             | 291 |

|    |       | 12.2.1          | Automotive Attackers                           | 292 |

|    |       | 12.2.2          | Automotive Attack Paths                        | 292 |

|    |       | 12.2.3          | Automotive Security Threats and Risks          | 296 |

|    |       | 12.2.4          | Security of Automotive Safety Mechanisms       | 296 |

|    |       | 12.2.5          | Security of Automotive Legal Applications      | 298 |

|    |       | 12.2.6          | Security of Automotive Business Models         | 298 |

|    |       | 12.2.7          | Automotive Privacy Aspects                     | 299 |

|    |       | 12.2.8          | Real-World Automotive Security Incidents       | 299 |

|    |       | 12.2.9          | Examples of Automotive Security Mechanisms     | 300 |

|    | 12.3  | Smart a         | and Secure Open Automotive Platforms Platform  | 302 |

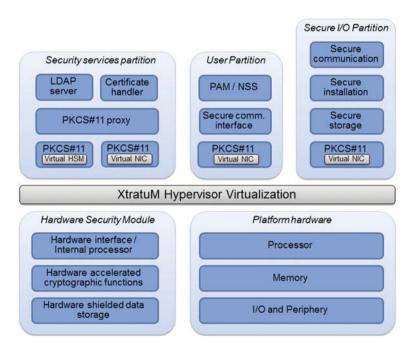

|    |       | 12.3.1          | OVERSEE Virtualisation                         | 302 |

|    |       | 12.3.2          | OVERSEE Security Services Architecture         | 304 |

|    |       | 12.3.3          | OVERSEE Security Implementation                | 306 |

|    | 12.4  | Conclu          | sions                                          | 308 |

|    | Refer | ences .         |                                                | 308 |

|    |       |                 |                                                |     |

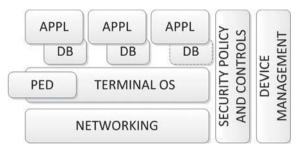

| 13 |       |                 | Potential Vulnerabilities in Payment Terminals | 311 |

|    | Kons  |                 | Rantos and Konstantinos Markantonakis          |     |

|    | 13.1  | Introdu         | ction                                          | 311 |

|    |       | 13.1.1          | EMV Standard                                   | 314 |

|    | 13.2  | Current         | t Terminal Status                              | 316 |

|    |       | 13.2.1          | Types of Terminals                             | 316 |

|    |       | 13.2.2          | Where does Security Apply?                     | 317 |

|    | 13.3  |                 | of Attacks                                     | 320 |

|    |       | 13.3.1          | Attacking the Supply Chain                     | 320 |

|    |       | 13.3.2          | Exploiting Inadequate Security Measures        | 322 |

|    |       | 13.3.3          | Skimming                                       | 324 |

|    |       | 13.3.4          | Covert Channels to PINs                        | 325 |

|    |       | 13.3.5          | PIN/PIN Block Interception and Cracking        | 326 |

|    |       | 13.3.6          | Manipulating the Terminal-Card Interface       | 327 |

|    |       | 13.3.7          | Relay Attacks                                  | 330 |

|    | 13.4  | Conclu          | sions and Future Considerations                | 331 |

|    | Refer | ences .         |                                                | 332 |

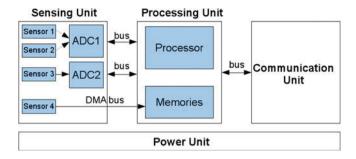

| 14 | Wire  | eless Sensor Nodes                                  | 335 |

|----|-------|-----------------------------------------------------|-----|

|    | Serge | e Chaumette and Damien Sauveron                     |     |

|    | 14.1  | Introduction                                        | 335 |

|    | 14.2  | Applications.                                       | 336 |

|    | 14.3  | Constraints                                         | 337 |

|    |       |                                                     | 337 |

|    |       |                                                     | 338 |

|    |       | e.                                                  | 339 |

|    | 14.4  |                                                     | 339 |

|    |       |                                                     | 340 |

|    |       |                                                     | 341 |

|    |       | 6                                                   | 342 |

|    |       |                                                     | 342 |

|    | 14.5  | 5 1 0 5                                             | 343 |

|    | 14.5  |                                                     | 343 |

|    |       | •                                                   | 345 |

|    | Dafar | •                                                   | 347 |

|    | Kelei |                                                     | 547 |

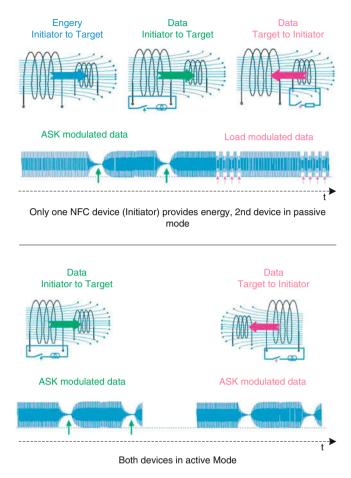

| 15 | Noon  | Field Communication                                 | 351 |

| 15 |       |                                                     | 551 |

|    | 15.1  | ld Madlmayr, Christian Kantner and Thomas Grechenig | 351 |

|    |       |                                                     |     |

|    | 15.2  | 6.                                                  | 352 |

|    |       | 5 5                                                 | 352 |

|    | 15.0  | 11                                                  | 354 |

|    | 15.3  | 8                                                   | 355 |

|    |       | 1                                                   | 355 |

|    |       |                                                     | 356 |

|    |       |                                                     | 357 |

|    | 15.4  |                                                     | 359 |

|    | 15.5  | e                                                   | 359 |

|    |       | 1                                                   | 360 |

|    |       | 1                                                   | 361 |

|    |       |                                                     | 362 |

|    |       |                                                     | 362 |

|    | 15.6  | e                                                   | 364 |

|    |       | 0 11                                                | 364 |

|    |       | 15.6.2 NFC Data Exchange Format (NDEF)              | 364 |

|    | 15.7  | Conclusion                                          | 366 |

|    | Refer | rences                                              | 366 |

|    |       |                                                     |     |

| 16 |       |                                                     | 369 |

|    |       | am Hili, Keith Mayes and Konstantinos Markantonakis |     |

|    | 16.1  |                                                     | 369 |

|    |       | 16.1.1 The BIOS Subsystem Functionality             | 370 |

|    | 16.2   | Attacks on the BIOS Subsystem                         | 371        |

|----|--------|-------------------------------------------------------|------------|

|    |        | 16.2.1 Countermeasures to BIOS Attacks                | 373        |

|    | 16.3   | Rootkits                                              | 373        |

|    |        | 16.3.1 Introduction to Rootkits                       | 373        |

|    | 16.4   | Rootkit Infections                                    | 374        |

|    |        | 16.4.1 Detection of Rootkits                          | 376        |

|    |        | 16.4.2 Removal of Rootkits                            | 378        |

|    | 16.5   | Conclusion                                            | 379        |

|    | Refer  | ences                                                 | 379        |

| 17 | Hard   | ware Security Modules                                 | 383        |

|    | Stathi | is Mavrovouniotis and Mick Ganley                     |            |

|    | 17.1   | Introduction                                          | 383        |

|    | 17.2   | HSM Usage                                             | 384        |

|    | 17.3   | HSM Physical Security                                 | 388        |

|    | 17.4   | HSM Security Evaluation and Approvals.                | 389        |

|    | 17.5   | HSM Management                                        | 393        |

|    | 17.6   | Key Management                                        | 395        |

|    | 17.7   | Command Manipulation Attacks.                         | 399        |

|    | 17.8   | Conclusions                                           | 403        |

|    | Refer  | ences                                                 | 404        |

| 18 |        | rity Evaluation and Common Criteria                   | 407        |

|    | •      | Boswell                                               |            |

|    | 18.1   | Introduction                                          | 407        |

|    | 18.2   | Security Evaluation Issues                            | 408        |

|    |        | 18.2.1 The Security Evaluation Model                  | 412        |

|    |        | 18.2.2 Structure and Use of the Common Criteria       | 413        |

|    |        | 18.2.3 Structure of Common Criteria                   | 415        |

|    |        | 18.2.4 Assurance Requirements and Assurance Levels    | 416        |

|    |        | 18.2.5 CC Interpretation and Supporting Documents     | 416        |

|    | 10.2   | 18.2.6 Attack Potential Calculations                  | 417        |

|    | 18.3   | Evolution of Common Criteria.                         | 418        |

|    |        | 18.3.1 CC Technical Communities                       | 419        |

|    | 10.4   | 18.3.2 New Generation Protection Profiles             | 420        |

|    | 18.4   | Other Security Evaluation Schemes                     | 420        |

|    |        | 18.4.1 FIPS 140                                       | 421        |

|    | 105    | 18.4.2 PCI PIN Transaction Security Requirements      | 422<br>423 |

|    | 18.5   | Example Protection Profiles                           |            |

|    |        | 18.5.1 Security IC PP                                 | 423        |

|    |        | 18.5.2 Payment Terminal (Point of Interaction) PP set | 424        |

|    |        | 1052 Trucked Dietforme Madul DD                       |            |

|    | Def    | 18.5.3 Trusted Platform Module PP                     | 425<br>426 |

| 19 | Phys            | ical Security Primitives                                | 429 |  |  |

|----|-----------------|---------------------------------------------------------|-----|--|--|

|    | Ahma            | ad-Reza Sadeghi, Steffen Schulz and Christian Wachsmann |     |  |  |

|    | 19.1            | Introduction                                            | 429 |  |  |

|    | 19.2            | Physically Unclonable Functions                         | 431 |  |  |

|    |                 | 19.2.1 PUF Concept and Properties                       | 431 |  |  |

|    |                 | 19.2.2 PUF Types                                        | 432 |  |  |

|    |                 | 19.2.3 Noise Compensation and Privacy Amplification     | 435 |  |  |

|    |                 | 19.2.4 Characterizing the Unpredictability of PUFs      | 436 |  |  |

|    | 19.3            | Attacks Against PUFs and PUF-Based Systems              | 437 |  |  |

|    |                 | 19.3.1 Emulation Attacks                                | 437 |  |  |

|    |                 | 19.3.2 Side-Channel Attacks                             | 437 |  |  |

|    |                 | 19.3.3 Fault Injection Attacks                          | 438 |  |  |

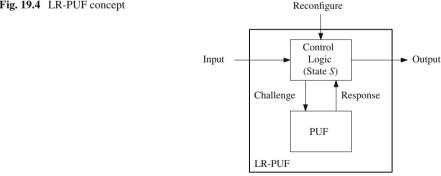

|    | 19.4            | Advanced PUF Concepts                                   | 438 |  |  |

|    |                 | 19.4.1 Controlled PUFs                                  | 439 |  |  |

|    |                 | 19.4.2 Emulatable PUFs                                  | 439 |  |  |

|    | 19.5            | Common Applications of PUFs                             | 440 |  |  |

|    |                 | 19.5.1 Device Identification and Authentication         | 440 |  |  |

|    |                 | 19.5.2 Secure Key Storage and Key Generation            | 441 |  |  |

|    | 19.6            | Future Directions                                       | 441 |  |  |

|    |                 | 19.6.1 Logically Reconfigurable PUFs                    | 441 |  |  |

|    |                 | 19.6.2 PUF-Based Remote Attestation                     | 442 |  |  |

|    | 19.7            | Open Questions and Challenges                           | 443 |  |  |

|    | 19.8            | Conclusion                                              | 444 |  |  |

|    | Refer           | rences                                                  | 445 |  |  |

|    |                 |                                                         |     |  |  |

| 20 |                 | DA System Cyber Security                                | 451 |  |  |

|    | Igor Nai Fovino |                                                         |     |  |  |

|    | 20.1            | Introduction                                            | 451 |  |  |

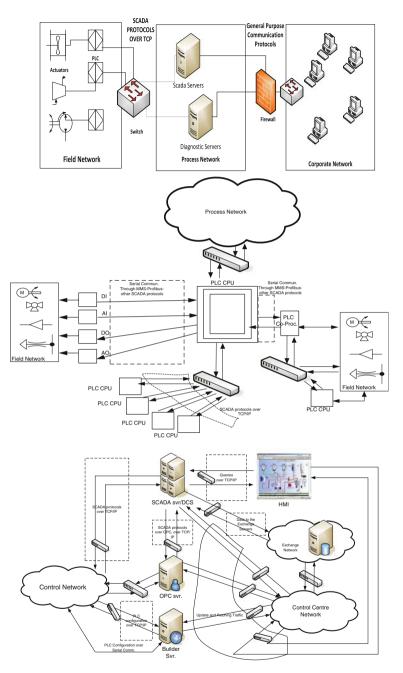

|    | 20.2            | SCADA Architecture Overview                             | 452 |  |  |

|    |                 | 20.2.1 SCADA Protocols Overview                         | 453 |  |  |

|    | 20.3            | SCADA Vulnerabilities and Attacks                       | 455 |  |  |

|    |                 | 20.3.1 Architectural Vulnerabilities                    | 456 |  |  |

|    |                 | 20.3.2 Security Policy Vulnerabilities                  | 457 |  |  |

|    |                 | 20.3.3 Software Vulnerabilities                         | 459 |  |  |

|    |                 | 20.3.4 Communication Protocol Vulnerabilities           | 459 |  |  |

|    | 20.4            | SCADA Security Countermeasures                          | 460 |  |  |

|    |                 | 20.4.1 Communication Protocol Countermeasures           | 461 |  |  |

|    |                 | 20.4.2 Filtering Coutermeasures                         | 462 |  |  |

|    |                 | 20.4.3 Monitoring Coutermeasures                        | 464 |  |  |

|    |                 | 20.4.4 General Architectural Best Practices             | 465 |  |  |

|    | 20.5            | Conclusion.                                             | 469 |  |  |

|    | Refer           | rences                                                  | 469 |  |  |

#### Part IV Practical Examples and Tools

| 21 |       | verview of PIC Microcontrollers and Their Suitability |     |

|----|-------|-------------------------------------------------------|-----|

|    |       | -, F8F8                                               | 175 |

|    |       | ri G. Msgna and Colin D. Walter                       |     |

|    | 21.1  | Introduction                                          | 175 |

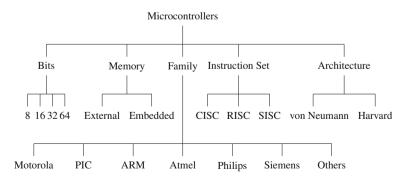

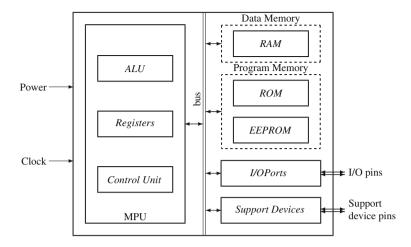

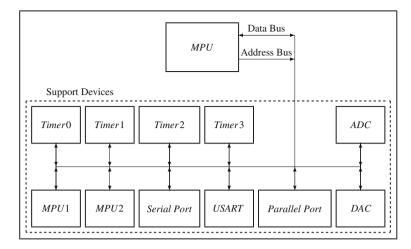

|    | 21.2  | Microcontroller Structure                             | 176 |

|    | 21.3  | Peripheral Interface Controllers 4                    | 177 |

|    |       | 21.3.1 PIC Architecture                               | 177 |

|    |       | 21.3.2 Memory 4                                       | 178 |

|    |       | 21.3.3 Other Components 4                             | 179 |

|    |       |                                                       | 179 |

|    |       |                                                       | 180 |

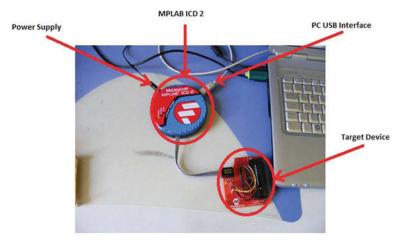

|    | 21.4  |                                                       | 180 |

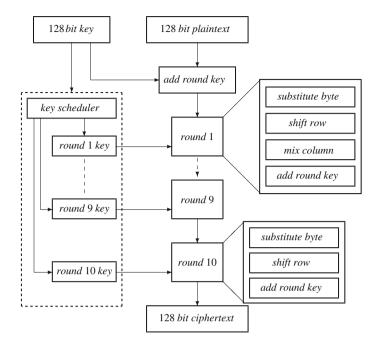

|    |       | 21.4.1 Implementation of AES                          | 181 |

|    | 21.5  |                                                       | 182 |

|    |       | 1                                                     | 183 |

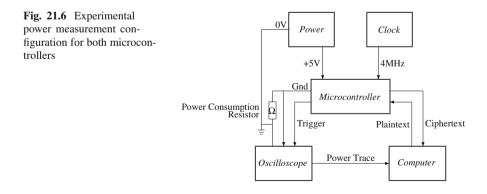

|    |       |                                                       | 185 |

|    | 21.6  | 1                                                     | 193 |

|    | Refer |                                                       | 193 |

|    |       |                                                       |     |

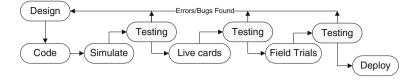

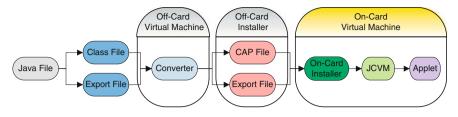

| 22 | An I  | ntroduction to Java Card Programming                  | 197 |

|    |       | Naeem Akram, Konstantinos Markantonakis               |     |

|    |       | Keith Mayes                                           |     |

|    | 22.1  | Introduction                                          | 197 |

|    | 22.2  |                                                       | 198 |

|    |       |                                                       | 198 |

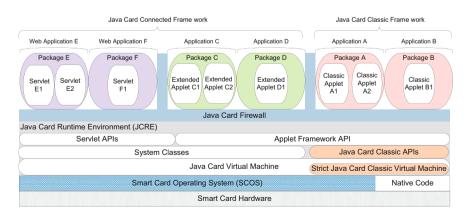

|    |       | 22.2.2 Smart Card Hardware                            | 199 |

|    |       | 22.2.3 Communication Architecture                     | 500 |

|    |       |                                                       | 502 |

|    | 22.3  |                                                       | 503 |

|    |       |                                                       | 503 |

|    |       |                                                       | 504 |

|    | 22.4  |                                                       | 506 |

|    |       |                                                       | 506 |

|    | 22.5  | 11                                                    | 507 |

|    |       | <b>y</b> 11                                           | 507 |

|    |       |                                                       | 509 |

|    |       | 6                                                     | 511 |

|    | 22.6  |                                                       | 512 |

|    |       |                                                       | 512 |

|    |       |                                                       | -   |

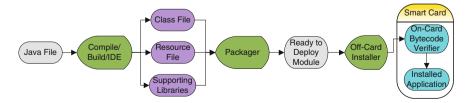

| 23 | A Practical Example of Mobile Phone Application      |         |                                                |     |  |

|----|------------------------------------------------------|---------|------------------------------------------------|-----|--|

|    | Using SATSA (JSR 177) API Lishoy Francis             |         |                                                |     |  |

|    |                                                      |         |                                                |     |  |

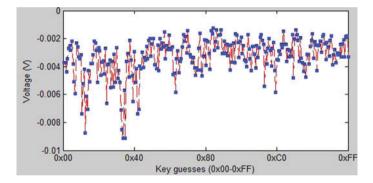

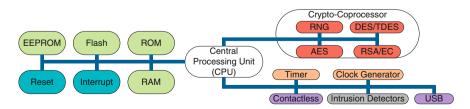

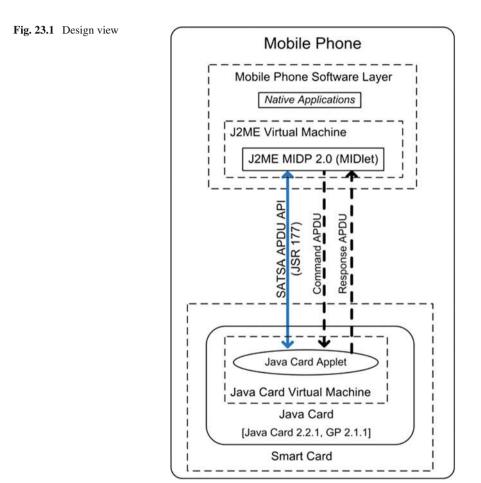

|    |                                                      | 23.1.1  | A Brief Overview of SATSA Framework            | 517 |  |

|    |                                                      | 23.1.2  | A Brief Overview of Java Card Framework        | 518 |  |

|    | 23.2                                                 | Practic | al Example                                     | 518 |  |

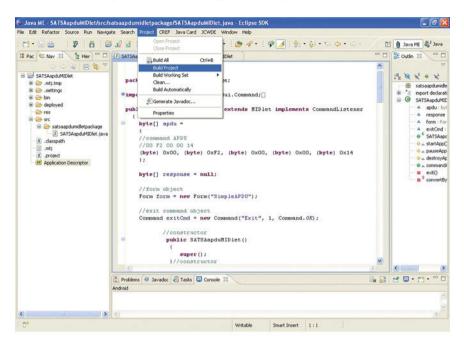

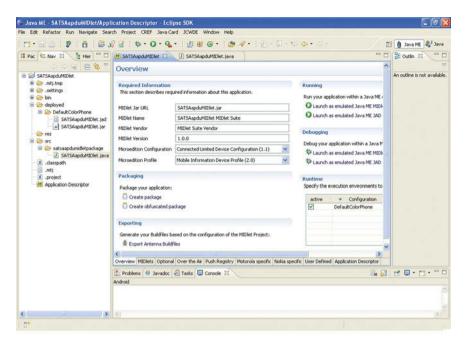

|    |                                                      | 23.2.1  | Developing a MIDP Application (MIDlet)         |     |  |

|    |                                                      |         | Implementing SATSA APDU Communication API      | 518 |  |

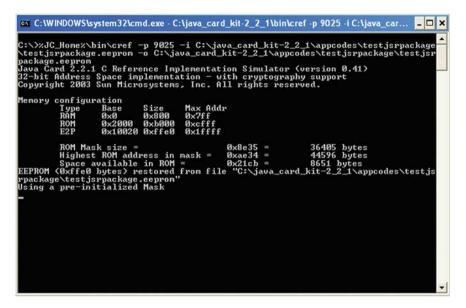

|    |                                                      | 23.2.2  | Developing a Java Card Applet                  | 525 |  |

|    |                                                      | 23.2.3  | Results: Testing MIDlet and Java Card Applet   | 531 |  |

|    | 23.3                                                 | Conclu  | sion                                           | 532 |  |

|    |                                                      | 23.3.1  | Source Code of MIDP Application (MIDlet)       | 533 |  |

|    |                                                      | 23.3.2  | Source Code of Java Card Applet.               | 535 |  |

|    |                                                      | 23.3.3  | Java Card Applet Download-Script               | 537 |  |

|    | Refer                                                | ences.  | ·····                                          | 539 |  |

|    |                                                      |         |                                                |     |  |

| 24 | Wireless Sensors (Languages/Programming/Developments |         |                                                |     |  |

|    | Tools/Examples)                                      |         |                                                |     |  |

|    |                                                      |         | rt, Lionel Barrère, Serge Chaumette            |     |  |

|    | and Damien Sauveron                                  |         |                                                |     |  |

|    | 24.1                                                 |         | ction                                          | 541 |  |

|    | 24.2                                                 |         | OTs (Sun Small Programmable Object Technology) | 542 |  |

|    |                                                      | 24.2.1  | Introduction                                   | 542 |  |

|    |                                                      | 24.2.2  | History                                        | 543 |  |

|    |                                                      | 24.2.3  | Hardware Overview                              | 543 |  |

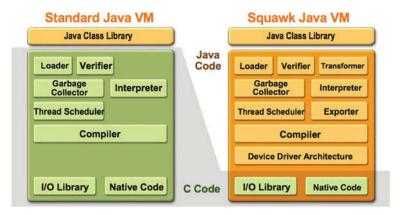

|    |                                                      | 24.2.4  | Software Overview                              | 544 |  |

|    |                                                      | 24.2.5  | How to Start with a Sun SPOT                   | 544 |  |

|    |                                                      | 24.2.6  | Hello World ("Shake and Blink")                | 546 |  |

|    |                                                      | 24.2.7  | Networked Sun SPOTs Applications               | 548 |  |

|    | 24.3                                                 |         | 0                                              | 550 |  |

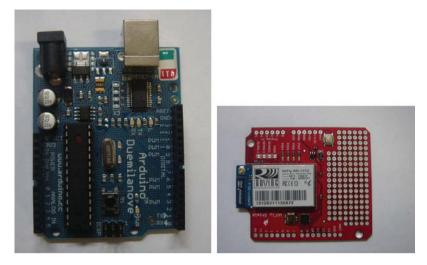

|    |                                                      | 24.3.1  | Introduction and History                       | 550 |  |

|    |                                                      | 24.3.2  | Hardware Overview                              | 550 |  |

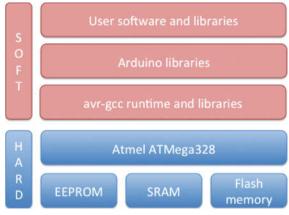

|    |                                                      | 24.3.3  | Software Overview                              | 551 |  |

|    |                                                      | 24.3.4  | How to Start with a Arduino                    | 552 |  |

|    |                                                      | 24.3.5  | Hello World ("Blinking SOS")                   | 553 |  |

|    |                                                      | 24.3.6  | Networked Arduino Application                  | 555 |  |

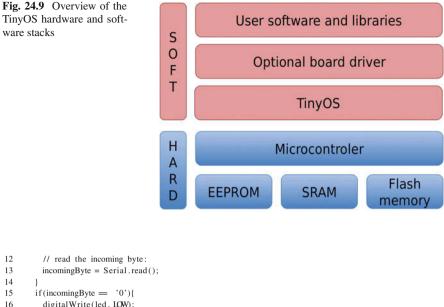

|    | 24.4                                                 | •       |                                                | 556 |  |

|    |                                                      | 24.4.1  | Introduction                                   | 556 |  |

|    |                                                      | 24.4.2  | Hardware Overview                              | 557 |  |

|    |                                                      | 24.4.3  | How to Start with TinyOS                       | 558 |  |

|    |                                                      | 24.4.4  | Hello World ("Sense and Blink")                | 559 |  |

|    |                                                      | 24.4.5  | Networking with TinyOS                         | 560 |  |

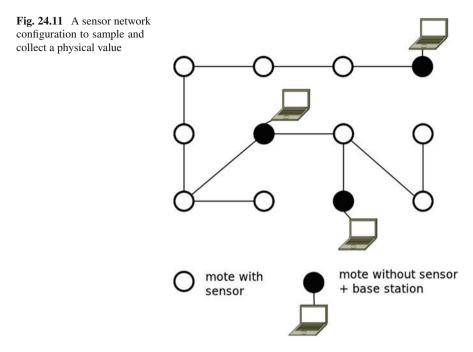

|    | 24.5                                                 | Sensor  | Network Deployment: An Example                 | 561 |  |

#### Contents

| 24.5.1                                                                  | Introduction                                      | 561 |  |  |  |

|-------------------------------------------------------------------------|---------------------------------------------------|-----|--|--|--|

| 24.5.2                                                                  | Hardware Architecture                             | 561 |  |  |  |

| 24.5.3                                                                  | The Time Synchronization Issue.                   | 562 |  |  |  |

| 24.5.4                                                                  | Data Collection, Location and Network Load Issues | 563 |  |  |  |

| 24.5.5                                                                  | The Problem of Missing Information                | 563 |  |  |  |

| 24.5.6                                                                  | Conclusion.                                       | 564 |  |  |  |

| References                                                              |                                                   | 564 |  |  |  |

| Errata to: Secure Smart Embedded Devices,<br>Platforms and Applications |                                                   |     |  |  |  |

| Errata to: Secure Smart Embedded Devices,<br>Platforms and Applications |                                                   |     |  |  |  |

| Index                                                                   |                                                   | 565 |  |  |  |

# Contributors

**Raja Naeem Akram** received B.Sc. from University of Punjab, Pakistan in 2002. After graduating, he studied for M.Sc. Computer Science from University of Agriculture, Pakistan. In 2004, after completing the Master's course in Distinction he worked as IT/Computer Science teacher at Government M.C. High School, Samanabad. He completed his M.Sc. Information Security from Royal Holloway, University of London (RHUL) with Distinction in 2007. In 2012 he completed his Ph.D. under the supervision of Dr. Konstantinos Markantonakis. Worked as Senior Research Fellow on the RatTrap project, designing fraud detection techniques in on-line affiliate marketing at Edinburgh Napier University. Currently, working as a Research Fellow at the Cyber Security Lab, Department of Computer Science, University of Waikato, New Zealand. His research mainly focuses on user centric security and privacy models in different computing environments.

**Dr. Jérémie Albert** received his M.Sc. in Computer Science from the University of Bordeaux in 2007 (with honors). Next, he pursued a Ph.D. in Computer Science in this same University under the supervision of Prof. Serge Chaumette. During his Ph.D. he designed a process calculus suitable for the modeling of Highly Mobile Ad Hoc Networks. After his graduation (with highest honors) in 2010, he was an Assistant Professor at the Polytechnic Institute of Bordeaux. Since 2011, he is a Senior Solutions Architectat Ezakus, Bruges, France. His current research interests are related to distributed computing, large datasets processing, semantic computing, machine learning and game theory.

**Dr. Lionel Barrére** is the Director of Research and Development team at H5 Audits. He previously graduated from the University of Bordeaux, France, and then received his Ph.D. in2009 under the supervision of S. Chaumette for his work on services over military MANets (Mobile Ad hoc Networks), work that was funded by the DGA (French Army). At the end of 2008, he joined the H5 Audits company to create its R&D Department. His research areasare oriented towards the development of passive network monitoring tools such as network probes.

**Tony Boswell** began working in IT security as a security evaluator in one of the original UK government Evaluation Facilities in 1987. Since then he has worked on a wide range of secure system developments and evaluations (including the

ITSEC E6 certifications of the Mondex purse and the MULTOS smart card operating system) in the government and commercial domains. Much of Tonys recent work has been on integrated circuit security projects and on server and applicationlevel virtualisation. Tony has been involved in UK and international interpretation of evaluation requirements for smart cards and payment terminals since 1995, and continues to contribute to multi-national technical community work on interpretation and maintenance of Common Criteria evaluation requirements, as well as assisting hardware and software developers to take their products through Common Criteria evaluations. He is currently a Principal Consultant and CLEF Technical Manager at SiVenture (www.siventure.com).

Serge Chaumette is a Professor in Computer Science at the University Bordeaux 1, Leader of the Mobility, Ubiquity, and Security research group at Laboratoire Bordelais de Recherche en Informatique. He has been using the Java technology for distributed programming since its early beginning. Being concerned by security issues he participated in the design of tools to help in the process of evaluating Java Cards (and applications) within government funded industrial projects. He then naturally moved to the domain of mobile systems and networks and he is collaborating with the French Army in the area of MANets; his group is designing peer to peer applications to support battlefield/emergency situation management (fleets of mobile terminals, robots, or drones). He is an expert by the European Union for Framework Program 7 (FP7) and non FP programs, expert by the ANR (French National Research Agency), and expert by the AERES (French Research and Higher Education Evaluation Agency). He is a member of IEEE, of IEEE Portable Information Devices (PID) group, of Situation Management SubCommittee of the Communications and Operations Technical Committee of the IEEE Communication Society, of IFIP groups 8.8 Smart Cards and 11.2 Pervasive Systems Security.

**François Durvaux** is a Ph.D. Student at Universit Catholique de Louvain. He received the Electro-mechanical Engineering Science degree from UCL in 2010 with his master thesis under the supervision of Pr. Jean-Didier Legat. He joined the Pr. Legat's team in October2010 to work as a researcher in the field of digital nanoelectronics. In January 2011 he started a Ph.D. thesis in cryptography under the supervision of Pr. Franois-Xavier Standaert at UCL. His researches are currently focused on cryptographic hardware design, side-channel analysis, and intellectual property protection.

**Dr. Igor Nai Fovino** Igor is the Head of the Research Division of the Global Cyber Security Center. Igor has deep knowledge in the fields of ICT Security of Industrial Critical Infrastructure, Energy and Smart Grids, Risk Assessment, IDS, Cryptography. He is author of more than 60 scientific papers published on international journals, books and conference proceedings; moreover, he serves as reviewer for several international journals in the ICT security field. In May 2010 he received the IEEE HSI 2010 best paper award in the area of SCADA Systems. He is also an expert in European Policies (mainly in CIIP field). From 2012 he is

member of the European Commission Experts Working Group on the security of ICS and Smart Grids. During his career Igor worked as Contractual Researcher at the University of Milano in the field of privacy preserving datamining and computer security and as Contractual Professor of Operating Systems at the University of Insubria. From 2005 to 2011 he served as Scientific Officer at the Joint Research Centre of the European Commission, providing scientific support to the EU Policies related to the EPCIIP program. Since 2007 he is member of the IFIP Working Group on Critical Infrastructure Protection.

Lishoy Francis is a Security Researcher with background in Computer Science and Engineering, and has specialised in Information Security. In 2002, he graduated with a B.E. in Computer Science and Engineering from Visvesvaraya Technological University (VTU), Belgaum, India. In 2004, he graduated with a M.Sc. degree in Information Security from Information Security Group (ISG) at RHUL. He is currently in his final stages of a Ph.D. degree in Information Security at RHUL. He has extensive practical experience in security testing and product prototyping of smart card, mobile, location, contactless, RFID and proximity technologies. He is an acknowledged and published expert on NFC security. He started his career by working as a Software Engineer in Wipro Fluid Power LTD (Wipro Group), Bangalore, India; and more recently he worked as an Expert Consultant at Crisp Telecom UK LTD. He is currently employed as a Senior Research Engineer at France Telecom R&D UK LTD (Orange, UK) where he is enterprising excellence and innovation in information security.

**Dr. Mick Ganley** is an independent security consultant who has worked in the industry for 25 years. He specialises in the security of card payment systems, cryptography and key management, hardware security modules and security management. His current client list includes a number of the worlds largest multinational corporations. Until recently, he provided consultancy services to the prestigious ISG at RHUL, and was on the editorial board of the Information Security Technical Report, published jointly by the ISG and Elsevier. In previous lives he was an academic mathematician and Head of Security Analysis for the security division of Racal (now Thales).

**Univ.-Prof. DI Dr. Thomas Grechenig** is a Senior Architect in large IT systems and nation-wide IT-infrastructures. He is a Professor for Industrial Software Engineering at the Vienna University of Technology. He and his teams have planned, designed, and built several large scale NFC-solutions in payment, mobile keys, mobile ticketing, railway and public transport applications. In science and research the focus of interest goes towards (a) enhancing the stability and fine-tuning of the NFC-mass-concept in all its critical sectors (usability, security, IT-infrastructure, performance, integration and interoperability) (b) redefining every day use cases and interactions for the consumers via NFC in a way that preserves the users' old experiences while providing "the new ubiquitous feeling of simple touch interaction" in a natural form (c) this leads into a science aiming at re-understanding daily processes like payments, locking doors, showing tickets, or

personal identification in its newly adapted "Gestalt" in fusion of the old metaphors, new facilities as well as its privacy and security needs. From a more abstract scientific point of view Thomas Grechenig promotes NFC being one out of 5 major technology enablers towards a "vitalized" environment on all three relevant operative levels: (1) "desktop"/individual (2) buildings/groups (3) urban and regional/social.

**Dr. Gerhard Hancke** (B.E., M.E., Ph.D., CSCIP, SMIEEE) received a Bachelor and Masters of Engineering degrees in Computer Engineering from the University of Pretoria (South Africa) in 2002 and 2003, and a Ph.D. in Computer Science for the Security group at the University of Cambridge's Computer Laboratory in 2008. He joined the ISG in 2007 as a post-doc, working within the ISG Smart Card Centre managing the RFID/Contactless research track and RF/Hardware laboratory. In 2011, he was appointed as a Fellow within the ISG. His main interests are smart hardware tokens and their applications, mobile systems and pervasive computing.

**Graham Hili** B.Sc. I.T. Hons (Malta), M.Sc. (Royal Holloway) began his career with the Vodafone Group (Malta) where he was in charge of the security and the availability of the mobile value added systems (SMS, MMS, WAP). After this he moved to a consultancy position with Orange Group in The Netherlands. His current fields of specialisation include smart card security and the development of digital identity and digital security in IT systems and virtual worlds.

DI Christian Kantner graduated in Communications Engineering from the Vienna University of Technology in 1997 Christian Kantner joined Ascom Business Systems in Switzerland. He was responsible for the design and implementation of data and fax protocols for the Thuraya satellite phone system. Before he joined Mobilkom Austria in 2003 he was working as Freelancer for Ascom (Solothurn), Philips Semiconductors (Zurich) and Hughes Network Systems (San Diego, CA) in the field of GSM and Data Protocols. He taught Real Time Operating Systems for several years at the University of Applied Science in Upper Austria. In 2003 he joined Mobilkom Austria's TechLab, where he was responsible for analyzing new technologies for mobile phone operators, focusing mainly on mobile terminal technology. He has been investigating NFC technology since 2004 and got involved in NFC Forum activities in 2005. He is coeditor of the NFC technical guidelines white paper published by the GSMA. Christian Kantner joined Mobilkom Austria's m-commerce team as Product Manager for NFC in 2007. He was in the leading team for key NFC projects at Mobilkom Austria. From 2010 to 2012 Christian Kantner was head of IT and Services at Mobilkom Austrias daughter paybox Bank. Paybox Bank operates ad hoc mobile payment services for customers of A1, T-mobile Austria and Orange Austria. Christian Kantner has dedicated his career to wireless communications. Starting with 36,000 km satellite links and arriving at 3 cm NFC transactions. He has deep understanding about technological aspects as well as market insight. Christian Kantner is now driving the payment innovation roadmap in A1 Telekom Austria (former Mobilkom Austria).

**Stéphanie Kerckhof** is a Ph.D. student at Universit Catholique de Louvain. She received the Electro-mechanical Engineering Science degree from UCL in 2007 with her master thesis under the supervision of Pr. Jean-Didier Legat. She was a hardware developer for two years at intoPIX, Louvain-la-Neuve, Belgium. In April 2010, she started a Ph.D. thesis in Cryptography under the supervision of Pr. Franois-Xavier Standaert at UCL. Her researches are currently focused on cryptographic hardware design, side-channel analysis, and intellectual property protection.

**Mario Kirschbaum** received the B.Sc., M.Sc., and Ph.D. degrees in Telematics from Graz University of Technology in Austria, in 2005, 2007, and 2011, respectively. He is currently working as a member of the Secure Entities for Smart Environments (SEnSE) group of the Institute for Applied Information Processing and Communications (IAIK), Graz University of Technology, Austria. His research interests include implementation attacks, development and investigation of countermeasures, and the implementation of cryptographic hardware modules.

Dr. Gerald Madlmayr is an IT and Telecommunication Architect based in Vienna. In his daily work he is confronted with technology strategy for mobile network operators, software system and IT Integration in banking and payment systems as well as customer focused mobile technologies and devices. Besides that, he is Lecturer at the Vienna University of Technology at the Research Group for Industrial Software. There his research is focused on mobile technology in society as well as energy and environmental topics. Before that he worked as a Research Associate at the Research Center Hagenberg. There his work was focused on NFC/RFID based applications as well as security and privacy in such systems. He is an authority on NFC technology and applications, actively participating in the standardization of NFC. Within the scope of this job one of the most sophisticated NFC trials was launched in 2006. Previously Gerald Madlmayr was working as a visiting Researcher in Princeton/New Jersey at Siemens Corporate Research (SCR) dealing with the design and implementation of CSCW Systems. Before that he was part of the innovations department of Siemens mobile in Munich. There he also wrote this diploma thesis with the focus on image processing on mobile devices. Gerald Madlmayr holds a Diploma in Media Technology from the University of Applied Sciences of Hagenberg and a Ph.D. in Computer Science from the University in Linz.

Konstantinos Markantonakis B.Sc. (Lancaster University), M.Sc., MBA, Ph.D. (London) received his B.Sc. (Hons) in Computer Science from Lancaster University in 1995, his M.Sc. in Information Security in 1996, his Ph.D. in 2000 and his MBA in International Management in 2005 from RHUL. He is currently a Reader (Associate Professor) in the ISG. His main research interests include smart card security and applications, secure cryptographic protocol design, Public Key

Infrastructures (PKI) and key management, embedded system security, mobile phone operating systems/platform security, NFC/RFID security, grouping proofs, electronic voting protocols. Since completing his Ph.D., he has worked as an independent consultant in a number of information security and smart card related projects. He has worked as a Multi-application Smart Card Manager in VISA International EU, responsible for multi-application smart card technology for southern Europe. More recently, he was working as a Senior Information Security Consultant for Steer Davies Gleave, responsible for advising transport operators and financial institutions on the use of smart card technology. He is also a member of the IFIP Working Group 8.8 on Smart Cards. He has published more than 90 papers in international conferences and journals. He continues to act as a consultant on a variety of topics including smart card security, key management, information security protocols, mobile devices, smart card migration program planning/project management for financial institutions, transport operators and technology integrators.