# Ricardo Reis · Yu Cao Gilson Wirth *Editors*

# Circuit Design for Reliability

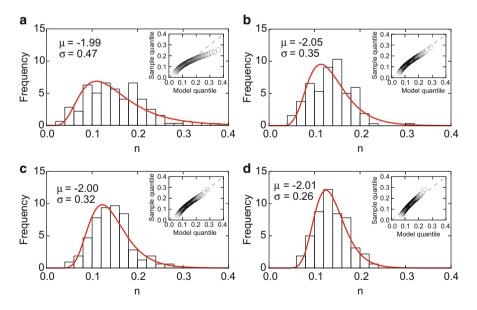

Circuit Design for Reliability

Ricardo Reis • Yu Cao • Gilson Wirth Editors

# Circuit Design for Reliability

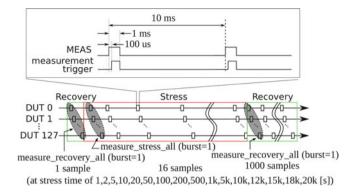

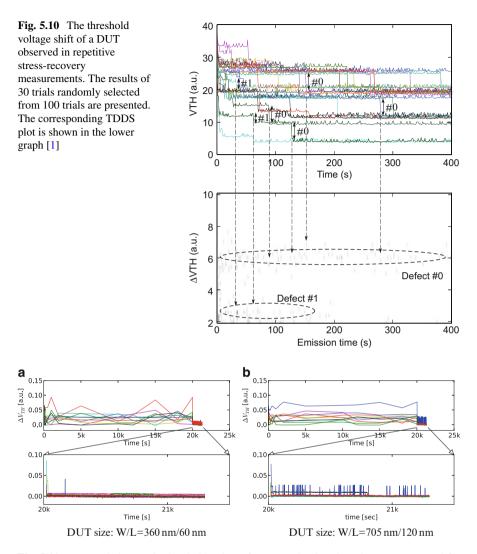

*Editors* Ricardo Reis Instituto de Informática Universidade Federal do Rio Grande do Sul (UFRGS) Porto Alegre, Rio Grande do Sul, Brazil

Gilson Wirth Electrical Engineering Department Universidade Federal do Rio Grande do Sul (UFRGS) Porto Alegre Rio Grande do Sul Brazil Yu Cao School of ECEE Arizona State University Tempe, USA

ISBN 978-1-4614-4077-2 ISBN 978-1-4614-4078-9 (eBook) DOI 10.1007/978-1-4614-4078-9 Springer New York Heidelberg Dordrecht London

Library of Congress Control Number: 2014952728

#### © Springer Science+Business Media New York 2015

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed. Exempted from this legal reservation are brief excerpts in connection with reviews or scholarly analysis or material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. Duplication of this publication or parts thereof is permitted only under the provisions of the Copyright Law of the Publisher's location, in its current version, and permission for use must always be obtained from Springer. Permissions for use may be obtained through RightsLink at the Copyright Clearance Center. Violations are liable to prosecution under the respective Copyright Law.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

While the advice and information in this book are believed to be true and accurate at the date of publication, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

## Contents

| 1 | Introduction<br>Ricardo Reis, Yu Cao, and Gilson Wirth                                                                                                     | 1   |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2 | Recent Trends in Bias Temperature Instability<br>B. Kaczer, T. Grasser, J. Franco, M. Toledano-Luque,<br>J. Roussel, M. Cho, E. Simoen, and G. Groeseneken | 5   |

| 3 | Charge Trapping Phenomena in MOSFETS: From Noise<br>to Bias Temperature Instability<br>Gilson Wirth and Roberto da Silva                                   | 21  |

| 4 | Atomistic Simulations on Reliability<br>Dragica Vasileska and Nabil Ashraf                                                                                 | 47  |

| 5 | <b>On-Chip Characterization of Statistical Device Degradation</b><br>Takashi Sato and Hiromitsu Awano                                                      | 69  |

| 6 | <b>Compact Modeling of BTI for Circuit Reliability Analysis</b><br>Ketul B. Sutaria, Jyothi B. Velamala, Athul Ramkumar,<br>and Yu Cao                     | 93  |

| 7 | <b>Circuit Resilience Roadmap</b><br>Veit B. Kleeberger, Christian Weis, Ulf Schlichtmann,<br>and Norbert Wehn                                             | 121 |

| 8 | Layout Aware Electromigration Analysis<br>of Power/Ground Networks<br>Di-an Li, Malgorzata Marek-Sadowska, and Sani R. Nassif                              | 145 |

| 9 | <b>Power-Gating for Leakage Control and Beyond</b><br>Andrea Calimera, Alberto Macii, Enrico Macii,<br>and Massimo Poncino                                 | 175 |

| 10 | <b>Soft Error Rate and Fault Tolerance Techniques for FPGAs</b><br>Fernanda Kastensmidt and Ricardo Reis | 207 |

|----|----------------------------------------------------------------------------------------------------------|-----|

| 11 | Low Power Robust FinFET-Based SRAM Design in Scaled<br>Technologies                                      | 223 |

|    | Sumeet Kumar Gupta and Kaushik Roy                                                                       |     |

| 12 | Variability-Aware Clock Design                                                                           | 255 |

|    | Matthew R. Guthaus and Gustavo Wilke                                                                     |     |

## Chapter 1 Introduction

Ricardo Reis, Yu Cao, and Gilson Wirth

The scaling of CMOS technology to the nanometer regime inevitability increases reliability concerns, profoundly impacting all aspects of circuit performance and posing a fundamental challenge to future IC design. These reliability concerns arise from many different sources, and become more severe with continuous scaling.

VLSI design in the late CMOS era is then driven by an increasing challenge to cope with unreliable components at the device and circuit levels. Early approaches focused only on technology improvement, but ignoring these effects in the design process causes an excessive amount of over-margining, with negative impact in both cost and performance of the final product. At the device and circuit levels, physical understanding, modeling, detection, and successful design techniques for leading reliability mechanisms are vitally important, not only to current robust design practice, but also to the prediction and management of system reliability over the full product life cycle. It is critical to understand, simulate, and mitigate their impact during the stage of physical and circuit design. This book presents physical understanding, modeling and simulation, on-chip characterization, layout solutions, and design techniques that are effective to enhance the reliability of various circuit units.

We start by addressing the physical mechanisms of reliability, focusing on aging and noise. Aging is among the critical reliability issues facing present and future deeply downscaled CMOS devices, and the major concern is the so-called Bias Temperature Instability (BTI). The elementary definitions and experimental

R. Reis • G. Wirth

Y. Cao (🖂)

Electrical Engineering Department, Universidade Federal do Rio Grande do Sul (UFRGS), Porto Alegre, Rio Grande do Sul, Brazil

School of ECEE, Arizona State University, Tempe, AZ, USA e-mail: ycao@asu.edu

<sup>©</sup> Springer Science+Business Media New York 2015 R. Reis et al. (eds.), *Circuit Design for Reliability*, DOI 10.1007/978-1-4614-4078-9\_1

observations of BTI are first briefly reviewed. Afterwards it is shown how the understanding of gate oxide defect properties can be used to explain BTI and its variability, and possible technological solutions for both nFETs and pFETs are discussed. The charge trapping phenomena that plays a dominant role in BTI also dominates low-frequency noise. A modeling and circuit simulation approach that focuses on operation conditions relevant for digital and analog design, including large signal AC operation, is presented. The modeling and simulation approach aims at helping circuit designers to cope with this reliability issue.

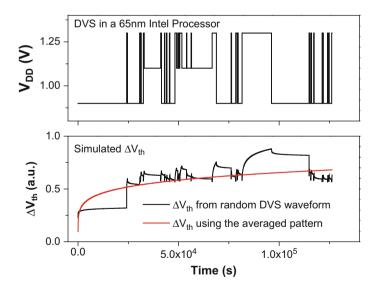

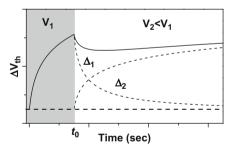

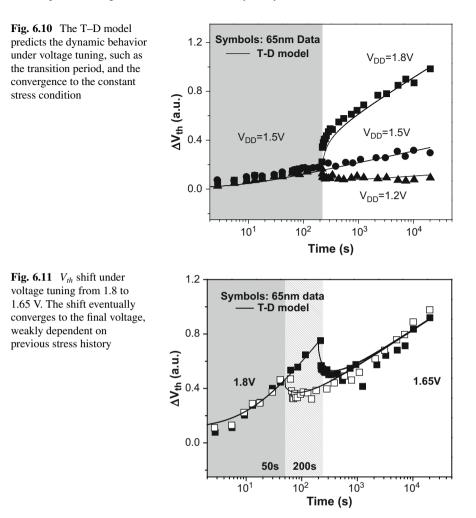

Next, the modeling and characterization is addressed. Any modeling effort needs a solid base to be built on. Models are based on accurate measurement methodologies, which contribute to understanding the mechanisms behind the device degradation. In this book, authors survey characterization methods for the purpose of device modeling that includes the effects of temporal parameter degradation, such as BTI and noise. Particular focus is placed on the approaches that utilize on-chip circuits to enhance the accuracy and fidelity of the measurements. Modeling must focus on real circuit operation conditions, such as Dynamic Voltage Scaling (DVS), or biasing found in mixed signal designs where the stress waveform is much more random. Modeling solutions suitable to allow aging simulation under all dynamic stress conditions are presented.

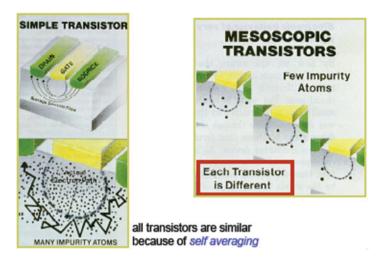

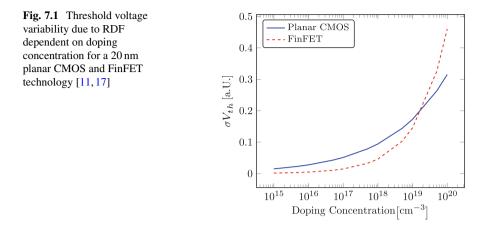

Variability in electrical parameters, such as variability in threshold voltage, is also known to be a major reliability concern. Among the sources of variability is random dopant fluctuation (RDF). We discuss how RDF can induce significant variation in saturation (on) current and transconductance degradation—two key metrics for benchmark performance of digital and analog integrated circuits.

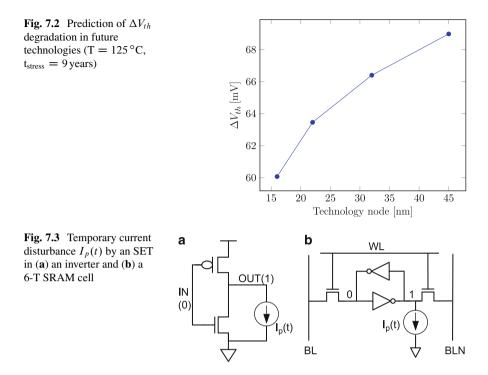

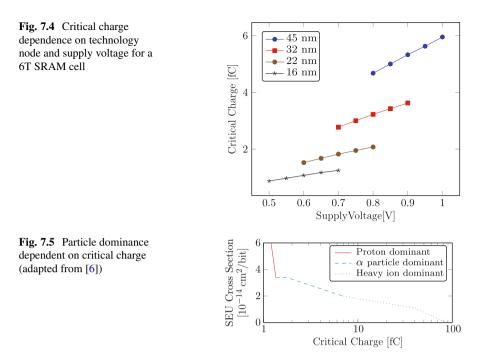

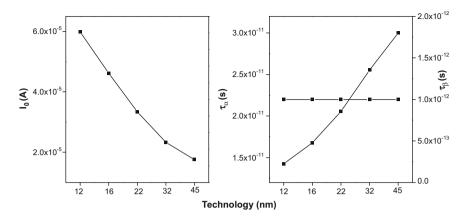

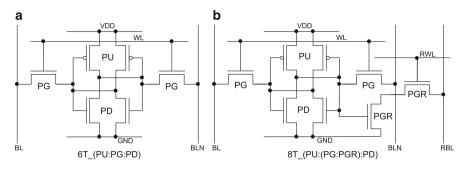

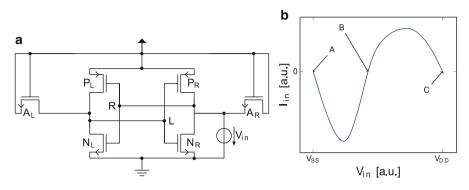

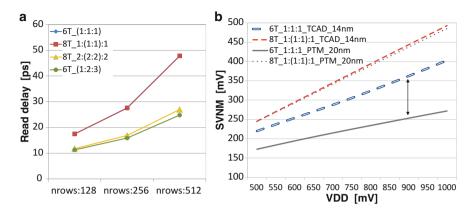

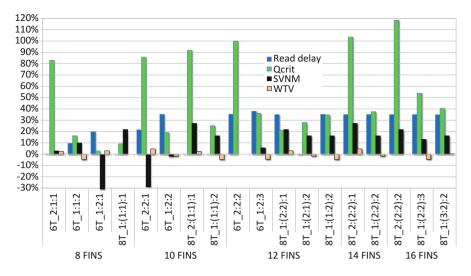

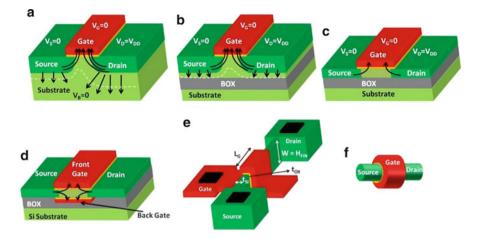

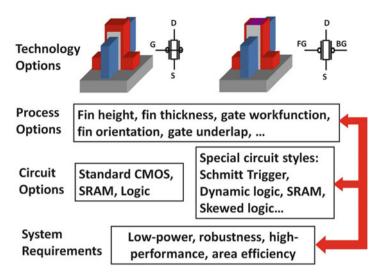

An analysis of ongoing scaling related trends of integrated circuits is also presented. For this purpose, authors discuss major trends observed in process technology, as well as in memory and logic designs. While newer technology styles, such as FinFETs provide necessary advances to enable further technology scaling, we can observe that there exists also a trend for reduced resilience with ongoing scaling. Our hope is that with the roadmap presented in this book, which concentrates on FinFET-based designs, we are able to sensitize the research community to present and near future problems associated with this technology. Additionally, different architectures for SRAM memories are analyzed, to demonstrate the different design choices available and tradeoffs that have to be made.

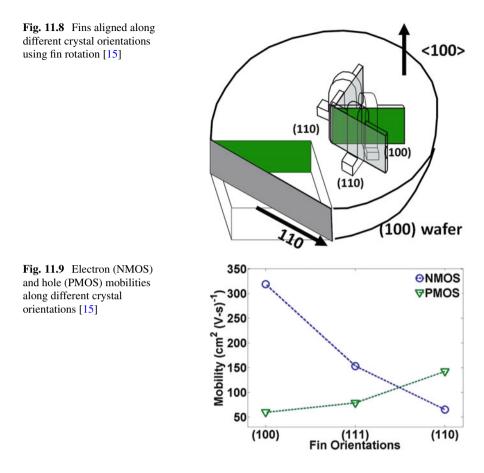

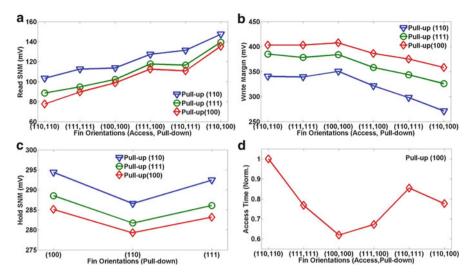

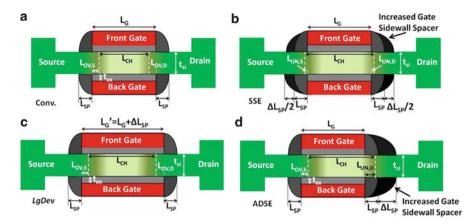

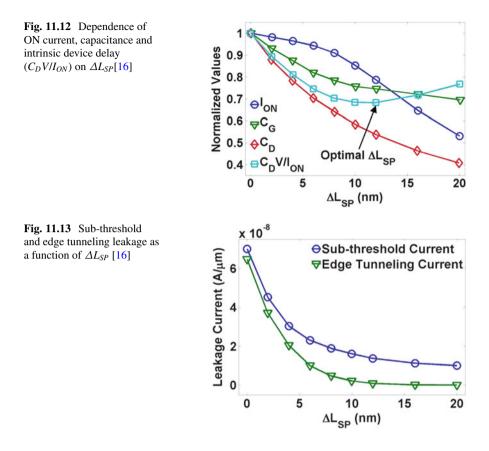

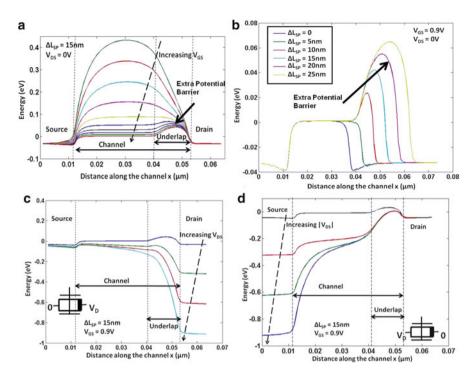

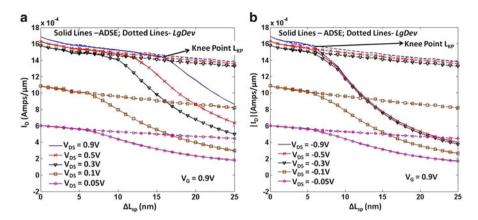

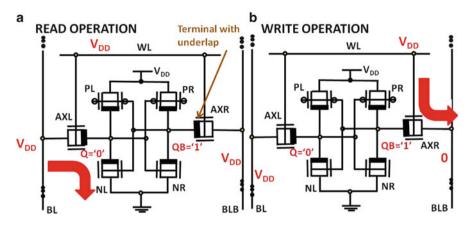

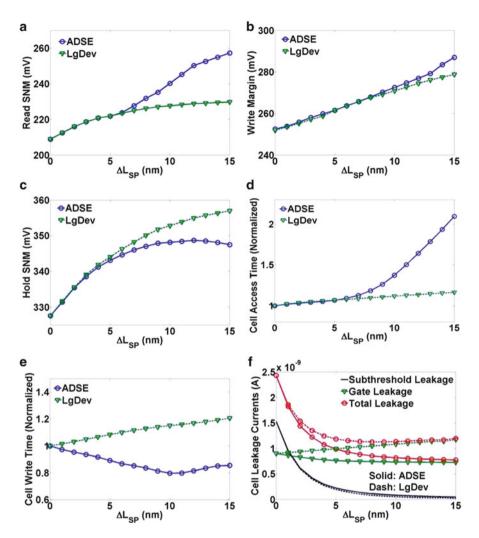

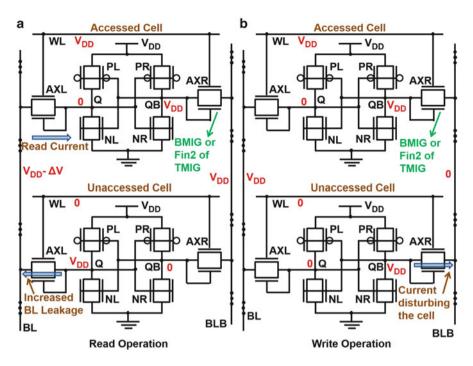

Finally, the last chapters present design techniques for reliability. FinFETs have emerged as alternatives to conventional bulk MOSFETs in scaled technologies due to superior gate control of the channel, lower short channel effects and higher scalability. However, width quantization in FinFETs constrains the design space of FinFET-based circuits, especially SRAMs in which transistor sizing is critical for the circuit robustness. The adverse effects of width quantization can be mitigated by appropriate device-circuit co-design of FinFET-based memories. Some of such techniques are described, with an emphasis on the device-circuit interactions associated with each methodology. The impact of different technology options in FinFETs like gate-underlap, fin orientation, fin height, gate workfunction and independent control of the gates on the stability, power and performance of 6T SRAMs is discussed.

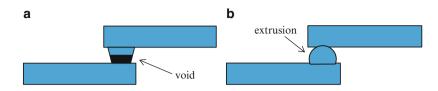

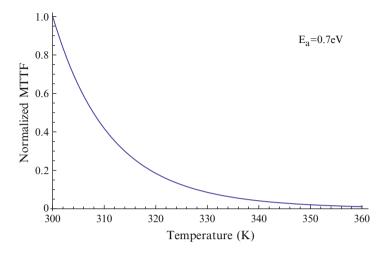

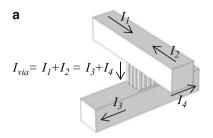

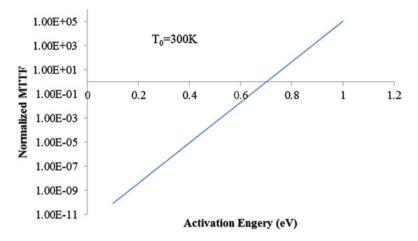

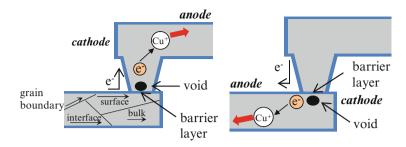

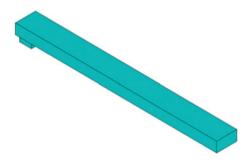

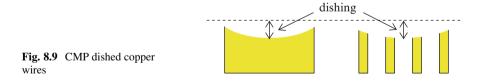

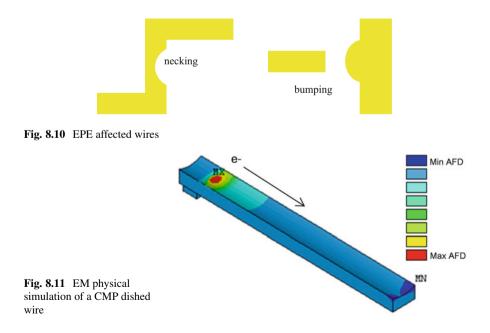

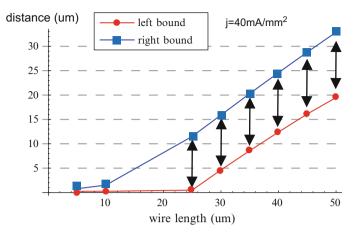

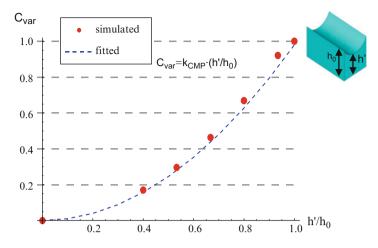

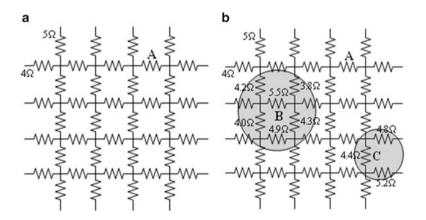

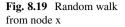

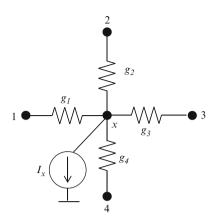

Electromigration is an aging effect that affects metal wires (interconnections). In this book, authors briefly introduce physical foundations of electromigration (EM). We discuss physical parameters affecting EM wire lifetime and we introduce some background related to the existing EM physical simulators. In the work presented in this book for EM physical simulation, authors adopt the atomic concentration balance-based model. We discuss the simulation setup and results. We present VEMA, a variation-aware electromigration (EM) analysis tool for power grid wires. The tool considers process variations caused by the chemical–mechanical polishing (CMP) and edge placement error (EPE). VEMA is a full-chip EM analysis tool. It performs EM lifetime calculation, and analyzes process variation effects on EM reliability and reports variation tolerances of EM-sensitive power grid wires.

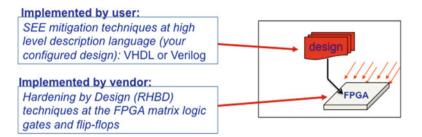

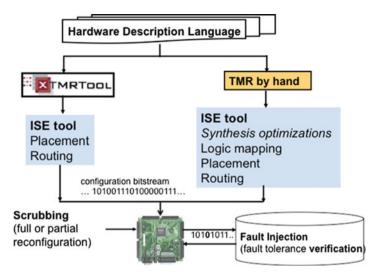

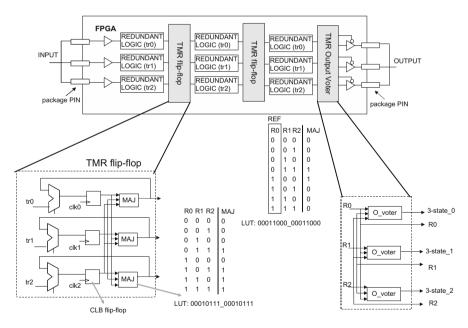

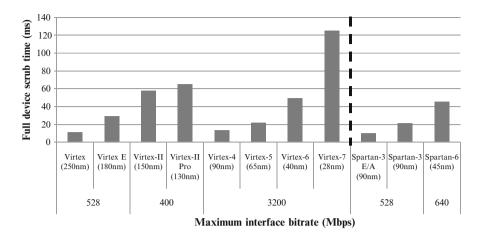

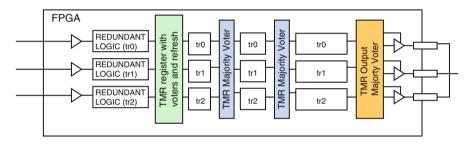

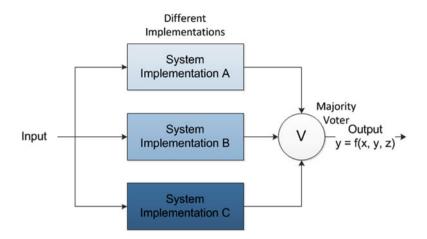

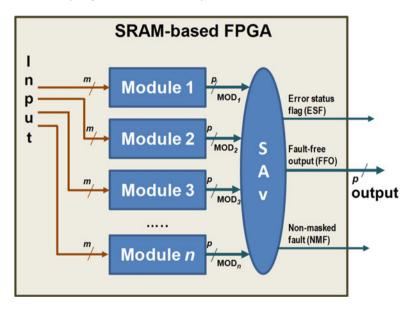

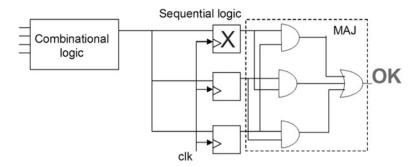

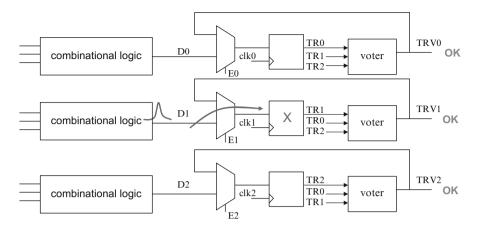

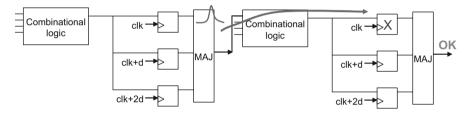

Integrated circuits subject to ionizing radiation are sensitive to transient faults caused by the interaction of ionizing particles with the semiconductor. At ground level, the main source of radiation are neutrons that interact with the material generating secondary particles that can ionize the silicon, provoking transient upset in circuits fabricated in nanometer technology. The interaction of the ionizing radiation with the transistor may provoke transient and permanent effects. Different fault tolerance techniques can be applied to FPGAs according to their type of configuration technology, architecture and target operating environment. A chapter is dedicated to present a set of fault mitigation techniques for SRAM, FLASH and ANTIFUSE-based FPGAs. A test methodology to characterize those FPGA under radiation is also presented. Results from neutron-induced faults are presented and discussed.

The relevance of power consumption and leakage currents is also increasing. Although several Design-for-Low-Power and Design-for-Variability options are already available in modern EDA suites, the contrasting nature of the two metrics makes their integration extremely challenging. Most of the approaches used to compensate and/or mitigate circuit variability (e.g., Dynamic Voltage Scaling and Adaptive Body Biasing) are, in fact, intrinsically power inefficient, as they exploit the concept of redundancy, which is known to originate power overhead. In this book, we introduce possible solutions for concurrent leakage minimization and variability compensation. More specifically, authors propose Power-Gating as a mean for simultaneously controlling static power consumption and mitigating the effects induced by two of the most insidious sources of variability, namely, electrical parameter variations and Aging due to BTI.

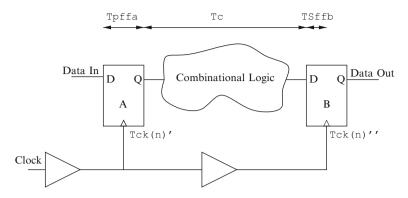

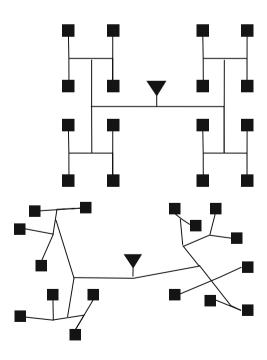

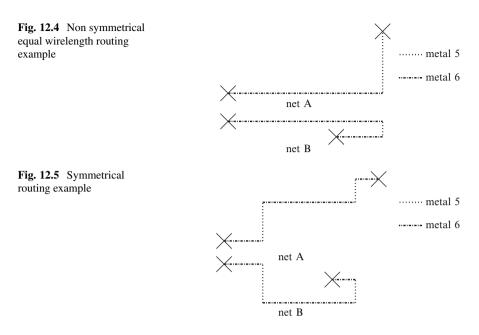

High-performance clock network design has been a challenge for many years due to the drastically increasing effect of process variability. In addition, tight power budgets have lowered supply voltage levels, which make designs more sensitive to noise. Together, variability and noise present a colossal challenge to clock designers in order to meet timing, yield, and power simultaneously. This chapter discusses the different strategies that designers use to ameliorate variability and noise problems in clock network design. The project of this book was born during the successful IEEE Circuits and Systems Society Summer School on Physical Design of Reliable Circuits that was held in Porto Alegre, Brazil, from January 12 to 15, 2010. Some chapters of the book are based on the talks realized during the school and other well-known invited authors wrote other chapters.

It is our hope that this book will provide the vitally important physical understanding and design techniques for state of the art and future technologies, ranging from technology modeling, fault detection and analysis, circuit hardening, and reliability management in different circuit units.

## Chapter 2 Recent Trends in Bias Temperature Instability

B. Kaczer, T. Grasser, J. Franco, M. Toledano-Luque, J. Roussel, M. Cho, E. Simoen, and G. Groeseneken

**Abstract** The paradigm shifts occurring in the past few years in our understanding of BTI are reviewed. Among the most significant ones is the shift from perceiving NBTI in terms of the Reaction-Diffusion model to analyzing BTI with the tools originally developed for describing low-frequency noise. This includes the interpretation of the time, temperature, voltage, and duty cycle dependences of BTI. It is further demonstrated that a wealth of information about defect properties can be obtained from deeply-scaled devices, and that this information can allow projection of variability issues of future deeply downscaled CMOS devices. The chapter is concluded by showing the most promising technological solutions to alleviate both PBTI and NBTI.

#### 1 Introduction

Among the critical reliability issues facing present and future deeply downscaled CMOS devices is the so-called Bias Temperature Instability (BTI). While BTI in nFET devices was generally ascribed to charge trapping in the high-k portion of the gate oxide, the interpretation of BTI in pFET devices still generates controversy [1–7]. This phenomenon in pFET devices has been previously described by diffusion of hydrogen from and back into substrate/gate oxide interface states [8]. The so-called Reaction–Diffusion model based on this assumption is still popular, especially in the design community [9], despite being inconsistent with some crucial observations [10].

In this chapter, the elementary definitions and experimental observations of BTI are first briefly reviewed. One of the most intriguing properties of BTI—the lack

e-mail: kaczer@imec.be

B. Kaczer (🖂) • J. Franco • M. Toledano-Luque • J. Roussel • M. Cho

<sup>•</sup> E. Simoen • G. Groeseneken imec, Leuven, Belgium

T. Grasser TU Wien, Wien, Austria

G. Groeseneken KU, Leuven, Belgium

<sup>©</sup> Springer Science+Business Media New York 2015 R. Reis et al. (eds.), *Circuit Design for Reliability*, DOI 10.1007/978-1-4614-4078-9\_2

of characteristic time scale, especially in pFETs—is then argued to point to a *dispersion* in the underlying mechanism [5, 7, 11]. In CMOS technologies, a response on many time scales is typical for low-frequency noise [and its manifestation as Random Telegraph Noise (RTN) in deeply-scaled devices], suggesting that (the principal component of) BTI is in fact caused by the same defects [12, 13]. The link between BTI and low-frequency noise is then further developed—it is shown that many properties of gate oxide defects can be directly extracted from BTI relaxation measurements in deeply-scaled devices [14] and the noise-inspired model capable to fully describe these properties is reviewed. Afterwards it is shown how the understanding of gate oxide defect properties can be used to explain variability of BTI in deeply-scaled technologies, as well as possible technological solutions for both nFETs and pFETs.

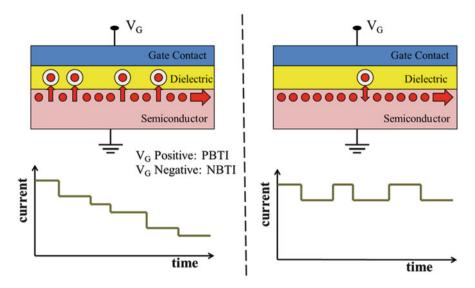

#### 2 Brief Overview of BTI

BTI is a consequence of charging of defect states in the gate oxide and at its interface [2]. The defects could be both pre-existing or generated during device operation. The trapped charge results in a shift of the device parameters, such as its threshold voltage  $V_{th}$ , channel mobility, transconductance, and subthreshold slope, and generally a decrease of the FET's drive current. The name is derived from the phenomenon being strongly accelerated by *temperature T* and gate *bias V<sub>G</sub>*. BTI in n-channel FET devices, which are typically biased in circuits at positive  $V_G$ , is referred to as Positive BTI (PBTI), while negative BTI (NBTI) takes place in p-channel FETs. Constant  $V_G$  stress bias is often referred to as static, or "DC" BTI, while periodically interrupted  $V_G$  stress is called "AC", or dynamic BTI.

#### 3 Static BTI

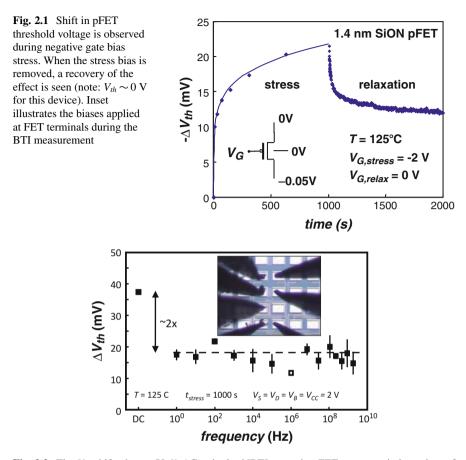

Figure 2.1 illustrates the typical gradual shift of pFET threshold voltage  $\Delta V_{th}$  during accelerated stress at elevated *T* [5]. The stress data are typically measured at several  $V_G$ 's and  $\Delta V_{th}$  is extrapolated to 10 years at the circuit operating voltage  $V_{DD}$  (or  $V_{DD} + 10$  %). The extrapolated  $\Delta V_{th}$  must be below a given value (typically 30 or 50 mV) for the technology to qualify.

This simple extrapolation procedure is, however, complicated by  $\Delta V_{th}$  decreasing *immediately* after the stress bias is removed, as illustrated in Fig. 2.1 [15]. As will be discussed henceforth, this *recovery*, or *relaxation*, component *R* typically proceeds simultaneously on many time scales, making it difficult to determine its beginning or end and thus separating it from the final *non-recoverable*, or *permanent*, component *P* [2, 6]. This  $\Delta V_{th}$  relaxation is thus a crucial problem for BTI measurement, interpretation, and extrapolation.

**Fig. 2.2** The  $V_{th}$  shifts due to 50 % AC unipolar NBTI stress in pFETs are seen independent of frequency in the entire frequency range of 1 Hz–2 GHz. The  $V_{th}$  shift of the corresponding DC NBTI stress obtained on an identical device is shown for comparison. Inset: Micrograph of the *on-chip* circuit for the DC and AC BTI measurements consisting of a ring oscillator, a frequency divider, a buffer, a pass-gate-based multiplexer, and the device under test [17]

#### 4 Dynamic BTI

In many CMOS applications, such as logic, the majority of the FETs are constantly switched and thus exposed to *dynamic* stress [16]. Figure 2.2 documents that NBTI is present at frequencies up to the GHz range, i.e., there does not appear to be any "cut-off" time constant of the degradation mechanism above  $\sim 1$  ns [17]. Furthermore, the AC bias signal reduces BTI with respect to the DC stress. This provides some additional reliability margin, which can be factored in during the application design phase [9].

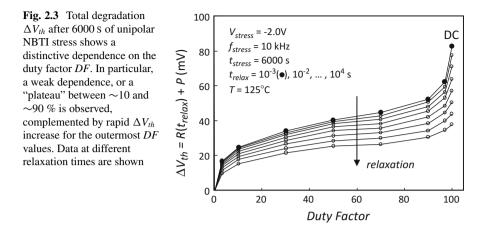

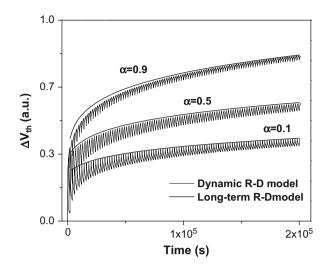

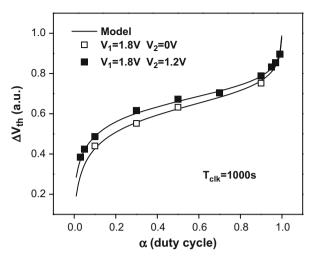

In an arbitrary FET of an arbitrary digital circuit, the average probability of a signal being high can vary between 0 and 100 %. The dependence of BTI on the *duty cycle* (called *duty factor* or *DF* here) thus needs to be studied. A NBTI  $\Delta V_{th}$ -*DF* dependence with an inflection point around *DF* ~50 %, first reported in [17], is shown in Fig. 2.3 [12].

## 5 Similarity Between BTI Relaxation and Low-Frequency Noise

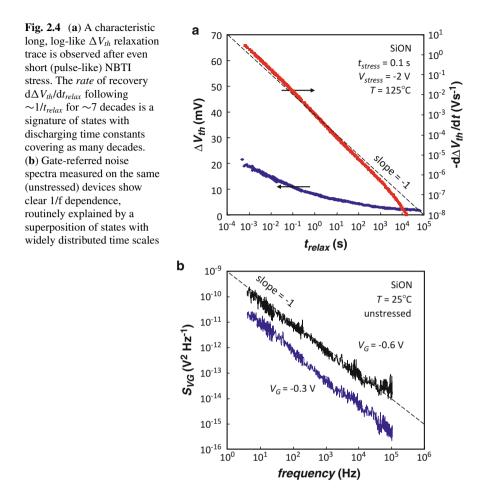

Long, log(*t*)-like behavior of  $\Delta V_{th}$  without a characteristic time scale is typically observed in both the initial portion of NBTI degradation [13, 18] and the recovery phase. Figure 2.4 illustrates that the *rate of degradation*  $d\Delta V_{th}/dt_{relax}$  [7] extracted from the log( $t_{relax}$ )-like  $\Delta V_{th}$  NBTI relaxation transient after even a *very short*, 0.1 s stress, follows  $1/t_{relax}$  for over seven decades. Such behavior is a signature of states with discharging time constants covering as many decades [19].

Incidentally, *superposition of states with widely distributed time scales* is the standard explanation of the 1/f noise spectra [20], which are clearly observed in our pFETs (Fig. 2.4). This obvious similarity leads us to argue that the same states with widely distributed time scales in fact play a fundamental role in both NBTI and noise measurements.

#### 6 Semi-quantitative Model for BTI Relaxation

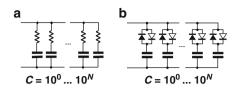

In order to visualize this common property it is beneficial to consider an equivalent circuit representing states with widely distributed time scales [19]. Note that in either NBTI relaxation or 1/f noise measurements, no maximum or minimum "cut-

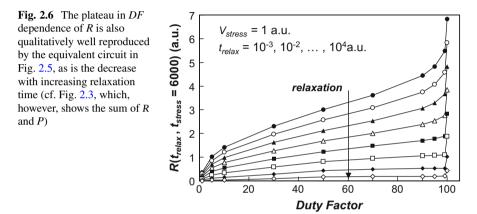

off" times are typically observed [12]. For the sake of simplicity it is therefore assumed here that the time constants are log-uniformly distributed from times much shorter than the switching time of a pFET to very long, corresponding to the lifetime of a CMOS application. Such states with widely distributed time scales are then represented by "RC" elements in Fig. 2.5 with the total FET  $\Delta V_{th}$  being proportional to the sum of voltages ("occupancies") on all capacitors. For the sake of simplicity, it is assumed that all RC elements have the same weight and can be partially occupied, which emulates the behavior of a large-area device. Most properties of the recoverable component can be reproduced when the ohmic resistors in Fig. 2.5 are replaced with a *non-linear* component (simulated by two diodes with different parameters, see Fig. 2.5), which emulates different charging (i.e., capture) and discharging (i.e., emission) time constants of each defect [21]. Such a circuit correctly reproduces *DF* (Fig. 2.6, cf. Fig. 2.3) and also the log-like relaxation (Fig. 2.4a) and the log-like initial phase of stress (not shown) [19].

Fig. 2.5 (a) An equivalent circuit with exponentially increasing capacitances used to emulate defect states with widely distributed time scales, such as those active in low-frequency noise. (b) The same circuit modified to account for charging (i.e., capture) and discharging (i.e., emission) time constants being voltage dependent, represented by asymmetric diodes. The sum of voltages on capacitors is assumed to be proportional to FET  $\Delta V_{th}$

#### 7 Properties of Individual Defects

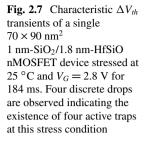

Figure 2.7 shows two typical  $\Delta V_{th}$  relaxation transients following positive  $V_G$  stress on a single 70 × 90 nm<sup>2</sup> nMOSFET (i.e., corresponding to PBTI). Conversely to the continuous relaxation curves obtained on large devices, a quantized  $\Delta V_{th}$  transient is observed in the deeply-scaled devices. In such devices, the relaxation is observed to proceed in discrete voltage steps, with each step corresponding to discharging of a *single* oxide defect [12, 22, 23]. Upon repeated perturbation, each defect shows up in the relaxation trace with a characteristic "fingerprint" consisting of its discharge, or *emission* time, and its voltage step [14].

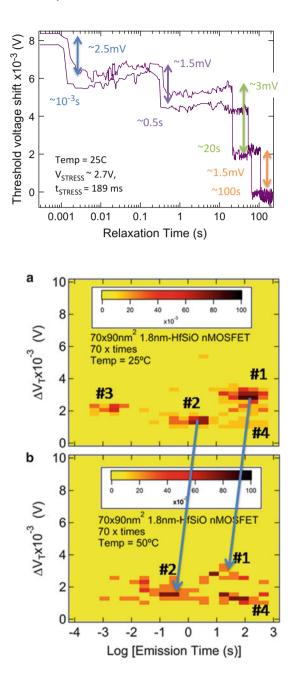

Figure 2.8 shows the two-dimensional histogram of the heights and the emission times of the steps when the experiment was repeated 70 times at the same stressing and relaxing condition as in Fig. 2.7 [14]. In Fig. 2.8, four clusters are clearly formed that correspond to four active defects in the time window of the experimental setup.

The emission times of each defect are stochastically distributed and follow an exponential distribution. This allows us to determine the average emission time  $\tau_e$ . The capture time of each trap can be obtained by varying the stress (i.e., charging) time from 240 ms down to 2 ms. The intensity of the cluster decreases with reducing

Fig. 2.8 Two-dimensional histograms (TDDS spectra) of the heights and emission times of the steps extracted from 70  $\Delta V_{th}$  transients of the particular device of Fig. 2.7 at (a) 25 °C and (b) 50 °C. Four clusters are formed that shift horizontally to shorter emission times with increasing temperature. Note that trap #3 disappears from the experimental window at 50 °C

stress time when the characteristic capture time is in the range of the stress time. The fit of the intensity to  $P_c = 1 - \exp(-t_{stress}/\tau_c)$  lets us calculate the average capture time  $\tau_c$ . This technique is known as Time Dependent Defect Spectroscopy (TDDS) [14].

In Fig. 2.8, an identical experiment was repeated at 50 °C on the same device. Note the large horizontal shift of the clusters to shorter emission times with only a 25 °C temperature increase. The Arrhenius plots of the emission and capture times obtained at *T* from 10 to 50 °C (not shown) provide activation energies of 0.48 eV for emission and 0.25 eV for capture. Similarly thermally activated capture and emission times are also observed in both nFET and pFET (i.e., corresponding to NBTI) with conventional SiO<sub>2</sub> gate oxide [14, 23, 24]. One can therefore conclude for all these cases that *both emission and capture in both electron and hole gate oxide traps are without a doubt thermally activated processes*. This experimental fact is incompatible with direct elastic tunneling theories widely used in different oxide trap characterization techniques and calculations. Consequently, a new model that takes into account this thermal dependence has to be considered.

#### 8 Modeling Properties of Individual Defects

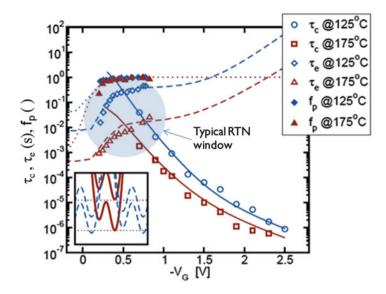

A model of the above-described properties of individual gate oxide defects can be constructed by drawing on the above similarities with low-frequency and Random Telegraph Noise (RTN) [25]. An example of the configuration coordinate diagram of the model is shown in the inset of Fig. 2.9. Four different configurations of the defect are considered [14]. Two of the states are electrically neutral while two of them correspond to the singly positively charged state. In each charge state the defect is represented by a double well, with the first of the two states being the equilibrium state and the other a secondary (metastable) minimum. The time dynamics of the defect can be described by a simple stochastic Markov process. Broadly, transition rates between states involving charge transfer assume (1) tunneling between the substrate and the defect, and (2) nonradiative multiphonon (NMP) theory, which has been often applied to explain RTN [26, 27]. Introduction of the NMP theory naturally explains the temperature dependence of both capture and emission time constants observed in the previous section. The wide distribution of time scales is then readily described by a distribution of the overlaps of the potential wells (i.e., a distribution of "potential barriers") [14].

The crucial extension of the NMP theory is the assumption of the relative position of the potential wells changing with gate bias [14], quite naturally introducing the required strong  $V_G$  dependence. As documented in Fig. 2.9, the model successfully describes the bias as well as the temperature dependences of the characteristic time constants. It is also noted that, contrary to techniques for the analysis of RTN, which only allow monitoring the defect behavior in a rather narrow time window, TDDS can be used to study the defects capture and emission times over an extremely wide range.

**Fig. 2.9** Simulated capture and emission time constants (*lines*) compared with to the experimental TDDS values obtained on SiO<sub>2</sub> pFETs (*symbols*) during NBTI stressing at 125 and 175 °C and varying  $V_G$ . The experimental occupation probability of the charged state  $f_p$  is also indicated. The configuration coordinate diagram is shown in the inset (*dashed line*: neutral defect state; *solid line*: charged state potential)

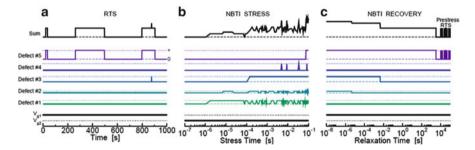

Fig. 2.10 Simulated RTN, stress, and recovery behavior of a nano-scale device using a stochastic solution algorithm of the proposed model. (a) At the threshold voltage (Vg1), the RTN is dominated by defect #5 with the occasional contribution from defect #3. Defects #1, #2, and #4 remain positively charged within the 'simulation/experimental' window. (b) During stress (Vg2), the capture times are dramatically reduced by the higher (more negative) gate voltage and the defects #3 and #5 become predominantly positively charged ( $\tau c \ll \tau e$ ). Defects #1, #2, and #4 start producing RTN. (c) During recovery (back at Vg1), trapped charge is subsequently lost and the dynamic equilibrium behavior is gradually restored

It has been previously argued that the phenomenon called NBTI relaxation in pFET devices is in fact just a different facet of the well-known low-frequency noise in these devices. While the low-frequency noise corresponds to the channel/gate dielectrics system being in the state of dynamic equilibrium, NBTI relaxation corresponds to the perturbed system returning to this equilibrium [28]. Figure 2.10

then illustrates this concept on a simulated example of a deeply scaled pFET containing only five active defects [23]. In particular it shows that the same defects can be responsible both for RTN as well as the NBTI relaxation and the (initial phase of) NBTI stress.

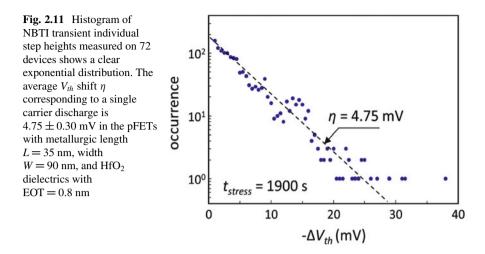

#### 9 BTI Distribution in Deeply-Scaled FETs

As CMOS devices scale toward atomic dimensions, device parameters become statistically distributed. Similarly, parameter *shifts* during device operation, once studied in terms of the average value only, will have to be described in terms of their distribution functions. The understanding of the properties of individual defects helps us to explain this distribution. Namely, much like in the case of random telegraph noise (RTN) [29, 30], it is observed the distribution of down-steps  $\Delta V_{th}$  due to *individual* discharging events to be *exponentially* distributed (Fig. 2.11). The exponential distribution of single-charge  $\Delta V_{th}$  can be understood if non-uniformities in the pFET channel due to random dopant fluctuations (RDF) are considered [28–30]. A *single* discharging event in many devices routinely exceeded 15 mV, *and in several devices exceeded 30 mV*, the NBTI lifetime criterion presently used by some groups. For comparison,  $\Delta V_{th}$  of less than 2 mV would be expected based on a simple charge sheet approximation. The large observed step height amplitude is due to the aggressively scaled dimensions of the pFETs used [28, 31].

Assuming the lateral locations of the trapped charges are uncorrelated, the overall  $\Delta V_{th}$  distribution can be readily expressed as a convolution of individual exponential distributions [28, 31]. An actual population of stressed devices will

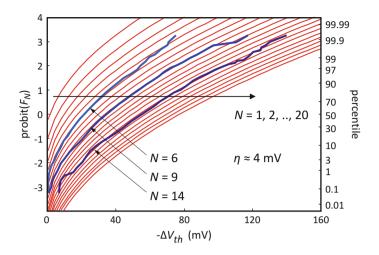

**Fig. 2.12** Equation (2.1) in a probit plot rescaled to fit experimental distributions from Fig. 2.10 of Ref. [22], with the corresponding values of N and  $\eta$  readily extracted

consist of devices with a *different* number *n* of oxide defects in each device, with *n* being Poisson distributed [12, 22, 28]. The *total*  $\Delta V_{th}$  distribution can be therefore obtained as

$$F_N\left(\Delta V_{th},\eta\right) = \sum_{n=0}^{\infty} \frac{e^{-N} N^n}{n!} \left[1 - \frac{n \Gamma\left(n, \Delta V_{th}/n\right)}{n!}\right],\tag{2.1}$$

where *N* is the mean number of defects in the FET gate oxide and is related to the oxide trap (surface) density  $N_{ot}$  as  $N = W L N_{ot}$ . The CDF is plotted in Fig. 2.12 for several values of *N*. For comparison, measured total  $\Delta V_{th}$  distributions for three different stress times from Ref. [22] are excellently fitted by the derived analytical description.

The advantage of describing the total  $\Delta V_{th}$  distribution in terms of Eq. (2.1) is its relative simplicity and tangibility of the variables. The analytical description allows, among other things, to calculate NBTI threshold voltage shifts in an unlimited population of devices, a feat practically impossible through device simulations.

#### **10** Technological Solutions

Once the underlying BTI mechanisms are understood, the defect properties can be modified to beneficial ends. Below, two possible technological solutions for both PBTI and NBTI are discussed.

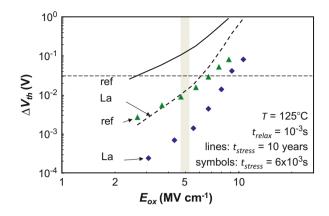

Fig. 2.13 A significant reduction of PBTI threshold voltage shift is observed in planar nFETs with La passivation ("La") over the reference stack ("ref") without passivation. Simplified power-law projection to 10 years shows passivated stack having sufficient reliability ( $\Delta V_{th} < 30 \text{ mV}$ ) at ~5 MV/cm operating field

#### 11 Improving PBTI with Rare-Earth Incorporation

PBTI was considered a minor problem in technologies based on SiO<sub>2</sub>. It arose as a reliability issue when high-k materials were incorporated into the gate stack. However, when rare earths were introduced to adjust the nFET initial threshold voltage, this issue was mitigated, as can be seen in Fig. 2.13. A significant reduction of PBTI is observed in planar nFETs with lanthanum with respect to a lanthanum-free reference [32].

Positive BTI in nFETs with high-k materials like  $HfO_2$  has been linked to oxygen vacancies, which produce a defect level in the upper part of the oxide band gap. Group III elements compensate unpaired electrons around the oxygen vacancy in  $HfO_2$  and the defects are "passivated" by being pushed up toward the conduction band minimum [33]. Such states are not easily accessible to nFET channel electrons, resulting in the significant reduction of negative charge capture in the stack and hence the reduction of PBTI.

#### 12 Improving NBTI in High-Mobility SiGe pFETs

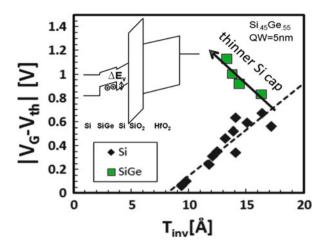

Reduction of gate stack EOT, which is one of the most efficient ways to improve FET performance, enhances NBTI due to increased oxide electric field. As a consequence, 10 year lifetime can be guaranteed for sub-1 nm EOT Si pFETs only at gate overdrive voltages far below the expected operating voltages (Fig. 2.14).

Another way to improve FET performance is the use of high-mobility substrates, such as buried-channel SiGe [34]. Because of the valence band offset between the

**Fig. 2.14** Plot of the operating overdrive voltage  $|V_G - V_{th}|$  for 10 year lifetime assuming a 30 mV threshold voltage shift criterion vs. the inversion capacitance equivalent thickness  $T_{inv}$ , for Si channel devices with different processing used as a reference, and for SiGe pFETs. For low  $T_{inv}$ , Si devices  $|V_G - V_{th}|$  is below the expected operating voltage. In contrast to that, optimized SiGe devices show improved lifetime. *Inset*: gate-stack band diagram in inversion. Si cap acts as a barrier  $\Delta E_V$  for holes

SiGe and the Si cap (see inset of Fig. 2.14), inversion channel holes are confined in the SiGe layer, which therefore acts as a quantum well (QW) for holes. The Si cap lowers the inversion capacitance as compared to the accumulation capacitance. For these devices it is therefore necessary to report the capacitance-equivalent thickness in inversion ( $T_{inv}$ , evaluated at  $V_G = V_{th} - 0.6$  V) which will be affected by the thickness of the Si cap [35].

As can be seen from Fig. 2.14, SiGe-based device gate stacks significantly increase operating gate overdrive while still guaranteeing 10 year device lifetime and at the moment seem to be the only solution to the NBTI issue for sub-1 nm EOT devices. It has been recently observed that both increasing the Ge content in the channel as well as increasing the SiGe QW thickness reduces NBTI. Most intriguingly, a *reduction* of Si cap thickness also diminishes NBTI [35]. The most likely hypothesis explaining all three trends appears to be the energetic decoupling of the buried channel and the gate oxide defects [36].

#### Conclusions

In this chapter some of the shifts occurring in the past few years in our understanding of BTI were reviewed. Among the most significant ones is the shift from perceiving NBTI in terms of the Reaction–Diffusion model to analyzing BTI with the tools originally developed for describing low-frequency

(continued)

noise. This includes the interpretation of the time, temperature, voltage, and duty cycle dependences of BTI. It was further demonstrated that a wealth of information about defect properties can be obtained from deeply-scaled devices, and that this information can allow interpretation of variability issues of future deeply downscaled CMOS devices. This theme was complemented by showing the most promising technological solutions to alleviate both PBTI and NBTI.

#### References

- 1. J. H. Stathis and S. Zafar, Microelectronics Reliab. 46, 270 (2006).

- 2. V. Huard, M. Denais, C. Parthasarathy, *Microelectronics Reliab*.46, 1 (2006).

- 3. D. K. Schroder, Microelectronics Reliab. 47, 841 (2007).

- 4. B. Kaczer, R. Degraeve, V. Arkhipov, N. Collaert, G. Groeseneken, M. Goodwin, as discussed at SISC, San Diego, CA, 2006.

- B. Kaczer, V. Arkhipov, R. Degraeve, N. Collaert, G. Groeseneken, and M. Goodwin, Proc. Int. Reliab. Phys. Symp., 381 (2005); Appl. Phys. Lett. 86, 143506 (2005).

- T. Grasser, B. Kaczer, P. Hehenberger, W. Goes, R. O'Connor, H. Reisinger, W. Gustin, and C. Schlunder, *Int. Electron Devices Meeting Tech. Dig.*, 801 (2007).

- 7. A. Kerber, K. Maitra, A. Majumdar, M. Hargrove, R. J. Carter, and E. A. Cartier, *IEEE T. Electron Dev.***55**, 3175 (2008).

- 8. M. A. Alam, Int. Electron Devices Meeting Tech. Dig., 345 (2003).

- S. V. Kumar, C. H. Kim, S. S. Sapatnekar, IEEE/ACM International Conference on Computer-Aided Design ICCAD'06, 493 (2006).

- T. Grasser, B. Kaczer, W. Goes, H. Reisinger, Th. Aichinger, Ph. Hehenberger, P.-J. Wagner, F. Schanovsky, J. Franco, Ph. Roussel, and M. Nelhiebel, to be presented at *Int. Electron Devices Meeting* 2010.

- 11. T. Grasser, B. Kaczer, and W. Goes, Proc. Int. Reliab. Phys. Symp, 28 (2008).

- B. Kaczer, T. Grasser, J. Martin-Martinez, E. Simoen, M. Aoulaiche, Ph. J. Roussel, and G. Groeseneken, Proc. Int. Rel. Phys. Symp., 55, 2009.

- T. Grasser, B. Kaczer, W. Goes, Th. Aichinger, Ph. Hehenberger, and M. Nelhiebel, "A Two-Stage Model for Negative Bias Temperature Instability", *Proc. Int. Reliab. Phys. Symp.*, 2009.

- T. Grasser, H. Reisinger, P.-J. Wagner, F. Schanovsky, W. Goes, and B. Kaczer, *Proc. Int. Rel. Phys. Symp.*, 16 (2010).

- 15. S. Rangan, N. Mielke, and E. C. C. Yeh, *Int. Electron Devices Meeting Tech. Digest*, 341 (2003).

- 16. G. Chen, K. Y. Chuah, M. F. Li, D. S. H. Chan, C. H. Ang, J. Z. Zheng, Y. Jin, and D. L. Kwong, Proc. Int. Reliab. Phys. Symp., 196 (2003).

- R. Fernández, B. Kaczer, A. Nackaerts, S. Demuynck, R. Rodríguez, M. Nafría, G. Groeseneken, *Int. Electron Devices Meeting Tech. Dig.*. 1 (2006).

- H. Reisinger, O. Blank, W. Heinrigs, A. Mühlhoff, W. Gustin, and C. Schlünder, *Proc. Int. Reliab. Phys. Symp.*, 448 (2006).

- B. Kaczer, T. Grasser, Ph. J. Rousse, J. Martin-Martinez, R. O'Connor, B. J. O'Sullivan, G. Groeseneken, *Proc. Int. Reliab. Phys. Symp.*, 20 (2008).

- 20. E. Milotti, arXiv:physics/0204033v1.

- 21. H. Reisinger, T. Grasser, W. Gustin, and C. Schlünder, Proc. Int. Reliab. Phys. Symp., 1 (2010).

- 22. V. Huard, C. Parthasarathy, C. Guerin, T. Valentin, E. Pion, M. Mammasse, N. Planes and L. Camus, *Proc. Int. Reliab. Phys. Symp*, 289 (2008).

- T. Grasser, H. Reisinger, W. Goes, Th. Aichinger, Ph. Hehenberger, P.-J. Wagner, M. Nelhiebel, J. Franco, and B. Kaczer, *Int. Electron Devices Meeting Tech. Dig.*, 729 (2009).

- 24. M. Toledano-Luque, B. Kaczer, Ph. Roussel, M.J. Cho, T. Grasser, and G. Groeseneken, presented at WoDiM 2010.

- 25. M. J. Uren, M. J. Kirton, and S. Collins, Phys. Rev. B37, 8346 (1988).

- 26. M. J. Kirton and M. J. Uren, Adv. Phys. 38, 367 (1989).

- 27. A. Palma et al., Phys. Rev. B56, 9565 (1997).

- B. Kaczer, T. Grasser, Ph. J. Roussel, J. Franco, R. Degraeve, L.-A. Ragnarsson, E. Simoen, G. Groeseneken, H. Reisinger, *Proc. Int. Reliab. Phys. Symp.*, 26 (2010).

- 29. A. Asenov, R. Balasubramaniam, A. R. Brown, J. H. Davies, *IEEE T. Electron Dev.***50**, 839 (2003).

- A. Ghetti, C. M. Compagnoni, A. S. Spinelli, A. Visconti, *IEEE T. Electron Dev.*56, 1746 (2009).

- 31. B. Kaczer, Ph. J. Roussel, T. Grasser, and G. Groeseneken, *IEEE Electron Dev. Lett.***31**, 411 (2010).

- B. Kaczer, A. Veloso, M. Aoulaiche, and G. Groeseneken, Microelectronic Engineering, 86(7-9), 1894 (2009).

- 33. D. Liu and J. Robertson, Appl. Phys. Lett. 94, 042904 (2009).

- 34. N. Collaert, P. Verheyen, K. De Meyer, R. Loo and M. Caymax, *IEEE T. Nanotech*1, 190 (2002).

- 35. J. Franco, B. Kaczer, M. Cho, G. Eneman, G. Groeseneken, and T. Grasser, Proc. Int. Rel. Phys. Symp., 1082 (2010).

- 36. J. Franco, B. Kaczer, G. Eneman, J. Mitard, A. Stesmans, V. Afanas'ev, T. Kauerauf, Ph. J. Roussel, M. Toledano-Luque, M. Cho, R. Degraeve, T. Grasser, L.-Å. Ragnarsson, L. Witters, J. Tseng, S. Takeoka, W.-E. Wang, T.Y. Hoffmann, and G. Groeseneken, *Int. Electron Devices Meeting* 2010.

## **Chapter 3 Charge Trapping Phenomena in MOSFETS: From Noise to Bias Temperature Instability**

#### Gilson Wirth and Roberto da Silva

**Abstract** Charge trapping phenomena is known to be a major reliability concern in modern MOSFETS, dominating low-frequency noise behavior and playing a significant role in aging effects such as Bias Temperature Instability (BTI). In this chapter we address this reliability issue.

We start by discussing MOSFET low-frequency (LF) noise, which is known to be dominated by charge capture and emission by defects (traps) close to the semiconductor-dielectric interface. Standard (LF) noise models used today (e.g. BSIM and PSP) do not properly model noise behavior under large signal excitation. A circuit level modeling and simulation approach, valid at both DC and large signal (AC) biasing, is presented.

The role of charge trapping and de-trapping in BTI (Bias Temperature Instability) is also discussed and modeled.

Mutual relation between the different reliability phenomena (LF noise, BTI and RDF) is also studied. For instance, random dopant fluctuations (RDF) may exacerbate the impact of BTI and LF noise on circuit performance.

#### 1 Introduction

The major goal of this chapter is to compile and critically discuss recent work performed by the authors on modeling of charge trapping and de-trapping phenomena in nanometer scale CMOS devices [1-6, 16-18]. The role of charge trapping and de-trapping in both low-frequency noise and bias temperature instability (BTI) is discussed.

G. Wirth (🖂)

Electrical Engineering Department, Universidade Federal do Rio Grande do Sul (UFRGS), Porto Alegre, Rio Grande do Sul, Brazil e-mail: wirth@ece.ufrgs.br

R. da Silva Physics Institute, UFRGS, Porto Alegre, Brazil

<sup>©</sup> Springer Science+Business Media New York 2015 R. Reis et al. (eds.), *Circuit Design for Reliability*, DOI 10.1007/978-1-4614-4078-9\_3

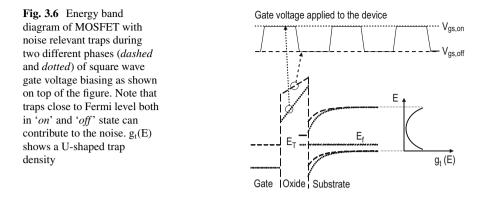

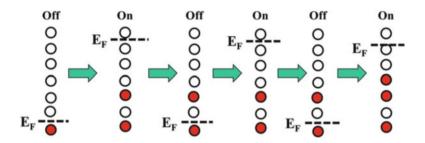

**Fig. 3.2** If a transistor is abruptly turned on, the Fermi level abruptly changes and trap occupation probability follows the Fermi level ( $E_F$ ) change. Charge trapping/de-trapping is not an instantaneous event. It is governed by characteristic time constants, and the trap occupation reflects the new Fermi level after an elapsed time. This figure depicts the situation for electron trapping in the channel of a NMOS transistor

Charge trapping and de-trapping at localized states (charge traps) at the interface or in the gate dielectric is a significant reliability issue for CMOS applications. It is known to be a source of low-frequency noise, besides playing a role in Bias Temperature Instability (BTI).

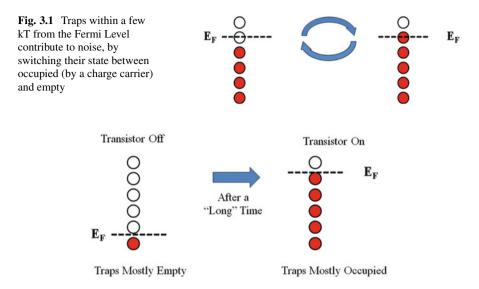

Traps that contribute to noise are the ones that keep switching their state between occupied and empty, as depicted in Fig. 3.1. These are the traps with occupation probability close to 50 %, which means that their capture and emission times are similar.

Traps that contribute to BTI are the ones that have a high probability to stay occupied after a charge trapping event, as depicted in Fig. 3.2. These are the traps with occupation probability close to 100 %, which means that their capture time is much shorter than the emission time.

Figure 3.3 depicts the mechanisms leading to BTI and low-frequency noise.

If a constant bias is applied to a Metal–Insulator–Semiconductor system, only the localized states (traps) with energy close to the Fermi level show significant activity, i.e., change their states between occupied and empty, by capture and subsequent emission of charge carriers from the channel region. This may be considered a steady state condition, where the *occupation probability* of a trap is time independent, i.e., a constant that does not change with time. This mechanism is known to originate low-frequency noise.

However, if the bias point changes abruptly, as is common in e.g. digital CMOS applications, the trap occupation probability abruptly changes. For instance, if the

**Fig. 3.3** (*Left hand side*) Traps that contribute to NBTI are the ones that stay occupied after an capture event occurs. This leads to a degradation of transistor on current over time. (*Right hand side*) Traps that contribute to noise are the ones that keep switching their state over time, exchanging charge carriers with the channel inversion layer. This leads to Random Telegraph Noise in the device current

gate voltage abruptly changes the Fermi level in such a way that trap occupation probability is increased, the rate at which charge carries are captured abruptly becomes larger than the rate at which carriers are emitted, and the number of trapped charge increases over time. Traps change their occupation state according to their characteristic time constant, meaning that the number of trapped charge does not instantaneously reflect the new occupation probability. The faster traps (with shorter capture time constants) become filled first, while the slowest traps take longer to become filled.

Each trap that becomes occupied degrades the channel conductivity, decreasing the device current. For nanometer scale devices, this current decrease is seen to occur in discrete steps, each step being related to the capture of a single channel carrier (in large area device it becomes hard to clearly identify the discrete steps). Since the dynamics of this occupation depends on the bias point and temperature, it may lead to bias temperature instability (BTI).

The first sections of this chapter cover the modeling of low-frequency noise, while the last section covers the modeling of BTI.

#### 2 Charge Trapping Events as a Source of Noise

In nanometer scale MOSFETs the alternate capture and emission of carriers at individual defect sites (traps) generates discrete fluctuations in the device conductance. These fluctuations, also called Random Telegraph Noise (RTN), are the main source of Low-Frequency Noise in deep-submicron MOSFETs. This work covers measurement, analytical analysis and Monte Carlo simulation of these fluctuations.

The low-frequency noise model is based on device physics parameters which cause statistical variation in low-frequency noise behavior of individual devices. It includes detailed consideration of statistical effects for distribution of number of traps per device, the trap energy distribution, trap location and its device bias dependent noise contributions [1, 2]. Microscopic discrete quantities are used in model derivation, and analytical equations for the statistical parameters are provided.

In many practical applications the MOS device is not biased at steady state, but periodically switched. This operation regime is called cyclo-stationary excitation. The modeling approach adopted allows analysis of noise both at steady state operation as well as under cyclo-stationary excitation. Noise behavior under cyclostationary excitation is the main focus of this work.

First the autocorrelation of the RTN signal is calculated, and then the Wiener– Khinchin formula applied, leading to an analytical formulation for the RTN spectrum due to a single trap. After the evaluation of the power spectrum due to a single trap, the noise behavior resulting from the combined effect of all traps found in a device is derived. The modeling approach is valid for steady state as well as for any periodic excitation signal, and allows the derivation of relevant statistical parameters. Square wave excitation is used as a case study, to explore noise behavior in detail.

It is shown that since RTN-amplitude depends on the bias point strong variations of noise performance may appear not only between devices, but also for a single device operated under different bias conditions.

If the trap energy distribution in the band-gap is a convex curve (e.g. "U"shaped), the model here presented yields a reduction in LF-noise under cyclostationary excitation when the device is biased between strong and weak inversion or even slight accumulation, which is in agreement to our experimental results [3, 7], and experimental results found in the literature [8–11]. However, while the average noise power is seen to decrease, the variability (normalized standard deviation) of noise power increases, as shown by the mathematical derivation, and experimental observations provided here.

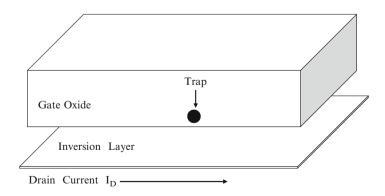

#### **3** Power Spectrum of the RTN Noise due to a Single Trap

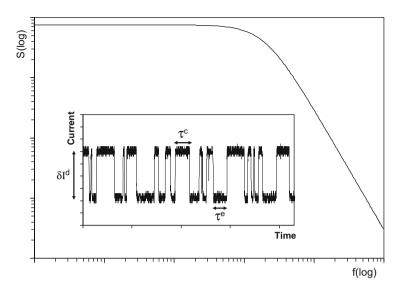

The origin of RTN noise is the alternate capture and emission of charge carriers at discrete trap levels near the Si–SiO<sub>2</sub> interface. Figure 3.4 depicts the cross section of an n-channel MOSFET through the location of the interface trap. The influence of the traps on the electrical current flowing through the channel is twofold. On the one hand, the occupation of a trap changes the number of free carriers in the inversion layer. On the other hand, a charged trap state has an influence on the local mobility near to its position due to Coulomb scattering. If the MOSFET biasing is kept constant, a stationary RTN is observed at the terminals of the device as a discrete fluctuation in electrical current,  $\delta I_d$  being the amplitude of the current fluctuation, as shown in the inset of Fig. 3.5. The average high current time corresponds to the electron capture time constant ( $\tau_e$ ).

The power spectrum of a RTN fluctuation can be evaluated by calculating the auto-covariance of the signal, and then applying the Wiener–Khinchin formula [12]. The power spectrum is then the Fourier transform of the auto-covariance, and is a Lorentzian, as given by Eq. (3.1) and depicted in Fig. 3.5.

$$S(\omega) = \frac{\delta^2}{\pi} \cdot \frac{\beta}{(1+\beta)^2} \cdot \frac{1}{\omega_0} \cdot \frac{1}{1+(\omega/\omega_0)^2}$$

(3.1)

where  $\delta$  is the RTN amplitude,  $\omega_0$  is the angular corner frequency and  $\beta$  is equal to  $\tau_c/\tau_e$ . The amplitude of the RTN fluctuation induced by a trap depends on trap position along the channel. It may be exacerbated by factors such as random dopant fluctuations (RDF). For nanometer scale channel lengths (L), traps near the source end of the channel can cause significant mobility fluctuations and surface potential

**Fig. 3.4** Schematic cross section of the inversion layer of a MOS transistor through the location of an interface trap. If the trap is electrically charged the inversion layer is disturbed by the trap, affecting the drain current  $I_D$ . The trap not only affects the number of free carriers in the inversion layer but is also a source of electrical charge carrier scattering

**Fig. 3.5** Time and frequency domain representation of a stationary random telegraph noise (RTN). In frequency domain, the power spectrum of a RTN is a Lorentzian. In time domain discrete fluctuations are observed in the drain current, where  $\tau_c$  is the average time in the high current state, which corresponds to the state where the trap is electrically neutral (empty).  $\tau_e$  is the average time in the low current state, which corresponds to the state where the trap is electrically charged.  $\delta I_d$  is the amplitude of the current fluctuation

fluctuations, hindering electrical current flow and enhancing RTN amplitude  $(\delta)$ . A trap positioned near the source junction may be able to create a repulsive Coulomb blockade well surrounding the trap, hindering trap injection from the source into the channel. Thus, a significant mobility fluctuation will be added to carrier number fluctuation for carrier electrons trapped near the source side [17]. Another parameter that may impact RTN amplitude is trap position into the dielectric.

Equation (3.1) assumes that the capture and emission time constants ( $\tau_c$  and  $\tau_e$ ) are time independent, constant values. This is true for constant (time invariant) biasing. However, under cyclo-stationary excitation the applied bias voltage is a periodic function of time, and  $\tau_c(t)$  and  $\tau_e(t)$  become periodic functions of time. Cyclo-stationary excitation is depicted in Fig. 3.6.

In order to derive the power spectrum under cyclo-stationary excitation, we did follow the methodology originally proposed by Machlup [12] for stationary RTN. A RTN is considered to be a purely random signal, which may be in one of two states, called 1 and 0. If the signal is in state 1, the probability of making a transition to 0 in a short time dt is assumed to be  $dt/\tau_c(t)$ . If the signal is in state 0, the probability of making a transition to 1 is assumed to be  $dt/\tau_e(t)$ . In this form, the state 1 is related to the empty trap, i.e., high current state in Fig. 3.5, while the state 0 is related to the occupied trap, i.e., low current state.

In order to derive the low frequency noise spectrum of cyclo-stationary RTN, we first calculate the autocorrelation of the RTN, and then apply the Wiener–Khinchin formula to obtain the spectrum. Let the RTN signal be x(t).

The autocorrelation is then given by

$$A(s) = \langle x(t) \cdot x(t+s) \rangle_{average} = P(x(t) = 1) \cdot P_{11}(s)$$

(3.2)

where  $P_{11}(s)$  is the probability of an even number of transitions in time *s*, given we start in state 1. P(x(t) = 1), the probability of being in state 1 at time *t*, is given by

$$P(x(t) = 1) = \frac{\frac{1}{T} \int_{0}^{T} \frac{1}{\tau_{e}(t)} dt}{\frac{1}{T} \int_{0}^{T} \frac{1}{\tau_{e}(t)} dt + \frac{1}{T} \int_{0}^{T} \frac{1}{\tau_{c}(t)} dt} = \frac{\langle \frac{1}{\tau_{e}(t)} \rangle}{\langle \frac{1}{\tau_{e}(t)} \rangle + \langle \frac{1}{\tau_{c}(t)} \rangle}$$

(3.3)

where *T* is the period of the cyclo-stationary excitation, and symbol  $\langle \bullet \rangle$  is an abbreviation for (1/T)  $\int_0^{T} dt$ , the time average value.

The autocorrelation can then be calculated as

$$A(s) = \frac{\langle \frac{1}{\tau_{e}(t)} \rangle}{\langle \frac{1}{\tau_{e}(t)} \rangle + \langle \frac{1}{\tau_{e}(t)} \rangle}.$$

$$\cdot \left( 1 + \int_{0}^{s} e^{\int_{0}^{x} \left( \langle \frac{1}{\tau_{e}(y)} \rangle + \langle \frac{1}{\tau_{e}(y)} \rangle \right) dy}_{-\left( \langle \frac{1}{\tau_{e}(y)} \rangle + \langle \frac{1}{\tau_{e}(y)} \rangle \right) dy}_{-\left( \langle \frac{1}{\tau_{e}(y)} \rangle + \langle \frac{1}{\tau_{e}(y)} \rangle \right) dy}$$

(3.4)

This formulation for the autocorrelation is a generalization of the Machlup formula, and is valid for any kind of periodic excitation and any frequency. If  $\tau_c$  and  $\tau_e$  become constant (independent of time), Eq. (3.4) becomes equal to (7) in [12].

# 4 Approximation for Excitation Frequencies Higher than the Noise Frequency

The case of interest for most practical applications is for the noise at frequencies below the frequency of the cyclo-stationary excitation signal.

If the probability of a trap to switch state during one period *T* of the cyclostationary excitation signal is very small, a simplification may be done in the calculation of the autocorrelation. This case corresponds to the limit where  $\tau_c(t)$ and  $\tau_e(t)$  are much larger than the period *T*, leading to small transition probabilities  $T/\tau_c(t)$  and  $T/\tau_e(t)$ .

In this case we can write, without loss of generality, that s = nT, where *n* is a positive integer (1, 2, 3, ...). In this situation we have

$$\int_{0}^{s} \left(\frac{1}{\tau_{c}(y)} + \frac{1}{\tau_{c}(y)}\right) dy = \sum_{i=0}^{n-1} \int_{iT}^{(i+1)T} \frac{1}{\tau_{c}(y)} dy + \sum_{i=0}^{n-1} \int_{iT}^{(i+1)T} \frac{1}{\tau_{c}(y)} dy =$$

$$= nT \left( \langle \frac{1}{\tau_{c}(t)} \rangle + \langle \frac{1}{\tau_{c}(t)} \rangle \right)$$

(3.5)

leading to

$$A(s) = \frac{\langle \frac{1}{\tau_{e}(t)} \rangle}{\langle \frac{1}{\tau_{e}(t)} \rangle + \langle \frac{1}{\tau_{c}(t)} \rangle} \left[ 1 - \frac{T \langle \frac{1}{\tau_{e}(t)} \rangle}{e^{T} \left( \langle \frac{1}{\tau_{e}(t)} \rangle + \langle \frac{1}{\tau_{c}(t)} \rangle \right)_{-1}} \right] e^{-s \left( \langle \frac{1}{\tau_{e}(t)} \rangle + \langle \frac{1}{\tau_{c}(t)} \rangle \right)} + \frac{\langle \frac{1}{\tau_{e}(t)} \rangle}{e^{T} \left( \langle \frac{1}{\tau_{e}(t)} \rangle + \langle \frac{1}{\tau_{c}(t)} \rangle \right)_{-1}} \right] e^{-s \left( \langle \frac{1}{\tau_{e}(t)} \rangle + \langle \frac{1}{\tau_{c}(t)} \rangle \right)} + (3.6)$$

For small values of T a Taylor expansion may be employed, leading to

$$A(s) = \frac{\langle \frac{1}{\tau_{e}(t)} \rangle}{\langle \frac{1}{\tau_{e}(t)} \rangle + \langle \frac{1}{\tau_{c}(t)} \rangle} \left[ 1 - \frac{\langle \frac{1}{\tau_{e}(t)} \rangle}{\langle \frac{1}{\tau_{e}(t)} \rangle + \langle \frac{1}{\tau_{e}(t)} \rangle} \right] e^{-s \left( \langle \frac{1}{\tau_{e}(t)} \rangle + \langle \frac{1}{\tau_{e}(t)} \rangle \right)} \dots + + \frac{\langle \frac{1}{\tau_{e}(t)} \rangle^{2}}{\left( \langle \frac{1}{\tau_{e}(t)} \rangle + \langle \frac{1}{\tau_{e}(t)} \rangle \right)^{2}}$$

(3.7)

This means that, if  $\tau_c(t)$  and  $\tau_e(t)$  are much larger than the period *T* of the excitation signal, the values of  $1/\tau_c(t)$  and  $1/\tau_e(t)$  in the integrals of (3.4) are equivalent to their time averages  $<1/\tau_c(t)>$  and  $<1/\tau_e(t)>$ .

The power spectrum  $S_i(\omega)$ , due to a single trap (the i-th trap), is the calculated as the Fourier transform of the autocorrelation, leading to

$$S_i(\omega) = \frac{1}{2\pi} \int_{-\infty}^{\infty} -A(s)e^{i\omega s} ds$$

(3.8)

which is evaluated as being

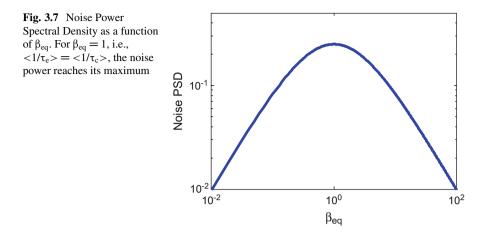

$$S_i(\omega) = \frac{\delta_i^2}{\pi} \cdot \frac{\beta_{eq}}{\left(1 + \beta_{eq}\right)^2} \cdot \frac{1}{\omega_i} \cdot \frac{1}{1 + \left(\omega/\omega_i\right)^2}$$

(3.9)

Here  $\delta_i$  determines the trap's voltage amplitude and  $\omega_i$  the angular frequency, and

$$\beta_{eq} = \langle 1/\tau_e(t) \rangle / \langle 1/\tau_c(t) \rangle$$

(3.10)

Figure 3.7 depicts the behavior of noise power as a function of  $\beta_{eq}$ .

The cyclo-stationary noise spectrum is still Lorentzian, with angular corner frequency  $\omega_i$  given by

$$\omega_{i} = \langle \frac{1}{\tau_{c}(t)} \rangle + \langle \frac{1}{\tau_{e}(t)} \rangle$$

(3.11)

This takes us to the conclusion that making a RTN signal cyclo-stationary leads to a Lorentzian spectrum with corner frequency equal to the sum of the inverse time average values of the capture and emission times. Please note that for stationary RTN the corner frequency is equal to the sum of the inverse values of the constant capture and emission times. Please refer to equation 9 in [12].

The result for this limit is valid for any kind of periodic excitation. This is the limit studied in [11, 13]. However, for this limit, we obtain the same result in a much simpler derivation than in [11, 13], and without making any further assumption or simplification. The single assumption is that the transition probabilities  $dt/\tau_e(t)$  and  $dt/\tau_c(t)$  are much smaller than the excitation period *T*.

Equations (3.11) and (3.9) are a generalization of the Machlup formulation for cyclo-stationary RTN with excitation frequency higher than the noise frequency.

The Machlup equations for the auto-correlation and power spectrum are recovered if we consider  $<1/\tau_e(t)>=1/\tau_e$  and  $<1/\tau_c(t)>=1/\tau_c$ , i.e., constant, not time dependent values.

## 5 Average Power Spectrum of the RTN Noise due to the Ensemble of Traps

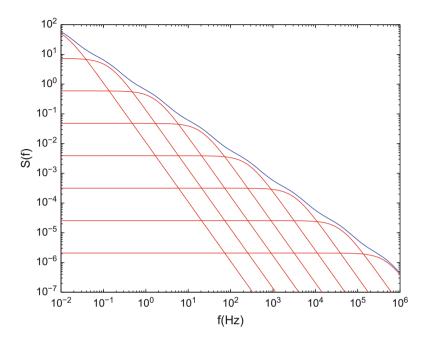

The noise behavior of a device results from the combined effect of all traps found in the device. The noise power spectrum may then be written as the summation of the contribution of each one of the  $N_{tr}$  traps found in the device. The observation that traps are Poisson distributed results in an average noise spectral density given by

$$\langle S \rangle = \sum_{N_{tr}=0}^{\infty} \sum_{i=1}^{N_{tr}} \langle S_i \rangle \frac{e^{-N} N_{tr}^N}{N_{tr}!} = N \langle S_i \rangle$$

(3.12)

Here  $\langle S_i \rangle$  is the average noise contribution of a trap,  $N_{tr}$  is actual number of traps in a particular device, and N is average number of traps in an ensemble of devices.

As depicted in Fig. 3.8, if the corner frequencies of the Lorentzians corresponding to power spectral density (PSD) of different traps are equally spaced on a log scale, the summation of the power spectrum due to all traps leads to 1/f noise. In time domain, this corresponds to the situation where the charge trap characteristic time constants are uniformly distributed on a log scale.

The equations above are valid for any waveform of the periodic excitation signal. In order to explore the noise behavior in detail and allow comparison to experimental results, a case of particular interest for practical applications will be studied. It is square wave excitation.

#### 6 Square Wave Excitation

Square wave excitation is chosen as case study, because of its interest in practical applications and because of the availability of experimental data. Comparison of model results to relevant experimental data is performed in the last section of this work.

Under square wave excitation, the bias voltage abruptly alternates between two states, called *on* and *off*. Please note that the state names *on* and *off* do not imply that the device has necessarily to be periodically turned on and off. The names refer to two distinct states, with different gate bias. With periodically changing gate bias, the Fermi level becomes a periodic function of time  $E_F(t)$ . This implies that the Fermi level alternates between two levels:  $E_{on}$  being the Fermi level during the *on* state and  $E_{off}$  being the Fermi level during the *off* state. The duty cycle  $\alpha$  is the fraction

Fig. 3.8 If the corner frequencies of the Lorentzians (*red lines*) corresponding to different traps are equally spaced on a log scale, the summation of the power spectrum due to all traps leads to 1/f noise (*blue line*)

of the period T in which the device is in the *on* state. The capture and emission time constants of a trap are affected by the Fermi level.

For square wave cyclo-stationary excitation with duty cycle  $\alpha$ , the time averaged capture and emission time constants may be written as

$$<1/\tau_c> = \left(\alpha/\tau_{c,on} + (1-\alpha)/\tau_{c,off}\right)$$

(3.13)

$$\langle 1/\tau_e \rangle = \left( \alpha/\tau_{e,on} + (1-\alpha)/\tau_{e,off} \right)$$

(3.14)

$$\beta_{eq} = \psi \left( E_{on}, E_{off}, \alpha \right) e^{2E_t/k_B T}$$

(3.15)

with

$$\psi(E_{on}, E_{off}, \alpha) = \frac{\alpha e^{-E_{on}/k_B T} + (1 - \alpha) e^{-E_{off}/k_B T}}{\alpha e^{E_{on}/k_B T} + (1 - \alpha) e^{E_{off}/k_B T}}$$

(3.16)

Assuming statistical independence of the random variables, the average noise of a transistor  $\langle S \rangle$  is then given by:

$$\langle S \rangle = \frac{N_{dec} \langle \delta^{2} \rangle}{\pi W L \omega} \int_{E_{v}}^{E_{c}} \frac{\psi e^{2E_{t}/k_{B}T}}{\left(1 + \psi e^{2E_{t}/k_{B}T}\right)^{2}} g\left(E_{t}\right) dE_{t}$$

(3.17)

where *W* is the channel width and *L* the channel length of the transistor, and  $N_{dec}$  is the trap density per unit area and frequency decade. Please see (3.1) for a detailed explanation of these parameters. This equation again looks similar to the DC noise behavior (see [1]). In case the cyclo-stationary period *T* is short compared to the trap's time constants their time averages and the trap numbers close to the two Fermi levels determine the noise level. At frequencies significantly higher than the excitation frequency the noise is given by DC theory.

Equation (3.17) above clearly relates the noise reduction to the distribution of traps over energy. From the above equation, it follows that if the distribution of traps in energy over the bandgap is uniform,  $\langle S \rangle$  is expected to remain approximately constant under cyclo-stationary excitation. In this case, the peak of the noise contribution of a trap always probes the same trap density, since the trap density around to the Fermi level is always the same. Note that for the peak of the noise contribution of a trap occurs for  $E_T = E_F$ . If the trap density is uniform over the bandgap,  $g(E_t)$  corresponding to the peak of  $\beta_{eq}$  is always the same.

Monte Carlo (MC) simulations are performed in time domain. The RTN of each trap is evaluated, and then the power spectral density is calculated. The Monte Carlo simulation show very good agreement to the analytical results, as well as to our experimental results, as shown in the last section of this work.

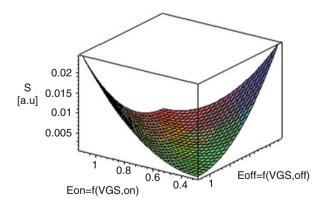

In Fig. 3.9 the results of Eq. 3.17 show noise reduction as a function of the Fermi levels in the 'on' and 'off' state at frequencies lower than the excitation period.

Fig. 3.9 Noise reduction as a function of the Fermi level in the 'on' and 'off' states. The noise power *S* is evaluated according to Eq. (3.17), considering the U-shaped trap density given by Eq. (3.18). The same parameter a = 11 is used in all figures and evaluations performed in this work. Note that the noise reduction is larger if the biasing levels are symmetrical in relation to the center of the U-shaped trap density

It can be seen that a higher noise reduction can be expected if the biasing levels are symmetrical in relation to the center of the U-shaped trap density. In this case, the traps that contribute most to the noise power are the ones close to the center of the bandgap, where the density is lowest.

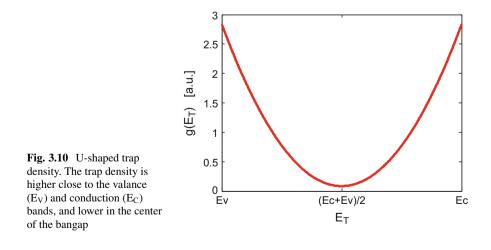

In good agreement to the works in [11, 13], the trap energy distribution  $g(E_t)$  is key for explaining experimentally observed findings. A parabolic U-shape trap density function is assumed here:

$$g(E_t) = aE_t^2 - a(E_c - E_v)E_t + k$$

(3.18)

where *a* is a fitting parameter. The integral of  $g(E_t)$  from  $E_v$  to  $E_c$  is normalized to one with

$$k = \frac{1}{E_c - E_v} \left( \frac{a}{6} \left( E_c^3 - E_v^3 \right) + \frac{a}{2} \left( E_c^2 E_v - E_v^2 E_c \right) + 1 \right)$$

(3.19)

Figure 3.10 depicts a U-shape trap density.

# 7 Variability in the Power Spectrum of the RTN Noise due to the Ensemble of Traps

Since the microscopic approach maintains the statistically relevant parameters, the model proposed here also allows the modeling of the statistically relevant parameters. As derived in [2], the normalized standard deviation of noise performance under constant biasing is

$$\frac{\sigma_{\rm np}}{\langle {\rm np}_{\rm BW} \rangle} = \frac{2}{\pi} \frac{1}{\sqrt{\rm N_{dec}WL}} \sqrt{\frac{\langle A^4 \rangle}{\langle A^2 \rangle^2}} \frac{\rm b}{\left(\frac{\rm f_H}{\rm f_L}\right)^{\rm c}}$$

(3.20)

Here  $f_H$  and  $f_L$  are the lower and upper boundaries of the bandwidth of interest in a given circuit design, respectively, and b and c are constants, with b = 0.74 and c = 0.05 [2].

A similar formulation can also be derived for cyclo-stationary operation. The standard deviation of noise power is given by:

$$\sigma_S = \sqrt{\langle S^2 \rangle - \langle S \rangle^2} \tag{3.21}$$

Hence, in addition to  $\langle S \rangle^2$  based on Eq. (3.17), it is necessary to evaluate  $\langle S^2 \rangle$ . Again following a similar approach to [12], the resulting normalized standard deviation under square wave excitation is given by:

$$\frac{\sigma_{S}}{\langle S \rangle} = \frac{\sqrt{\frac{\langle \delta^{4} \rangle}{\langle \delta^{2} \rangle^{2}}}}{\sqrt{N_{dec}WL}} \frac{\left(\int_{E_{v}}^{E_{c}} \frac{\psi^{2} e^{4E_{t}/k_{B}T}}{\left(1 + \psi e^{2E_{t}/k_{B}T}\right)^{4}} g\left(E_{t}\right) dE_{t}\right)^{\frac{1}{2}}}{\int_{E_{v}}^{E_{c}} \frac{\psi e^{2E_{t}/k_{B}T}}{\left(1 + \psi e^{2E_{t}/k_{B}T}\right)^{2}} g\left(E_{t}\right) dE_{t}}$$

(3.22)

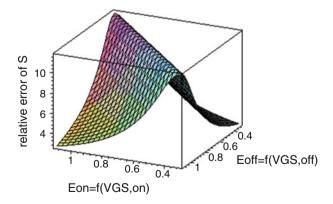

Figure 3.11 shows the normalized standard deviation as a function of the Fermi levels in the 'on' and 'off' state for the U-shaped trap density given by (3.18). The normalized standard deviation becomes higher when the traps that contribute most to noise are the ones close to the center of the band gap. In this case the normalized standard deviation increases even though the average noise power decreases.

**Fig. 3.11** Normalized standard deviation of noise performance as given by Eq. (3.22). An increase in normalized standard deviation is seen under cyclo-stationary excitation, especially for conditions where the average cyclo-stationary noise reduction is high

#### 8 Experimental Results

The low frequency noise was experimentally investigated using short and long channel NMOS devices from a 45 nm technology. Technology details are described in [15]. The DC and large signal noise was measured using a semi-automatic prober setup using a BTA noise system, and the results are described in [3]. A square wave with 50 % duty cycle ( $\alpha = 0.5$ ) was applied to the gate using a waveform generator HP33120A for measuring cyclo-stationary noise. Two types of cyclo-stationary measurements were performed, one with V<sub>GS,OFF</sub> = 0 V and V<sub>GS,ON</sub> = V<sub>T</sub>, and the other with V<sub>GS,OFF</sub> = V<sub>T</sub> and V<sub>GS,ON</sub> = V<sub>DD</sub>. Note, that the effect of modulation for a signal modulated by a square wave with 50 % duty cycle is a reduction of noise power (in baseband) by a factor of four.

After the standard modulation theory, for square wave excitation, switching operation can be represented by the multiplication of the noise with a square-wave signal with 50 % duty cycle, m(t), as follows [19]:

m (t) =

$$\frac{1}{2} + \frac{2}{\pi} \sin \omega_{sw} t + \frac{2}{3\pi} \sin 3\omega_{sw} t + \frac{2}{5\pi} \sin 5\omega_{sw} t + \dots$$

In frequency domain this corresponds to a convolution of the noise PSD with a spectrum with delta functions at dc,  $\omega_{sw}$ ,  $3\omega_{sw}$ ,  $5\omega_{sw}$ , and so forth. The dc-term determines the resulting noise power in baseband, which is  $(1/2)^2$  or -6 dB, if compared to the original noise power.

However, the measurements results did show a much larger noise reduction. The noise reduction was larger than a factor of ten, and the mean value of the LF-noise under DC conditions was seen to follow 1/f behavior, but with deviations at some frequencies, showing Lorentzian components [3]. For cyclo-stationary conditions these deviations were more pronounced in agreement to our theory. Also in good agreement to our theory, the noise reduction factor was found to be almost constant if only measured results below the excitation frequency are considered.

To compare theory and experiment, the average number of traps for all possible energetic levels in the bandgap were extracted from average noise behavior. The model comparisons are based on the total number of traps and the assumption of a U-shaped trap density with a = 11 (see Eq. 3.18).

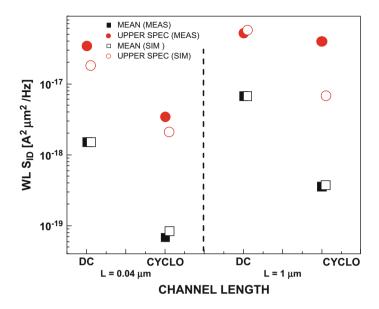

Experimental results did show that whereas the average LF noise is decreasing under cyclo-stationary conditions, the normalized standard deviation of noise power increases. As shown in Fig. 3.12, this again is in good agreement to the model presented here. In Fig. 3.12, the model values for mean and upper spec in cyclo-stationary conditions are given by Eqs. 3.17 and 3.22, respectively. Here the upper boundary for the DC noise is evaluated using the model presented in [1].

Fig. 3.12 Area normalized average and  $+3\sigma$  worst case noise behavior under DC and CS conditions. All data are taken at 10 Hz noise frequency. *Open symbols* are data from simulation and *closed symbols* are measured data reported in [3]

## 9 The Charge Trapping Component of Bias Temperature Instability

Above we discussed the low-frequency noise originated from trapping and detrapping at localized states (charge traps) at the interface or in the gate dielectric of transistors. Here we discuss the role of charge trapping in Bias Temperature Instability (BTI). It is widely accepted that charge trapping plays a role in the threshold voltage shifts ( $\Delta V_T$ ) produced by Bias Temperature stress. It was reported that a significant fraction of the threshold voltage shift is recovered spontaneously once the Bias Temperature stress is removed [20–22]. Although first observed decades ago, the phenomenon still remains controversial in both experimental and theoretical terms.

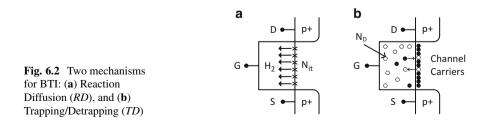

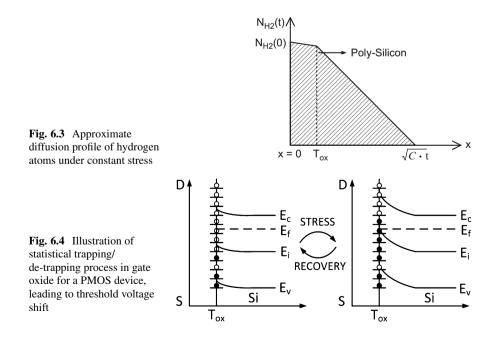

There is a vast literature on Negative Bias Temperature Instability (NBTI) in PMOSFETs, where most models are based on reaction diffusion. Reaction diffusion models involve breaking of Hydrogen-Silicon bonds at the Silicon-Gate Dielectric interface, related to the trapping of inversion layer holes, with the release and diffusion of a hydrogenic species. Recovery (relaxation) is assumed to occur with re-bonding of the Hydrogen-Silicon bonds, i.e., anneal out the interface traps [20]. Although reaction diffusion models have been very useful and successful, some aspects of NBTI are difficult to be fully explained in a reaction diffusion framework, as for instance the fast recovery which occurs if bias stress is removed [20]. Other

phenomena, such as charge trapping, therefore have to be also considered in the NBTI mechanism [22, 23]. Clear steps caused by single trapping or de-trapping events were seen in experimental works, showing the discrete nature of  $V_T$  shifts, [22–24].

The discussion here presented will not focus on the origin and nature of the charge traps. Detailing lattice dynamics, tunneling mechanisms, or determining the physical location of trapping centers is also not the focus of this work. This work focuses instead on the charge trapping statistics (stochastic capture and emission events) that contribute to degradation of transistor on-current over time (BTI). The basic assumptions made in the modeling of BTI here presented are the same ones as in our work presented above, on the modeling of low-frequency noise: 1) charge trapping and de-trapping are stochastic events, governed by characteristic time constants, which are uniformly distributed on a log-scale; 2) the number of traps is assumed to be Poisson distributed, and the parameter of the Poisson distribution is assumed to be U-shaped (this last assumption is key to explain the AC-Behavior), and 4) the amplitude of the fluctuation induced by a single trap is a random variable.

In this section we develop a theoretical analysis to describe the density of occupied traps as a function of bias, temperature and time, aiming to understand and model the charge trapping component of the aging (degradation) process that occurs in MOSFETs.

The same equation (model) applies to the degradation process, i.e., increase in number of occupied traps, as well as to the recovery process, i.e., decrease in number of occupied traps.

The capture and emission of charge carriers by a trap are described as simple Poisson processes governed by rates  $\tau_c$  and  $\tau_e$ , where the capture occurs with probability  $p_{01}(dt) = dt/\tau_c$  and emission occurs with probability  $p_{10}(dt) = dt/\tau_e$ . State 1 stands for the occupied trap, while state 0 stands for the empty trap.  $\tau_c$ and  $\tau_e$  are then the average residence time in states 0 and 1, respectively.

We start by evaluating the device degradation process, which is described by the average number of occupied traps at time *t*, which we denote  $\langle n(t) \rangle$ . First we write the equation for the probability of a particular trap, which is initially empty (state 0), to remain in the same state after an elapsed time *t*. We denote this probability as  $P_{00}(t)$ . This probability can be calculated observing that:

$$P_{01}(t+dt) = P_{01}(t)p_{11}(dt) + P_{00}(t)p_{01}(dt)$$

(3.23)

where  $p_{11}(dt) = 1 - p_{10}(dt) = 1 - dt/\tau_e$  and  $P_{00}(t) = 1 - P_{01}(t)$ . This leads to a simple differential equation. The solution of this differential equation is [18]:

$$P_{01}(t) = \left[1 - \exp\left(-t/\tau_{eq}\right)\right]\tau_{e}/(\tau_{c} + \tau_{e})$$

(3.24)

where  $1/\tau_{eq} = 1/\tau_c + 1/\tau_e$ . A similar evaluation can be performed for  $P_{11}(t)$ , leading to

$$P_{11}(t) = \left[\tau_{\rm e} + \tau_{\rm c} \exp\left(-t/\tau_{\rm eq}\right)\right] / \left(\tau_{\rm c} + \tau_{\rm e}\right)$$

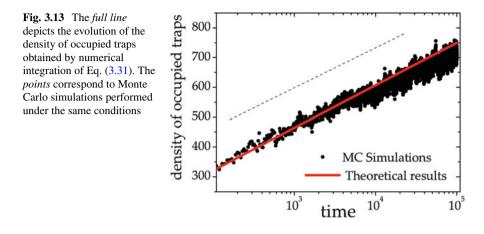

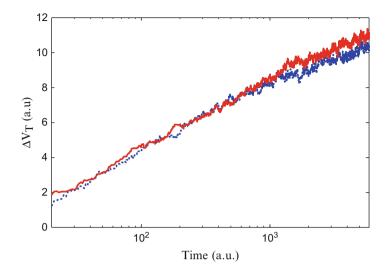

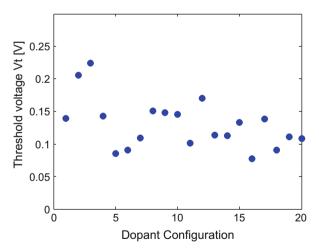

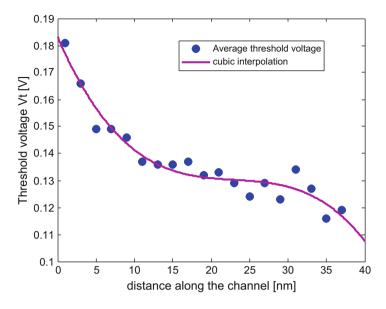

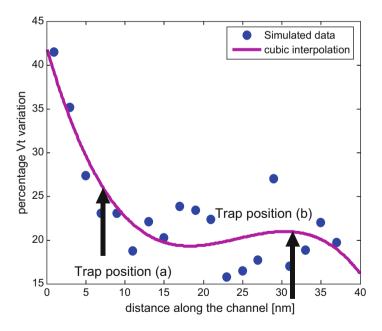

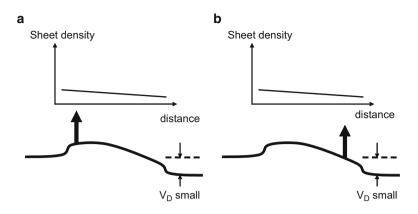

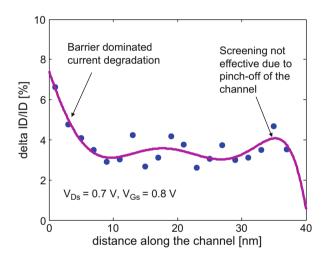

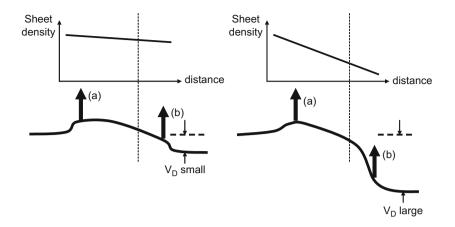

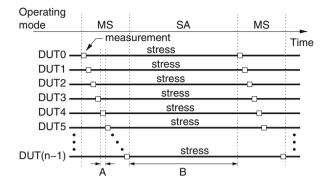

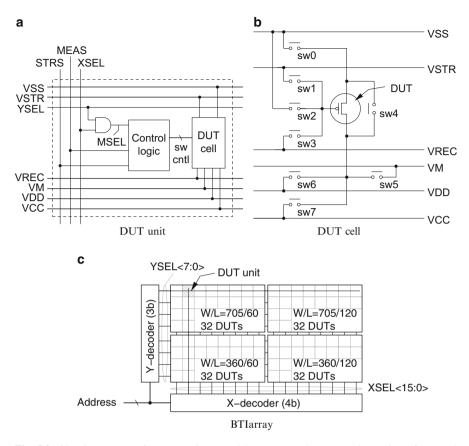

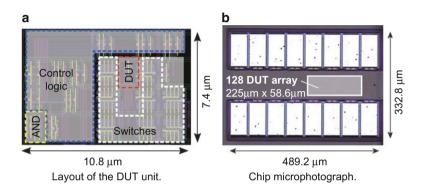

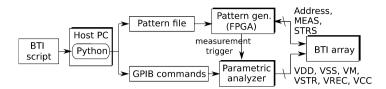

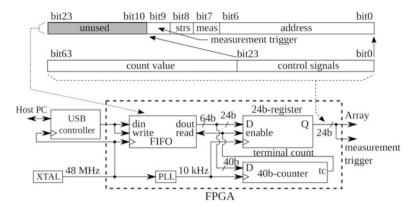

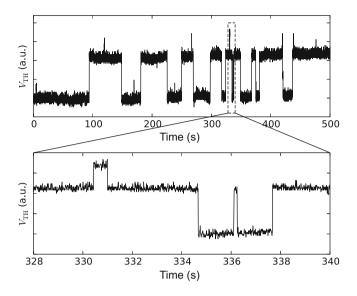

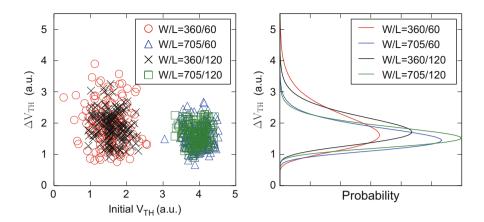

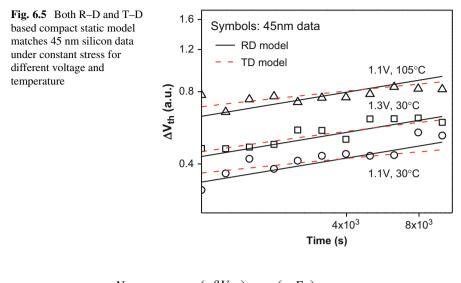

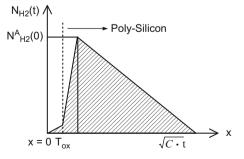

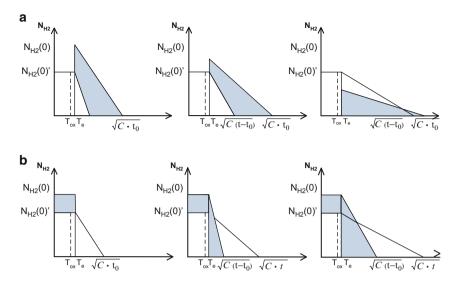

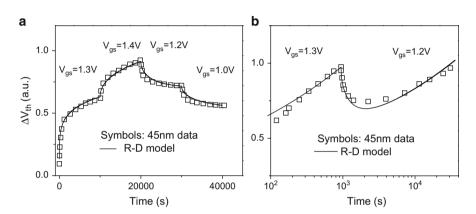

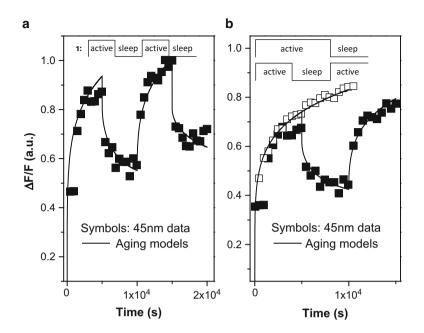

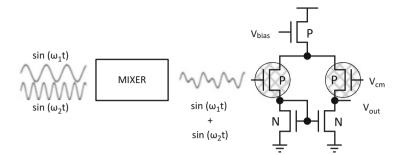

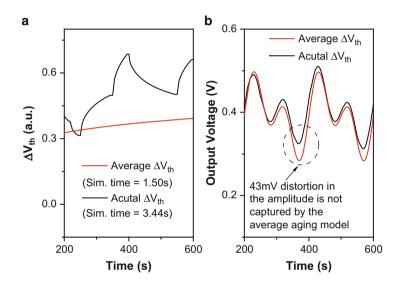

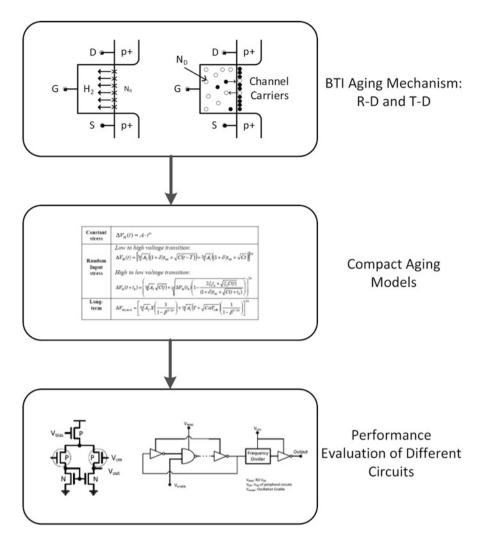

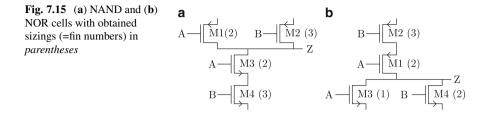

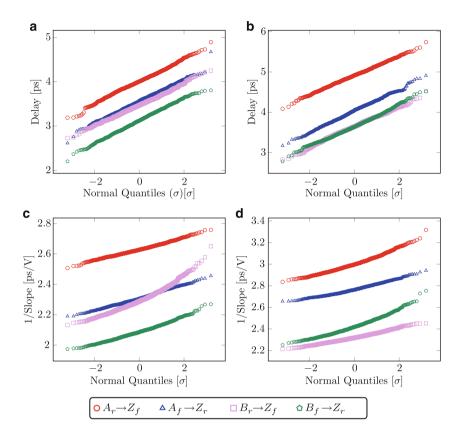

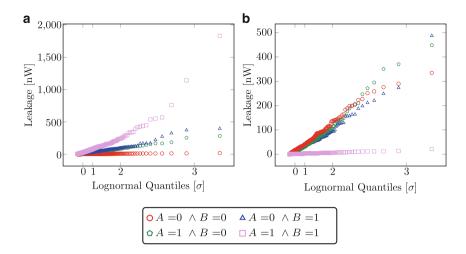

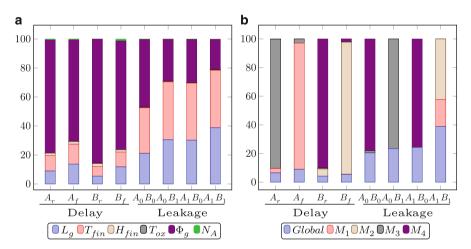

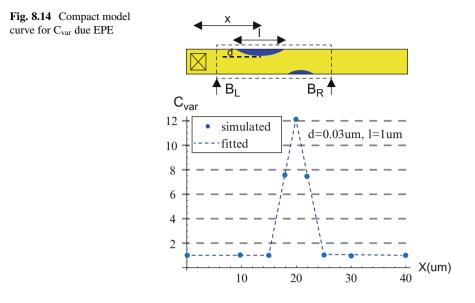

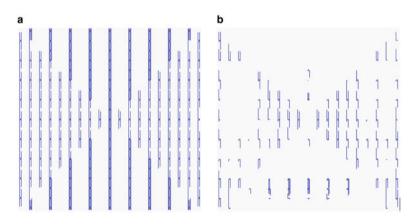

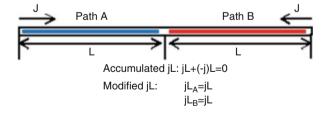

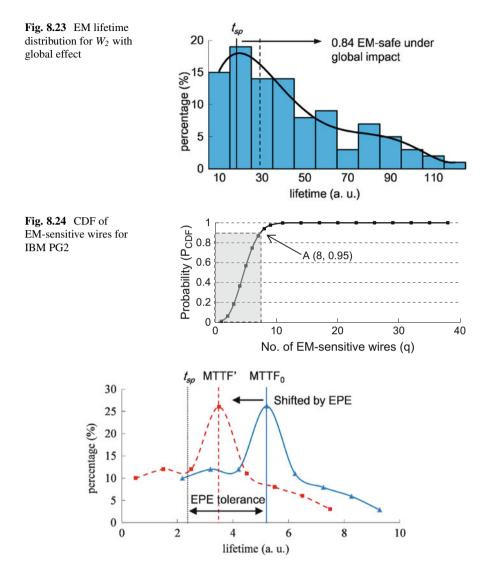

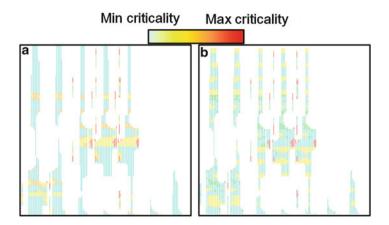

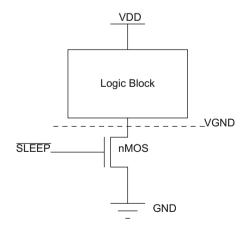

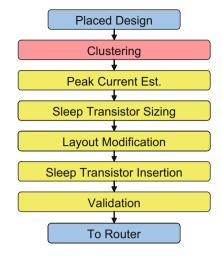

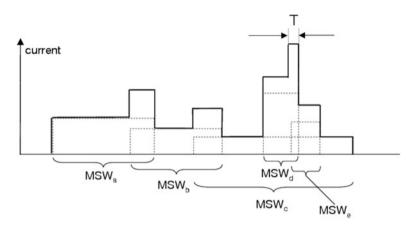

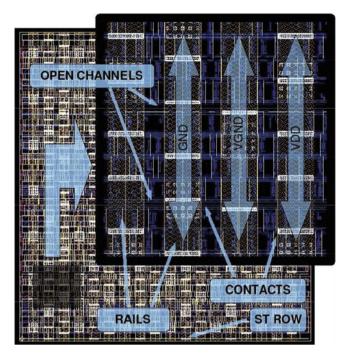

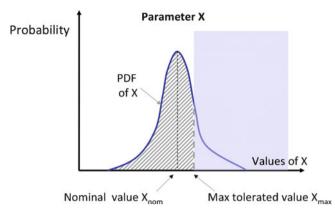

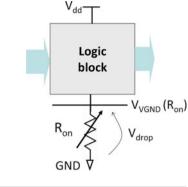

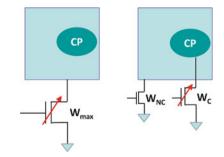

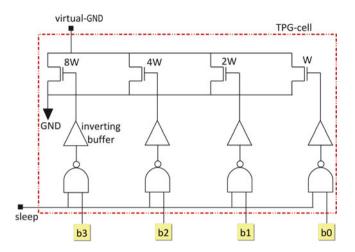

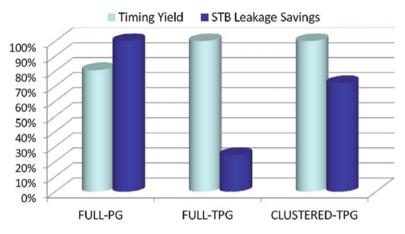

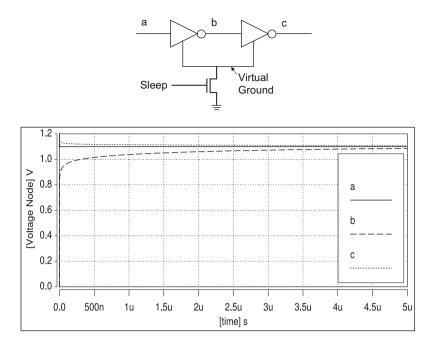

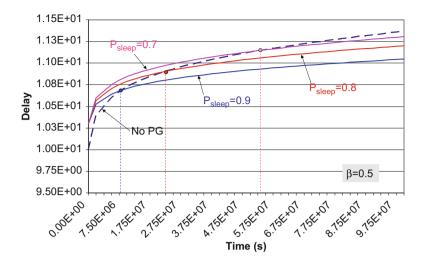

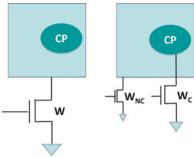

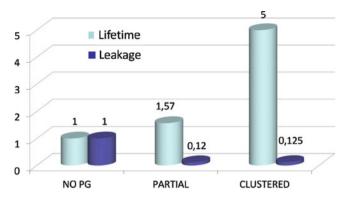

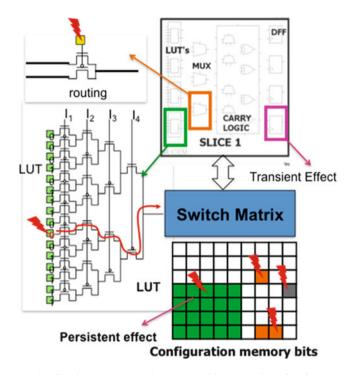

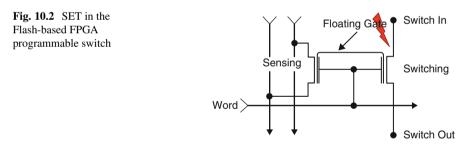

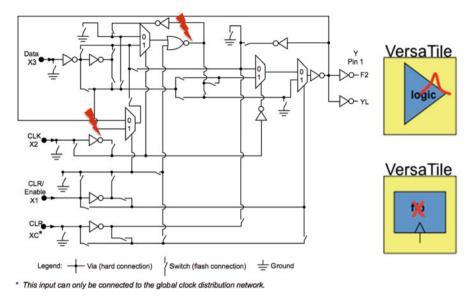

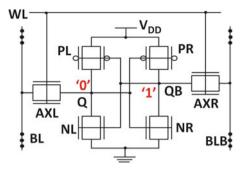

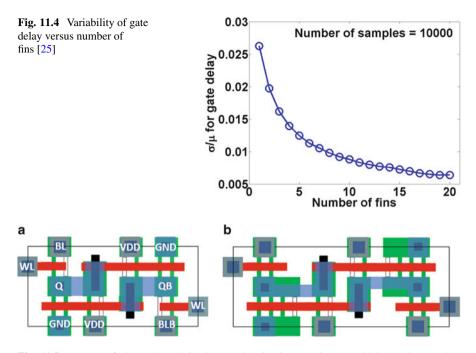

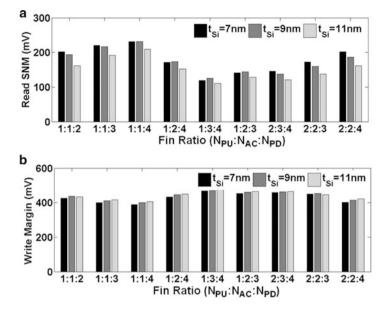

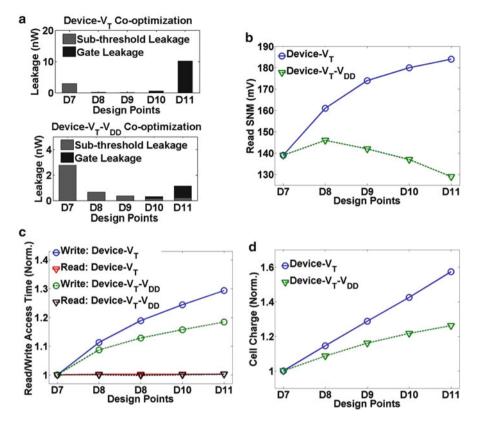

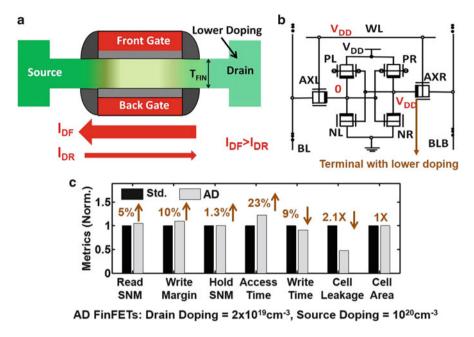

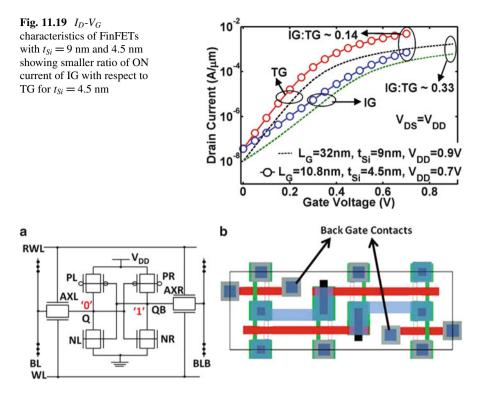

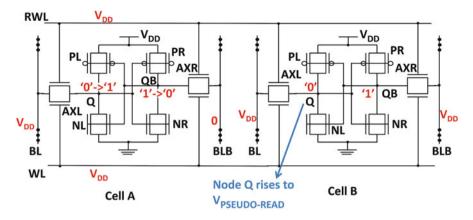

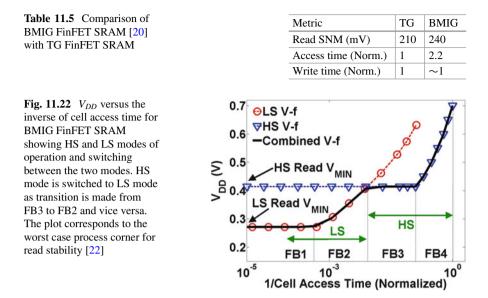

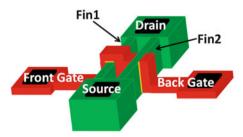

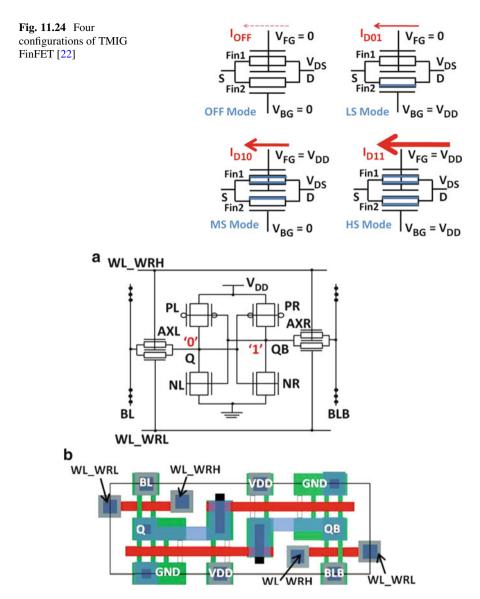

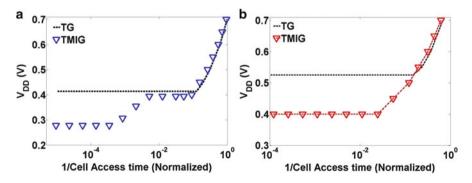

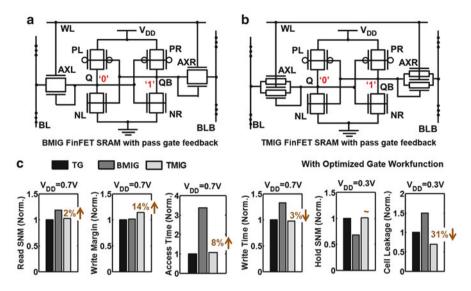

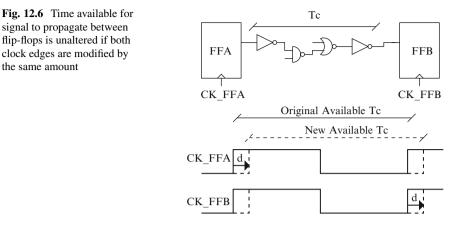

(3.25)