Vikram Arkalgud Chandrasetty

# VLSI Design A Practical Guide for FPGA and ASIC Implementations

For further volumes: http://www.springer.com/series/10059

Vikram Arkalgud Chandrasetty

# VLSI Design

A Practical Guide for FPGA and ASIC Implementations

Vikram Arkalgud Chandrasetty University of South Australia Adelaide, Australia vikramac@ieee.org

ISSN 2191-8112 e-ISSN 2191-8120 ISBN 978-1-4614-1119-2 e-ISBN 978-1-4614-1120-8 DOI 10.1007/978-1-4614-1120-8 Springer New York Dordrecht Heidelberg London

Library of Congress Control Number: 2011934747

#### © Springer Science+Business Media, LLC 2011

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

To My Family and Friends

# **Preface**

The area of VLSI design has gained enormous popularity over the past few decades due to the rapid advancements in integrated circuit (IC) design and technology. The ability to produce miniaturized circuits with high performance in terms of power and speed is the reason for its popularity. Low production cost and advanced techniques for reduced time-to-market adds to the ever-growing demand for ICs. The two major IC design flows – FPGA and ASIC have their own advantages and disadvantages. FPGAs are widely used for quick prototyping and also implementation of various multimedia applications by compromising power, area and speed performance with substantially reduced time-to-market and cost factors. Using ASIC technology, it has been possible to develop high performance multi-core processors. Verification and testing of such complex designs is a critical and challenging task to ensure the quality of the resulting circuits. The advances in EDA software and CAD tools alleviate the effort necessary to carry out the cumbersome design and verification process of ICs.

As we understand that the subject of VLSI design is vast, it is quite complex to find and comprehend the complete details about the design process. This book *VLSI Design: A practical guide for FPGA and ASIC implementations* provides an insight into practical design of VLSI circuits with minimal theoretical arguments. While this publication is not a complete text book on VLSI design, it is intended to serve as supplementary or reference material on practical design and implementation of VLSI circuits. The content of the book is focused for novice VLSI designers and other enthusiasts who would like to understand the VLSI practical design flows. The designs are demonstrated using industry standard software from MATLAB®, Mentor Graphics®, Xilinx®, Synopsys® and Cadence®.

I encourage you to send any errata or feedback for improving the quality of this book to vikramac@ieee.org.

Thank you,

Adelaide, Australia

Vikram Arkalgud Chandrasetty

# **Contents**

| 1 | CM   | OS Dig  | gital Design                                | 1  |

|---|------|---------|---------------------------------------------|----|

|   | 1.1  | Desig   | n of CMOS SRAM Cell and Array               | 1  |

|   |      | 1.1.1   |                                             | 1  |

|   |      | 1.1.2   | Design of 6 Transistor SRAM Cell            | 2  |

|   |      | 1.1.3   | Simulations of SRAM Cell                    | 2  |

|   |      | 1.1.4   | Layout of SRAM Cell                         | 3  |

|   |      | 1.1.5   | Design of SRAM Array                        | 4  |

|   |      | 1.1.6   | Simulation of SRAM Array                    | 4  |

|   | 1.2  | Desig   | n of SRAM Chip Circuit Elements             | 5  |

|   |      | 1.2.1   | SRAM Chip Circuit Elements                  | 5  |

|   |      | 1.2.2   | Design of Complete SRAM Chip                | 8  |

|   |      | 1.2.3   | Simulations of Complete SRAM Chip           | 10 |

|   |      | 1.2.4   | Delay Extraction for SRAM Chip Write/Read   |    |

|   |      |         | Operation                                   | 10 |

|   |      | 1.2.5   | Re-Design of SRAM Chip for Low Power        |    |

|   |      |         | Consumption                                 | 10 |

|   | App  | endix   |                                             | 12 |

|   | Refe | erences |                                             | 15 |

| 2 | FPG  | SA App  | olication Design                            | 17 |

|   | 2.1  |         | n of Direct Sequence-Spread Spectrum System | 18 |

|   |      | 2.1.1   |                                             | 18 |

|   |      | 2.1.2   | •                                           |    |

|   |      |         | Spectrum System                             | 21 |

|   |      | 2.1.3   | Receiver for Direct Sequence-Spread         |    |

|   |      |         | Spectrum System                             | 24 |

|   | 2.2  | FIR F   | ilter Design                                | 29 |

|   |      | 2.2.1   | Concepts of FIR Filter                      | 29 |

|   |      | 2.2.2   | Low Pass FIR Filter Design                  | 30 |

|   |      | 2.2.3   | Distributed Arithmetic Architecture         | 31 |

|   |      | 2.2.4   | Simulation and Synthesis Results            | 31 |

x Contents

|    | 2.3         | Discre  | te Cosine Transform Algorithms                   | 32  |

|----|-------------|---------|--------------------------------------------------|-----|

|    |             | 2.3.1   | Concepts of DCT                                  | 32  |

|    |             | 2.3.2   | DCT Architectures on FPGA                        | 33  |

|    |             | 2.3.3   | Scaled 1-D 8-Point DCT Architecture              | 34  |

|    |             | 2.3.4   | Simulation and Synthesis Results                 | 35  |

|    | 2.4         | Convo   | lution Codes and Viterbi Decoding                | 36  |

|    |             | 2.4.1   | Concepts of Convolution Codes                    | 36  |

|    |             | 2.4.2   | Viterbi Decoder                                  | 38  |

|    |             | 2.4.3   | Simulation and Synthesis Results                 | 40  |

|    | Appe        | endix   |                                                  | 42  |

|    | Refe        | rences  |                                                  | 46  |

| 3  | ASI         | C Desig | ;n                                               | 47  |

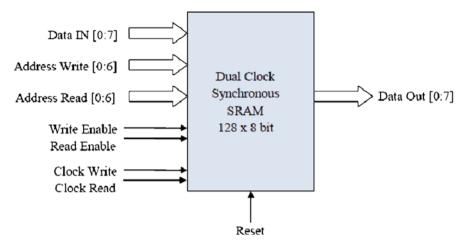

|    | 3.1         |         | Front-End Memory Design                          | 47  |

|    | 5.1         | 3.1.1   | Introduction                                     | 47  |

|    |             | 3.1.2   | Memory Architecture and Specifications           | 48  |

|    |             | 3.1.3   | Implementation and Simulations                   | 48  |

|    |             | 3.1.4   | Results Analysis and Conclusion                  | 49  |

|    | 3.2         |         | Front-End Matrix Multiplier Design               | 51  |

|    | J. <b>_</b> | 3.2.1   | Introduction                                     | 51  |

|    |             | 3.2.2   | Problem Statement                                | 52  |

|    |             | 3.2.3   | Matrix Multiplier Design                         | 52  |

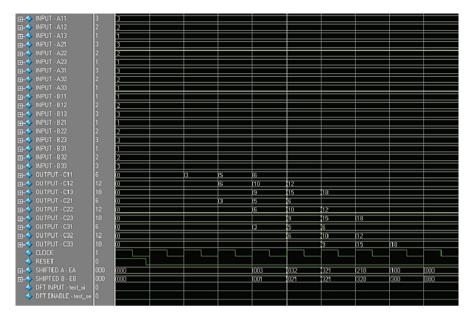

|    |             | 3.2.4   | Implementation and Simulations                   | 52  |

|    |             | 3.2.5   | Analysis of Results and Conclusion               | 54  |

|    | 3.3         | Physic  | al Design of Matrix Multiplier                   | 57  |

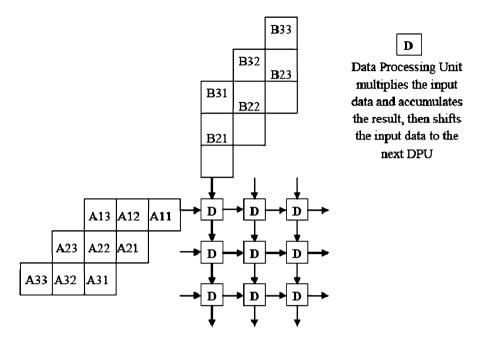

|    |             | 3.3.1   | Introduction to Systolic Array Matrix Multiplier | 57  |

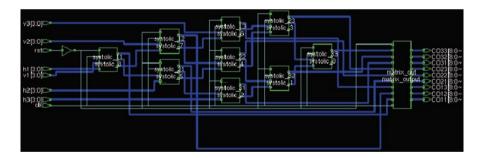

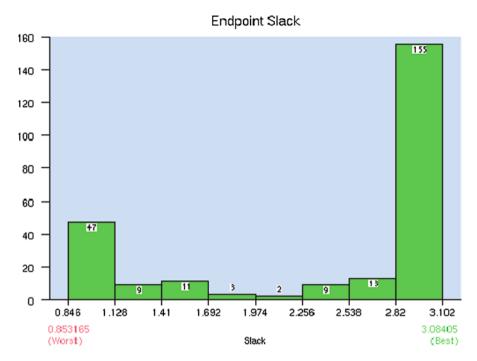

|    |             | 3.3.2   | Physical Design Flow                             | 59  |

|    |             | 3.3.3   | Results and Conclusion                           | 78  |

|    | Appe        | endix   |                                                  | 79  |

|    |             |         |                                                  | 81  |

| 4  | Anal        | log and | Mixed Signal Design                              | 83  |

|    | 4.1         |         | atic Design of OPAMP                             | 83  |

|    |             | 4.1.1   | Introduction                                     | 83  |

|    |             | 4.1.2   | Two Stage OPAMP Design                           | 84  |

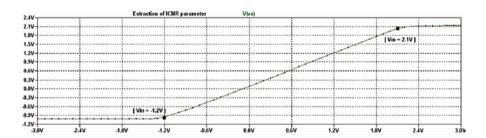

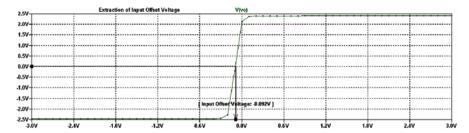

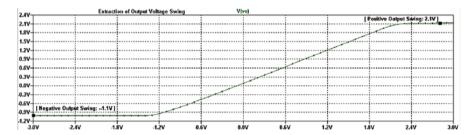

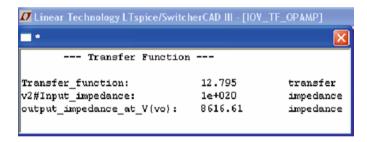

|    |             | 4.1.3   | Results                                          | 93  |

|    | 4.2         | Lavou   | t Design of OPAMP                                | 93  |

|    |             | 4.2.1   | Introduction                                     | 93  |

|    |             | 4.2.2   | Layout Design                                    | 93  |

|    |             | 4.2.3   | Summary and Results                              | 98  |

|    | Appe        |         |                                                  | 99  |

|    |             |         |                                                  | 104 |

| Ab | out t       | he Auth | 10r                                              | 105 |

# **Abbreviations**

ADC Analog to Digital Converter

ASIC Application Specific Integrated Circuit

ATM Asynchronous Transfer Mode AWGN Additive White Gaussian Noise

BJT Bipolar Junction Transistor BPSK Binary Phase Shift Keying

CAD Computer Aided Design

CDMA Code Division Multiple Access

CDR Clock Data Recovery

CMOS Complementary Metal Oxide Semiconductor

CORDIC Coordinate Rotation Digital Computer

CP Charge Pump

CTO Clock Tree Optimization CTS Clock Tree Synthesis

DAA Distributed Arithmetic Architecture

DAC Digital to Analog Converter

DCT Discrete Cosine Transform

DEF Design Exchange Format

DFM Design For Manufacturability

DFT Design For Testability

DRAM Dynamic Random Access Memory

DRC Design Rule Check

DSPF Detailed Standard Parasitic Format

DSSS Direct Sequence Spread Spectrum

DTC Divide by Two Circuit

DTFS Deflash Trim Form Singulation

DUT Device Under Test

DWT Discrete Wavelet Transform

xii Abbreviations

EDA Electronic Design Automation

EEPROM Electrically Erasable Programmable Read Only Memory

ERC Electrical Rule Check

FDA Functional Data Analysis

FEC Forward Error Correction Codes

FF Flip Flop

FFT Fast Fourier Transform FIR Finite Impulse Response

FPGA Field Programmable Gate Array

FSM Finite State Machine

GDS II Graphic Data System II

GUI Graphical User Interface

HDL Hardware Description Language

ICMR Input Common Mode Range

IGFET Insulated Gate Field Effect Transistor

IOV Input Offset Voltage

ITF Interconnect Technology Format

ITRS International Road Map for Semiconductors

JFET Junction Field Effect Transistor JPEG Joint Photographic Experts Group

LEF Library Exchange Format

LFSR Linear Feedback Shift Register

LP Low Pass

LPE Layout Parasitic Extraction

LSB Least Significant Bit LUT Look Up Table

LVS Layout Versus Schematic

MAC Multiply And Accumulate MBE Molecular Beam Epitaxy

MEMS Mico Electro Mechanical System

MOSFET Metal Oxide Semiconductor Field Effect Transistor MOSIS Metal Oxide Semiconductor Implementation Service

MPEG Moving Picture Experts Group

MSB Most Significant Bit

OVS Output Voltage Swing

PFD Phase Frequency Detector

PG Power Ground

PIT Progressive Image Transmission

PLL Phase Locked Loop

PN Pseudo-random Noise

PPO Post Placement Optimization

PWM Pulse Width Modulation

Abbreviations xiii

QAM Quadrature Amplitude Modulation

QDR Quad Data Rate

QPSK Quadrature Phase Shift Keying

RC Resistance Capacitance

RF Radio Frequency

ROM Read Only Memory

RTL Register Transfer Level

SDC Synopsys Design Constraint SDF Standard Delay Format SNR Signal to Noise Ratio SOI Silicon On Insulator SOP Sum Of Products

SPEF Standard Parasitic Exchange Format SRAM Static Random Access Memory

STA Static Timing Analysis

TDF Top Design Format

TLU Table Look Up

TSMC Taiwan Semiconductor Manufacturing Company

TS-OPAMP Two Stage-Operational Amplifier

USB Universal Serial Bus VCD Value Change Dump

VCO Voltage Controlled Oscillator

# **Chapter 1 CMOS Digital Design**

The demand for electronic and multimedia devices is increasing exponentially. This demand in-turn has propelled the need for memory chips to process instructions, store data and other multimedia content. Some of the most common memory structures used for faster data and program memory access are Static (SRAM) and Dynamic (DRAM) memory.

In this chapter, a 6 Transistor CMOS based SRAM memory chip of 1 KB capacity is designed and simulated. The complete chip along with SRAM cells array and circuit elements is designed using SPICE program. Simulations for the design are done using LTspice. Schematic and Layout for a single SRAM cell is also designed using Cadence Schematic and Virtuoso tool respectively. An estimation of parasitic resistance and capacitance values for the layout drawn for the SRAM cell is extracted Vituoso.

The prerequisite to approach this chapter would be an adequate background of CMOS digital circuits, Spice programming and basic knowledge of IC layout design.

# 1.1 Design of CMOS SRAM Cell and Array

# 1.1.1 Plan of SRAM Cell and Array

Static Random Access Memory (SRAM) is a type of semiconductor memory. The word static indicates that the memory retains its contents as long as power remains applied. 'Random Access' means that the location in the memory can be written to or read from in any order regardless of the memory location that was last accessed [1]. The SRAM cell has the capability to store one bit data as long as the power is continuously applied. Hence SRAM's are volatile memory devices. An array of eight SRAM cells can store 1 byte of data. Considering this unit of 8-bit SRAM array, a number of these structures can be replicated to build a large memory block. In this chapter, an SRAM memory of 1 KB is designed using 6 Transistor (6T) CMOS SRAM cell.

1

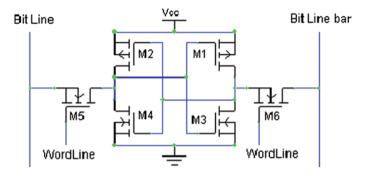

Fig. 1.1 6T CMOS SRAM cell

# 1.1.2 Design of 6 Transistor SRAM Cell

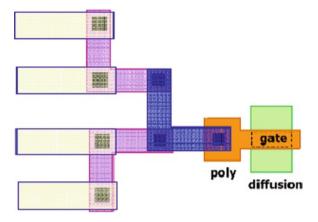

An SRAM cell can store one bit data on four transistors that form two cross-coupled inverters [1]. This storage cell has two stable states which are used to denote 0 and 1. Two additional access transistors serve to control the access to storage cell during read and write operations. Thus, a combination of 6 transistors is used to store one bit data.

Access to the cell is enabled by the word line (WL) which controls the two access transistors. They are used to transfer data for both read and write operations by connecting the bit lines (BL and BL bar). Although the two bit lines are not necessary, both the signal and its inverse are typically provided since it improves noise margins. The symmetric structure of SRAM's allows for differential signaling, which makes small voltage swings more easily detectable. A schematic of 6T CMOS SRAM cell is shown in Fig. 1.1.

# 1.1.3 Simulations of SRAM Cell

An SRAM cell has three different states of operation: *standby* when the circuit is idle, *reading* when the data has been requested and *writing* when updating the contents. Each states are discussed with respect to the Fig. 1.1 as follows [2]:

# Standby:

If the word line is not asserted, the access transistors M5 and M6 disconnect the cell from bit lines. The two cross coupled inverters formed by M1–M4 will continue to reinforce each other as long as they are disconnected from the outside world.

#### Reading:

Assuming that the content of memory is 1, when the word line is asserted, the state stored in the cell is transferred to the bit line which is then read on the data output port. If the memory content was a 0, the opposite would happen.

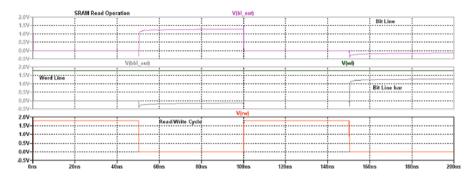

Fig. 1.2 Spice simulations for SRAM cell read operation

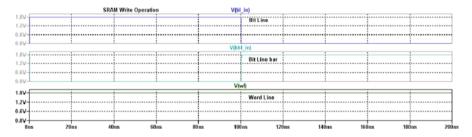

Fig. 1.3 Spice simulations for SRAM cell write operation

## Writing:

The start of a write cycle begins by applying the value to be written to the bit lines. The word line is asserted to store the input data on to the cell. The bit line input drivers are designed to be much stronger than the relatively weak transistors in the cell itself, so that they can easily override the previous state of the cross-coupled inverters. Careful sizing of the transistors in the SRAM cell is needed to ensure proper operation.

The spice simulation for SRAM cell Read operation is shown in Fig. 1.2. The spice simulation for SRAM cell Write operation is shown in Fig. 1.3.

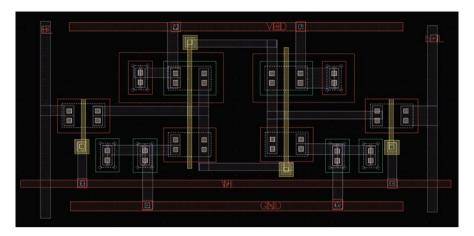

# 1.1.4 Layout of SRAM Cell

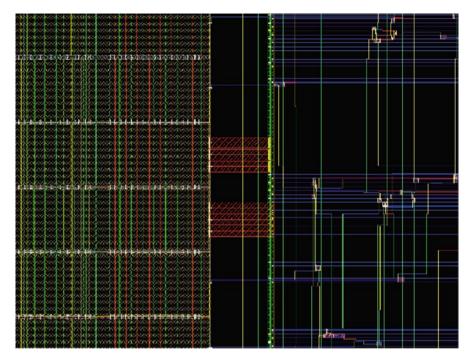

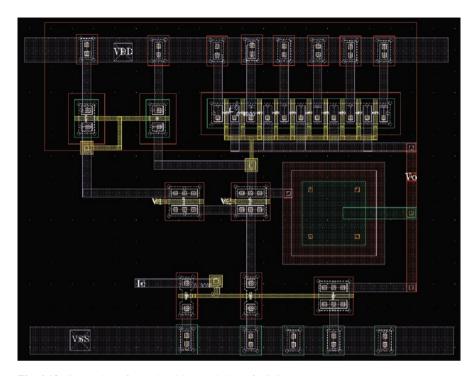

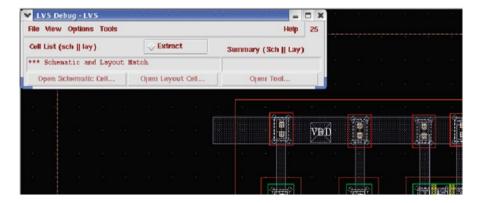

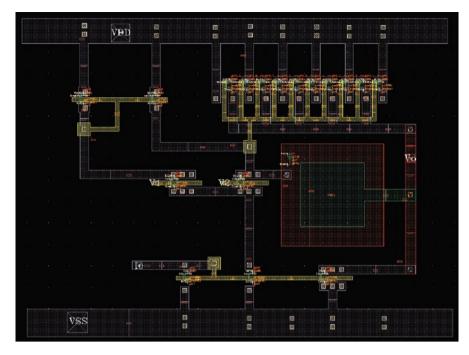

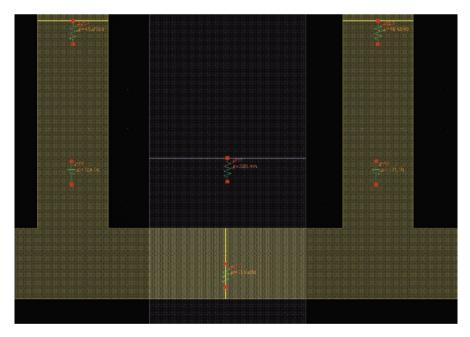

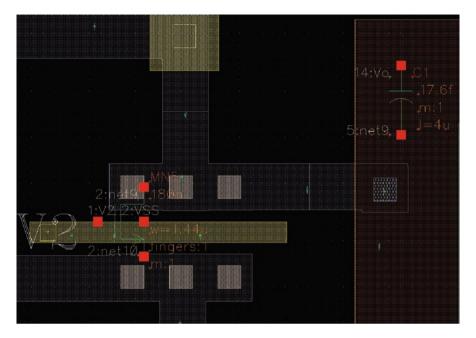

The layout for SRAM cell is drawn using Cadence Virtuoso for 180 nm technology. The layout is successfully completed with Design Rule Checks (DRC) and Layout versus Schematic (LVS) evaluation as well. A snapshot of the layout of SRAM cell is shown in Fig. 1.4. The resistance and capacitance parasitic parameters are extracted from the layout using Cadence Virtuoso.

Fig. 1.4 Layout of 6T SRAM cell

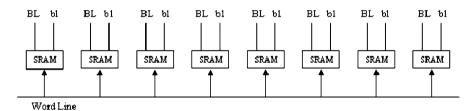

Fig. 1.5 Block diagram of 8-bit SRAM array

# 1.1.5 Design of SRAM Array

For this design, 1 KB SRAM chip with 8-bit data I/O is required. Since one bit data can be stored in a single SRAM cell, an array of 8 cells should satisfy the requirement. Hence 1,024 such arrays are required to build 1 KB memory chip. A block diagram representing an 8-bit memory SRAM array is shown in Fig. 1.5.

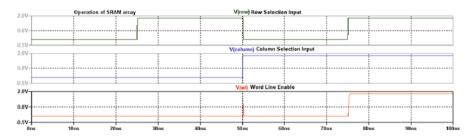

# 1.1.6 Simulation of SRAM Array

An SRAM array (8-bit) is selected or activated by the row and column decoder based on the input address. The spice simulation for SRAM array section is shown in Fig. 1.6.

Fig. 1.6 Spice simulations for section of SRAM array

# 1.2 Design of SRAM Chip Circuit Elements

# 1.2.1 SRAM Chip Circuit Elements

The 6T CMOS SRAM chip requires various circuit elements to execute the desired memory operations. In this section, a complete SRAM chip circuitry elements such as, address decoder, sense amplifier, pre-charge circuit and data I/O control logic is designed using LTspice. The detailed design, schematic and simulation of these circuit elements are discussed in the following sections:

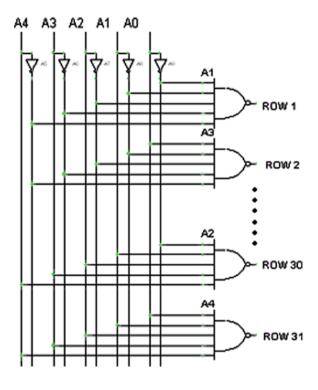

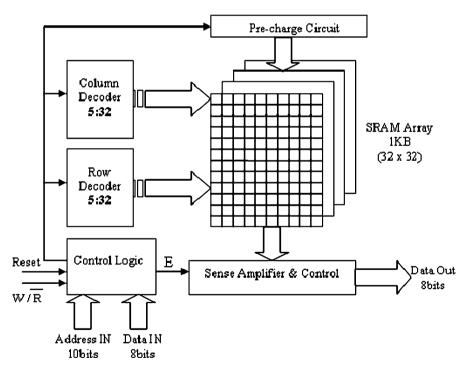

#### 1.2.1.1 Address Decoder

The Address Decoder is nothing but a simple logic circuitry used to select and enable the memory cells in the SRAM array corresponding to the input address value. In this section, 1 KB SRAM is required to be designed. Hence it requires 10 address bits to cover entire 1 KB memory area. A 5:32 NAND based decoder is designed as row decoder to access 32 bytes of memory area and another 5:32 decoder is used as column decoder in order to access 32 such 32 bytes of memory areas. There by achieving the desired access to 1 KB memory. The schematic of NAND based 5:32 decoder is shown in Fig. 1.7.

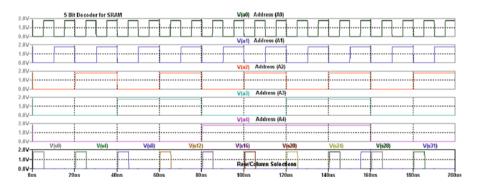

The 5:32 NAND based decoder is designed and simulated using LTspice [3]. The simulation results for 5:32 NAND based decoder are shown in Fig. 1.8.

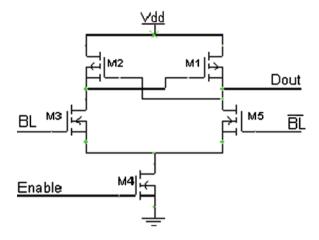

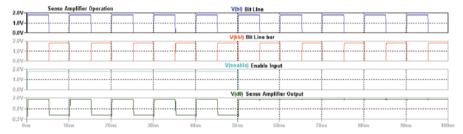

# 1.2.1.2 Sense Amplifier

A Sense amplifier is an essential circuit in memory chips to speed up the *Read* operation. Due to large arrays of SRAM cells, the resulting signal in the event of *Read* operation has a much lower voltage swing [4]. To compensate for that swing, a sense amplifier is used to amplify voltage coming off Bit Line and ~Bit Line. The voltage coming out of sense amplifier has a full swing voltage of (0–1.8 V). Sense Amplifier also helps reduce the delay times and power dissipation in the overall

**Fig. 1.7** Schematic of NAND based 5:32 row/column decoder

Fig. 1.8 Spice simulations of 5:32 NAND based row/column decoder

SRAM chip. There are many versions of sense amplifier used in memory chips. The one that is designed in this chapter is a Cross-coupled Sense Amplifier. The schematic of the same is shown in Fig. 1.9.

The Cross-coupled/Feedback Sense amplifier is designed and simulated using LTspice. The LTspice simulations for the same are shown in Fig. 1.10.

**Fig. 1.9** Schematic of cross-coupled sense amplifier

Fig. 1.10 Spice simulations of cross-coupled sense amplifier

**Fig. 1.11** Schematic of a pre-charge circuit

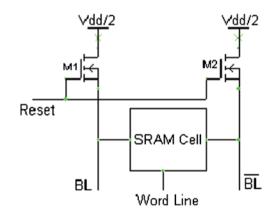

# 1.2.1.3 Pre-Charge Circuit

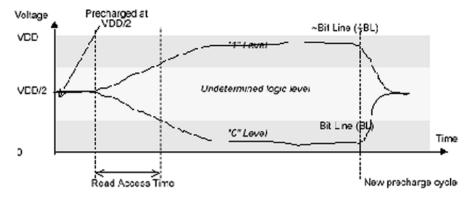

Safe read and write operations require a modification of the memory array and timing sequence based on a pre-charge circuit [5]. The schematic of a pre-charge circuit is shown in Fig. 1.11. The usual voltage of pre-charge is VDD/2. Before reading or

Fig. 1.12 Read cycle using pre-charge circuit

writing to the memory, the bit lines are tied to VDD/2 using appropriate pass gates. When reading, the BL and ~BL diverge from VDD/2 and reach the "1" or "0" levels after a short time. As the SRAM cells are based on active devices, the memories usually provide the fastest read and write access times. A simple pre-charge circuit consists of a NMOS or PMOS. The drain is connected to VDD/2 and the source to the bit line. The pre-charging on bit lines is done whenever a Reset is triggered. The Read cycle using pre-charge circuit is shown in Fig. 1.12 [5].

# 1.2.1.4 Data I/O Control Logic

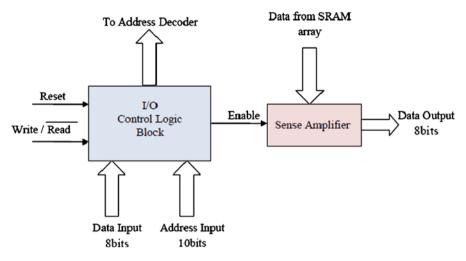

The Data Input/Output control logic block is responsible for latching Input data to the SRAM memory cells and also latching the data that needs to be read on the output data ports from the specified address in the SRAM.

The Input data control block is basically a data routing block. Data from the input pins is passed into the block and then transferred to the memory cell array via the buffer circuit and a pass transistor. The pass transistor controls the flow of data into the memory cell array.

The Output data control block is a simple controlled buffer circuit. A tri-state inverter is used to control the flow of data to the Data Out pins on the SRAM chip. When Read is enabled, the tri-state transistors are turned off and prevent data from entering in to the SRAM chip to write. The data is accessed at the specified address on SRAM and latched on the data output pins via Sense amplifier. The I/O control logic block is shown in Fig. 1.13.

# 1.2.2 Design of Complete SRAM Chip

An SRAM chip with 1 KB memory can be built using 32 blocks of 32 bytes array. The design of circuit elements required to support the operation of SRAM chip is

Fig. 1.13 Block diagram of I/O control logic block for 1 KB SRAM chip

Fig. 1.14 Complete plan of 1 KB SRAM chip

discussed in Sect. 1.2.1. Using these memory cell arrays and circuit elements, a complete 1 KB CMOS based SRAM chip can be designed. In this section, 6T CMOS 1 KB SRAM chip is designed as per the plan shown in Fig. 1.14.

Fig. 1.15 Spice simulations for complete SRAM chip operation

The approximate chip area required for the designed 1 KB CMOS based SRAM chip including circuitry elements can be calculated as follows:

No. of MOSFET used in the design (Approx.) = 56,000Area of a single MOSFET [NMOS/PMOS – average] (Approx.) =  $20 \mu^2$ Total area =  $56,000 \times 20 \mu^2$  =  $1,120,000 \mu^2$ Estimated chip area for the designed 1 KB SRAM chip =  $1.12 \text{ mm}^2$

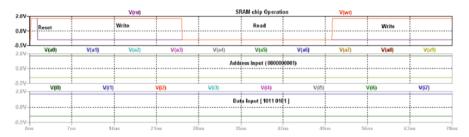

# 1.2.3 Simulations of Complete SRAM Chip

The complete 1 KB SRAM chip is designed and simulated using LTspice [6]. The LTspice simulations for the same are shown in Fig. 1.15.

# 1.2.4 Delay Extraction for SRAM Chip Write/Read Operation

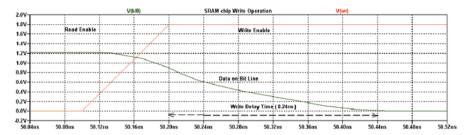

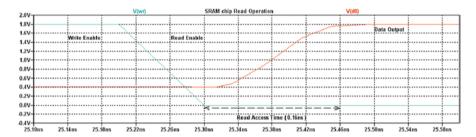

The Write delay and Read access times are extracted for the designed SRAM chip from the simulations.

The Write delay time is measured when Write is enabled until when the data appears on the data bit lines. From the LTspice simulations shown in Fig. 1.16, it can be inferred that the *Write delay time* is 0.24 ns.

The Read Access time is measured from when Read is enabled until when the data appears on the data output lines. From the LTspice simulations shown in Fig. 1.17, it can be inferred that the *Read Access time* is 0.16 ns.

# 1.2.5 Re-Design of SRAM Chip for Low Power Consumption

The power consumption is very important factor that needs to be considered while designing a chip. It is evident that the SRAM chip is operational whenever the

Fig. 1.16 Spice simulation of SRAM chip to measure write delay time

Fig. 1.17 Spice simulation of SRAM chip to measure read access time

word-line is asserted for read/write operation. The current passes through the cell during read/write operation as long as the word-line is asserted. Hence the power consumption in the chip is directly proportional to the time during which the word-line is asserted.

Based on the above hypothesis, certain measures can be taken by implementing appropriate logic to optimize the power consumption. One of the approaches to the solution for the above mentioned problem is to incorporate clock based assertion of word-line. The word-line may be asserted only for a short and optimized duration for which the write or read operation can be performed completely. Hence the power consumption can be reduced to a certain extent.

The pre-charge voltage that is applied on the bit lines also can be optimized to minimize the power consumption. The duration for which the charge applied on the bit lines may be optimized so that it is just sufficient enough for the sense amplifiers to sense the voltage levels at the shortest time.

Various other measures may be taken based on the floor plan of the transistor, layout, dimensions of transistors, and other factors etc. to optimize power consumption. Additional circuitry also may be incorporated to obtain an optimized and lowest power consuming SRAM chips.

# **Appendix**

.ends

#### A. SPICE code for SRAM circuit elements

```

* Interface components subcircuits

* File Name: subckt comp.sp

**** Sense Amplifier unit subcircuit

.subckt sense amplifier Enable BL bBL output src gnd

M1 output A src src cmosp l=0.18u w=0.72u

M2 A output src src cmosp l=0.18u w=0.72u

M3 A BL B qnd cmosn 1=0.18u w=0.36u

M4 output bBL B qnd cmosn l=0.18u w=0.36u

M5 B Enable qnd qnd cmosn l=0.18u w=0.36u

.ends

**** Sense Amplifier row subcircuit

.subckt sense amplifier row E BLO bBLO BL1 bBL1 BL2 bBL2 BL3 bBL3

BL4 bBL4 BL5 bBL5 BL6 bBL6 BL7 bBL7 D0 D1 D2 D3 D4 D5 D6 D7 VDD gnd

X0 E BLO bBLO NO VDD gnd sense amplifier

X1 E BL1 bBL1 N1 VDD gnd sense amplifier

X2 E BL2 bBL2 N2 VDD gnd sense amplifier

X3 E BL3 bBL3 N3 VDD gnd sense amplifier

X4 E BL4 bBL4 N4 VDD gnd sense amplifier

X5 E BL5 bBL5 N5 VDD gnd sense amplifier

X6 E BL6 bBL6 N6 VDD gnd sense amplifier

X7 E BL7 bBL7 N7 VDD gnd sense amplifier

X8 NO DO VDD gnd buffer

X9 N1 D1 VDD gnd buffer

X10 N2 D2 VDD and buffer

X11 N3 D3 VDD and buffer

X12 N4 D4 VDD and buffer

X13 N5 D5 VDD qnd buffer

X14 N6 D6 VDD and buffer

X15 N7 D7 VDD and buffer

X16 E Dis VDD gnd inverter

M1 D0 Dis gnd gnd cmosn l=0.18u w=0.36u

M2 D1 Dis qnd qnd cmosn l=0.18u w=0.36u

M3 D2 Dis gnd gnd cmosn l=0.18u w=0.36u

M4 D3 Dis qnd qnd cmosn l=0.18u w=0.36u

M5 D4 Dis gnd gnd cmosn l=0.18u w=0.36u

M6 D5 Dis gnd gnd cmosn l=0.18u w=0.36u

M7 D6 Dis gnd gnd cmosn l=0.18u w=0.36u

M8 D7 Dis gnd gnd cmosn l=0.18u w=0.36u

```

Appendix 13

## \*\*\*\* 5 bit Decoder subcircuit

.subckt decoder\_5bit A0 A1 A2 A3 A4 s0 s1 s2 s3 s4 s5 s6 s7 s8 s9 s10 s11 s12 s13 s14 s15 s16 s17 s18 s19 s20 s21 s22 s23 s24 s25 s26 s27 s28 s29 s30 s31 VDD qnd

X0 A0 bA0 VDD gnd inverter X1 A1 bA1 VDD gnd inverter X2 A2 bA2 VDD gnd inverter X3 A3 bA3 VDD gnd inverter X4 A4 bA4 VDD gnd inverter

X5 bA4 bA3 bA2 bA1 bA0 s0 VDD gnd and5 Х6 bA4 bA3 bA2 bA1 A0 s1 VDD qnd and5 X7 bA4 bA3 bA2 A1 bA0 s2 VDD qnd and5 X8 bA4 bA3 bA2 A1 A0 s3 VDD qnd and5 X9 bA4 bA3 A2 bA1 bA0 s4 VDD and and5 X10 bA4 bA3 A2 bA1 A0 s5 VDD gnd and5 VDD gnd and5 X11 bA4 bA3 A2 A1 bA0 s6 X12 bA4 bA3 A2 A1 A0 s7 VDD and and5 X13 bA4 A3 bA2 bA1 bA0 s8 VDD gnd and5 X14 bA4 A3 bA2 bA1 A0 s9 VDD gnd and5 X15 bA4 A3 bA2 A1 bA0 s10 VDD gnd and5 X16 bA4 A3 bA2 A1 A0 s11 VDD gnd and5 X17 bA4 A3 A2 bA1 bA0 s12 VDD gnd and5 X18 bA4 A3 A2 bA1 A0 s13 VDD gnd and5 X19 bA4 A3 A2 A1 bA0 s14 VDD gnd and5 X20 bA4 A3 A2 A1 A0 s15 VDD qnd and5 X21 A4 bA3 bA2 bA1 bA0 s16 VDD gnd and5 X22 A4 bA3 bA2 bA1 A0 s17 VDD gnd and5 X23 A4 bA3 bA2 A1 bA0 s18 VDD gnd and5 X24 A4 bA3 bA2 A1 A0 s19 VDD gnd and5 X25 A4 bA3 A2 bA1 bA0 s20 VDD gnd and5 X26 A4 bA3 A2 bA1 A0 s21 VDD qnd and5 X27 A4 bA3 A2 A1 bA0 s22 VDD gnd and5 X28 A4 bA3 A2 A1 A0 s23 VDD gnd and5 X29 A4 A3 bA2 bA1 bA0 s24 VDD gnd and5 X30 A4 A3 bA2 bA1 A0 s25 VDD and and5 X31 A4 A3 bA2 A1 bA0 s26 VDD gnd and5 X32 A4 A3 bA2 A1 A0 s27 VDD gnd and5 A3 A2 bA1 bA0 s28 VDD gnd and5 X33 A4 X34 A4 A3 A2 bA1 A0 s29 VDD qnd and5 X35 A4 A3 A2 A1 bA0 s30 VDD gnd and5 X36 A4 A3 A2 A1 A0 s31 VDD gnd and5

.ends

# B. SPICE code for RC parasitic extraction from SRAM cell layout

```

* LINUX Sat Mar 24 15:11:27 2007

```

- \* PROGRAM advgen

- \* SPICE LIBRARY

.SUBCKT sram cell VDD GND BL WL bBL

- \* Caps2d version: 8

- \* TRANSISTOR CARDS

\*

\* RESISTOR AND CAP/DIODE CARDS

\*

| Rg1  | WL#3    | WL#2    | 45.2083  | \$poly |

|------|---------|---------|----------|--------|

| Rg2  | net12   | net12#2 | 116.2500 | \$poly |

| Rg3  | net12   | net12#3 | 53.9583  | \$poly |

| Rg4  | net5#6  | net5#7  | 115.4167 | \$poly |

| Rg5  | net5#7  | net5    | 35.6250  | \$poly |

| Rg6  | WL#6    | WL#5    | 46.2500  | \$poly |

| Rf1  | BL#1    | BL      | 1.0564   | \$mt1  |

| Rf2  | WL#1    | WL#2    | 2.4110   | \$mt1  |

| Rf3  | GND#1   | GND#2   | 2.4778   | \$mt1  |

| Rf4  | GND#1   | GND#3   | 0.2601   | \$mt1  |

| Rf5  | VDD#1   | VDD#2   | 0.3244   | \$mt1  |

| Rf6  | VDD#2   | VDD#3   | 2.4814   | \$mt1  |

| Rf7  | net5    | net5#2  | 1.2832   | \$mt1  |

| Rf8  | net5#2  | net5#3  | 0.3333   | \$mt1  |

| R£9  | net5#3  | net5#4  | 1.0512   | \$mt1  |

| Rf10 | net5#3  | net5#5  | 0.3238   | \$mt1  |

| Rf11 | VDD#4   | VDD#5   | 0.1669   | \$mt1  |

| Rf12 | VDD#5   | VDD#6   | 2.5082   | \$mt1  |

| Rf13 | GND#1   | GND#4   | 0.3203   | \$mt1  |

| Rf14 | GND#1   | GND#5   | 2.4776   | \$mt1  |

| Rf15 | net12#4 | net12#5 | 1.3201   | \$mt1  |

| Rf16 | net12#5 | net12#6 | 0.3653   | \$mt1  |

| Rf17 | net12#6 | net12#3 | 1.4158   | \$mt1  |

| Rf18 | net12#5 | net12#7 | 0.2855   | \$mt1  |

| Rf19 | WL#4    | WL#5    | 2.4070   | \$mt1  |

| Rf20 | bBL#1   | bBL     | 0.9190   | \$mt1  |

| Re1  | VDD#6   | VDD     | 0.2832   | \$mt2  |

| Re2  | VDD     | VDD#3   | 1.2223   | \$mt2  |

| Re3  | GND#5   | GND     | 0.7362   | \$mt2  |

| Re4  | GND     | GND#2   | 1.3788   | \$mt2  |

| Re5  | WL#4    | WL      | 2.2416   | \$mt2  |

| Re6  | WL      | WL#1    | 2.0018   | \$mt2  |

Appendix 15

```

CAPACITOR CARDS

C1

VDD

GND

2.038E-16

C2

_{\mathrm{BL}}

GND

2.661E-16

C3

WL

6.774E-16

GND

2.865E-16

C4

bBL

GND

C5

1.597E-16

net12

GND

C6

net5

GND

4.261E-16

C7

net5#6

GND

2.298E-16

C8

WL#6

GND

7.296E-17

C9

net5#7

1.507E-16

GND

C10

net12#2 GND

2.056E-16

C11

WL#3

GND

7.003E-17

C12

WL#5

GND

3.171E-16

C13

net12#3 GND

4.754E-16

C14

WL#2

GND

3.062E-16

C15

WL#4

7.411E-16

GND

C16

VDD#6

GND

4.331E-16

C17

6.310E-16

VDD#3

GND

C18

WL#1

GND

6.933E-16

C19

VDD#4

GND

1.635E-16

7.459E-16

C20

bBL#1

GND

C21

2.806E-16

net12#4 GND

C22

net12#7 GND

1.575E-16

C23

net5#2

3.270E-16

GND

C24

net5#4

GND

2.873E-16

C25

BL#1

GND

7.836E-16

C26

VDD#5

GND

1.549E-16

C27

net12#6 GND

3.979E-16

C28

net5#5 GND

1.381E-16

C29

VDD#2

GND

1.350E-16

C30

VDD#1

1.746E-16

GND

3.524E-16

C31

net5#3 GND

C32

net12#5 GND

3.510E-16

```

.ENDS sram\_cell

#### References

- Kang S, Leblebici Y (2003) CMOS digital integrated circuits, 3rd edn. Tata McGraw-Hill, Boston

- Static Random Access Memory Interface (2007) EE Herald. http://www.eeherald.com/section/ design-guide/esmod15.html. Accessed 4 June 2007

- LT Spice User Guide (2006) Linear technology. http://LTspice.linear-tech.com/software/scad3. pdf. Accessed 10 August 2006

- Mehata K, Zinkovski I (2002) CSE447: Design of 1 KB SRAM chip. The Pennsylvania State University. http://www.cedcc.psu.edu/khanjan/vlsihome.htm. Accessed 4 June 2007

- Static RAM Memory (2006) Institut National des Sciences. https://intranet.insa-toulouse.fr/ view/422/content/static\_ram.html. Accessed 10 August 2006

- ECE558: Spice Simulations (2006) University of Massachusetts http://www-unix.ecs.umass. edu/~zzeng/ece558/spice\_www/spice.html. Accessed 10 August 2006

# **Chapter 2 FPGA Application Design**

In wired or wireless communication systems, the information that needs to be transmitted is not only required to reach the destination but it should be error free and should make efficient use of the channel bandwidth available. Various DSP based encoding/decoding algorithms, data compression and noise filtering techniques have been developed to achieve effective and efficient data transmission with the help of FPGAs for hardware implementation. FPGA based implementations provide the flexibility of re-programming and quick delivery of the product to the market.

This chapter demonstrates the design of a simple DS-SS system including the basic building blocks such as, PN sequence generator, BPSK modulator/demodulator, BOOTH multiplier, Low Pass Filter and convolutional coding. The system is designed using Verilog HDL, simulation and functional verification of the design is performed using ModelSim® XE III 6.0d, and synthesis using Xilinx® ISE. The design is implemented and tested on Xilinx® Spartan 2E FPGA.

This chapter also demonstrates some of the algorithms and techniques used to accomplish data integrity and channel bandwidth efficiency in a communication system such as, Low Pass FIR filter using efficient Distributed Arithmetic (DA) architecture, Discrete Cosine Transform (DCT) using Scaled DCT architecture and Convolution coding and Viterbi decoding techniques. The Low Pass-Finite Impulse Response (LP-FIR) filter coefficients are calculated using MatLab FDA tool based on the given specification of the filter. The systems are designed using Verilog HDL, simulation and functional verification of the design is done using ModelSim® XE II 6.0d and synthesis using Xilinx® ISE. The designs are implemented on Xilinx® Spartan 2E FPGA.

The prerequisites for approaching this chapter would be an adequate background of basic digital communication system.

# 2.1 Design of Direct Sequence-Spread Spectrum System

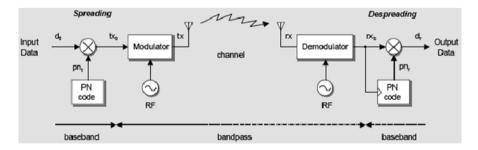

Direct Sequence-Spread Spectrum (DS-SS) is a transmission technique in which a pseudo-noise code, independent of the information data is employed as a modulation waveform to "spread" the signal energy over a bandwidth much greater than the signal information bandwidth. At the receiver the signal is *de-spread* using a synchronized replica of the pseudo-noise code. The spreading sequence in DS-SS is often called as PN sequence.

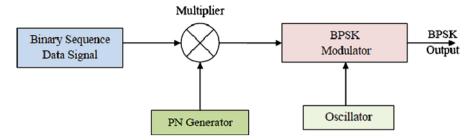

In this section, the spread signal is modulated using Binary Phase Shift keying (BPSK) modulation technique in the transmitter and on the receiver side the modulated signal is recovered using BPSK demodulation technique.

The basic building blocks of DS-SS system are shown in Fig. 2.1 [1].

# 2.1.1 PN Sequence Generator

#### 2.1.1.1 Overview of PN Sequence Generator

A Pseudo-random Noise (PN) sequence/code is a binary sequence that exhibits randomness properties but has a finite length and is therefore deterministic. PN generators are heart of every spread spectrum systems. Each symbol or bit in the sequence is called as *Chip* [2].

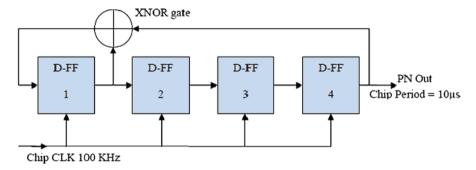

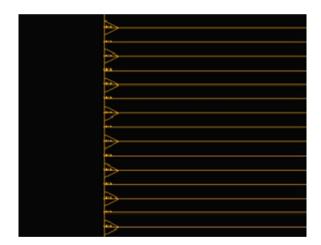

PN generators are based on Linear Feedback Shift Registers (LFSR). The contents of the registers are shifted right by one position at each clock cycle. The feedback from predetermined registers or taps to the left most register are XNOR-ed together.

LFSRs have several variables:

- The number of stages in the shift registers

- The number of taps in the feedback path

- The position of each tap in the shift registers stage

- The initial starting condition of the shift register often referred to as the "FILL" state

Fig. 2.1 Basic building blocks of DS-SS system

The longer the number of stages of shift registers in the PN generator, longer the duration of the PN sequence before it repeats. For a shift register of fixed length N, the number and duration of the sequences that it can generate are determined by the number and position of taps used to generate the parity feedback bit.

A maximum length sequence (L) for a shift register of length N is referred to as m-sequence and is defined as [3]:

$$L = 2^{N} - 1$$

,

E.g. an eight stage LFSR will have a set of m-sequences of length 255. Some of the most popular types of PN Sequence generators are:

- m-sequence codes

- · Barker codes

- · Gold codes

# 2.1.1.2 Design of PN Sequence Generator

#### Design

## Specifications:

- Clock frequency for PN sequence generator system,  $F_{nn} = 100 \text{ KHz}$ .

- LFSR length, N=4.

- LFSRs are of D-FF type.

- X-NOR gate is used for linear parity feedback to the system.

- FPGA board clock frequency,  $F_b = 50 \text{ MHz}$  (assumption)

#### Procedure:

A clock frequency of 100 KHz for PN Sequence generator is designed using a divider of 500 clock cycles of F<sub>b</sub>.

Clock divider =  $F_b/F_{pn}$  = 50 MHz/100 KHz = 500

Maximum length sequence, N=4 corresponds to 4 D-FF to realize LFSRs of the PN generator system.

Since N=4, the maximum sequence length  $L=2^4-1=15$ .

Hence the sequence repeats every 15 clock cycles.

• The Chip rate for the PN sequence generator system is calculated as follows:

Chip period,  $T_c = 1/100 \text{ KHz} = 10 \text{ }\mu\text{s}$

Chip rate,  $F_c = 100 \text{ KHz}$

• The bit period for the input data signal is calculated as follows:

Data bit period,  $T_d = Max$ . sequence Length (L) × Chip period (Tc)

For the system,  $T_d = 15 \times 10 \,\mu s$

Hence, the input data bit period for the system is,  $T_d \ge 150 \mu s$ .

Fig. 2.2 Block diagram of a PN sequence generator

#### Block Diagram

The block diagram of a PN sequence generator for the design specification is shown in Fig. 2.2.

## 2.1.1.3 Properties of PN Sequence

*Merits of using PN sequence* [4]:

1. *Balance property*: In each period of the sequence the number of binary ones differ from the number of binary zeros by at most one digit (when LFSR stage length is odd)

$$Pn = +1+1+1-1-1+1-1=+1$$

- 2. Run-length Distribution: A run is a sequence of a single type of binary digits. Among the sequence of ones and zeros in each period it is desirable that one-half the runs of each type are of length 1, about one-fourth are of length 2, one-eight are of length 3 and so on.

- 3. Autocorrelation: The origin of the name pseudo-noise is that the digital signal has an autocorrelation function which is very similar to that of a white noise signal. For PN sequences the autocorrelation has a large peaked maximum for perfect synchronization of two identical sequences (like white noise). The synchronization of receiver is based on this property.

- 4. Cross-correlation: Cross-correlation is the measure of agreement between two different codes pn<sub>1</sub> and pn<sub>2</sub>. When Cross-correlation is zero the codes are called Orthogonal. In CDMA multiple users occupy the same RF bandwidth and transmit simultaneously. When the user codes are orthogonal, there is no

Fig. 2.3 Simulation results for PN sequence generator

interference between the users after dispreading and the privacy of the communication of each user is protected.

Demerits of using PN sequence [4]:

- 1. *Synchronization*: The most sensitive aspect of DS-SS system is the synchronization of the transmitter's PN sequence to that of the receiver where an offset of even one PN chip can result in noise rather than a de-spread symbol sequence.

- 2. *Increased Bandwidth*: As the data signal is spread using PN codes at higher frequency, there is an increase in bandwidth used in the process.

- 3. *Complexity*: There is an increased complexity and computational load both in the receiver and the transmitter to spread/de-spread the signal.

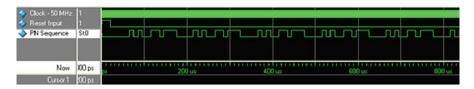

# 2.1.1.4 Simulation Results for PN Sequence Generator

The PN sequence generator is designed using Verilog HDL. Functional verification and simulation is performed using ModelSim.

The simulation results for PN sequence generator is shown in Fig. 2.3.

# 2.1.2 Transmitter for Direct Sequence-Spread Spectrum System

#### 2.1.2.1 Overview of DS-SS Transmitter System

In DS-SS transmitter, the input data bits are spread by PN sequence generator. The spreading is actually done by multiplying the data bits with that of the PN sequence code generated. The frequency of PN sequence is higher than the Data signal. After spreading, the Data signal is modulated and transmitted. There are several schemes available for modulation, viz. BPSK, QPSK, M-QAM etc. The most widely used modulation scheme is the BPSK. In this design, BPSK modulation is used to modulate and transmit the spread signal.

The basic building blocks of a simple DS-SS transmitter system are shown in Fig. 2.4.

Fig. 2.4 Block diagram of a DS-SS transmitter system

| <b>Table 2.1</b> | Truth table for the multiplier |      |  |

|------------------|--------------------------------|------|--|

| m(t)             | p(t)                           | s(t) |  |

| 0                | 0                              | 1    |  |

| 0                | 1                              | 0    |  |

| 1                | 0                              | 0    |  |

| 1                | 1                              | 1    |  |

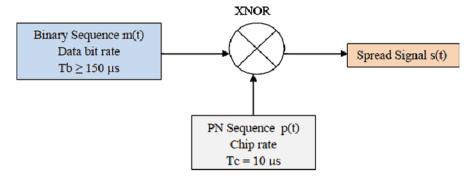

## 2.1.2.2 Design of DS-SS Transmitter

#### Multiplier Design

## Specifications:

- PN sequence Chip rate, Tc = 10 μs.

- Data signal Bit rate, Tb≥150 μs.

Let the data signal be m(t) and PN sequence p(t). The two signals are multiplied and the multiplied output is the spread signal. Truth table for the multiplier s(t) = m(t). p(t) is shown in Table 2.1.

From the truth table, it can be inferred that an XNOR gate can act as a multiplier to spread the data signal with the PN signal. Hence the block diagram for the multiplier is shown in Fig. 2.5.

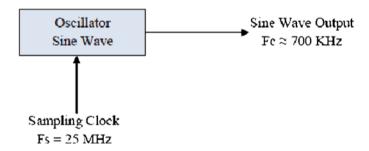

## Oscillator Design

# Specification:

- PN sequence Chip rate, Tc=10 μs.

- Carrier frequency, Fc≥5 times Chip rate.

#### Design:

The oscillator carrier sampling rate is designed

Let the Sampling rate of sine wave be Fs=25 MHz.

Fig. 2.5 Block diagram of a data and PN sequence multiplier

Fig. 2.6 Block diagram of an oscillator

- Number of samples for a full cycle of sine wave is designed Let the number of samples for a full cycle be N = 36.

- The oscillator is designed to generate sine wave of carrier frequency Fc Fc  $\geq 5(1/T_c) = 5(1/10\mu s) = 500 \text{KHz}.$

For the above design with sampling rate 25 MHz and 36 samples per cycle, the carrier frequency,  $Fc = 25 \text{ MHz}/36 \approx 700 \text{ KHz}$ . The oscillator is implemented using a Look-Up-Table (LUT) of nine samples and the logic is design in order to oscillate generating a sine wave.

The block diagram of the oscillator as per the design is shown in Fig. 2.6.

#### **BPSK Modulator Design**

## Specification:

- Spread binary sequence is the input to the system

- Oscillator carrier sine wave of frequency, Fc≈700 KHz

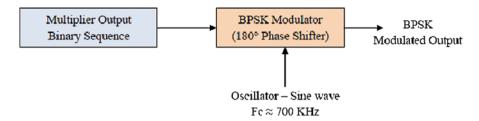

Fig. 2.7 Block diagram of BPSK modulator

Fig. 2.8 Simulation results for DS-SS transmitter system

#### Design:

The BPSK modulator is designed using the spread binary sequence as the input to the system and the carrier frequency  $F_c$ . The logic is implemented in such a way that the phase of the sine wave is shifted by  $180^\circ$  whenever the input binary bit changes.

The block diagram of the BPSK Modulator as per the design is shown in Fig. 2.7.

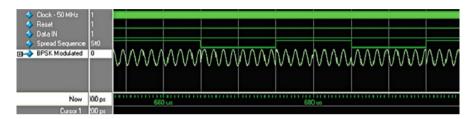

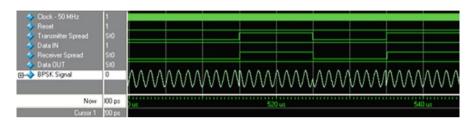

#### 2.1.2.3 Simulation Results for DS-SS Transmitter

The DS-SS transmitter is designed using Verilog HDL. Functional verification and simulation is done using ModelSim. The simulation results for DS-SS transmitter is shown in Fig. 2.8.

# 2.1.3 Receiver for Direct Sequence-Spread Spectrum System

#### 2.1.3.1 Overview of DS-SS Receiver System

In DS-SS receiver, the input to the system is the BPSK modulated signal. This signal would have been affected by noise and other interference in the communication channel. The DS-SS receiver should be designed carefully to reproduce the data signal with least error.

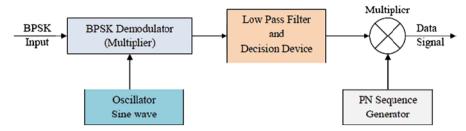

Fig. 2.9 Block diagram of a DS-SS receiver system

The BPSK modulated input signal is multiplied by the locally generated carrier wave by the oscillator. The multiplied signal is then passed through the low pass filter to get low frequency components only. A decision device is used to approximate the signal to binary sequence. This binary sequence is the spread sequence of the data signal.

The most sensitive part of the DS-SS receiver is the synchronization of the locally generated PN sequence and the sequence obtained from the decision device [3]. Even a single bit mismatch may lead to noise instead of the data signal. Suitable technique is used to achieve synchronization and multiply the local PN sequence code with that of the received PN code. The Data signal is obtained after the multiplication process.

In this design, since transmitter and receiver uses common clock on the same FPGA board, the delay in the receiver is considered and modeled appropriately. No specific synchronization technique is used.

The block diagram of a simple DS-SS receiver system is shown in Fig. 2.9.

#### 2.1.3.2 Design of DS-SS Receiver

#### **BPSK Demodulator Design**

#### Specifications:

- BPSK modulated signal is the input to the system

- Oscillator carrier sine wave of frequency, Fc≈700 KHz

The input BPSK signal is multiplied with the carrier sine wave generated from the local oscillator. The design and implementation of the signed BOOTH multiplier is discussed in the following section.

The multiplied output will have higher frequency components and channel noise as well. The high frequency components are eliminated using a suitable Low Pass Filter. Design of rectangular window Low-Pass FIR filter is also discussed in the following section.

The filtered low frequency component will have distortion in the signal. Hence a suitable 'Decision Device' is used to smoothen to binary sequence.

#### **BOOTH Multiplier Design**

The BPSK modulated input signal is multiplied with the carrier sine wave generated using the local oscillator. A signed multiplier is designed using BOOTH multiplier algorithm [5].

The BOOTH algorithm used to implement the signed multiplier is as follows:

- The multiplicand X and multiplier Y is loaded into a register. Bit adjustment is

made with X and Y so that bits length of X and Y are equal. Bit '0' is padded in

order to achieve it

- An accumulator is used to store the result. The length of the accumulator should be twice the length of multiplicand or multiplier. A=2X or 2Y

- The multiplicand X is loaded into the accumulator from LSB

- A dummy bit of 0 is appended with the accumulator A at the LSB

- During the multiplication operation, the pair of LSB of the accumulator and the dummy bit is considered to follow further arithmetic operations

- Depending on the bit pair obtained in the previous step, following operations are performed:

- o "00" Arithmetic shift right of the Accumulator.

- o "01" Add multiplier Y to the Accumulator A (from MSB of A) and Arithmetic shift right of Accumulator.

- o "10" Subtract multiplier Y from the Accumulator A (from MSB of A) and Arithmetic shift right of Accumulator.

- "11" Arithmetic shift right of the Accumulator.

Shift operations are performed along with dummy bit.

The above operations are continued till MSB of multiplicand X is shifted off from the accumulator A.

In this section, 5-bit signed BOOTH multiplier is designed and implemented.

Low Pass Filter and Decision Device Design

#### Specifications:

- The multiplied output from the BPSK demodulator is the input to this system

- A Low Pass Filter with cutoff frequency, f=105 KHz

- Oscillator carrier wave sampling rate, Fs = 25 MHz

#### Design:

A Rectangular window FIR filter is designed with a cutoff frequency, f=105 KHz. Let the length of impulse response for the filter, N=2.

The desired response of the ideal Low-pass filter is given by,

$$H_d(e^{jw}) = 1, 0 \le f \le 105 \text{ KHz}, \text{ otherwise } 0$$

The normalized angular frequency,  $\omega_c = 2\pi F/Fs = 8.4\pi \times 10^{-3}$

$$H_d(e^{jw}) = 1, 0 \le \omega \le \omega_c; 0, \omega_c \le \omega \le \pi$$

The filter coefficients are given by,

$$h_{d}(n) = \sin(8.4\pi \times 10^{-3} \text{ N}) / (\pi \text{ N}), \text{ where N } \neq 0.$$

Therefore, the filter coefficients are,

$$h(0) = 8.40 \times 10^{-3}$$

and  $h(1) = 8.39 \times 10^{-3}$

In this design, one sample of the signal is stored in a register and then it's added with the next sample. The filtered output samples obtained is then processed by the Decision Device. The output of the Decision Device is held High (1) when the output of the filter is non-negative otherwise it's made Low (0).

#### 2.1.3.3 Noise Models and Synchronization

*Noise models* [1]:

- Multi Path Channels: In wireless channels there exists often multi path propagation. Since there are more than one path from the transmitter to the receiver. Such multi paths may be due to (a) atmospheric reflection or refraction (b) Reflections from ground, buildings or other objects. Corrective actions are taken to eliminate noise due to multi path channels using appropriate synchronization techniques.

- Jamming: The goal of the jammer is to disturb the communication of his adversary. Protection against jamming waveforms is provided by purposely making the information-beating signal occupy a bandwidth far in excess of the minimum bandwidth necessary to transmit it. This has the effect of making the transmitted signal assume a noise-like appearance so as to blend into background. The transmitted signal thus enabled to propagate through the channel undetected by anyone who may be listening. Spread spectrum is a method of "camouflaging" the information bearing signal.

In this design, the noise effect is not modeled as the transmitter and receiver is on the same FPGA board without any air interface.

*Synchronization techniques* [1]:

For proper operation of DS-SS system, the locally generated PN sequence in the receiver is synchronized to the PN sequence of the transmitter generator in both its

Fig. 2.10 Simulation results for DS-SS receiver system

Fig. 2.11 Simulation results for DS-SS modem

rate and position. A slight misalignment in the sequence results in noise instead of data signal.

The process of synchronizing the locally generated PN sequence with the received PN sequence is usually accomplished in two steps. The first step called *acquisition* consists of bringing the two spreading signals into coarse alignment with one another. Once the received PN sequence has been acquired, the second step called *tracking* takes over and continuously maintains the best possible waveform fine alignment by means of a feedback loop. This is essential to achieve highest correlation power and thus highest processing gain (SNR) at the receiver.

In this design, synchronization technique is not modeled since the same clock and PN sequence for receiver and transmitter is implemented on the same FPGA board. A delay of one clock pulse is modeled while multiplying the PN code in the receiver to compensate the filtering delay of one sample.

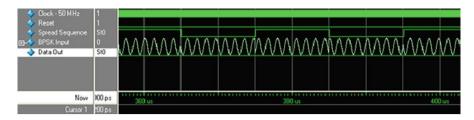

#### 2.1.3.4 Simulation Results for DS-SS Receiver

The DS-SS receiver is designed using Verilog HDL [6]. Functional verification and simulation is done using ModelSim.

The simulation results for DS-SS receiver is shown in Fig. 2.10.

The simulation results for DS-SS modem is shown in Fig. 2.11. The synthesis report obtained from Xilinx ISE is also shown in Fig. 2.12. The modem can operate at a maximum frequency of 64 MHz on Xilinx Spartan 2E FPGA.

```

HDL Synthesis Report

Macro Statistics

: 17

# Adders/Subtractors

10-bit adder

: 10

: 4

: 2

: 5

: 33

: 29

: 2

: 33

: 5

: 5

: 5

: 5

: 5

11-bit adder

32-bit adder

5-bit adder

# Counters

32-bit up counter

32-bit updown counter

# Registers

1-bit register

10-bit régister

5-bit register

# Comparators

33-bit comparator greatequal

# Multiplexers

11-bit 4-to-1 multiplexer

# Xors

1-bit xor2

```

Fig. 2.12 Synthesis report for DS-SS modem

## 2.2 FIR Filter Design

## 2.2.1 Concepts of FIR Filter

A discrete-time filter produces a discrete-time output sequence for the discrete-time input sequence. In the Finite Impulsive Response (FIR) system, the impulse response sequence is of finite duration, i.e. it has a finite number of non-zero terms and hence the filter coefficients are also constant. The response of the FIR filter depends only on the present and past input samples (a causal system). Thus making the system always stable.

The difference equation for length 'M' FIR filter is given by [4],

$$y(n) = b_0 \times (n) + b_1 \times (n-1) + b_2 \times (n-2) + b_3 \times (n-3) + \dots + b_{M-1} \times (n-M+1)$$

$$Y(n) = \sum_{K=0}^{M-1} b_K \times (n-K)$$

where,  $[b_{i}]$  is the set of filter coefficients.

Some of the important characteristics of FIR digital filter are as follows [4]:

- They can have an exact linear phase

- They are always stable

- The design methods are generally linear

- They can be realized efficiently in hardware

- The filter start-up transients have finite duration

- The filter coefficients are constant for the given order of the filter

| Transfer function | Coefficients | Transfer function | Coefficients |

|-------------------|--------------|-------------------|--------------|

| h(0)              | 0.0328       | h(8)              | 0.5763       |

| h(1)              | 0.0816       | h(9)              | -0.0550      |

| h(2)              | -0.0065      | h(10)             | -0.0694      |

| h(3)              | -0.0047      | h(11)             | 0.0847       |

| h(4)              | 0.0847       | h(12)             | -0.0047      |

| h(5)              | -0.0694      | h(13)             | -0.0065      |

| h(6)              | -0.0550      | h(14)             | 0.0816       |

| h(7)              | 0.5763       | h(15)             | 0.0328       |

|                   |              |                   |              |

**Table 2.2** Filter coefficients for LP FIR filter with order 16

Fig. 2.13 Frequency response (Magnitude) for the designed LP FIR filter

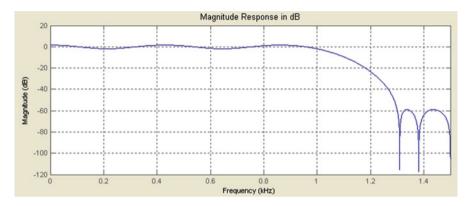

In this section a Low-Pass FIR filter is designed using MatLab FDA tool for the given specifications. Simulated using ModelSim® and implemented using Xilinx® 2E FPGA.

# Low Pass FIR Filter Design

The Low Pass FIR (LPF) specifications given in the assignment are,

- F<sub>pass</sub> = 1 KHz, F<sub>stop</sub> = 1.3 KHz

Pass band ripple = 3 dB, Stop band ripple = 60 dB

#### Assuming,

- Sampling frequency of the input signal, F<sub>s</sub> = 3 KHz.

- FIR Filter design method: Equiripple with density factor 16.

The filter coefficients are obtained using MatLab FDA tool for the given specification. The order of the filter, N = 16. The filter coefficients h(n) are as shown in Table 2.2. The frequency response for the given filter specification is shown in Fig. 2.13

Fig. 2.14 Block diagram to illustrate the functional operation of DA architecture

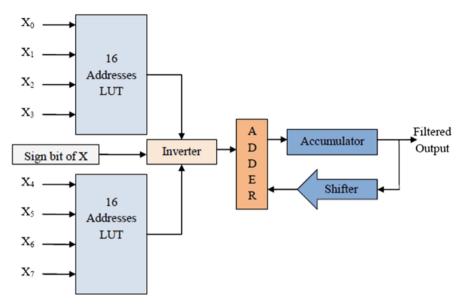

#### 2.2.3 Distributed Arithmetic Architecture

Distributed Arithmetic (DA) is an important technique to implement digital signal processing functions in FPGAs. DA provides an approach for multiplier-less implementation of DSP systems. It is an algorithm that can perform multiplication with Look-Up Table (LUT) based schemes. DA specifically targets the sum of products (also referred to as the vector dot product) computation that is found in many of the important DSP filtering and frequency transforming functions [7].

In this section, LP FIR filter is designed and implemented using DA architecture. By observing the filter coefficients in Table 2.2, the second half (8–15) of filter coefficients are mirror image of the first half (0–7). Hence the SOP for second half can be accessed from the first half by re-ordering the input bits appropriately. The first half (0–7) coefficients can be broken into two parts and SOP can be calculated and stored in two different blocks. Hence, two LUTs of length 16 are sufficient to store the SOP for the obtained filter coefficients.

The basic functional operation of DA architecture is shown in Fig. 2.14.

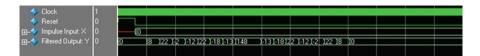

# 2.2.4 Simulation and Synthesis Results

The LP FIR filter is designed using Verilog HDL. The design is simulated using ModelSim<sup>®</sup>. The impulse response for the LP FIR filter system is shown in Fig. 2.15. In this design, fixed point representations of real numbers are used. Filtered output

Fig. 2.15 Simulation results for impulse response for the LP FIR filter system

HDL Synthesis Report Macro Statistics # ROMs : 4 16x13-bit ROM # Adders/Subtractors 13-bit adder 22-bit adder carry in # Counters : 1 4-bit up counter : 1 # Registers • 20 : 1 1-bit register : 16 10-bit register 13-bit register : 1 22-bit register : 2 # Multiplexers : 16 1-bit 10-to-1 multiplexer : 16 # Logic shifters 22-bit shifter logical left : 1 32-bit shifter logical left

------

Fig. 2.16 HDL synthesis report for LP FIR filter design

values have lower 8 bits representing decimal part. Hence the exact filtered output values from the simulation results are calculated as follows:

```

Y = (8,22,-2,-12,22,-18,-13,148,148,-13,-18,22,-12,-2,22,8)/2^{8}

Y = (0.0312,0.8593,-0.0078,-0.0468,0.8593,-0.0703,-0.0507,0.5781,0.5781,-0.0507,-0.0703,0.8593,-0.0468,-0.0078,0.8593,0.0312)

```

The design is synthesized and implemented on Xilinx® Spartan 2E FPGA. The HDL synthesis report is shown in Fig. 2.16.

## 2.3 Discrete Cosine Transform Algorithms

# 2.3.1 Concepts of DCT

The Discrete Cosine Transform (DCT) is a technique that converts a spatial domain waveform into its constituent frequency components as represented by a set

of coefficients. The process of reconstructing a set of spatial domain samples is called the Inverse Discrete Cosine Transform (IDCT). The equation for 1-D N-point DCT is given by [8],

$$X(k) = \alpha(k) \sum_{n=0}^{N-1} x(n) \cos[\frac{\pi(2n+1)k}{2N}] \qquad 0 \le k \le N-1$$

where,

$$\alpha(0) = \sqrt{\frac{1}{N}}, \ \alpha(k) = \sqrt{\frac{2}{N}} \text{ for } 1 \le k \le N - 1$$

One-Dimensional DCT has most often been used in two-dimensional DCT by employing the row-column decomposition which makes it suitable for hardware implementation. Typically the DCT coefficients produced have most of the block's energy in a few frequency domain elements and hence quantization and coding is applied after DCT to provide lossless as well as lossy actual compression [8].

For data compression of image/video frames, usually a block of data is converted from spatial domain samples to another domain (usually frequency domain) which offers more compact representation. DCT technique is used in a wide range of signal and image processing applications. Some of the most popular applications are [8],

- JPEG and JPEG2000 image compression standards

- MPEG digital video standards

- H.261 and H.263 video conferencing standards

- Progressive Image Transmission (PIT) systems: teleconferencing, medical diagnostic imaging and security services

#### 2.3.2 DCT Architectures on FPGA

The DCT can be implemented on FPGA using various architectures. Some of the popular one's reported in [9] are discussed below:

• Distributed Arithmetic: The N-points DCT can be considered as N parallel filters. The DCT on the array requires N shift registers for parallel-to-serial conversion, N LUT memories and N shift-accumulators. All the N memories receive the same address. One shift-register and a shift-accumulator are each mapped to an add-shift cluster, while the LUT is mapped to a part of a memory cluster.

*Area usage*: 8 shift registers + 8 ROMs + 8 Accumulators

• *Mixed ROM*: The 8-point 1D-DCT can be expressed as the product of an 8×8 matrix by an eight element column vector. Through algebraic manipulations, this matrix can be reduced to 4×4 matrix. Hence, the number of words per ROM is reduced to only 16 but some overhead has been incurred in the form of adders to calculate the address of the ROMs.

*Area usage*: 4 adders + 4 subtractions + 8 shift registers + 8 accumulators + 8 ROMs

• CORDIC Rotator based: The DCT computation is done using CORDIC rotator [10]. Since the memory is an integral part of the DA, and ROM size increases exponentially with respect to vector size N. Many techniques have been developed for reducing the size of ROM. The CORDIC algorithm reformulates the 1-D DCT so that the ROM size is reduced to a fix size of four words, independent of the bandwidth of the input data. The DA functionality is implemented by converting parallel data to serial through shift registers and using this data to formulate the address of the memories. This implementation requires 6-CORDIC and 16 butterfly adders for an 8-point 1-D DCT. The CORDIC rotators are implemented through ROM and shift accumulators, while butterfly adders are implemented through add-shift clusters [11].

Area usage: 8 adders+8 subtractions+8 shift registers+12 accumulators+12 ROMs

• *Skew circular convolution*: This technique starts with re-ordering the input sequences. Then skew circular convolutions are performed on the reordered inputs, which give odd-indexed transformed sequence. The transformed sequences are re-ordered for the proper output sequences.

Area usage: 4 adders+4 subtractions+8 shift registers+8 accumulators+8 ROMs

### 2.3.3 Scaled 1-D 8-Point DCT Architecture

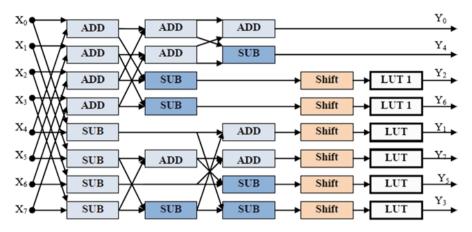

Since using LUTs results in a very efficient and regular structure suitable for VLSI implementation, especially on the FPGAs, there has been great interest in developing similar kind of LUT based DCT architecture. The Scaled DCT architecture is also a LUT based design. The architecture is primarily designed by making mathematical and trigonometric manipulation using 1-D 8-point DCT equation on eight input data samples. In this design, LUT based Distributed Arithmetic architecture is used. The basic building blocks of this architecture are [9]:

- 20 butterfly adders

- 12 shift registers

- 10 LUTs

The constant scale factor (Y0 and Y4) is not considered in this implementation as that can be combined with the quantization constants without requiring any additional hardware such as LUTs. The simplified 1-D 8-point DCT equations are as shown below:

$$Y_0 = \left[ \sqrt{2} \times (X_0 + X_1 + X_2 + X_3 + X_4 + X_5 + X_6 + X_7) \right] / 4$$

$$Y_1 = \left[ (X_0 - X_7) \times A + (X_1 - X_6) \times B + (X_2 - X_5) \times C + (X_3 - X_4) \times D \right] / 2$$

$$Y_2 = \left[ (X_0 + X_7 - X_3 - X_4) \times E + (X_1 + X_6 - X_2 - X_5) \times F \right] / 2$$

Fig. 2.17 Block diagram of scaled DCT architecture

$$\begin{split} Y_3 &= \left[ (X_0 - X_7) \times B + (X_6 - X_1) \times D + (X_5 - X_2) \times A + (X_4 - X_3) \times C \right] / 2 \\ Y_4 &= \left[ \sqrt{2} \times (X_0 - X_1 - X_2 + X_3 + X_4 - X_5 - X_6 + X_7) \right] / 2 \\ Y_5 &= \left[ (X_0 - X_7) \times C + (X_6 - X_1) \times A + (X_2 - X_5) \times D + (X_3 - X_4) \times B \right] / 2 \\ Y_6 &= \left[ (X_0 + X_7 - X_3 - X_4) \times F + (X_2 + X_5 - X_1 - X_6) \times E \right] / 2 \\ Y_7 &= \left[ (X_0 - X_7) \times D + (X_6 - X_1) \times C + (X_2 - X_5) \times B + (X_4 - X_3) \times A \right] / 2 \\ For N &= 8, \\ A &= \cos(\pi / 16) \\ B &= \cos(3\pi / 16) \\ C &= \cos(5\pi / 16) \\ D &= \cos(7\pi / 16) \\ E &= \cos(\pi / 8) \\ F &= \cos(3\pi / 8) \end{split}$$

The constant values A, B, C, D, E and F that is required to be multiplied with input X is performed by LUT based Distributed Arithmetic architecture. The block diagram of Scaled DCT architecture for 1-D 8-point samples is shown in Fig. 2.17.

## 2.3.4 Simulation and Synthesis Results

In this section, 1-D 8-point DCT is designed using Scaled DCT architecture and coded in Verilog HDL. The design is simulated using ModelSim<sup>®</sup>. The DCT for the input samples, X = (4, 2, 8, 4, 4, 6, 6, 6) is as shown in Fig. 2.18.

| ◆ Clock                | 1    |    |       |   |       |  |

|------------------------|------|----|-------|---|-------|--|

| Reset                  | 0    |    |       |   |       |  |

| ⊕                      | 4    |    | 4     |   |       |  |

| ⊞-4 ×1                 | 2    |    | 2     |   |       |  |

| <b>⊞</b> -∜ X2         | 8    |    | 8     |   |       |  |

| <u>-</u> ×3            | 4    |    | 4     |   |       |  |

| ⊕- <b>∜</b> ×4         | 4    |    | 4     |   |       |  |

| <b>⊕</b> -∜ X5         | 6    |    | 6     |   |       |  |

| <b>⊞</b> -∜ ×6         | 6    |    | 6     |   |       |  |

| <b>⊞</b> -∜ X7         | 6    |    | 6     |   |       |  |

| <b>⊞</b> Y0            | 5120 | (0 | (512  | 0 |       |  |

| ⊕                      | -544 | (0 |       |   | )-544 |  |

| <b>⊞</b> - <b>∜</b> Y2 | -58  | (0 |       |   | ).58  |  |

| <b>⊞</b> - <b>∜</b> Y3 | -372 | (0 |       |   | )-372 |  |

| <b>⊞</b> - <b>♦</b> Y4 | -512 | (0 | (-512 |   |       |  |

| ⊕- <b>∜</b> Y5         | 404  | (0 |       |   | (404  |  |

| ⊕                      | 807  | (0 |       |   | (807  |  |

| ⊕- <b>∜</b> Y7         | 439  | (0 |       |   | (439  |  |

|                        |      |    |       |   |       |  |

Fig. 2.18 Simulation results for 1-D 8-point DCT

$$Y = (5120 / \sqrt{2}, -544, -58, -372, -512 / \sqrt{2}, 404, 807, 439)$$

In this design, fixed point representations of real numbers are used. DCT output values have lower eight bits representing decimal part of DCT output. Hence the exact DCT output values from the simulation results are calculated as follows:

$$Y = (5120 / \sqrt{2}, -544, -58, -372, -512 / \sqrt{2}, 404, 807, 439) / 2^{8}$$

$$Y = (14.1421, -2.0882, -0.2242, -1.4221, -1.4142, 1.6011, 3.1543, 1.7475)$$

This design is implemented on Xilinx® Spartan 2E FPGA. The HDL [13] synthesis report is shown in Fig. 2.19.

# 2.4 Convolution Codes and Viterbi Decoding

# 2.4.1 Concepts of Convolution Codes

Forward Error Correction (FEC) technique is used to improve the capacity of channel by adding some carefully designed redundant information to the data that is transmitted over the communication channel. The process of adding this redundant information is known as *channel coding*.

| HDL Synthesis Report        |       |

|-----------------------------|-------|

|                             |       |

| Macro Statistics            |       |

| # ROMs                      | : 10  |

| 4x16-bit ROM                | : 10  |

| # Adders/Subtractors        | : 31  |

| 16-bit adder                | : 13  |

| 4-bit adder carry out       | : 4   |

| 5-bit adder                 | : 10  |

| 5-bit adder carry out       | : 3   |

| 6-bit adder carry out       | : 1   |

| # Counters                  | : 1   |

| 4-bit up counter            | : 1   |

| # Registers                 | : 113 |

| 1-bit register              | : 91  |

| 16-bit register             | : 8   |

| 5-bit register              | : 14  |

| # Multiplexers              | : 10  |

| 1-bit 5-to-1 multiplexer    | : 10  |

| # Logic shifters            | : 12  |

| 16-bit shifter logical left | : 12  |

|                             |       |

Fig. 2.19 HDL synthesis report for 1-D 8-point DCT

Fig. 2.20 Block diagram of convolutional encoder for a rate ½, constraint length K=3

Convolutional coding and Block coding are the two major forms of channel coding. Convolutional codes operate on serial data, one or a few bits at a time. Block codes operate on relatively large message blocks. There are a variety of useful convolutional and block codes, and a variety of algorithms for decoding the received coded information sequences to recover the original data. Convolutional encoding with Viterbi decoding is a FEC technique that is particularly suited to a channel in which the transmitted signal is corrupted mainly by Additive White Gaussian Noise (AWGN) [12].

The technique of convolutional coding transforms a binary message into a sequence of symbols to be transmitted. Upon reception, the received information must be related back to the original message bits. If there are no errors the process of decoding is readily accomplished. In general, convolutional coding techniques are applied to very long messages, such as the continuous stream of data from a satellite television transmitter.

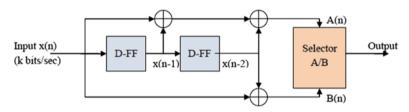

A convolutional encoder with two shift registers is shown in Fig. 2.20.

| Table 2.3         State transition           table for the convolutional | Current |

|--------------------------------------------------------------------------|---------|

| encoder                                                                  | 00      |

|                                                                          | 01      |

| Current state | Output symbols, if input=0 | Output symbols, if input=1 |

|---------------|----------------------------|----------------------------|

| 00            | 00                         | 11                         |

| 01            | 11                         | 00                         |

| 10            | 10                         | 01                         |

| 11            | 01                         | 10                         |

The system block diagram can be expressed with the following equations:

$$A(n) = x(n) + x(n-1) + x(n-2)$$

$$B(n) = x(n) + x(n-2)$$

The basic building components of the convolutional encoder are flip-flops comprising the shift registers and Exclusive-OR gates comprising the associated Modulo-Two adders. The number of shift registers in the encoder generating the encoded sequence determines the capability of the decoder to detect and correct number of bit errors received on the receiver in the obtained encoded sequence of data.

In this encoder, data bits are provided at a rate of 'k' bits per second. Channel symbols are output at the rate of n=2k symbols per second. The constraint length K=3 is the length of convolutional encoder, i.e., how many k-bit stages are available to feed the combinatorial logic that produces the output symbols. The input bit is stable during the encoder cycle. The encoder cycle starts when an input clock edge occurs. When the input clock edge occurs, the output of the left-hand flip-flop is clocked into the right-hand flip-flop, the previous input bit is clocked into the left-hand flip-flop and a new input bit becomes available. Then the outputs of the upper and lower modulo-two adders become stable. The output selector cycles through two states. In the first state, it selects and outputs the output of the lower modulo-two adder.

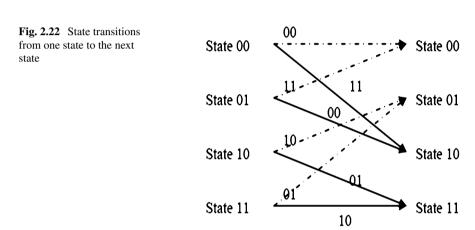

The state transition table that lists the channel output symbols, given the current state and the input data is shown in Table 2.3.

#### 2.4.2 Viterbi Decoder

A Viterbi decoder uses the Viterbi algorithm for decoding bit stream that has been encoded using Convolutional codes. There are other algorithms for decoding a convolutional encoded stream (Ex: Fanon algorithm). The Viterbi algorithm is the most resource-consuming but it does the maximum likelihood decoding [12]. Viterbi decoding has the advantage that it has a fixed decoding time. It is well suited for hardware decoder implementation. But its computational requirements grow exponentially as a function of constraint length. So it is usually limited in practice to constraint lengths of  $K \leq 10$ .

Fig. 2.21 Trellis diagram for Viterbi decoding with encoder rate  $\frac{1}{2}$  and K=3

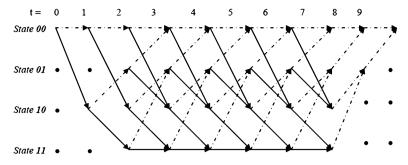

The most important concept to aid in understanding the Viterbi algorithm is the Trellis diagram. The Trellis diagram for the convolutional encoder rate  $\frac{1}{2}$ , constraint length K=3 is shown in Fig. 2.21.

The four possible states of the encoder are depicted as four rows of horizontal dots. There is one column of four dots for the initial state of the encoder and one for each time instant during the message. For a 4-bit message with two encoder memory flushing bits, there are six time instants in addition to t=0, which represents the initial condition of the encoder. The solid lines connecting dots in the diagram represent state transitions when the input bit is a one. The dotted lines represent state transitions when the input bit is a zero. The expanded version of the transition between one time instant to the next is shown in Fig. 2.22. Notice the correspondence between the arrows in the Trellis diagram and the state transition diagram. Since the initial condition of the encoder is State 00, and the two memory flushing bits are zeros, the arrows start out at State 00 and end up at the same state [12].

Each time when a pair of channel symbols is received, the metric- Hamming distance between the received channel symbol pair and the possible channel symbol pairs is calculated for each state. The Hamming distance is computed by simply counting how many bits are different between the received channel symbol pair and the possible

Fig. 2.23 Simulation results for Viterbi decoding with no error in received channel data

channel symbol pairs. The results can only be zero, one, or two. The metrics computed at each time instant for the paths between the states at the previous time instant and the sates at the current time instant are called branch metrics. For the first time instant, the results are stored as "accumulated error metric" values associated with the states. For the second time instant onwards, the accumulated error metrics will be computed by adding the previous accumulated error metrics to the current branch metrics. The process is continued for k+m symbols (for k bits message and k shift registers). The smallest accumulated error metric in the final state indicates how many channel symbol errors occurred. This survival path which has the least accumulated error metric is selected. Original message bits are recreated by interpreting the bits from the solid and dotted arrows from the survival path in the Trellis diagram. The two flushing bits at the end are discarded from the recreated message bits.

In this section, Viterbi decoder for 4-bit message is designed using Viterbi algorithm [12].

- Four registers of 6-bit width are used to store the survival path at each state transition.

- Four registers of 4-bit width are used to store the accumulated error metrics at each state.

- At the end of the last state, the survival path having the least accumulated error metrics is used to reproduce the estimated input message bits from the survival path register.

# 2.4.3 Simulation and Synthesis Results

In this section, Convolutional encoder is designed using two shift-registers and Viterbi decoder is designed using Accumulated Error Metrics algorithm. The design is simulated using ModelSim<sup>®</sup>.

Assuming the input data to the convolutional encoder is x = (1001), the encoded sequence is,  $e = (11\ 10\ 11\ 11\ 10\ 11)$ . Following different cases are simulated to test the Viterbi decoder design:

1. No error in the received data from the channel. The simulation result for this case is shown in Fig. 2.23.

Received data: 11 10 11 11 10 11

2. One bit error in the received data from the channel. The simulation result for this case is shown in Fig. 2.24.

Fig. 2.24 Simulation results for Viterbi decoding with one bit error in received channel data

Figure 2.25 Simulation results for Viterbi decoding with two bits error in received channel data

------

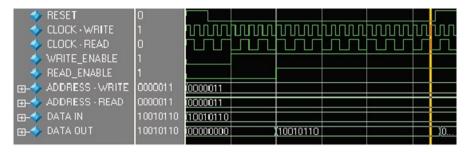

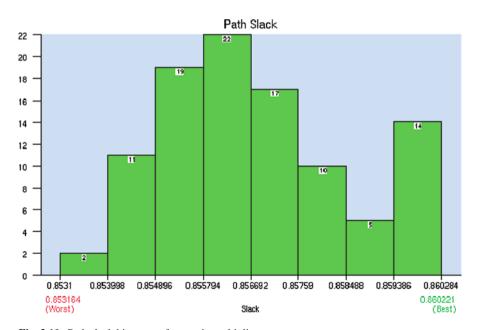

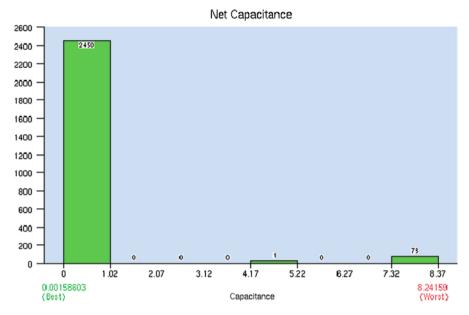

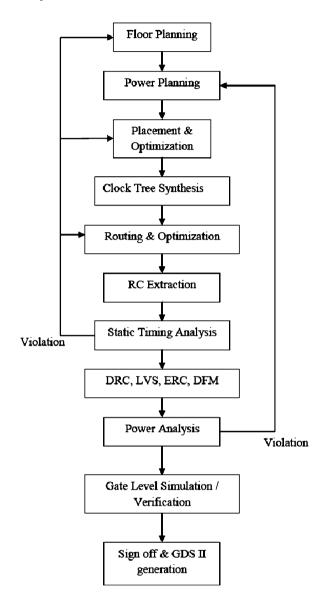

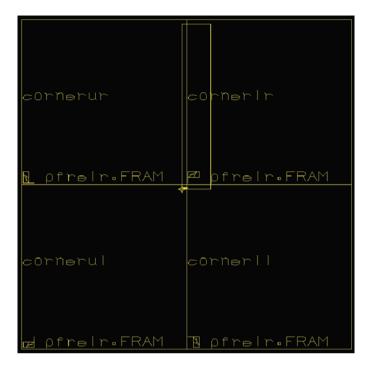

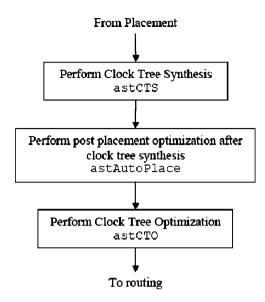

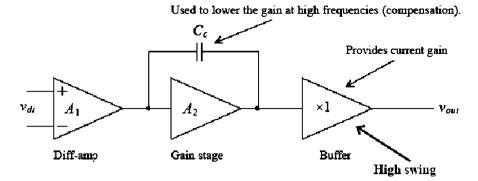

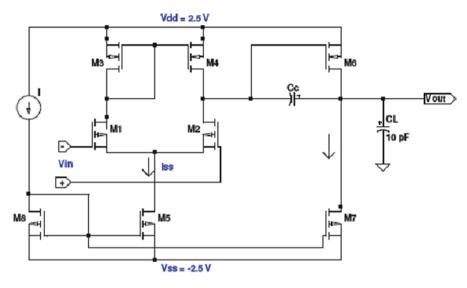

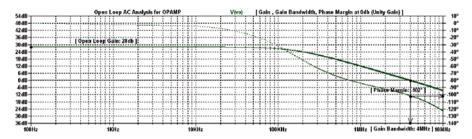

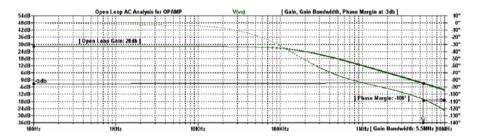

```