Swarup Bhunia Saibal Mukhopadhyay *Editors*

# Low-Power Variation-Tolerant Design in Nanometer Silicon

# Low-Power Variation-Tolerant Design in Nanometer Silicon

Swarup Bhunia · Saibal Mukhopadhyay Editors

Low-Power Variation-Tolerant Design in Nanometer Silicon

Editors

Swarup Bhunia

Department of Electrical Engineering and Computer Science

Case Western Reserve University

Cleveland, OH 44106-7071, USA skb21@case.edu

Saibal Mukhopadhyay School of Electrical and Computer Engineering Georgia Institute of Technology Atlanta, GA 30332-0250, USA saibal@ece.gatech.edu

ISBN 978-1-4419-7417-4 e-ISBN 978-1-4419-7418-1 DOI 10.1007/978-1-4419-7418-1 Springer New York Dordrecht Heidelberg London

Library of Congress Control Number: 2010938792

#### © Springer Science+Business Media, LLC 2011

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

# **Preface**

The energy required for running integrated circuits (ICs) is increasing in every new generation of electronic systems. At the same time the manufacturing process used to build these ICs are becoming less deterministic. Hence, low-power design under large parameter variations has emerged as an important challenge in the nanometer regime. The book, for the first time, integrates description of low power and variation issues and provides design solutions to simultaneously achieve low power and robust operation under variations.

Design considerations for low power and robustness with respect to variations typically impose contradictory requirements. Power reduction techniques such as voltage scaling, dual-threshold assignment and gate sizing can have large negative impact on parametric yield under process variations. This book introduces the specific challenges associated with low power and variation-tolerant design in the nanometer technology regime at different levels of design abstraction. It considers both logic and memory design aspects and encompass modeling, analysis as well as design methodology to simultaneously achieve low power and variation tolerance while minimizing design overhead. The issue of device degradation due to aging effects as well as temporal variation in device parameters due to environmental fluctuations are also addressed. Micro-architecture level design modifications, subthreshold design issues, statistical design approaches, design of low-power and robust digital signal processing (DSP) hardware, analog and mixed-signal circuits, reconfigurable computing platforms such as field programmable gate array (FPGA) are covered. The book also discusses emerging challenges at future technology nodes as well as methods industrial and academic researchers and engineers are developing to design low-power ICs under increasing parameter variations.

# Why a New Book

Designing low power but reliable ICs using inherently unreliable process is a key challenge in current generation IC design. The problem is escalating in every new generation of ICs. The students, industrial/academic researchers, and practicing engineers need to have basic understanding of this problem and knowledge of

vi Preface

existing and emerging methods to enable designing ICs using nanoscale processes. Currently, there exists no book that specifically addresses this problem. Considering the importance of the topic, the book compiles outstanding contributions from prominent personalities in this area covering different aspects of low power and variation-tolerant design.

#### **Unique Features**

- Introduction to the most important challenges in the area of low power and variation-tolerant IC design in nanoscale technologies.

- A holistic view of the solution approaches at different levels of design abstraction covering device, circuit, architecture, and system.

- Comprehensive coverage on both logic and memory circuits.

- Comprehensive coverage of system-level design micro-architecture, DSP, mixed-signal, and FPGA.

- Modeling and analysis of different variation effects (die-to-die and within-die, process and temporal) on low power designs.

- Description of ultralow power and robust subthreshold design aspects.

- Description of technology scaling trends, emerging challenges, and future research directions.

# **Organization and Overview of the Content**

This book is organized in four integrated parts, each covering a major aspect of low power and variation tolerance. The content of each part as well as each chapter in the part is designed to provide necessary background to the readers new in the field as well as detailed discussions on state-of-the-art techniques for the experts in the topic. Part I is dedicated to provide the reader a comprehensive background of the two complementary problems – power dissipation and parameter variations. The backgrounds are supplemented with description of existing techniques for power estimation and optimization as well as variation modeling and characterization. The rest of the book aims at establishing the principle that the challenge of low power under process variations needs to be addressed at all levels of design abstraction, i.e., from circuits to logic to micro-architecture to system. Part II focuses on circuit and logic level techniques including computer-aided design methods; Part III discusses system-level methods for low power under process variations for microprocessors, digital signal processors, and analog/RF/mixed-signal systems. Part IV discusses the power and variation challenges for reconfigurable computing platforms and unique design methods to address them, particularly focusing on Field-Programmable-Gate-Arrays (FPGA). We will now provide a brief overview of each part of this book and the corresponding chapters.

# Part I: Physics of Power Dissipations and Parameter Variations

Part I provides a comprehensive background of the two complementary problems – power dissipation and variations. This part is organized in two chapters – one dedicated to basics of power dissipation and second dedicated to the basics of process variations. Chapter 1 discusses the different sources of variation in CMOS technologies and presents an overview of how to characterize these variations. The chapter covers various sources of process variation during manufacturing; sources of environmental variations including temperature and voltage fluctuations; and finally, sources of temporal variations. Different state-of-the-art characterization circuits and sensors employed in modern integrated circuits to understand the extent and impact of variations are presented. An overview of the power dissipation issues of the state-of-the-art CMOS technologies is presented in Chapter 2. This chapter investigates the sources of IC power dissipation and techniques for power analysis in nanometer CMOS circuits. Finally, different power optimization techniques from circuit and physical design to system synthesis are discussed.

# **Part II: Circuit-Level Design Solutions**

Part II discusses the circuit-level challenges and design methodologies for low-power and process variation tolerance. This part is organized in four chapters – logic circuits, statistical design, memory circuits, and ultra-low-voltage design.

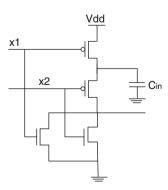

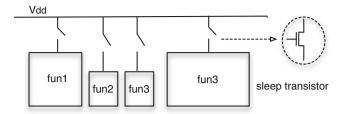

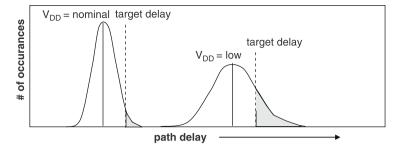

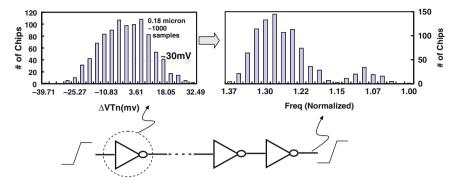

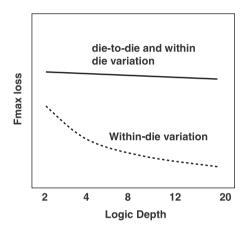

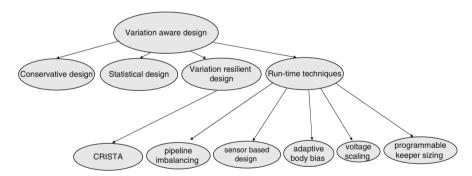

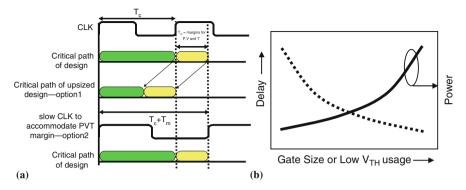

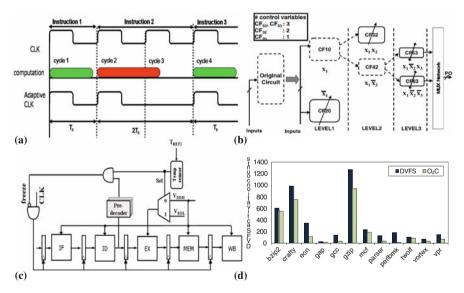

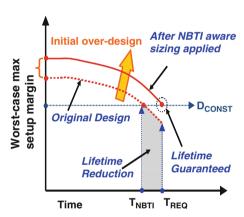

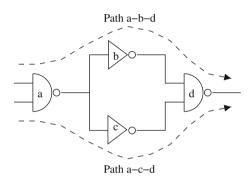

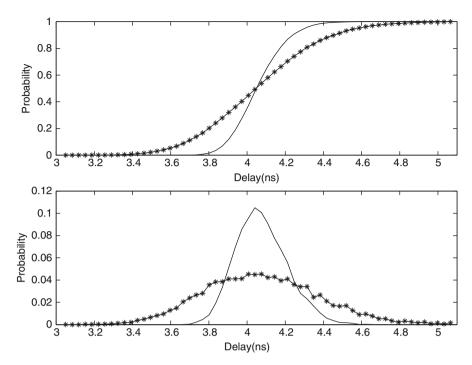

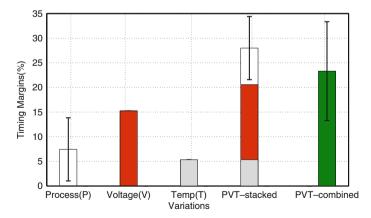

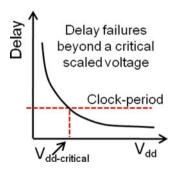

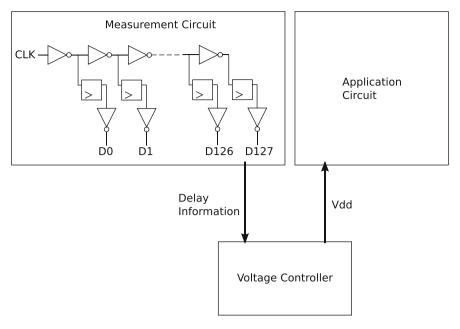

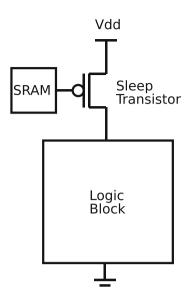

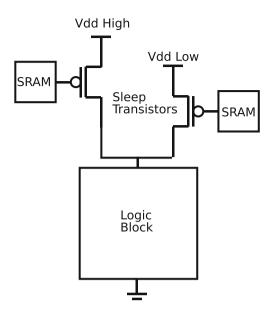

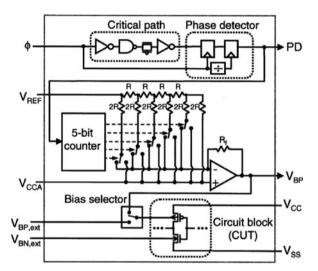

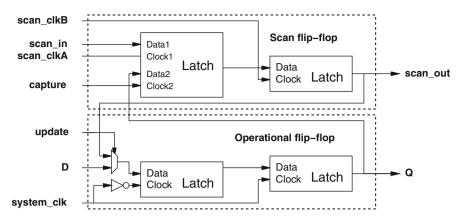

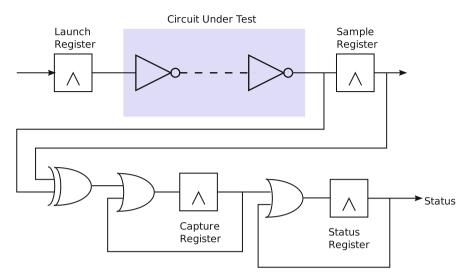

The process and temporal variations prevent a logic block from meeting timing and power criteria. The net effect is degradation in the parametric yield. The low-power design methods like voltage scaling, dual threshold assignment further magnify the effect of variations. A trivial solution to the problem of variation is over-designing the logic circuit, for example, using transistor upsizing or supply voltage boosting. But over-design comes at a serious power cost. Researchers at industry and academia have been exploring methods that would allow variation tolerance at no or minimum power overhead. Considering the complexity of the current day integrated circuits, these methods span the domains of circuit design as well as computer-aided design (CAD) methodologies. Chapter 3 reviews circuit-level methods to address this goal. The chapter first analyzes the effect of process variations and time-dependent degradation mechanisms. The analysis is followed by discussion of two design approaches to address these problems: variation tolerant circuits and adaptive circuits that tune themselves to operate correctly under variations. Chapter 4 of this part focuses on the statistical design paradigm, as opposed to the traditional corner-based methodology, to address the variation problem. The techniques for pre-silicon statistical timing and power analysis are presented to determine the performance spread of large logic blocks due to variations. Next, the pre-silicon statistical optimization techniques are discussed to improve the parametric yield. Finally, the chapter discusses how a set of compact sensors may be used to predict the delay of a manufactured part and drive adaptive post-silicon tuning.

viii Preface

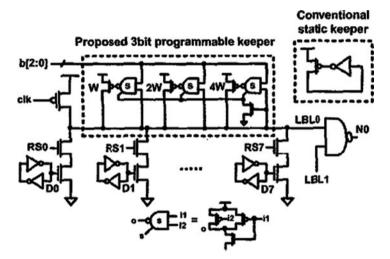

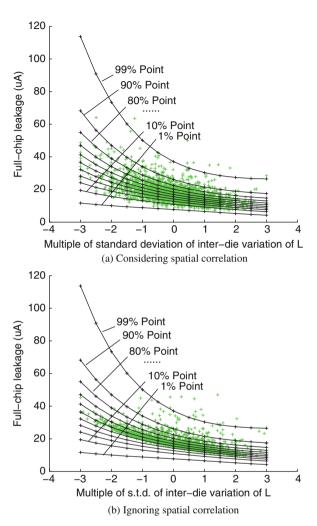

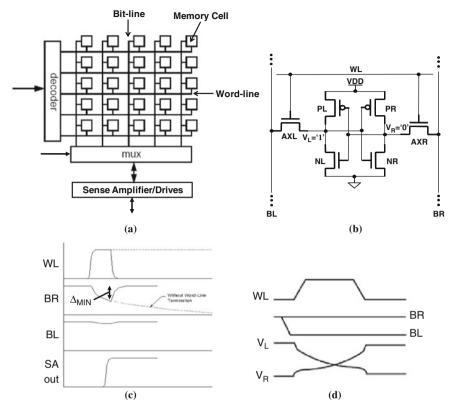

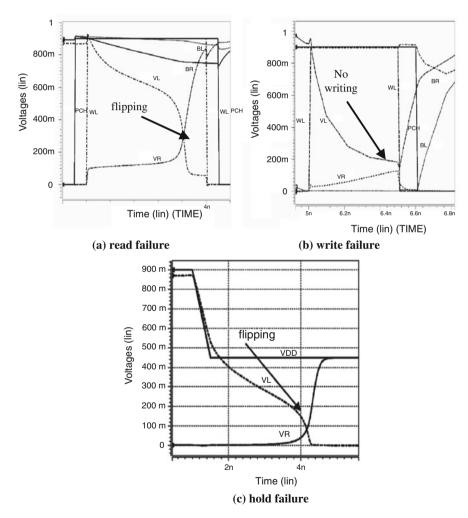

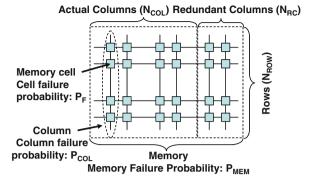

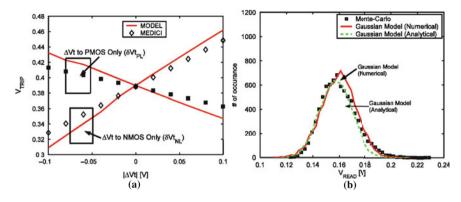

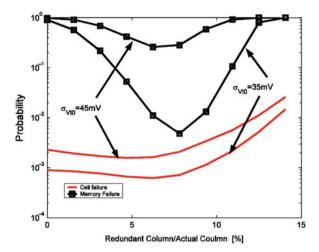

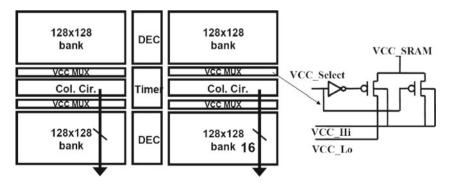

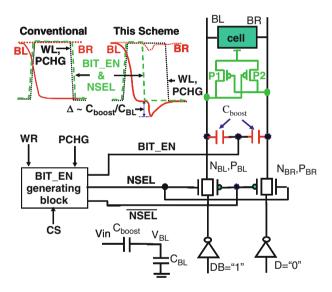

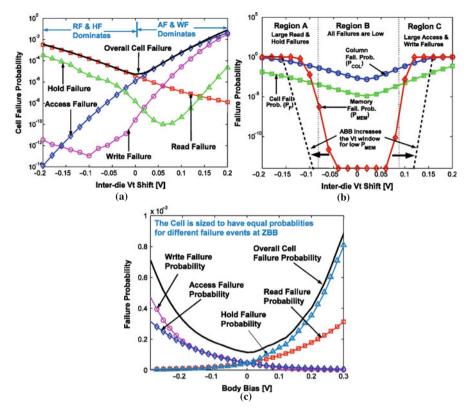

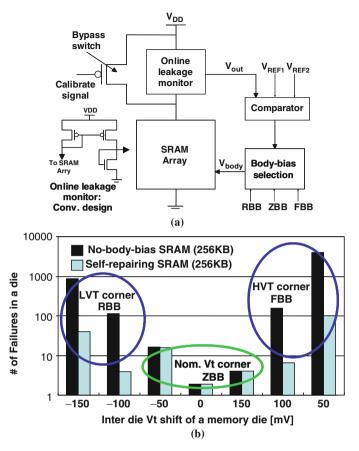

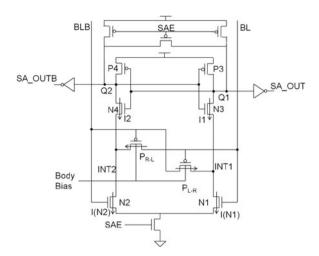

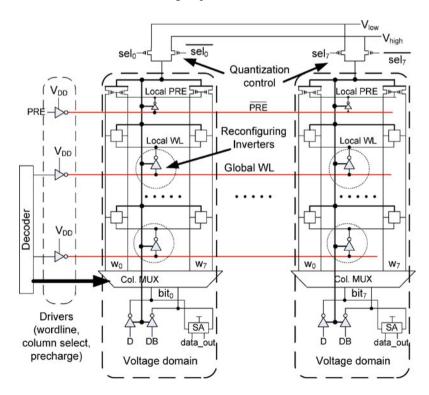

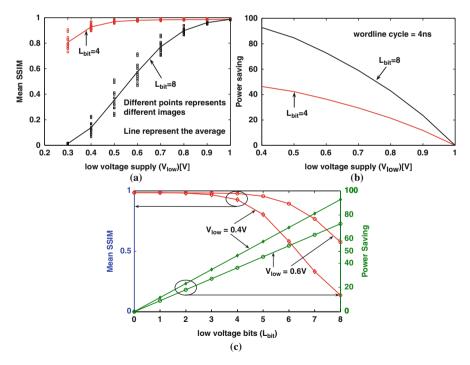

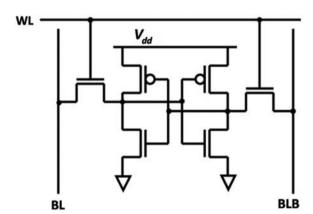

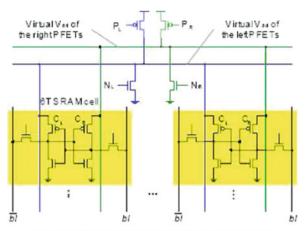

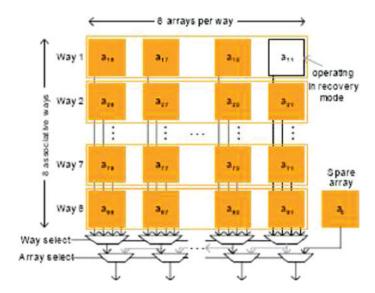

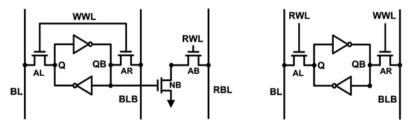

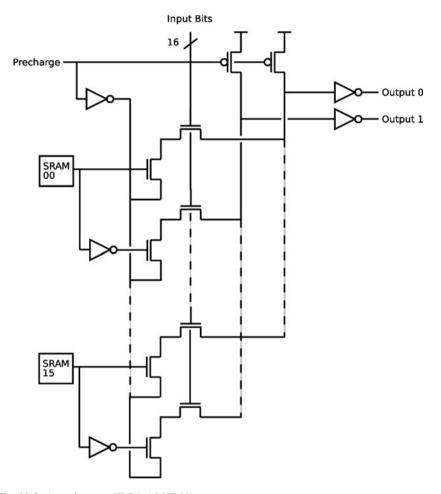

The die-to-die or within-die spatial variations in process parameters are the primary cause of concerns in logic circuits which lead to delay or leakage variations. On the other hand, the memory circuits are more susceptible to local random variations that results in different types of parametric failures. Chapter 5 discusses the impact of process variations on reliability of Static Random Access Memory (SRAM). The chapter provides an overview of the mechanisms of SRAM parametric failures and estimation methods for failure probabilities and parametric yield of SRAM. This analysis is followed by design approaches for SRAM yield enhancement including cell sizing, redundancy, dynamic circuit techniques, post-silicon adaptive repair techniques, and variation-tolerant SRAM peripherals. Finally, a discussion on adaptive low power and variation-tolerant SRAM design for multimedia applications is provided.

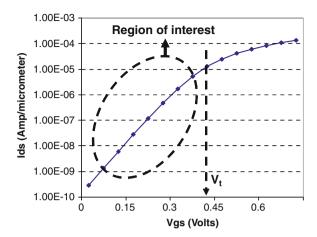

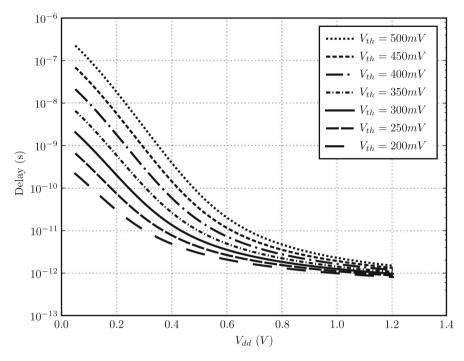

This part concludes with the discussion of a relatively new concept of digital design – the subthreshold design – where operating voltage of the circuit is lower than the threshold voltage of the transistor. The applications of the subthreshold design in ultra-low-power electronics are being actively investigated. Chapter 6 provides a brief overview of the principles and challenges subthreshold digital design. Design principles at all levels of hierarchy, namely, devices, circuits, and architecture, need to be evaluated for maximum power gains. Brief description of SRAM design techniques as well as alternative architectures for lower power in subthreshold design has also been discussed.

# **Part III: System-Level Design Solutions**

Part III focuses on system-level design challenges and design methodologies for low-power and process-variation tolerance. The three chapters cover three different types of mainstream electronic systems: microprocessor, application specific integrated circuits such as digital signal processors, and analog/mixed Signal/RF circuits.

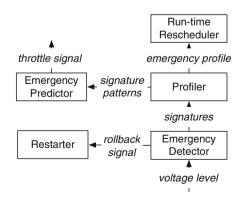

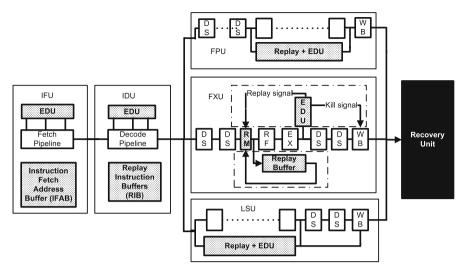

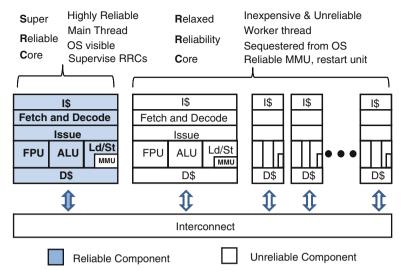

Chapter 7 discusses micro-architectural techniques to tolerate variations in microprocessors and design variation-tolerant low-power systems. The chapter discusses how different variation sources impact the timing uncertainty at the system level. Designers typically account for parameter variations by inserting conservative margins that guard against worst-case variation characteristics to guarantee functional correctness of the system under all operating conditions. But such conservative approaches lead to performance degradation. This chapter presents alternative error-tolerant schemes to deal with these different sources of parameter variations. Error-tolerant schemes aim to run with nominal timing-margins but without comprising robustness and correctness.

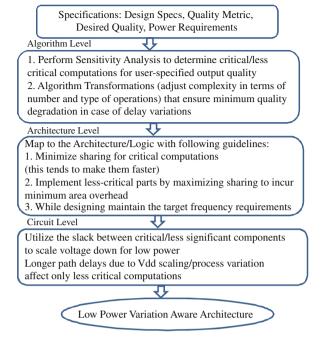

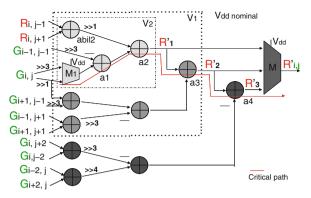

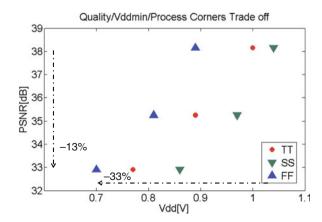

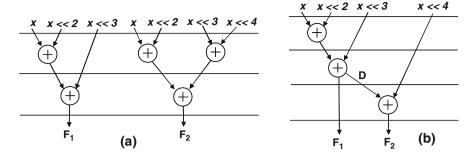

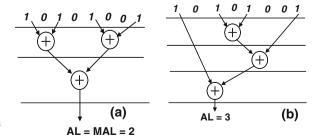

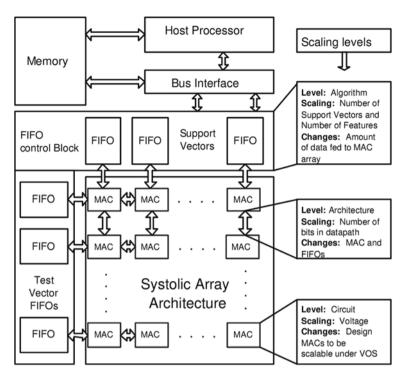

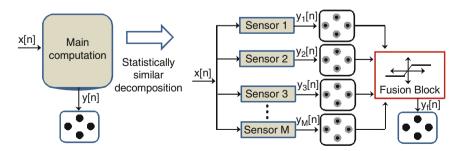

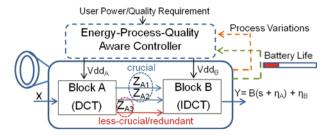

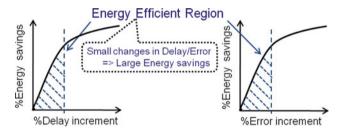

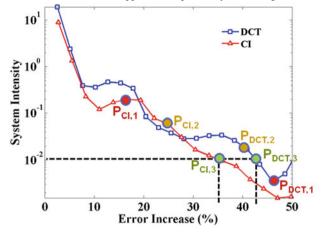

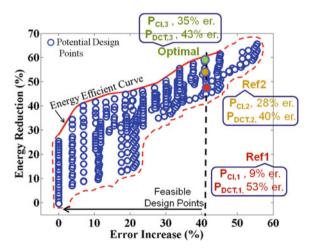

Chapter 8 presents an overview of low power and variation tolerant challenges in digital signal processing (DSP) systems. The chapter discusses how to exploit properties of DSP algorithms and combine circuit and architecture-level techniques in order to provide intelligent trade-offs between circuit-level metrics such as power

and performance with system-level metrics such as quality-of-results and tolerance to variations (yield). The techniques presented in this chapter target various types of designs that include logic and memory architectures and complete DSP systems.

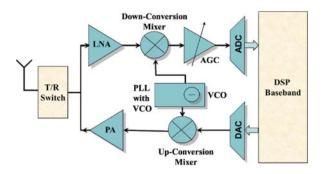

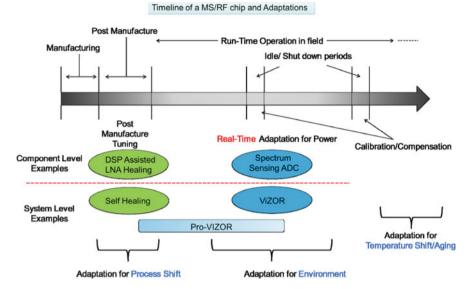

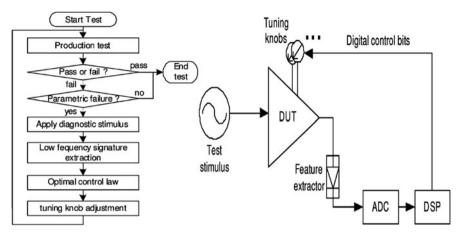

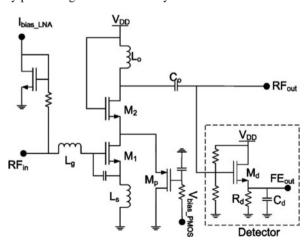

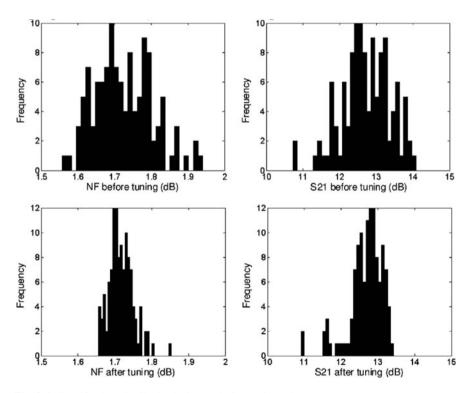

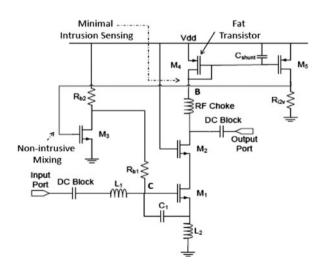

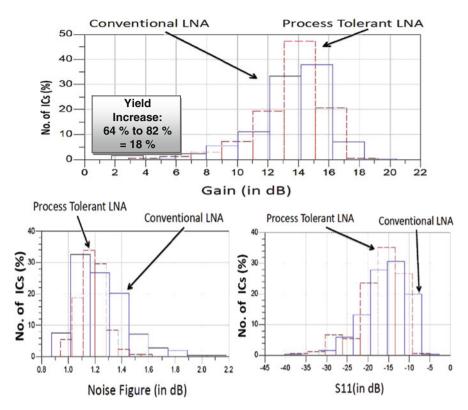

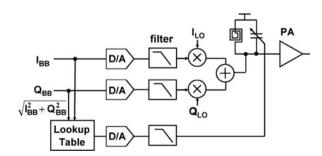

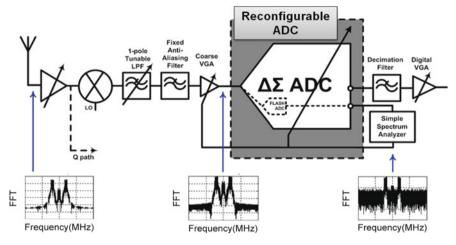

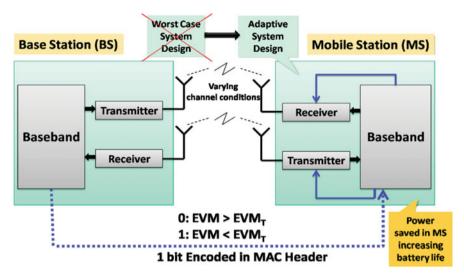

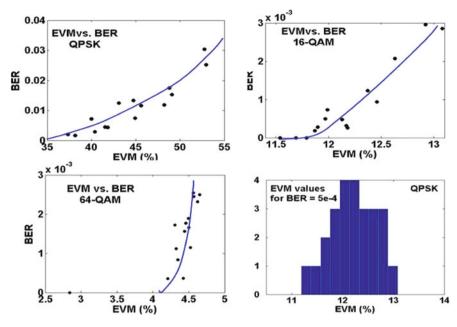

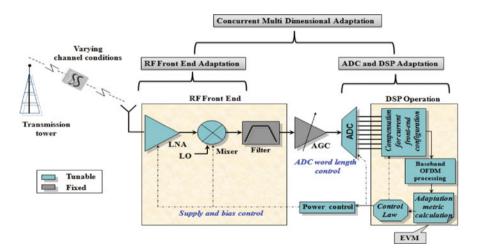

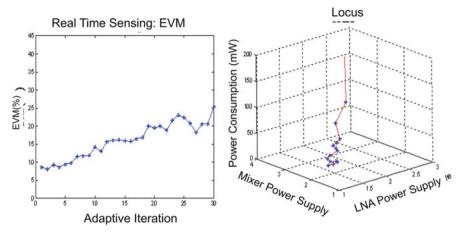

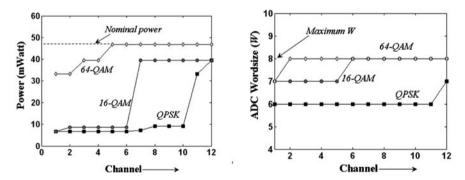

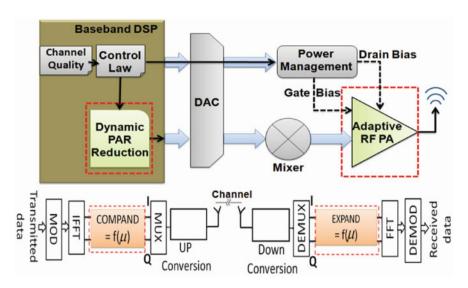

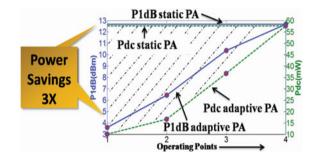

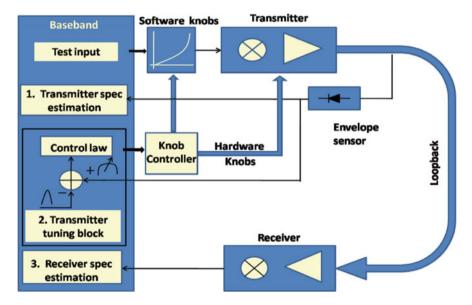

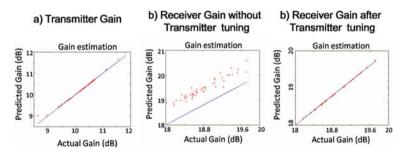

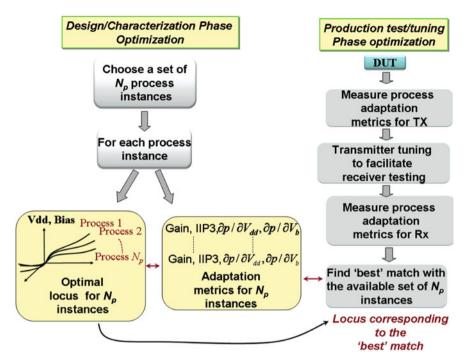

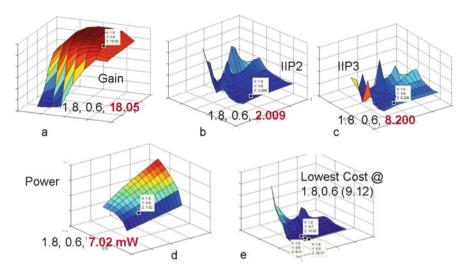

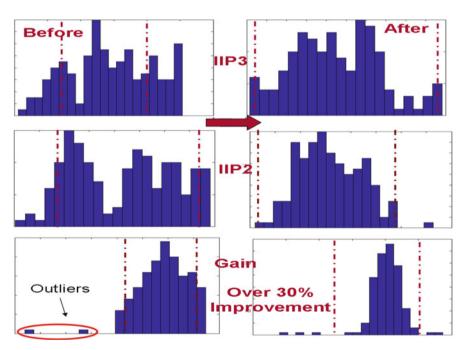

Chapter 9 discusses challenges in analog/mixed Signal/RF systems and complements the methodologies throughout the book for digital circuits and systems. Low-Power and variation-tolerant analog/mixed Signal/RF circuits require very different set of design techniques. The design techniques range from individual circuit components to system-level methods. This chapter highlights the component level as well as system-level design challenges in a low-power, process-tolerant mixed Signal/RF system using a wireless transceiver as a demonstration vehicle. At the component level, variation-tolerance for critical blocks such as analog-to-digital conversion, low-noise amplifiers are discussed. At the system level, the chapter focuses on how to achieve low power and end-to-end quality-of-service in RF transceiver under both manufacturing and environmental variations.

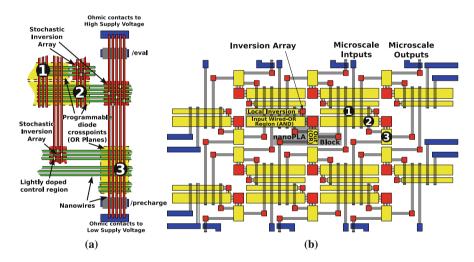

# Part IV: Low-Power and Robust Reconfigurable Computing

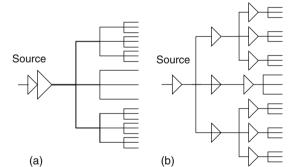

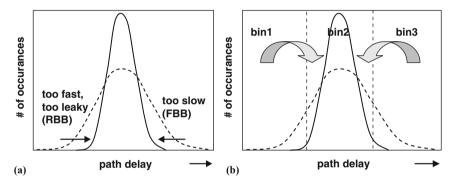

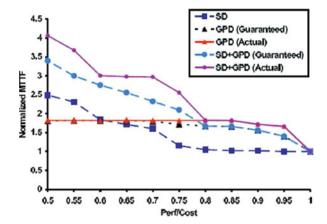

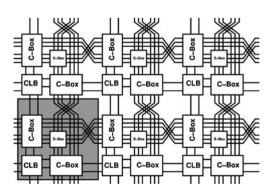

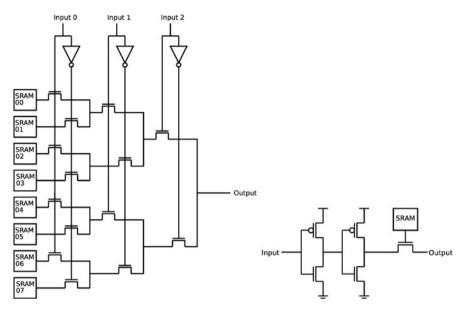

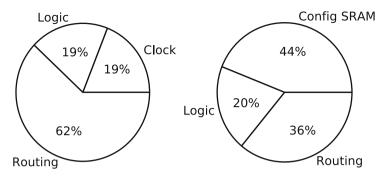

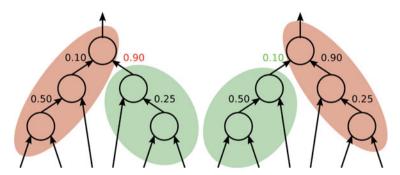

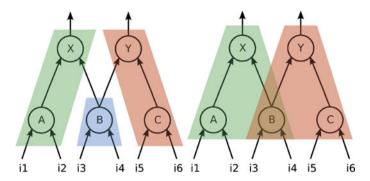

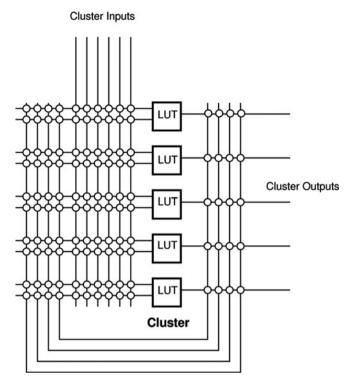

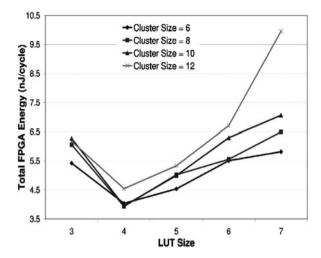

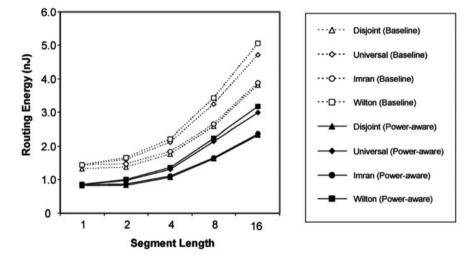

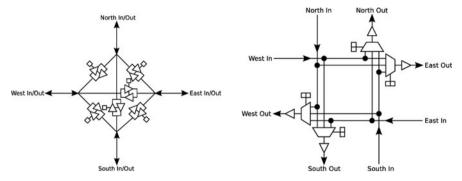

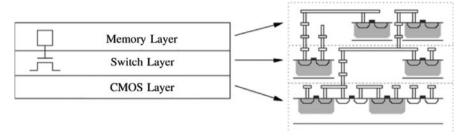

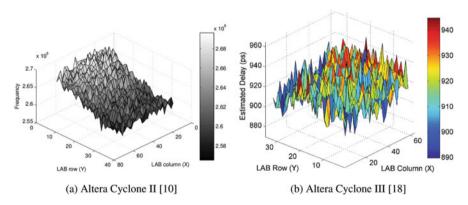

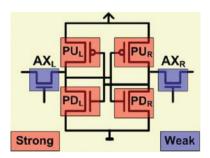

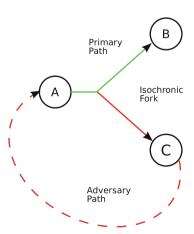

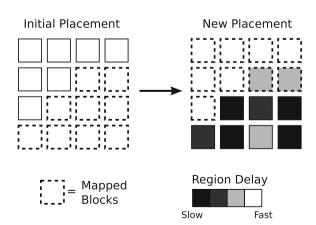

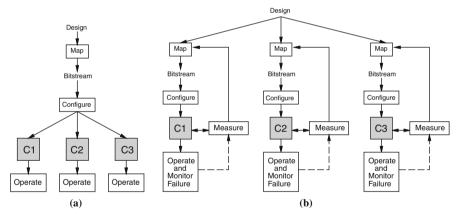

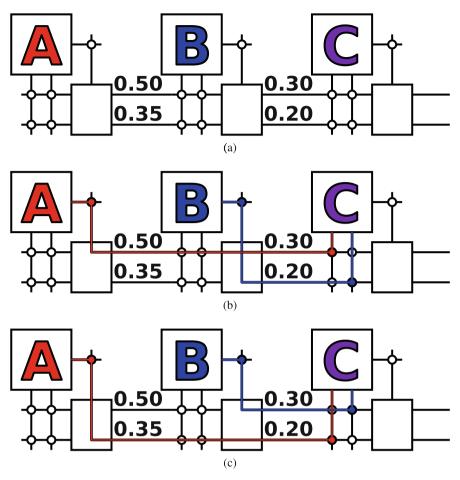

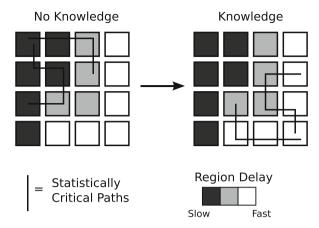

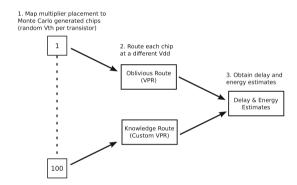

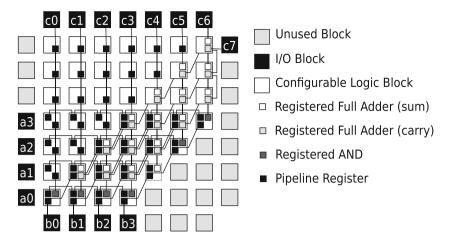

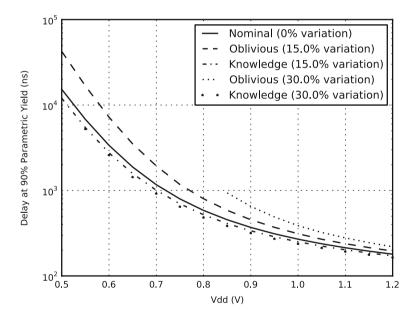

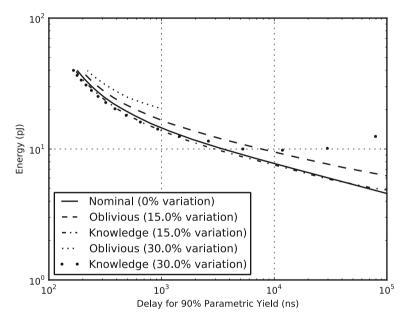

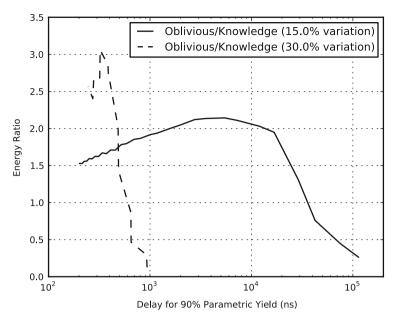

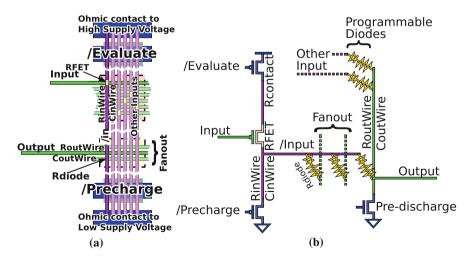

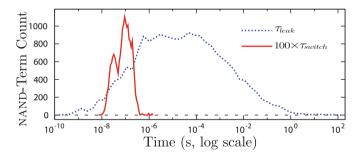

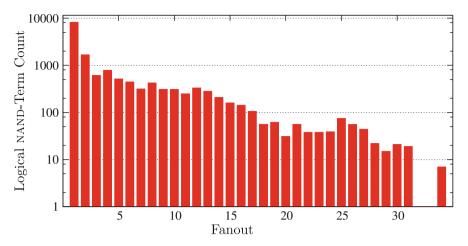

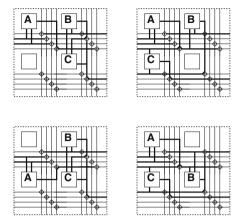

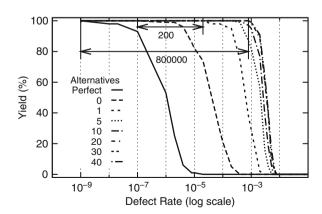

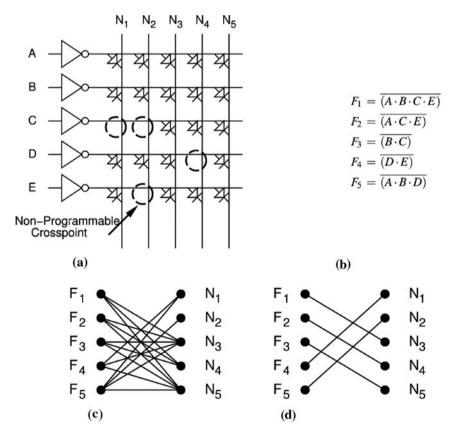

Part IV concentrates on low power and variation tolerance in reconfigurable computing platforms. FPGAs are reconfigurable devices that can be programmed after fabrication to implement any digital logic. Compared to application-specific integrated circuits or ASIC, FPGA provides flexibility, in-field reconfigurability, and potential cost advantage but at the expense of area, performance, and perhaps most importantly power. FPGAs are normally less power efficient than ASICs but significant research efforts devoted to improving power efficiency of FPGA can potentially narrow or even close this gap. Chapter 10 surveys the techniques and progress made to improve FPGA power efficiency. Parameter variation and component aging are becoming a significant problem for all digital circuits including FPGAs. These effects degrade performance, increase power dissipation, and cause permanent faults at manufacturing time and during the lifetime of an FPGA. Chapter 11 examines the impact of variation and device wear-out on FPGAs. The chapter discusses different techniques that can be used to tolerate variations in FPGA with specific attention to how the reconfigurable nature of the FPGAs can lead to innovative solutions to variation and wear-out management. Chapter 12 discusses design methods that can provide both low power and variation tolerance. This chapter discusses the opportunities of using post-fabrication reconfiguration in FPGA to tolerate variation effects without expensive static margins. The post-fabrication reconfigurability can be used to deploy devices based on their fabricated or aged characteristics to place the highspeed/leaky devices on critical paths and slower/less-leaky devices on non-critical paths. The component-specific mapping methodologies that can achieve the above objectives are discussed in the chapter.

We believe the target readership consisting of students, researchers, and practitioners will like the content and be greatly benefited from it. We also believe

x Preface

that the content will remain highly relevant to emerging technologies – both silicon and non-silicon – since power and variability continue to be major design issues in the nanometer regime. We are very grateful to all the outstanding contributors for providing the high-quality chapters for the book. We highly appreciate their whole-hearted cooperation throughout this project. We also acknowledge the help and support from the students, in particular from Somnath Paul, Seetharam Narasimhan, and Anandaroop Ghosh of Nanoscale Research Lab at Case Western Reserve University as well as students from the GREEN Lab, at Georgia Institute of Technology. We also remain sincerely thankful to Springer, USA and all their publication stuffs.

Cleveland, Ohio Atlanta, Georgia Swarup Bhunia Saibal Mukhopadhyay

# **Contents**

| Part | I Physics of Power Dissipations and Parameter Variations                                          |     |

|------|---------------------------------------------------------------------------------------------------|-----|

| 1    | Variations: Sources and Characterization                                                          | 3   |

| 2    | <b>Power Dissipation</b>                                                                          | 41  |

| Part | II Circuit-Level Design Solutions                                                                 |     |

| 3    | Effect of Variations and Variation Tolerance in Logic Circuits                                    | 83  |

| 4    | Statistical Design of Integrated Circuits                                                         | 109 |

| 5    | <b>Low-Power and Variation-Tolerant Memory Design</b> Hamid Mahmoodi                              | 151 |

| 6    | Digital Subthreshold for Ultra-Low Power Operation: Prospects and Challenges                      | 185 |

| Part | III System-Level Design Solutions                                                                 |     |

| 7    | <b>Variation-Tolerant Microprocessor Architecture at Low Power</b> Meeta S. Gupta and Pradip Bose | 211 |

| 8    | Low-Power and Variation-Tolerant Application-Specific System Design                               | 249 |

| 9    | Low-Power Adaptive Mixed Signal/RF Circuits<br>and Systems and Self-Healing Solutions             | 293 |

xii Contents

| Part | IV Low-Power and Robust Reconfigurable Computing                                          |     |

|------|-------------------------------------------------------------------------------------------|-----|

| 10   | Low-Power Techniques for FPGAs  Nikil Mehta and André DeHon                               | 337 |

| 11   | Variation and Aging Tolerance in FPGAs                                                    | 365 |

| 12   | Component-Specific Mapping for Low-Power Operation in the Presence of Variation and Aging | 381 |

| Sumi | mary                                                                                      | 433 |

| Inde | x                                                                                         | 435 |

# **Contributors**

Aditya Bansal IBM T.J. Watson Research Center, Yorktown Heights, NY, USA, bansal@us.ibm.com

**Pradip Bose** IBM T.J. Watson Research Center, Yorktown Heights, NY, USA, pbose@us.ibm.com

**Abhijit Chatterjee** Department of Electrical and Computer Engineering, Georgia Institute of Technology, Atlanta, GA, USA, chat@ece.gatech.edu

**André DeHon** Department of Electrical and Systems Engineering, University of Pennsylvania, Philadelphia, PA, USA, andre@seas.upenn.edu

**Swaroop Ghosh** Intel Corporation, Portland, OR, USA, swaroopad.ghosh@intel.com

**Benjamin Gojman** Department of Computer and Information Science, University of Pennsylvania, Philadelphia, PA, USA, bgojman@seas.upenn.edu

**Meeta S. Gupta** IBM T.J. Watson Research Center, Yorktown Heights, NY, USA, msgupta@us.ibm.com

**Georgios Karakonstantis** Department of Electrical and Computer Engineering, Purdue University, West Lafayette, IN, USA, gkarakon@purdue.edu

**Hamid Mahmoodi** Department of Electrical and Computer Engineering, San Francisco State University, San Francisco, CA, USA, mahmoodi@sfsu.edu

**Nikil Mehta** Department of Computer Science, California Institute of Technology, Pasadena, CA, USA, nikil@caltech.edu

**Vishwanath Natarajan** Department of Electrical and Computer Engineering, Georgia Institute of Technology, Atlanta, GA, USA, vishwa@ece.gatech.edu

**Bipul C. Paul** Global Foundries, Fishkill, NY, USA, bipul.paul@globalfoundries.com

Rahul M. Rao IBM T.J. Watson Research Center, Austin, TX, USA, raorahul@us.ibm.com

xiv Contributors

**Kaushik Roy** Department of Electrical and Computer Engineering, Purdue University, West Lafayette, IN, USA, kaushik@ecn.purdue.edu

**Arijit Raychowdhury** Intel Corporation, Portland, OR, USA, arijit.raychowdhury@intel.com

**Raphael Rubin** Department of Computer and Information Science, University of Pennsylvania, Philadelphia, PA, USA, rafi@seas.upenn.edu

**Sachin S. Sapatnekar** Department of Electrical and Computer Engineering, University of Minnesota, Minneapolis, MN, USA, sachin@umn.edu

**Shreyas Sen** Department of Electrical and Computer Engineering, Georgia Institute of Technology, Atlanta, GA, USA, shreyas.sen@gatech.edu

**Li Shang** Department of Electrical, Computer, and Energy Engineering, University of Colorado, Boulder, CO, USA, li.shang@colorado.edu

**James Williamson** Department of Electrical, Computer, and Energy Engineering, University of Colorado, Boulder, CO, USA, james.williamson@colorado.edu

**Wei Zhang** School of Computer Engineering, Nanyang Technological University, Singapore, zhangwei@ntu.edu.sg

# **About the Editors**

Swarup Bhunia received his B.E. (Hons.) from Jadavpur University, Kolkata, and the M.Tech. degree from the Indian Institute of Technology (IIT), Kharagpur. He received his Ph.D. from Purdue University, USA, in 2005. Currently, Dr. Bhunia is an assistant professor of electrical engineering and computer science at Case Western Reserve University, Cleveland, USA. He has published over 100 articles in peer-reviewed journals and premier conferences in the area of VLSI design, CAD, and test techniques. His research interests include low power and robust design, hardware security and protection, adaptive nanocomputing, and novel test methodologies. He has worked in the semiconductor industry on RTL synthesis, verification, and low power design for about 3 years. Dr. Bhunia received Semiconductor Research Corporation (SRC) technical excellence award (2005), SRC Inventor Recognition Award (2009), best paper award in International Conference on Computer Design (ICCD 2004), best paper award in Latin American Test Workshop (LATW 2003), and best paper several best paper nominations. He has served as a guest editor of IEEE Design and Test of Computers (2010), and Journal of Low Power Electronics (JOLPE). He has also served in the technical program committee of many IEEE and ACM conferences. He is an Associate Editor of ACM Journal on Emerging Technologies (JETC) and a senior member of IEEE.

Saibal Mukhopadhyay received the B.E. degree in electronics and telecommunication engineering from Jadavpur University, Calcutta, India, in 2000 and the Ph.D. degree in electrical and computer engineering from Purdue University, West Lafayette, IN, in 2006. He was with the IBM T.J. Watson Research Center, Yorktown Heights, NY, as a research staff member. Since September 2007, he is with the School of Electrical and Computer Engineering, Georgia Institute of Technology, Atlanta, as an assistant professor. His research interests include analysis and design of low power and robust circuits in nanometer technologies. Dr. Mukhopadhyay was the recipient of the IBM Faculty Partnership Award in 2009 and 2010, SRC Inventor Recognition Award in 2008, IBM Ph.D. Fellowship Award in 2004, the SRC Technical Excellence Award in 2005, the Best in Session Award at the 2005 SRC TECNCON, and the Best Paper Awards at the 2003 IEEE Nano and the 2004 International Conference on Computer Design. He is a coauthor of more than 100 papers in refereed journals and conference proceedings, and co-inventor of three US Patent.

# Part I Physics of Power Dissipations and Parameter Variations

# **Chapter 1**

# Variations: Sources and Characterization

Aditya Bansal and Rahul M. Rao

**Abstract** This chapter discusses the different sources of variation which can deviate a circuit's characteristics from its intended behavior. First we discuss the sources of process variation during manufacturing, followed by environmental variations during usage. Environmental variations include temperature, voltage fluctuations, and temporal variations. Finally, we discuss the state of art characterization circuits (or sensors) employed to understand the extent and impact of variations.

#### 1.1 Introduction

Traditionally, performance benchmarking and power estimation are based on the premise that the electrical characteristics and operating conditions of every device in the design matches the model specifications. However, with continued scaling of device dimensions to sub-100-nm regime, it has become nearly impossible to maintain the same level of manufacturing control and uniformity. This can cause devices to behave differently from model characteristics. Further, devices that were intended to be identical could differ vastly in their electrical characteristics which can lead to functional failures. Environmental factors such as supply voltage and temperature experienced by devices in different parts of the chip (or on different chips) also vary due to different levels of device densities, switching activities, and noise integrity of the various blocks. The voltage and temperature stress experienced by the devices with continued usage degrades their electrical characteristics, thereby increasing the mismatch between the idealistic models and the actual device parameters. All these factors can combine to make the actual design considerably different from the intended design. The performance of the design can thus vary and be lower than the intended one. Similarly, due to the exponential dependence between process/device parameters and transistor leakage, the chip power can also vary and be significantly higher than the nominal values. This translates into a reduced

A. Bansal (⋈)

IBM T.J. Watson Research, Yorktown Heights, NY, USA

e-mail: bansal@us.ibm.com

parametric yield, which is the number of manufactured chips that satisfy the required performance, power, and reliability specifications, and hence limits the number of shippable products. With the initial design cost being the same, the cost per good chip increases which has a direct impact on the bottom line dollar value of the design.

The impact of these variations on the parametric yield is generally reduced by guard-banding to provide sufficient tolerance margins during design, which is equivalent to designing at a non-optimal power-performance point. Designs are rated to run at lower than nominal frequencies to guarantee functional correctness in the presence of variations. With increasing variation, the required guard-banding also increases, especially if worst-case conditions are considered. Understanding the various sources of variation and their impact on circuits can help in determining a realistic amount of design margining required, and also provide insights to mitigate the effects of variation. On-chip characterization circuits can help in determining the extent of variation, isolating various effects and their dependence and providing feedback to the manufacturing team. They can also be used in the field to monitor the chip periodically, detect possible failure conditions, and adjust global parameters that can help compensate against these effects.

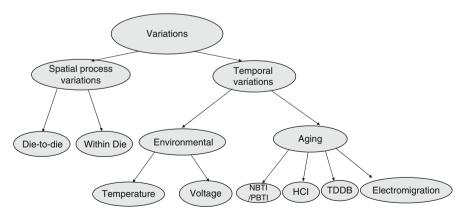

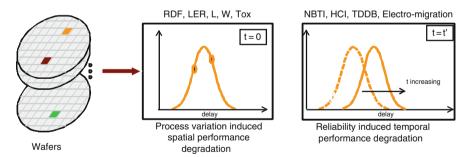

Variations can be broadly classified into process, environmental, and temporal variations. *Process variations* are a consequence of imperfect control over the fabrication process. *Environmental variations* arise during the operation of the circuit due to changes in the operating conditions such as temperature and supply voltage. *Temporal variations* refer to the change in the device characteristics over time. The rest of the chapter will provide an insight into the sources of variation and circuits commonly used to characterize these effects.

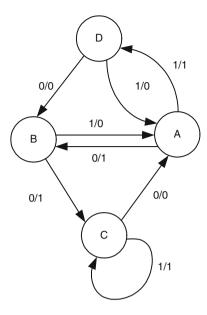

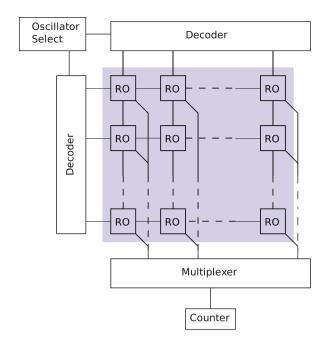

#### 1.2 Process Variations

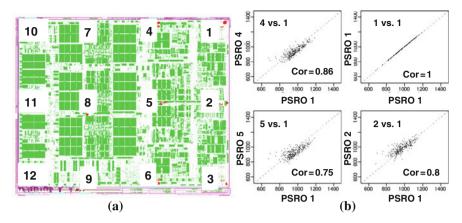

Process variations occur due to lack of perfect control over the fabrication process. These variations always existed since the invention of transistor; however, they are increasingly gaining importance with the scaling of FET dimensions – especially in sub-100-nm technology nodes. In today's VLSI circuits, no two FETs on a chip are exactly same at the atomic level – even neighboring devices can be significantly different. As an illustration, Fig. 1.1 shows the correlation in frequency among four identically designed performance screen ring-oscillators (PSROs) on a chip. It can be seen that the frequencies of neighboring PSROs are correlated to each other; however, not exactly matched though identically designed. This correlation depends on the technology, layout, and the fabrication imperfections.

# 1.2.1 Sources of Variations

Process variations can be categorized as systematic or statistical in nature. Systematic variations repeat from chip-to-chip and cause fixed offset from design target in FETs. They are typically caused by errors in mask build, optical proximity

Fig. 1.1 (a) Chip ( $\sim$ 250 mm<sup>2</sup>) map showing the location of 12 identical ring-oscillators. (b) Correlation corner (averaged over 300 chips) for 4 ring-oscillators. (Courtesy: Manjul Bhushan, IBM)

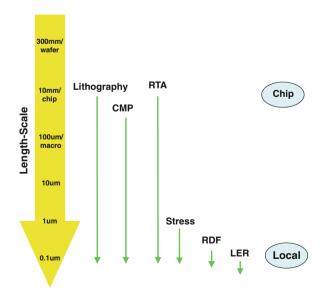

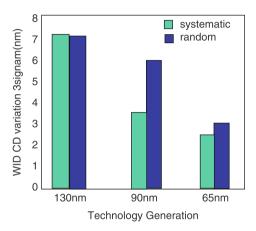

correction (OPC), layout, tool optics, etc. Statistical variations make the two chips or two devices different. Range of statistical variations can vary from  $\sim 300$  mm to less than 10 nm. Figure 1.2 summarizes the range of key process variations. Wafer-scale variations (may be due to chuck holding the wafer during process steps) cause variations in wafers but all the chips on a particular wafer see the same effect. Similarly, chip-level variations cause two chips to differ from each other; however, all the FETs

**Fig. 1.2** Variation range of various mechanisms

on one chip see the same affect. Medium range variations ( $10{\text -}100~\mu\text{m}$ ) cause variations from one circuit block to another circuit block. For example, one section of a chip can become very slow whereas another section can be very leaky. Small range variations ( $<1~\mu\text{m}$ ) are typically intrinsic and caused by random dopant fluctuations (RDF) and line-edge roughness (LER). These variations cause two neighboring FETs to have different electrical characteristics.

In this section, we will focus on the sources of statistical process variations and their impact on electrical characteristics. We broadly classify sources of variations into two categories – tool-based and intrinsic. Tool-based variations are medium to long-range variations whereas intrinsic variations are small variations.

#### 1.2.2 Fabrication Tool-Induced Variations

#### 1.2.2.1 Lithographic Variations

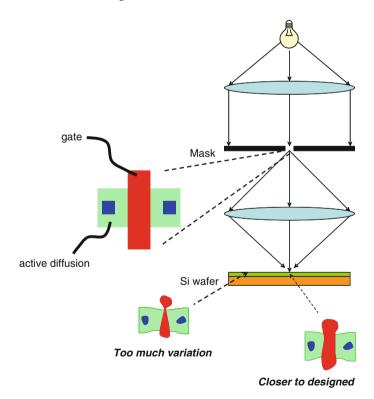

Lithographic variations occur due to the imperfect tools and depend on the physical design. Figure 1.3 shows a simplified view of a lithographic tool used to pattern the FET gate, active diffusion region, contacts, vias, and interconnects. First masks are

Fig. 1.3 Schematic of a lithographic tool

generated to represent the designed patterns in each fabrication layer. VLSI circuits are highly complex and the mask formation is largely an automated process. Today, sub-50-nm dimensions are printed on a wafer using a light source with wavelength 193 nm. Several advanced mathematical algorithms and techniques, such as optical proximity correction (OPC) [1], (RET), etc., are used to reliably print a pattern. During the mask generation process, some errors can occur resulting in ill-formation of the pattern. These are called mask errors. These errors are random in nature and may or may not exist. For example, mask-error can occur for a specific shape of poly silicon resulting in narrow gate of a FET. After a mask is generated, it is used to print a pattern on the wafer. For sub-50-nm dimensions on a wafer, lenses have to be perfectly aligned and focused. However, it is not possible to perfectly control the focus on the whole wafer resulting in reduced or increased dimensions. For example, focus variation in a gate formation can either narrow the gate length or increase it. Further, the dosage of light source is very critical and it is not uniform across the full wafer resulting in the variation in critical dimension (CD) due to dose variations. These lithographic variations are typically of the order of tens of microns. These statistical variations can be assumed to have Gaussian distribution. Typically we look at the variation in CD for  $\pm 3\sigma$  variations in lithography.

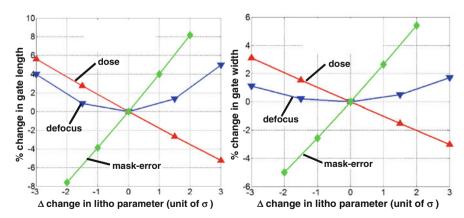

For circuit analysis, an effective gate length needs to be computed for each FET considering process fluctuations. There are several methods devised to account for non-rectangularity in FETs and include them in circuit simulations. Heng et al. [2] proposed one such method which can be used to estimate lithography-aware equivalent gate length and width. This method was used in [3] to design a virtual fabrication environment to maximize circuit yield. Figure 1.4 shows the percentage deviation of gate width and length from the design value in a 45-nm technology as computed using this method. In this example, designed gate length is 40 nm and gate width is 200 nm.

Fig. 1.4 Variation in a FET's length and width due to variation in lithography parameters – defocus, dose, and mask errors. Percentage change in gate length/width, from designed, are computed using the method proposed by [2]

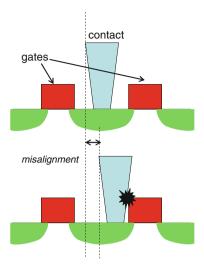

Fig. 1.5 Implication of contact and gate misalignment

Another source of variation can arise from wafer misalignment from one process to another. One critical example of misalignment-induced variation or defect is the distance between a gate and a contact (Fig. 1.5). For example, gate pitch of 130 nm with gate length of 40 nm leaves 90-nm distance between the two neighboring gate edges for contact formation. For a contact size of 40 nm  $\times$  40 nm, the closest distance between the gate edge and the contact edge is 25 nm. The size of the contact cannot be reduced to keep the low resistance while gate pitch cannot be increased to maintain density. Hence, increase in wafer misalignment will increase the gate to contact capacitance eventually leading to catastrophic failure – short between gate and contact.

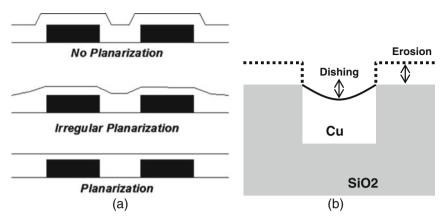

#### 1.2.2.2 Chemical Mechanical Polishing (CMP)

CMP is used for planarizing the metal interconnect layer or inter-layer dielectric (ILD) between adjacent metal layers due to copper damascene process. Figure 1.6 shows the variation in interconnect thickness in interconnect layer post-CMP. Metal CMP increases resistance due to loss of metal and decreases intra-layer coupling among adjacent wires. Increased resistance is somewhat compensated by decrease in capacitance for circuit delay. ILD CMP introduces change in inter-wire capacitances. Hence, CMP brings variation in the delay of interconnects resulting in non-deterministic circuit performance from chip-to-chip and within chip.

Other fabrication steps which can induce variation are rapid thermal annealing (RTA) [4] and stress liner effect [5]. The key FET parameters prone to these variations are length and width.

Fig. 1.6 (a) Planarization by CMP and (b) dishing and erosion causing variation in interconnect thickness

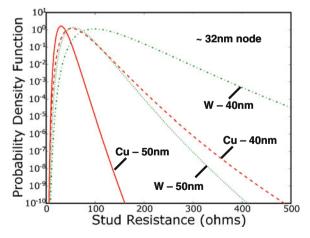

#### 1.2.2.3 Variation in Contact Resistance

Contact resistance is becoming critical for circuit analysis because of increasing resistance with contact dimension scaling. Figure 1.7 shows the distribution of contact resistance as analyzed by Sleight et al. [6]. They proposed an analytical cone model to compute the resistance under variation in bottom diameter, height and angle of a contact. Variation in contact resistance between two FETs can result in a significant difference in voltages seen by the terminals of these FETs. As an example, let us consider two 1- $\mu$ m-wide FETs (located spatially far off) such that their source contact resistances differ by 100  $\Omega$ . For 1 mA of drain-to-source current,

**Fig. 1.7** Distribution of contact resistance due to variation in – angle, bottom diameter, and height for a designed contact diameter. Shown are the two types of contacts – Tungsten (W) and Copper (Cu). W contacts are easy to manufacture. *Source*: [6]

the difference in voltage drops at the source terminals will be 100 mV between the two FETs. This will bring a difference of 100 mV between effective gate-to-source voltages, directly translating to the  $V_{\rm T}$  variation of 100 mV between two FETs. An analytical cone model [6] can be used to compute the contact resistance.

#### 1.2.3 Intrinsic Variations

Beyond variations due to imperfect fabrication tools, some variation sources are intrinsic to a technology. Two key sources of variation which are truly random in nature are random dopant fluctuation (RDF) and line-edge roughness (LER).

#### 1.2.3.1 Random Dopant Fluctuations (RDF)

FETs are doped with impure atoms to control the transistor's electrical properties, primarily short-channel effect and threshold-voltage. With technology scaling, the device volume is reducing thereby reducing the number of dopant atoms in a FET's channel. In sub-100-nm transistors, the position and the number of dopant atoms are critical. When a FET is doped with impurity, the number of dopant atoms and their placements cannot be controlled to the last atom. Moreover, dopant atoms diffuse in the Si channel and randomly get placed as illustrated in Fig. 1.8a. This random number and placement of dopants bring uncertainty in threshold voltage which is called RDF-induced  $V_{\rm T}$  variation. This variation is a grave concern in very small FETs because it is very unlikely to have two neighboring FETs with same number and placement of dopants. The statistical distribution of  $V_{\rm T}$  due to RDF has been found to follow normal distribution. The standard deviation ( $\sigma V_{\rm T}$ ) of these distribution scales with FET area following inverse square root law. For example, when a FET scales from  $L_1$ ,  $W_1$  to  $L_2$ ,  $W_2$ , the standard deviation changes to

Fig. 1.8 (a) RDF [7] and (b) distribution of Ion and Ioff in a 65 nm technology [8]

$$\sigma_{V_{\rm T}}|_{L_2,W_2} = \sqrt{L_1 W_1 / L_2 W_2} \ \sigma_{V_{\rm T}}|_{L_1,W_1} \tag{1.1}$$

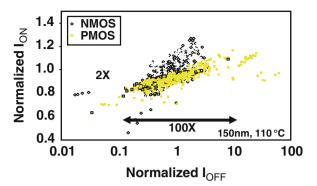

implying that if a FET's area is reduced by half, the  $\sigma V_T$  increases by a factor of 1.4 times. Figure 1.8b shows variation in on and off currents due to RDF-induced  $V_T$  fluctuation [8]. As can be understood, large area devices have tighter (lower  $\sigma V_T$ ) normal distribution of  $V_T$ .  $\sigma V_T$  is the same for two FETs with same device widths irrespective of the number of fingers. The distribution of  $V_T$  due to RDF can be obtained by atomistic Monte-Carlo simulations [9, 10].

# 1.2.4 Line-Edge Roughness (LER)

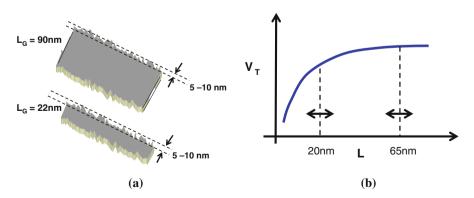

The gate edge of a MOSFET is not smooth; instead it is rough (as shown in Fig. 1.9a) primarily due to material properties, imperfect lithography and etching tools. Conventionally, polycrystalline silicon (polysilicon) is used to make gate. Polysilicon material has varying grain size, typically in the range of 5–10 nm. Current fabrication tools are unable to smooth this edge resulting in LER. Similar roughness is expected in metal gates due to the properties of metal used and fabrication steps. As shown in Fig. 1.9a, in FETs with gate length 90 nm or higher, the intrinsic fluctuation in gate length due to LER is less prominent compared to 22 nm technologies. In sub-50 nm technologies, the LER can be critical because FETs are typically designed at the knee of  $V_{\rm T}$  roll-off curve. Figure 1.9b shows that tighter control over the gate length is required in 20 nm long FETs compared to in 65-nm long FETs. The impact of LER can be analyzed by doing 3D TCAD simulations [11]. The distribution of LER-induced  $V_{\rm T}$  variation is Gaussian and scales with gate width following inverse square root law.

$$\sigma_{V_{\rm T}}|_{W_2} = \sqrt{W_1/W_2} \ \sigma_{V_{\rm T}}|_{W_1} \tag{1.2}$$

implying that the impact of LER will be less in wider transistors.

**Fig. 1.9** (a) Line Edge Roughness (b)  $V_T$  roll-off curve

# 1.3 Temperature and Supply Voltage Variations

The electrical behavior of devices in a circuit is strongly dictated by the operating conditions it experiences. The current through a device is determined by the voltage at its terminals, and hence influenced by the operational supply voltage. The threshold voltage  $(V_{\rm TH})$ , and carrier mobility  $(\mu)$  are dependent on the operating temperature. In addition to process variations described in the previous section, any change in these environmental conditions also causes a deviation of the power and performance characteristics of devices from their ideal behaviors.

# 1.3.1 Temperature Variations

The spatial temperature variation across the die or the temporal difference at the same location on the die depends on several factors. These include:

#### 1.3.1.1 Power Characteristics of the Neighboring Blocks

At a circuit level, the switching activity and the load characteristics of the blocks in the regions around that location determine the power consumption and hence the heat generated near that location. Highly capacitive blocks have a greater current demand and experience a relatively higher temperature in comparison to low-capacitive blocks. Further, blocks with a high-switching activity (e.g., clock-sector buffers) also generate a larger amount of heat in comparison to the blocks with minimal switching activity (e.g., inside a SRAM array or a power-gated block).

#### 1.3.1.2 Thermal Characteristics of Materials

For a given power density, the silicon temperature is a function of the thermal conductivity of the materials used. In a bulk CMOS technology, the heat generated spreads through the silicon substrate as well as the wires. However, in a siliconon-insulator (SOI) technology the poor thermal conductivity of the buried oxide causes most of the heat to be carried away primarily along the wires, which causes the temperature to increase at a faster rate. This results in a greater variation in the temperature gradient between the power-hungry hotter regions and the low-power cooler regions of the chip.

#### 1.3.1.3 Cooling and Packaging Efficiency

The cooling efficiency of the system also determines the spatial temperature variation. In a conventional design, the rate of temperature increase is determined by the package and heat sink design and the cooling mechanism, with a water-cooled system seeing a better thermal profile than an air-cooled system. However, the temperature variations are likely to be exacerbated in a three-dimensional (3-D) stack technology, where in the dies further away from the heat sink experience a

much reduced cooling efficiency and hence experience a large temperature gradient between the hot-regions and the cold-regions of the chip.

#### 1.3.1.4 Switching Activity and Workload Management

Another factor that determines the spatial temperature variation is the actual workload (or application) being run on the system. Certain blocks are continuously exercised in some workloads. In the current era of multi-core processors, it is likely that some of the cores are inactive and hence cold for a greater percentage of time. Depending on the ability of the system to dynamically manage the workload by periodically assigning tasks to different cores, or moving tasks from one core to another, the temperature difference between the cores will vary.

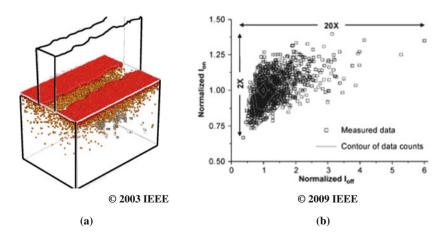

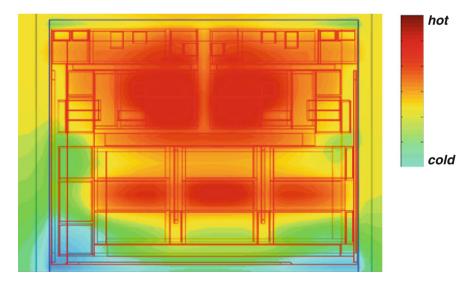

As a result, the temperature on different parts of the die can be vastly different a given point of time. As an example, Fig. 1.10 shows the temperature profile on an IBM Power 4, with a nearly  $20^{\circ}$ C difference between the hottest and the coolest portions of the chip. With the power densities of current generation designs being much higher, this spatial temperature variation is likely to be even higher, causing a significant difference in the performances of devices across the chip.

Fig. 1.10 Temperature difference across regions of IBM Power 4

# 1.3.2 Supply Voltage Variations

The supply voltage at any location on a die deviates from the nominal design value depending on the characteristics of the power grid network and the current requirement (both steady state and transient) of the design. Increased device

densities and operating frequency of highly pipelined systems have increased the current requirement of current designs. This, along with worsening wire properties, has made the problem of supply voltage variations more significant.

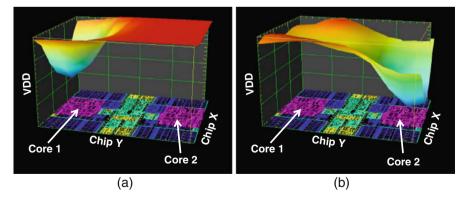

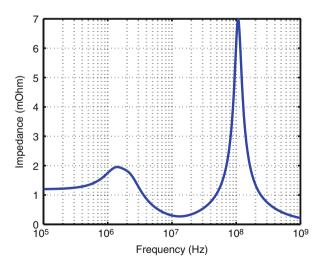

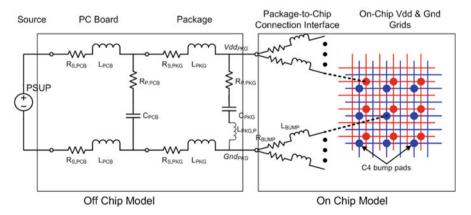

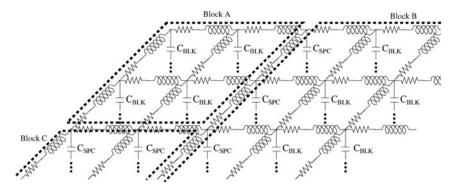

#### 1.3.2.1 Ldi/dt Effect

Various blocks in a design usually share a single power grid. Any sudden increase in the switching activity of a particular block requires additional current to be supplied to that area of the chip. The parasitic inductance in the power grid network and the package causes a di/dt drop and hence a transient voltage drop on the supply lines. With aggressive power management techniques, such as clock-gating and power-gating becoming prevalent in designs, the likelihood of such transient current requirements and its magnitude has increased. Further, with multi-core processors under a common power grid becoming the norm, dynamic changes in the current requirement of any one of the cores can create supply voltage variations on all of the others. This can be seen from Fig. 1.11 which shows the droop in the supply voltage for Core 1 and Core 2 in the scenario that Core 2 turns on a few ns after Core 1. In both the scenarios, there is significant supply voltage droop. However, Core 2 has a much worse voltage droop than Core 1, since the voltage droop from Core 1 is coupled to Core 2 just as it turns on, creating an increased supply voltage noise effect. Such peak-voltage droop scenarios are very difficult to predict, model, or avoid and hence require sufficient guard-banding in the design. The impact of such scenarios can be reduced by proper and sufficient use of on-chip decoupling capacitors and regulators.

**Fig. 1.11** Power supply droop in a multi-core processor for Core 1 and Core 2. (a) Voltage droop in Core 1 (left) as it turns on, followed by (b) voltage droop in Core 2 (right) as it turns on a few nano-seconds after Core 1 [12]

#### 1.3.2.2 IR Drop

There is also a voltage drop across the power grid due to the resistance of the power supply lines, which is a function of the steady state current carried through the network. This is referred to as the IR drop and is equivalent to the steady state current drawn from the power supply times the resistance of the power grid. Continued scaling of wire dimensions to match device scaling has increased the resistance per unit length of wire. In addition, growing die sizes with larger transistor counts (especially on-die caches) has increased the steady state (leakage) currents exacerbating the IR drop problem. The resistivity of the wires also increases with temperature, which further worsens the IR drop.

# 1.3.3 Impact on Circuit Performance

Let us now briefly look into the sensitivity of device characteristics and circuit metrics to these environmental variations.

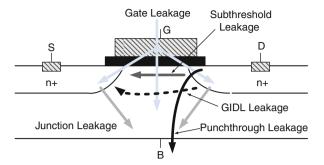

The mobility of charge carriers degrade with temperature due to the increased scattering in the channel. On the other hand, the semiconductor band gap is known to decrease with temperature. Due to the combination of these contradicting effects, the saturation current (and hence the delay of the worst path in the design) can either improve or worsen. However, in the weak inversion region, the effect of decreased band gap and its exponential influence on the sub-threshold leakage current results in a substantial increase in leakage currents for a small change in temperature. Further, all junction leakages also increase with temperature. Hence, the leakage power significantly increases with temperature making it a critical challenge especially for low-power designs in the hand-held and portable market space. A detailed analysis of the relationship between leakage power and temperature is presented in Chapter 2.

Current characteristics of devices significantly depend on changes in the supply voltage in all regions of operation. With a supply voltage droop of  $\Delta V$ , both the gate and drain bias seen by the devices reduce, resulting in a reduction in the device current. This increases the path delays and causes non-critical paths to become critical. Further, it worsens signal slew, which can increase the short circuit power drawn and makes the circuits more susceptible to noise.

# 1.4 Temporal Variations

So far we have discussed how a FET's characteristics strongly depend on the fabrication processes and environmental factors. Once a chip is manufactured, packaged, tested (for correct functionality), and shipped to the customers, it is expected to function at the tested voltage, temperature, and frequency till the end of its usage life-time. Assumption is that if we do not have moving parts (as in mechanical machines) then machines do not age (analogous to human aging). However, physical changes can occur in a FET due to movement of charges – electrons and

holes – and breaking of atomic bonds. Key mechanisms which affect a FET's behavior with time are:

- (1) Time-Dependent Dielectric Breakdown (TDDB): Creation and joining of defects in gate-dielectric causing gate dielectric breakdown.

- (2) Hot Carrier Injection (HCI): Defects in gate stack by highly energized carriers under large lateral (drain-to-source) electric fields causing shift in threshold voltage.

- (3) *Bias-Temperature Instability (BTI)*: Capturing of holes (electrons) from the inverted channel in PFETs (NFETs) by the broken Si–H bonds (charge-trapping sites in high-k gate dielectrics such as HfO<sub>2</sub>).

All the above mechanisms accelerate under large electric fields and high temperatures. In this section we discuss the mechanisms which vary the electrical characteristics of a circuit with usage. Many engineers term it as degradation of electrical characteristics; however, we will refrain from using the word degradation as in some aspects, electrical aging is not analogous to human or mechanical aging. There are several trade-offs at FET level which pose challenges in meeting desired circuit requirements. Say, if we want to increase performance, we will end up increasing power consumption as well. Therefore, a change in electrical characteristics which will degrade performance as well as power consumption will be a true degradation. We will learn that this is not always true when it comes to FET aging. In this section, we will learn different mechanisms which can affect circuit functionality with usage and also how we can estimate them. Before we proceed, we need to stress that "use" of a FET is a key factor in temporal variation of the characteristics of a FET. When a FET is subjected to voltage bias and operated under certain temperature, materials can degrade resulting in breaking of Si-H bonds causing interface traps, gradual breakdown of gate dielectric due to vertical electrical field, electrons/holes moving in unwanted directions under large lateral, and transversal fields.

# 1.4.1 Bias Temperature Instability (BTI)

Since the invention of semiconductor transistors, it has been widely known that high voltage and/or temperature stress on the gate electrode with  $SiO_2$  as gate dielectric can change the flatband-voltage  $V_{\rm fb}$  or the threshold-voltage  $V_{\rm T}$  of MOS transistors [13]. This phenomenon is called Bias-Temperature-Instability (BTI). Several researchers have extensively studied the impact of positive as well as negative high voltage stresses on MOS FETs. With  $SiO_2$  as the dielectric, the main focus was only on negative BTI (NBTI) which impacts PFETs. However, with the usage of HfO<sub>2</sub> as part of the gate dielectric to facilitate scaling, positive BTI (PBTI) which impacts NFETs has also become significant.

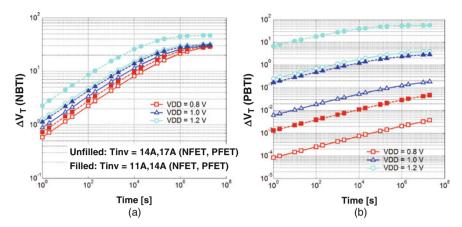

**Fig. 1.12** Time-dependence of threshold voltage in TiN- and Re-gated devices with SiO2/HfO2 as dielectric stack due to (a) NBTI (on PFET), and (b) PBTI (on NFET). Two cases of inversion thicknesses (Tinv) are shown to analyze the impact of scaling *Source*: [15]

We saw that high temperatures cause  $|V_T|$  to reduce, thereby giving a chance to have higher performance; however, mobility also reduces resulting in a conflict and eventually causing higher leakage power and lower performance. Interestingly (and conveniently too), most of the effects of device aging mechanisms can be understood by the change in  $V_T$  only. Figure 1.12 shows the time-dependence of threshold voltage shift due to NBTI and PBTI. Scaling the inversion layer thickness ( $T_{\rm inv}$ ) increases the vertical electric field at the given  $V_{\rm DD}$  causing increase in  $V_T$  shifts due to BTI.

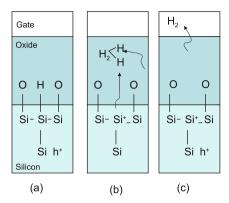

#### 1.4.1.1 Negative-Bias-Temperature-Instability (NBTI)

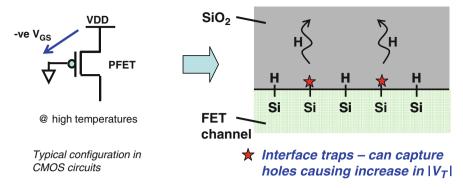

NBTI relates to the instability induced in a FET due to generation of traps at FET channel and gate dielectric interface. A FET's channel is made of highly ordered crystalline silicon whereas gate dielectric is traditionally made of amorphous SiO<sub>2</sub>. The interface surface of these two dissimilar materials is rough, resulting in dangling Si atoms from the channel due to unsatisfied chemical bonds. These dangling atoms are the interface traps which can lead to poor performance (lower on-state current) due to charge trapping and scattering. Hence, traditionally, the FETs are hydrogen annealed during fabrication after the formation of Si-SiO<sub>2</sub> interface. Hydrogen gas diffuses to the interface resulting in binding of hydrogen atoms (H) to the dangling Si atoms. Figure 1.13 shows the resulting Si-SiO<sub>2</sub> interface with hydrogen-passivated Si atoms. These Si-H bonds can break under large vertical negative electrical field ( $V_{GS}$ ,  $V_{GD} < 0$ ) and high temperature. Dissociation of Si-H atoms will result in generation of interface traps. Note that when gate-drain and gate-source voltages are negative in a PFET, channel is inverted and conducting (whereas NFETs are off or under accumulation). Holes in PFET's inversion layer tunnel to SiO<sub>2</sub>, and are captured by the Si-H bonds thereby weakening the bond.

Fig. 1.13 Schematic of hydrogen dynamics after it is released from a Si-H bond. Interface traps are denoted by \* [16]

Subsequently, high temperatures result in dissociation of Si–H pair resulting in one donor-like interface trap or Si dangling bond, and one H atom which diffuses in the oxide. These interface traps can capture the holes in an inverted PFET channel resulting in  $V_{\rm GS}$  to become *extra* negative to reach similar strong inversion which existed without interface traps. Hence,  $V_{\rm T}$  of a PFET will become more negative ( $|V_{\rm T}|$  will increase) resulting in reduced on-state current (keeping same  $V_{\rm DD}$ ). Note that such increase of  $|V_{\rm T}|$  in a PFET also reduces off-state leakage power, and effective capacitance thereby reducing active power. This change in  $V_{\rm T}$  of a PFET is called NBTI-induced change in  $V_{\rm T}$ .

In early (before the year 2000) technologies, power supply was reduced with gate dielectric scaling to maintain the near constant vertical electrical field. However, in recent technologies, power supply is scaled less aggressively compared to gate—dielectric to improve performance. This has resulted in increased vertical electric field. Further, power density is increasing due to packing of more functionality in same area with every technology resulting in increased local temperatures. Also, oxides are nitrided to prevent Boron penetration from polysilicon gate to the Si channel. Nitrogen is also added in gate dielectric to increase gate dielectric constant thereby increasing gate capacitance and performance. Unfavorably, it increases the NBTI-induced generation of interface traps [17].

Present day VLSI circuits operate at high temperatures ( $\sim$ 60–100°C) and also have large vertical electric field resulting in NBTI induced generation of interface traps in PFETs. The interface traps make the  $V_{\rm T}$  of a PFET more negative and reduce carrier mobility. There are several physics models proposed by researchers; the most popular among them is reaction-diffusion model [18–24]. According to R-D model, inversion holes can break Si–H bonds freeing up H atoms (neutral) and creating donor like interface traps. H atoms can either diffuse away from the interface into the oxide or can anneal an existing trap. Interface traps result in increased  $V_{\rm T}$  which can be given as

$$\Delta V_{\rm T}(t) \approx (m_{\mu} + 1) \frac{q N_{\rm IT}(t)}{C_{\rm ox}} t^n \tag{1.3}$$

where  $m_{\mu}$  is the mobility-degradation factor,  $N_{\rm IT}$  is the number of interface traps at time t, and  $C_{\rm ox}$  is oxide capacitance. The time-exponent n is  $\sim 1/6$  [22, 23] for onthe-fly measurements whereas it is >1/6 for delay-based measurements. Here, we will take n=1/6 and include the recovery separately. Along with interface trap generation, other processes such as hole-trapping can also occur [25, 26] changing the form of above equation. Hence, in current technologies, change in  $V_{\rm T}$  is empirically estimated by fitting the equation below

$$\Delta V_{\rm T}(t) = A.V_{\rm stress}^k e^{-Ea/kT} t^n \tag{1.4}$$

where parameters A, k, n, and Ea (activation energy) are fitted to match measured data.  $V_{\rm stress}$  is the stress voltage. Typically the chip testing time (approximately days—weeks) is significantly shorter than the desired lifetime ( $\sim 10$  years). Hence, accelerated characterization is performed at elevated stress voltages and temperatures, and the models are generated to predict the lifetime of a FET under operating voltage and temperatures.

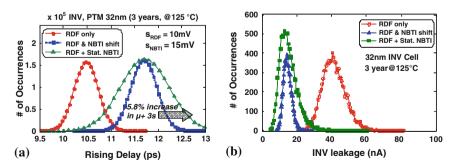

#### Spatial Variation in NBTI

NBTI primarily depends on the number of interface traps. If a FET size  $(L \times W)$  is small, the number of traps can differ between FETs resulting in different NBTI degradation even at identical stress conditions. This difference in number of traps between FETs is observed to be random in nature and follow similar scaling law as RDF. Stewart Rausch [27] has given a semi-analytical model to quantify the statistics of  $V_{\rm T}$  mismatch between the neighboring FETs in sub-100 nm technologies. The standard deviation of distribution of  $\Delta V_{\rm T}$  follows Poisson model (dependence on mean  $\Delta V_{\rm T}$  shift) and can be written as

$$\sigma_{\Delta}V_{\rm T} = \sqrt{\frac{2K_1qT_{\rm ox,eff}Mean(\Delta V_{\rm T})}{\varepsilon_{\rm ox}A_{\rm G}}}$$

(1.5)

where  $T_{\text{ox,eff}}$  is the effective oxide thickness of gate dielectric,  $\varepsilon_{\text{ox}}$  is the dielectric constant of SiO<sub>2</sub>,  $A_{\text{G}}$  is the gate area  $(L \times W)$  and mean  $(\Delta V_{\text{T}})$  is the mean shift in  $V_{\text{T}}$  as computed by (Equation 1.4).  $K_{\text{1}}$  is an empirical parameter and found to be between 2.5 and 3.0 in most of the measured cases. Inclusion of NBTI statistics for analysis becomes important in small area FETs such as SRAM arrays.

#### 1.4.1.2 Positive-Bias-Temperature-Instability (PBTI)

To reap the benefits of technology scaling, gate dielectric (primarily  $SiO_2$ ) thickness is aggressively scaled to increase gate capacitance, thereby increasing gate control over the channel. In sub-50-nm MOSFETs, due to short-channel effects,  $SiO_2$  needs to be scaled to  $\sim 1$  nm. Such thin gate oxides result in high gate direct tunneling leakage currents. Hence, the introduction of high-k gate dielectric became inevitable

in sub-50-nm technologies. HfO<sub>2</sub> is one of the most promising candidates as high-k dielectric due to large dielectric constant 20–25, large band gap (5.6 eV), and thermal stability in contact with silicon.

The  $V_{\rm T}$  shift in MOSFETs with high-k dielectric is primarily attributed to charge trapping in high-k layer [28]. The trap density in high-k layer is much higher than SiO<sub>2</sub>. Hence, at low stress voltages,  $V_{\rm T}$  shifts due to filling of existing traps. Creation of traps is observed at high stress voltages. The reasons for significant charge trapping in high-k gate stacks can be attributed to process-induced defects, impurities, and material-related traps. There have been significant researches in last few years to understand the charge trapping phenomenon [29–32], deemed necessary for optimizing high-k dielectric for VLSI circuits. The  $\Delta V_{\rm T}$  due to PBTI is computed in similar fashion as for NBTI by empirically fitting the Equation (1.4).

#### 1.4.1.3 BTI Recovery

As a FET is turned OFF, it relaxes thereby releasing the trapped charges. Traps can be broadly classified as slow and fast traps. Fast traps get relaxed quickly but slow traps release charges relatively slowly. They can also be classified as recoverable and permanent components of BTI-induced  $V_T$  shift [33]. Fraction Remaining (FR), after the stress has been removed, follows the universal recovery curve [34, 35].

$$FR = \frac{1}{1 + \alpha \left(\frac{T_{\text{relax}}}{T_{\text{stress}}}\right)^n}$$

(1.6)

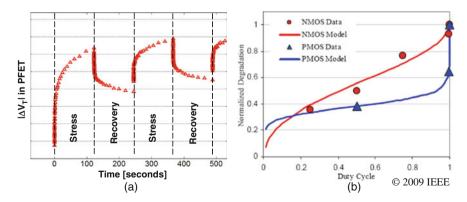

where  $T_{\rm relax}$  is the duration of relaxation and  $T_{\rm stress}$  is the stress time.  $\alpha$  is an empirical parameter (fitted separately for NBTI and PBTI) and n is the time exponent used in Equation (1.4). Figure 1.14a illustrates the  $\Delta V_{\rm T}$  with multiple stress-relaxation-stress cycles. Note that as soon as the stress is removed, recovery happens. Figure 1.14b shows the impact of duty cycle on the  $V_{\rm T}$  degradation. Duty

Fig. 1.14 (a) PMOS Stress-Relax-Stress behavior. (b) Alternating OTF measurements for varying duty cycle. Duty cycle of 1 represents the static stress *Source*: [36]

cycle of 1 represents the static stress when the FETs are continuously ON. Duty cycle of 0.5 represents alternating stress causing FETs to be ON 50% of the time. It shows that in a circuit, if we can somehow make sure that a FET does not see static stress, we can increase the life of IC.

Typically we do accelerated stress at very high voltage (sometimes just below the breakdown limit) and then lower the voltage to measure the change in  $V_{\rm T}$ .  $V_{\rm T}$  is typically measured using constant drain current method ( $V_{\rm GS}$  when  $I_{\rm ds}$  is some pre-determined value). FET instantaneously recovers as soon as the gate voltage is lowered to measure  $V_{\rm T}$ , making it difficult to measure the actual change in  $V_{\rm T}$ . Several measurement techniques have been proposed to circumvent this. One popular method is on-the-fly (OTF) measurement. In OTF, we measure the drain current (let us say with  $|V_{\rm GS}| = V_{\rm DD}$  and  $|V_{\rm DS}| = 50$  mV at time t = 0 and build a relationship  $I_{\rm dlin} = k(V_{\rm DD} \cdot |V_{\rm T}|)^{\rm alpha}$ . Now, during measurement, instead of measuring  $V_{\rm T}$ , we measure  $\Delta I_{\rm dlin}$  and back compute the  $\Delta V_{\rm T}$ . Further, recovery varies with the mechanism – NBTI or PBTI – as well as with varying gate stack [37]. Hence, as technology is changed, empirical fitting parameters in BTI-induced  $V_{\rm T}$  shift equations may have to be retuned.

#### 1.4.1.4 Estimation and Impact of BTI in Circuits

In the experiments, FETs are typically stressed using static stress (gate is always ON during stress) and alternating stress (gate is switching at different frequencies with varying duty cycle). These stresses can be conveniently used to generate a threshold voltage model dependent on stress time, frequency and duty cycle. However, in a circuit, more often each FET sees a unique gate signal during the life of usage. This signal depends on

#### Applications Executed:

For example, an application involving multiplication of 40-bit data on a 64-bit multiplier will result in the 24 most significant bits never switching. Another example can be clock signals which always switch irrespective of computation being done in logic blocks.

Also, in a cache (say SRAM), it is quite possible that some bits are regularly flipped whereas some bits are read often but not flipped resulting in varying impact of BTI between bits. We will study the impact of BTI in SRAMs in more detail in the next section.

Power Reduction Techniques Used – Dynamic Voltage Scaling (DVS), power-gating, etc.

In a multi-core chip, all the cores are rarely used at maximum throughput. A core not heavily needed can be run at a lower frequency (by lowering the power supply voltage) to save power. This will result in lower BTI impact in this core. Further, if a core is completely shut down (say using power-gating), it will help in recovery.

There are recent efforts to build commercial tools [38], which can monitor the gate signal of each FET and apply suitable threshold voltage shift using

pre-characterized models. This enables a designer to estimate the EOL shift in a circuit's performance, power, or robustness under real usage conditions. Other efforts are focused to build a BTI aware standard cell library [39].

From circuit application point of view, the nature and analysis of BTI can be broadly classified into two categories – impact of BTI in logic circuits (performance and power are major concerns) and memory circuits (stability and performance are major concerns). In this section, we will focus on these two separately.

#### **BTI Impact in Logic Circuits**

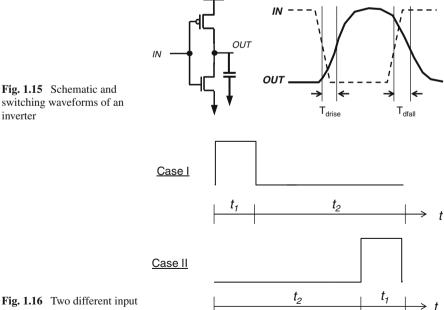

Critical metrics for a logic circuit are performance and power. As we studied earlier, BTI results in increased threshold voltage of NFETs and PFETs which can result in lower currents thereby reducing performance and leakage power dissipation. First let us analyze the impact of BTI on a static CMOS inverter. Figure 1.15 shows the output response of an inverter to an input voltage pulse. The output rise time primarily depends on the strength of PFET to charge the output load to  $V_{\rm DD}$ , whereas, output fall time depends on the strength of NFET to discharge the output load. NBTI and PBTI will reduce the driving strengths of PFET and NFET, respectively, resulting in increased rise and fall delays. The change in  $V_T$  will depend on the duration for which a FET was ON. For example, let us consider two input voltage pulses as shown in Fig. 1.16. In both the cases, the input is high for the duration  $t_1$  and low for the duration  $t_2$ . Let us look at the net FET degradation in both the cases computed by multiplying  $\triangle V_T$  due to stress (Equation (1.4)) and fraction remaining (Equation (1.6)):

signals to an inverter

Case - I:

$$\Delta V_{\rm T}(\rm PFET) = F_{\rm NBTI}(t_2)\dots(a) \quad \Delta V_{\rm T}(\rm NFET) = \frac{F_{\rm PBTI}(t_1)}{\left(1 + \alpha_{\rm PBTI} \left(\frac{t_2}{t_1}\right)^{\beta_{\rm PBTI}}\right)}\dots(b)$$

(1.7)

Case – II:

$$\Delta V_{\rm T}(\rm PFET) = \frac{F_{\rm NBTI}(t_2)}{\left(1 + \alpha_{\rm NBTI} \left(\frac{t_1}{t_2}\right)^{\beta_{\rm NBTI}}\right)} \dots (a) \quad \Delta V_{\rm T}(\rm NFET) = F_{\rm PBTI}(t_1) \dots (b)$$

$$(1.8)$$

Where  $F_{NBTI}$  and  $F_{PBTI}$  are the  $V_T$  shifts due to stress and computed using Equation (1.4). The FET degradation in the two cases is quite different. Hence, it is important to consider the actual signal at the gate instead of just looking in terms of duty cycle. If instead of looking at actual signal we had assumed that in the total time of  $t_1 + t_2$ , NFET (PFET) is stressed for the duration of  $t_1(t_2)$  and relaxed for the duration of  $t_2(t_1)$ , we would have wrongly estimated the same degradation in both the cases –(Equation (1.7b)) for NFET and (Equation (1.8a)) for PFET. That would have resulted in underestimation of PFET degradation in case I and underestimation of NFET degradation in case II. In practice, during EOL estimation via simulation, it can be quite difficult to monitor the input signal of each FET in a complex circuit. Computation complexity is traded with accuracy by averaging the signal over a long period of time. To date, no such efficient method exists which can accurately estimate the usage-based EOL degradation in each FET of a complex VLSI circuit.

The challenge in front of a circuit designer is to ensure reliable functionality of a circuit during the life of usage. If EOL shift can be accurately predicted during pre-Si circuit tuning, a sufficient guard-banding can be applied such as making extra slack available in critical paths. However, it can be quite difficult to test a circuit for all benchmark applications while monitoring the gate signal of each FET. Hence, on-chip BTI monitors are required to continuously monitor the frequency degradation in a chip and make self-repairs if necessary. The nature of self-repairs can be:

- In multi-core processors, shutting down a core for some time to do BTI recovery

- Power-gating the unused portions of a chip to do BTI recovery along with saving power

- Lowering voltage to reduce stress

- Using redundant copies of the degraded circuits, especially if the primary circuits become unusable due to HCI or TDDB (discussed in next section).

One other important aspect of analyzing BTI impact on a circuit is understanding the relative sensitivity of a circuit's performance to NBTI and PBTI. To a first order, the relative sensitivities of their drive current's strength to  $V_T$  can be simplified as

$$\frac{(\partial I_{\rm DS}/\partial V_{\rm T})\mid_{\rm pull-down}}{(\partial I_{\rm DS}/\partial V_{\rm T})\mid_{\rm pull-up}} = \left(\frac{\mu_{\rm electron}}{\mu_{\rm hole}}\right) \left(\frac{W_{\rm pull-down}}{W_{\rm pull-up}}\right) \tag{1.9}$$

Typically, electron mobility ( $\mu_{electron}$ ) in pull-down NFET is twice of hole mobility ( $\mu_{hole}$ ) in pull-up PFET and width of pull-up ( $W_{pull-up}$ ) is designed to be higher than the width of pull-down ( $W_{pull-down}$ ) to balance the rise and fall delays. For example, 50 mV of  $V_T$  shift in either PFET (due to NBTI) or NFET (due to PBTI) will result in approximately same amount of increase in RO frequency.

### **BTI Impact in Memory Circuits**

BTI can be understood as increase in  $V_{\rm T}$  with time. As we saw earlier that the impact of BTI can potentially be different for each FET in a circuit. Hence, the ratioed circuits which primarily depend on the relative driving strengths among different FETs can be severely affected. In this section, we focus on Static Random Access Memory (SRAM) to understand the impact of BTI [15, 40, 41].

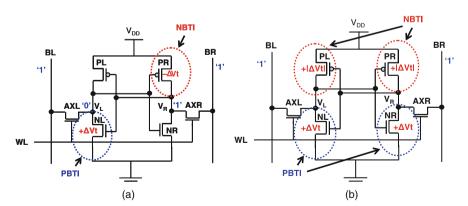

Figure 1.17 shows the schematics of an SRAM cell under two conditions – static stress and alternating stress. Static stress happens when a cell is storing the same data for long period of time resulting in a cell becoming asymmetric, i.e., NL (due to PBTI) and PR (due to NBTI) become weak. Note that a cell will undergo static stress even if it is read several times or written with the same data several times. Due to static stress, gradually, the read operation will become unstable in this cell – reading "0" at left-node may cause failure as NL has become weak. We do not consider the impact of PBTI in access FETs (AXL and AXR) because they are turned on for short duration of time. However, in some cases when a cell is accessed very frequently, the access FETs may also become weak resulting in reduced impact of PBTI on read stability. Weaker pull-down NFET will also reduce the read current resulting in increased access time. Read current dictates how fast the BL discharges through the series combination of AXL and NL (for  $V_L$ = "0"). Since reading is getting unstable due to static stress, writing will become easier. For example, flipping the left node from "0" to "1" will become easier because NL has become weak whereas PL retains its original strength. Also flipping the right node from

Fig. 1.17 Schematic of SRAM cell showing the FETs affected under (a) Static stress, and (b) Alternating stress

"1" to "0" has become easier because PR has become weak whereas NR retains its original strength. Hence, flipping data after long duration of static stress will become easier. On the other hand, a second write to *again flip the data* will become difficult [15].

Alternatively, a cell may be regularly flipped over the period of use resulting in the cell storing "0" and "1" for approximately same duration of time. This will keep the cell symmetric, i.e., same PBTI degradation in NL and NR, and same NBTI degradation in PL and PR (Fig. 1.17b). Considering negligible degradation in access FETs, the read will gradually become unstable and read access time will also increase (due to weak pull-down NFETs). Write operation will become easier, and unlike static stress, even second write operation will also be easier. Further, for a given duration of use, each FET will see the effective stress of half the use time and relaxation for the remaining half. On the other hand, static stress will cause the two FETs (NL and PR) to see the stress during whole use time without any recovery. Note that the static and alternating stress cases are the two extremes. Majority of cells in an SRAM array will see the stress somewhere in between.

In SRAM cells, width of pull-down is typically made higher than the width of pull-up to maintain read stability. Looking at (Equation (1.9)), let us assume that  $\mu_{\rm electron} \sim 2\mu_{\rm hole}$  and  $W_{\rm pull-down} \sim 2.5W_{\rm pull-up}$ . Now, 50 mV of  $V_{\rm T}$  shift due to PBTI will reduce the drive strength of pull-down NFET roughly 5X more than the similar  $V_{\rm T}$  shift due to NBTI will do in PFET. Hence, the stability (read and write) of an SRAM cell is more sensitive to PBTI than NBTI.

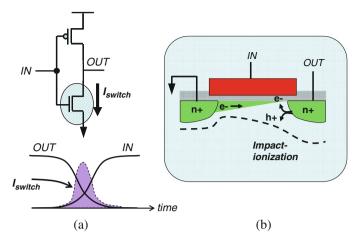

## 1.4.2 Hot-Carrier-Injection (HCI)

Let us consider an NFET (as part of static CMOS inverter) during switching (Fig. 1.18). Its gate voltage rises turning it ON resulting in discharge of output node or drain. As the gate-to-source voltage rises, channel gets inverted resulting in abundance of electrons in the channel. In the initial part of switching, when drain-to-source voltage is high resulting in large lateral electric field, electrons gain high kinetic energy (called hot electrons) and accelerate toward drain. Near drain junction, the hot electrons generate secondary carriers through impact ionization. These primary and secondary electrons can gain enough energy to be injected into the gate stack resulting in the creation of traps at silicon/gate-dielectric interface and also bulk traps in the dielectric. These traps are electrically active and capture carriers at energy levels within the bandgap resulting in increased threshold voltage. HCI occurs in both NFETs and PFETs, however, it is prominent in NFETs because electrons face a smaller potential barrier than holes at the silicon/gatedielectric interface. This aging mechanism has become less prominent in sub-50-nm technologies due to reduced operating voltages; however, it remains a concern due to high local electric fields. In addition, the dependence of HCI on stress time is higher than BTI bringing it at the forefront of aging culprits after long periods of usage.

Fig. 1.18 (a) Schematic of an inverter showing switching current during input rising; (b) shows the mechanism of charged carriers causing impact ionization

The HCI occurs while a FET is switching contrary to BTI which is dependent on the gate voltage. HCI is empirically estimated in same way as BTI by empirically fitting (equation (1.4)). Authors in [42] measured HCI by separating it from BTI+HCI degradation.

## 1.4.3 Time-Dependent Dielectric Breakdown (TDDB)

As the name (TDDB) suggests, this phenomena pertains to gate dielectric breakdown under high vertical electric fields. Large voltage drop across the gate stack results in the creation of traps (or defects) within the gate dielectric. These defects may join together and form a conductive path through the gate stack causing dielectric breakdown. TDDB is an increasing concern as gate dielectric thicknesses are scaled down causing *faster* breakdown of gate–dielectric (less defects required to cause breakdown). The physical scaling of gate dielectric has been slowed down with the introduction of high-k dielectric materials; however, it is still a critical aging mechanism.

TDDB is measured by noticing the sudden jump in gate current. However, in today's sub-2-nm gate dielectrics, gate tunneling current is high enough to mask the jump in current. In TDDB analysis, mean-time-to-failure (MTTF) at a particular voltage bias is critical. In low-power circuits, the creation of first conductive or breakdown path through the gate dielectric seldom destroys the transistor. The lifetime of a FET after first breakdown typically depends on the spatial and temporal dependence of the subsequent breakdown [43, 44].

First order impact of TDDB in a circuit can be analyzed by connecting a resistor between gate-source and/or gate-drain in circuit simulations. Instead of a resistor, a constant current source can also be included to simulate the effect of gate current

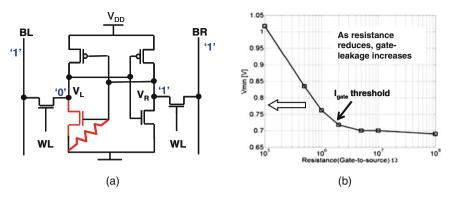

**Fig. 1.19** (a) An SRAM cell with breakdown in left pull-down FET simulated by connecting a resistor. (b) Change in Vmin with resistance. Igate threshold represents the maximum gate leakage this cell can tolerate before suddent jump in Vmin

during breakdown. For example, Fig. 1.19 shows the simulation of gate–dielectric breakdown in the left pull-down FET of an SRAM cell by connecting a resistor between the gate and source. The value of resistance is varied to obtain the change in minimum operating voltage  $(V_{\min})$ . This analysis can help a reliability engineer to obtain the gate current  $(I_{\text{gate}})$  tolerance of a particular circuit.

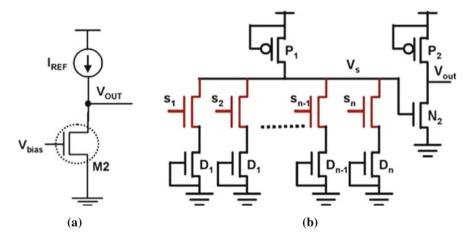

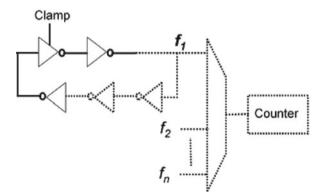

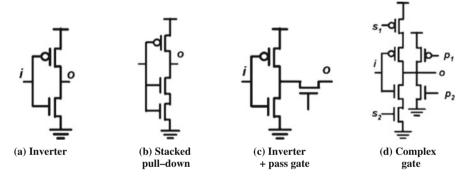

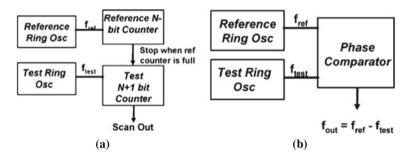

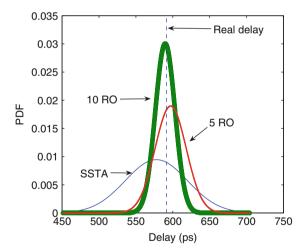

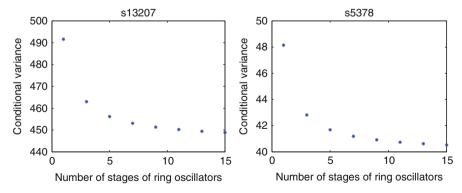

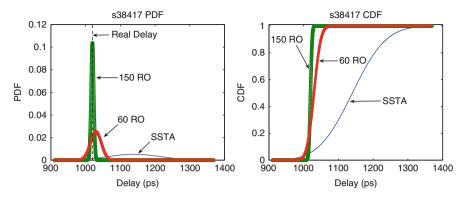

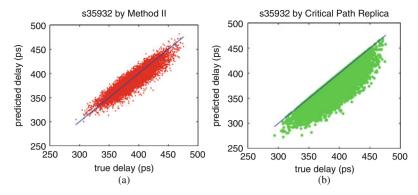

### 1.5 Characterization Circuits