# Srinivasan Murali

# Designing Reliable and Efficient Networks on Chips

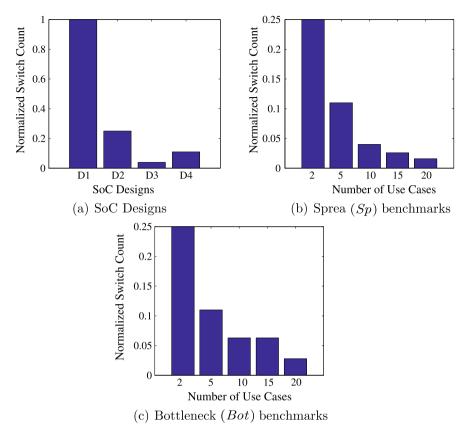

Designing Reliable and Efficient Networks on Chips

For other titles published in this series, go to www.springer.com/series/7818

Srinivasan Murali

# Designing Reliable and Efficient Networks on Chips

Dr. Srinivasan Murali INF 331, Station 14, EPFL 1015 Lausanne Switzerland srinivasan.murali@epfl.ch

ISBN 978-1-4020-9756-0

e-ISBN 978-1-4020-9757-7

DOI 10.1007/978-1-4020-9757-7

Library of Congress Control Number: 2008944292

© 2009 Springer Science + Business Media B.V.

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Printed on acid-free paper

987654321

springer.com

## Preface

The complexity of *Multiprocessor Systems on Chips (MPSoCs)* is growing rapidly with the advances in semiconductor technology. The number of processors, hardware cores, and memories on a single chip is increasing and a highly-scalable communication infrastructure is required to connect them. To effectively tackle the interconnect complexity of current and future MPSoCs, a communication-centric design approach, *Networks on Chips (NoCs)*, has recently emerged. NoCs bring the networking principles for data transfer, such as those used in large area networks (e.g., the Internet), to the on-chip domain.

Developing NoC-based systems tailored to a particular application domain, satisfying the application performance constraints with minimum power-area overhead is a major challenge. With technology scaling, as the geometries of on-chip devices reach the physical limits of operation, another important design challenge for NoCs will be to provide dynamic (run-time) support against permanent and intermittent faults that can occur in the system.

The purpose of this book is to provide state-of-the-art methods to solve some of the most important and time-intensive problems encountered during NoC design. We present methods for topology synthesis, mapping of cores onto NoC topologies, crossbar sizing, route generation, resource reservation, achieving fault-tolerance, RTL code, and layout generation. We show how the different design methods can be integrated to make a complete tool flow for designing reliable and efficient NoCs for application-specific MPSoCs and chip multiprocessors. To have less design respins and faster time-to-market, we show how the architectural synthesis models can be integrated with back-end physical design tools and models, thereby bridging a big design gap in on-chip interconnect synthesis.

Key features of book:

- Presents in depth the state-of-the-art algorithms and optimization models for performing system-level design of NoCs

- Presents an integrated flow to design interconnect architectures that can lead to faster time-to-market and design closure

- Shows evolution of design methods from complex crossbar based buses to NoCs

- Presents static and run-time methods for achieving reliable operation of the NoC and the entire system

This book should be of interest to:

- System level architects and designers: The methods show how to improve design productivity and achieve design closure of SoCs.

- Communication architecture/interconnect designers: The methods show trade-off analysis and explorations of NoCs.

• Design automation engineers: The high-level synthesis methods and mathematical models presented in this book can be applied to solve several communication architecture issues. They are also of general interest to designers working in related fields, such as sensor, body-area, and automotive networks.

This book is based on my Ph.D. research work done at Stanford University. I am greatly indebted to my adviser Prof. Giovanni De Micheli and co-adviser Prof. Luca Benini (University of Bologna), as they were instrumental in shaping the ideas presented here. The work is a result of collaboration with many researchers. I thank all my collaborators: Dr. Federico Angiolini and Antonio Pullini of iNoCs, Prof. David Atienza (EPFL), Dr. Kees Goossens and his team (Dr. Andrei Radulescu, Martijn Coenen, Andreas Hansson) at NXP research, Prof. Davide Bertozzi (University of Ferrara), Rutuparna Tamhankar (Marvell Technology), Prof. N. VijayKrishnan, Prof. Mary Jane Irvin and Dr. Theocharis Theocharides at Pennsylvania State University, Prof. Salvatore Carta, Paolo Meloni and Prof. Luigi Raffo of University of Cagliari for their contributions to this work.

EPFL, Lausanne, Switzerland

Srinivasan Murali

# Contents

| Pre | face |         |                                                       | v  |

|-----|------|---------|-------------------------------------------------------|----|

| 1   | Intr | oductio | m                                                     | 1  |

|     | 1.1  |         | orks on Chips: Scalable Interconnects for SoCs        | 1  |

|     | 1.2  |         | Design Challenges                                     | 4  |

|     | 1.3  |         | Overview                                              | 5  |

|     |      | 1.3.1   | NoC Design Methods                                    | 5  |

|     |      | 1.3.2   | NoC Reliability Mechanisms                            | 7  |

|     | 1.4  | Relate  | d Work                                                | 7  |

|     |      | 1.4.1   | NoC Architectures and Design Methods                  | 8  |

|     |      | 1.4.2   | Reliability Support for NoCs                          | 10 |

| Par | t I  | NoC D   | Design Methods                                        |    |

| 2   | Desi | gning ( | Crossbar Based Systems                                | 15 |

|     | 2.1  | Proble  | m Motivation and Application Traffic Analysis         | 17 |

|     |      | 2.1.1   | Problem Motivation                                    | 17 |

|     |      | 2.1.2   | Application Traffic Analysis                          | 19 |

|     | 2.2  | Design  | n Methodology                                         | 19 |

|     | 2.3  | Exact   | Approach to Crossbar Synthesis                        | 22 |

|     |      | 2.3.1   | Problem Formulation                                   | 22 |

|     |      | 2.3.2   | Exact Crossbar Synthesis Algorithm                    | 24 |

|     | 2.4  |         | stic Approach to Crossbar Synthesis                   | 24 |

|     | 2.5  | Experi  | iments and Case Studies                               | 28 |

|     |      | 2.5.1   | Experimental Platform and Power Models                | 28 |

|     |      | 2.5.2   | Application Benchmark Analysis                        | 29 |

|     |      | 2.5.3   | Comparisons of Heuristic Engine with the Exact Engine | 32 |

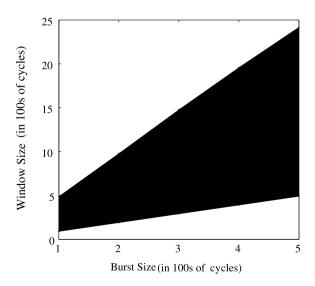

|     |      | 2.5.4   | Window Sizing                                         | 34 |

|     |      | 2.5.5   | Real-Time Streams & Effect of Binding                 | 36 |

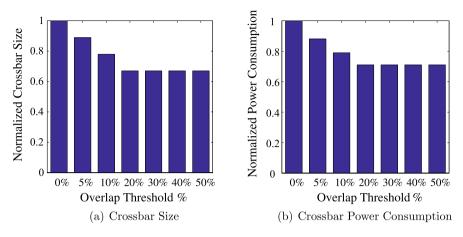

|     |      | 2.5.6   | Overlap Threshold Setting                             | 36 |

|     | 2.6  | Summ    | ary                                                   | 37 |

| 3   | Neto |         | ol Flow for NoC Design                                | 39 |

|     | 3.1  | Front-  | End Design Phase                                      | 39 |

|     | 3.2  |         | ectural Design Phase: The ×pipes NoC Library          | 40 |

|     | 3.3  | Summ    | ary                                                   | 42 |

| 4   | Desi |         | Standard Topologies                                   | 43 |

|     | 4.1  |         | nip Traffic Modeling                                  | 45 |

|     | 4.2  | Proble  | m Formulation                                         | 47 |

|   | 4.3  | Mapping and Physical Planning Algorithm    | 50 |

|---|------|--------------------------------------------|----|

|   | 4.4  | Physical Planning                          | 51 |

|   | 4.5  | Experiments and Case Studies               | 53 |

|   |      | 4.5.1 Effect of Physical Planning          | 53 |

|   |      | 4.5.2 Design for QoS Guarantees            | 53 |

|   |      |                                            | 54 |

|   |      |                                            | 54 |

|   | 4.6  |                                            | 56 |

| 5 | Desi | igning Custom Topologies                   | 57 |

|   | 5.1  | Objectives                                 | 57 |

|   |      | 5.1.1 Background on NoC Topology Synthesis | 58 |

|   |      |                                            | 59 |

|   | 5.2  | Input Models                               | 60 |

|   |      | 5.2.1 Area, Power Models                   | 60 |

|   |      | 5.2.2 Traffic Models                       | 62 |

|   | 5.3  |                                            | 62 |

|   | 5.4  |                                            | 68 |

|   |      |                                            | 68 |

|   |      |                                            | 70 |

|   |      |                                            | 72 |

|   |      | 1 1 2                                      | 74 |

|   | 5.5  |                                            | 74 |

| 6 | Sup  | porting Multiple Applications              | 77 |

|   | 6.1  |                                            | 78 |

|   |      |                                            | 79 |

|   |      |                                            | 79 |

|   | 6.2  |                                            | 80 |

|   | 6.3  |                                            | 82 |

|   | 6.4  |                                            | 83 |

|   | 6.5  |                                            | 89 |

|   |      |                                            | 89 |

|   |      | -                                          | 90 |

|   |      |                                            | 90 |

|   |      |                                            | 92 |

|   |      |                                            | 93 |

|   | 6.6  |                                            | 93 |

| 7 | Sup  | porting Dynamic Application Patterns       | 95 |

|   | 7.1  |                                            | 95 |

|   | 7.2  |                                            | 97 |

|   | 7.3  |                                            | 98 |

|   | 7.4  | 6                                          | 99 |

|   | 7.5  |                                            | 01 |

|   |      |                                            | 02 |

|   |      | e e                                        |    |

|     |      | 7.5.2   | Timing Feasibility Check                                 |   |     |

|-----|------|---------|----------------------------------------------------------|---|-----|

|     |      | 7.5.3   | Algorithm Run-Time                                       |   |     |

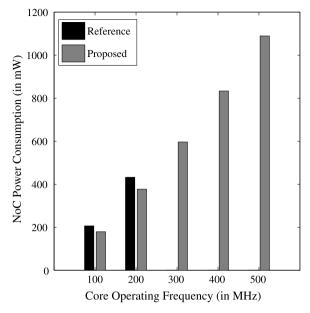

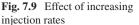

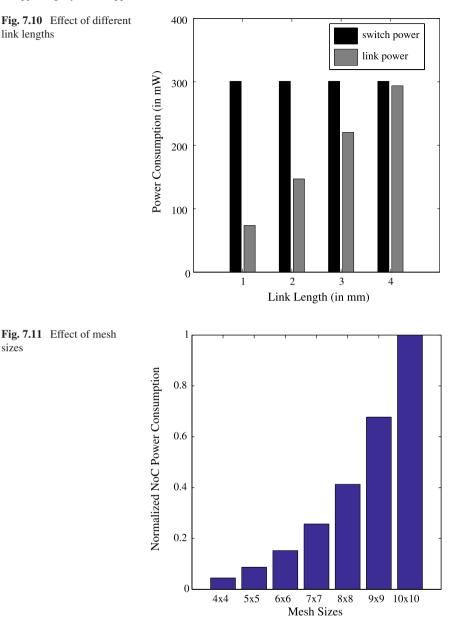

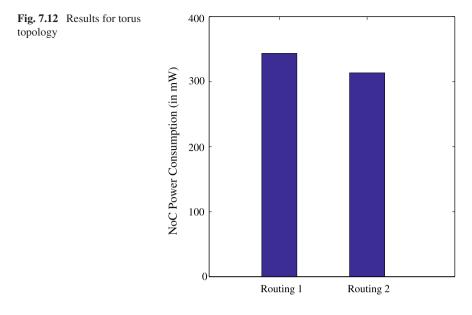

|     | 7.6  | Experi  | mental Results                                           |   | 105 |

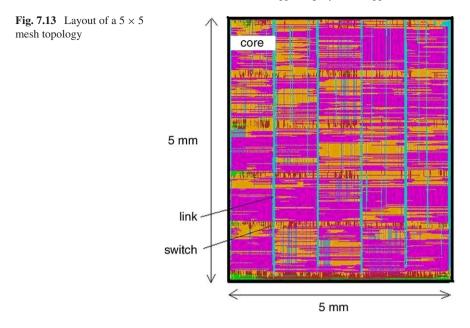

|     |      | 7.6.1   | Experiments on a Mesh Topology                           |   | 106 |

|     |      | 7.6.2   | Effect of Core Injection Rates                           |   |     |

|     |      | 7.6.3   | Effect of Different NoC Sizes                            |   |     |

|     |      | 7.6.4   | Effect of Link Length                                    |   | 110 |

|     |      | 7.6.5   | Application to Torus Topology                            |   | 110 |

|     |      | 7.6.6   | Validating Design Flow Predictability                    |   | 111 |

|     | 7.7  | Summ    | ary                                                      | • | 112 |

| Par | t II | NoC R   | Reliability Mechanisms                                   |   |     |

| 8   | Timi | ing-Err | or Tolerant NoC Design                                   |   | 117 |

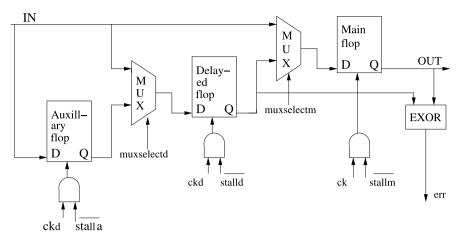

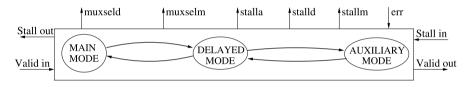

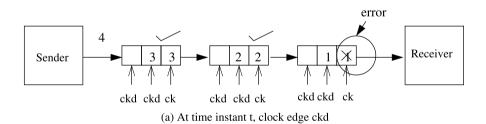

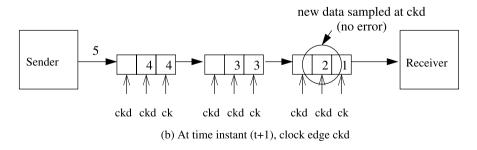

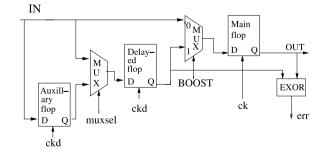

|     | 8.1  | 0       | ouble Sampling Technique                                 |   |     |

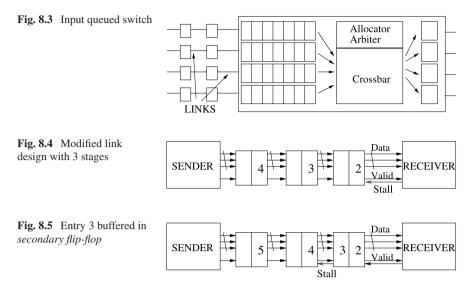

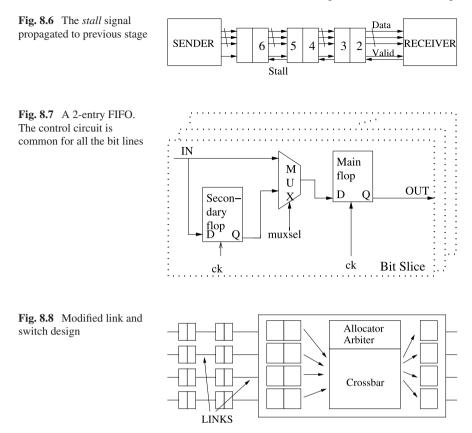

|     | 8.2  |         | Links as a Storage Medium                                |   |     |

|     | 8.3  |         | r Link Designs                                           |   |     |

|     |      | 8.3.1   | Scheme 1: Low overhead <i>T-error</i> Links              |   |     |

|     |      | 8.3.2   | Scheme 2: High-Performance <i>T-error</i> Links          |   |     |

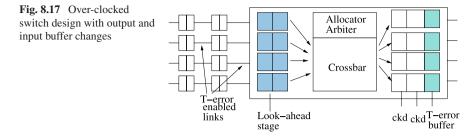

|     | 8.4  | Aggres  | ssive Switch/NI Design                                   |   |     |

|     |      | 8.4.1   | Output Buffer Changes                                    |   |     |

|     |      | 8.4.2   | Input Buffer Changes                                     |   |     |

|     | 8.5  | Dynan   | nic Configuration of the NoC                             |   |     |

|     | 8.6  |         | mental Results                                           |   |     |

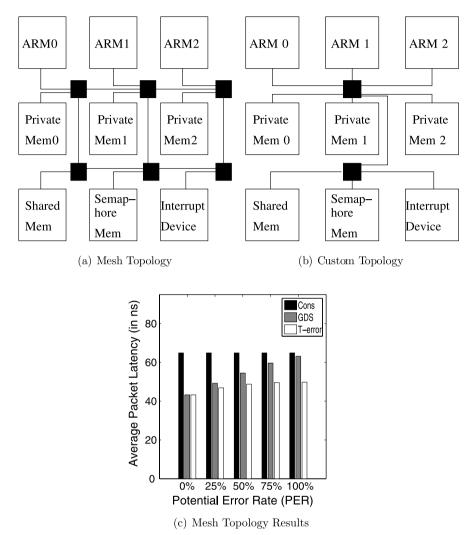

|     |      | 8.6.1   | Simulation Platform                                      |   |     |

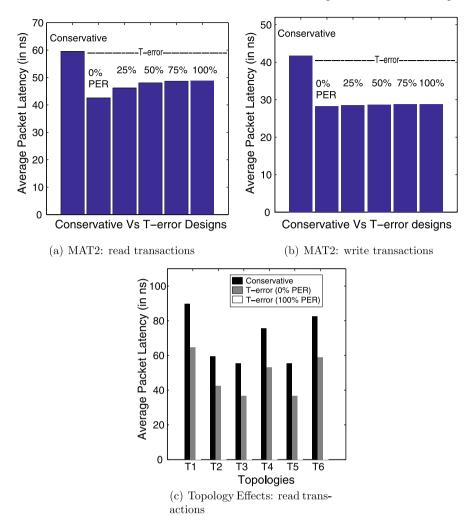

|     |      | 8.6.2   | Experiments on a Multi-Media Benchmark                   |   |     |

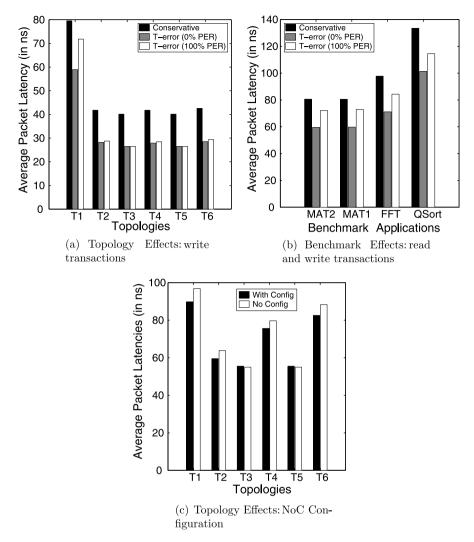

|     |      | 8.6.3   | Effect of Application-Level Power Management             |   |     |

|     |      | 8.6.4   | Experiments on Other Benchmarks                          |   |     |

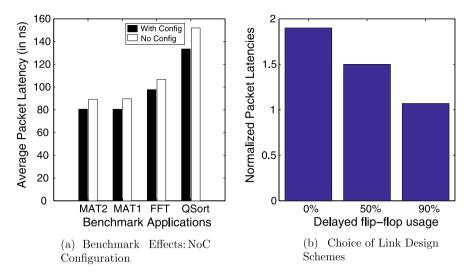

|     |      | 8.6.5   | Effect of NoC Configuration                              |   |     |

|     |      | 8.6.6   | Choice of Link Design Schemes                            |   |     |

|     |      | 8.6.7   | Synthesis Results                                        |   |     |

|     | 8.7  |         | ary                                                      |   |     |

|     |      |         |                                                          |   |     |

| 9   | Ana  |         | NoC Error Recovery Schemes                               |   |     |

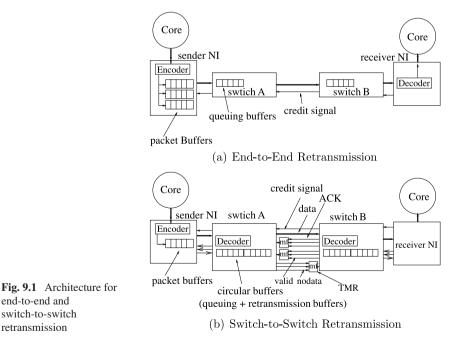

|     | 9.1  | Switch  | Architecture Design                                      |   | 142 |

|     |      | 9.1.1   | End-to-End Error Detection                               |   | 142 |

|     |      | 9.1.2   | Switch-to-Switch Error Detection                         |   | 143 |

|     |      | 9.1.3   | Hybrid Single Error Correcting, Multiple Error Detecting |   |     |

|     |      |         | Scheme                                                   |   | 143 |

|     | 9.2  | Energy  | Set Estimation and Models                                |   | 144 |

|     |      | 9.2.1   | Energy Estimation                                        |   | 144 |

|     |      | 9.2.2   | Error Models                                             |   | 144 |

|     | 9.3  | Experi  | ments and Simulation Results                             |   | 144 |

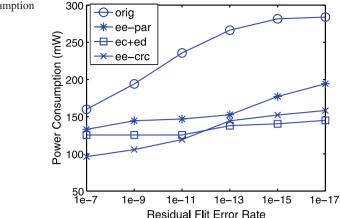

|     |      | 9.3.1   | Power Consumption of Schemes for Fixed Residual Error    |   |     |

|     |      |         | Rates                                                    |   | 144 |

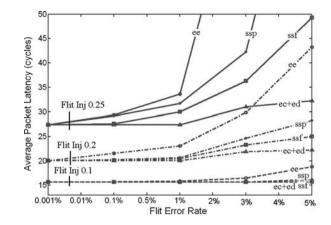

|     |      | 9.3.2   | Performance Comparison of Reliability Schemes            |   | 146 |

|     |      |         |                                                          |   |     |

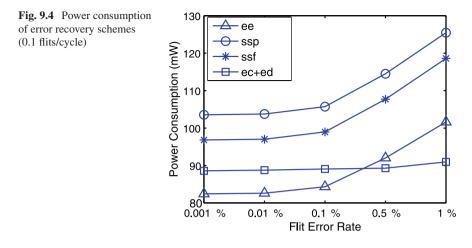

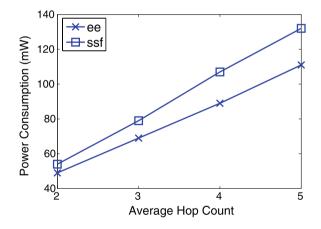

|     |        | 9.3.3   | Power Consumption Overhead of Reliability Sc     | hem   | ies |   |     | 146 |

|-----|--------|---------|--------------------------------------------------|-------|-----|---|-----|-----|

|     |        | 9.3.4   | Effect of Buffering Requirements, Traffic Patter | rns : | and | l |     |     |

|     |        |         | Packet Size                                      |       |     |   |     | 149 |

|     | 9.4    | Summ    | ary                                              |       |     | • |     | 151 |

| 10  |        |         | ant Route Generation                             |       |     |   |     |     |

|     | 10.1   | Multi-  | Path Routing with In-Order Delivery              |       |     |   |     | 155 |

|     | 10.2   | Path Se | election Algorithm                               |       |     |   |     | 156 |

|     | 10.3   | Multip  | ath Traffic Splitting                            |       |     |   |     | 160 |

|     | 10.4   | Fault-7 | Folerance Support with Multipath Routing         |       |     |   |     | 161 |

|     |        | 10.4.1  | Resilience Against Transient Errors              |       |     |   |     | 161 |

|     |        | 10.4.2  | Resilience Against Permanent Errors              |       |     |   |     | 162 |

|     | 10.5   | Simula  | tion Results                                     |       |     |   |     | 164 |

|     |        |         | Area, Power and Timing Overhead                  |       |     |   |     |     |

|     |        |         | Case Study: MPEG Decoder                         |       |     |   |     |     |

|     |        | 10.5.3  | Comparisons with Single-Path Routing             |       |     |   |     | 165 |

|     |        | 10.5.4  | Effect of Fault-Tolerance Support                |       |     |   |     | 166 |

|     | 10.6   | Summ    | ary                                              |       |     | • | • • | 167 |

| 11  |        |         | rt for Reliable On-Chip Memories                 |       |     |   |     |     |

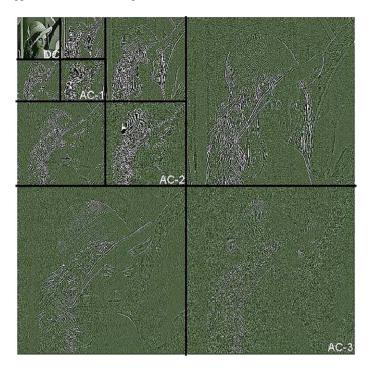

|     |        |         | sis of Multimedia Software                       |       |     |   |     |     |

|     | 11.2   | Baselii | ne SoC Architecture and Extensions               |       |     |   |     | 172 |

|     |        | 11.2.1  | SoC Template Architecture                        |       |     |   |     | 172 |

|     |        | 11.2.2  | Proposed Hardware Extensions                     |       |     |   |     | 173 |

|     | 11.3   | Run-Ti  | ime Fault Tolerant Schemes                       |       |     |   |     | 176 |

|     |        | 11.3.1  | Permanent Error Recovery Support                 |       |     |   |     | 177 |

|     |        | 11.3.2  | Intermittent Error Recovery Support              |       |     |   |     | 178 |

|     | 11.4   | Experi  | mental Results                                   |       |     |   |     | 178 |

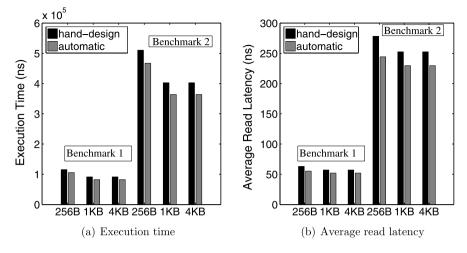

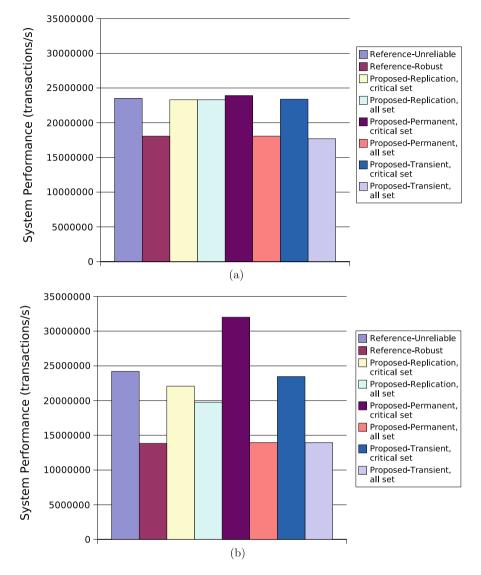

|     |        | 11.4.1  | Performance Studies                              |       |     |   |     | 179 |

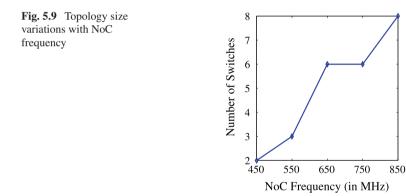

|     |        | 11.4.2  | Architectural Exploration of NoC Features        |       |     |   |     | 182 |

|     |        | 11.4.3  | Effects of Varying Percentages of Critical Data  |       |     |   |     | 183 |

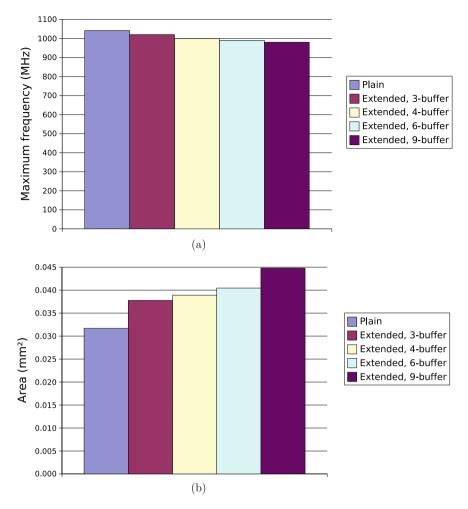

|     |        | 11.4.4  | Synthesis Results                                |       |     |   |     | 184 |

|     | 11.5   | Summ    | ary                                              |       |     | • |     | 186 |

| 12  |        |         | and Future Directions                            |       |     |   |     |     |

|     | 12.1   | Putting | g It All Together                                |       |     | • | • • | 187 |

| Bib | liogra | phy.    |                                                  |       |     |   |     | 191 |

## Chapter 1 Introduction

*Multiprocessor Systems on Chips (MPSoCs)* are high-complexity, high-value semiconductor chips comprising general-purpose processors, hardware cores, DSPs, and memory blocks [1, 5]. Today, the commercial MPSoCs have several tens of cores on a chip (e.g., the NEC's TCP/IP offload engine is powered by 10 Tensilica Xtensa processor cores [71]), and in the next few years technology will support the integration of several tens to hundreds of cores, making a large computational power available.

Full exploitation of the increased level of SoC integration requires new paradigms and significant improvements of design productivity, as current system architectures and design styles do not scale up to such dimensions and complexities. A relevant example regards the system architecture, whose paradigm is progressively shifting from computation-centric to communication-centric. In fact, MPSoC performance will be increasingly determined by the ability of the communication infrastructure to efficiently accommodate the communication needs of the integrated computation resources.

#### 1.1 Networks on Chips: Scalable Interconnects for SoCs

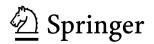

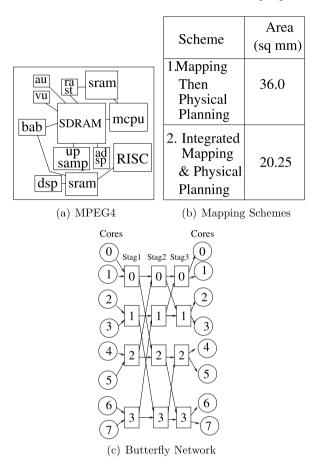

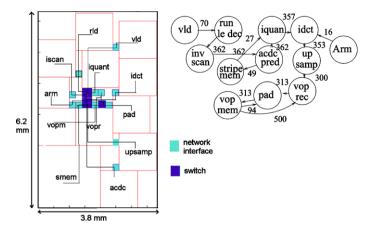

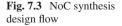

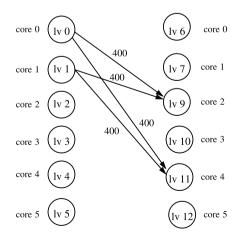

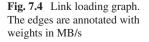

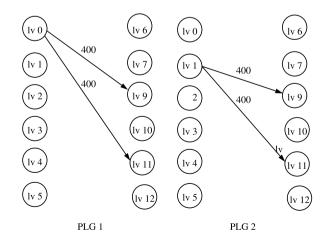

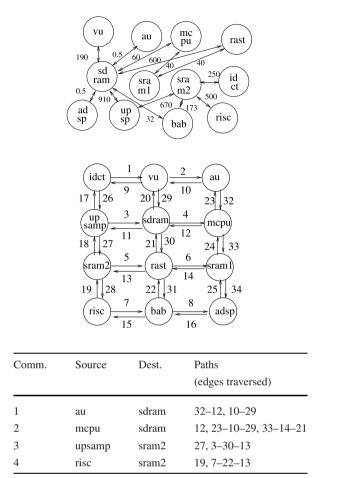

In several application domains, such as multimedia processing, the bandwidth requirement between the cores in SoCs is increasing. The aggregate communication bandwidth between the cores is in the GB/s range for many video applications. In the future, with the integration of many applications onto a single device and with increased processing speed of cores, the bandwidth demands will scale up to much larger values [7]. As an example of a media processing application, a Video Object Plane decoder [8] is shown in Figure 1.1. Each block in the figure corresponds to a core and the edges connecting the cores are labeled with bandwidth demands of the communication between them. As seen from the figure, the bandwidth demands are in the order of hundreds of MB/s.

Traditionally, bus-based architectures have been used to interconnect the various cores of the MPSoCs. To meet the increasing communication demands, the busbased architectures have evolved over time from a single shared bus to multiple bridged buses and to crossbar-based designs. Current state-of-the art bus architectures, such as the AMBA multilayer [2], enable the instantiation of multiple buses operating in parallel, thereby providing a crossbar architecture. However, such an architecture is inherently nonscalable for large number of cores in the design.

To effectively tackle the interconnect complexity of current and future MPSoCs, a micro-networks based interconnect architecture is needed to connect the cores.

Fig. 1.1 Block diagram of Video Object Plane Decoder, with communication BW (in MB/s)

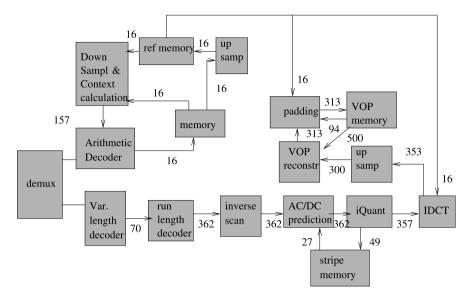

Fig. 1.2 Example NoC system with pipelined links

A communication-centric design approach, *Networks on Chips* (*NoCs*), has recently emerged as the design paradigm for designing such scalable micronetworks for MP-SoCs [20–23, 30, 31].

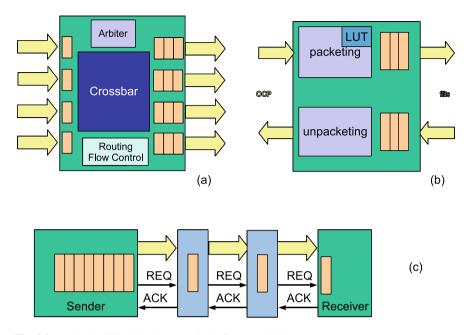

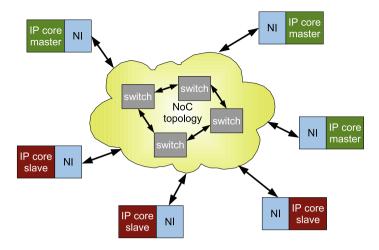

A typical NoC consists of switches, links, and Network Interfaces (NIs), as shown in Figure 1.2. A NI connects a core to the network and coordinates the transmission and reception of packets from/to the core. A packet is usually segmented into multiple *FLow control unITS (flits)*. The switches and links are used to connect

the various cores and NIs together. To tackle the delay of long NoC links, a *latency insensitive design* approach in which the links are pipelined can be utilized [70]. Link pipelining increases the link throughput and decouples the cycle time of the communication system from the link length.

The use of a NoC to replace bus-based wiring has several key advantages:

- Better scalability at the architectural and physical levels. NoCs can add bandwidth as needed and segment wires as required.

- Better performance under high loads. NoCs can operate at high frequencies, cope with large bandwidth demands, and parallelize traffic streams.

- NoCs facilitate modularity by orthogonalizing the design of the communication architecture from the computation architecture, thereby leading to reduced design efforts.

- Quicker design closure. NoC are more predictable: They intrinsically provide wire segmentation, which helps ensuring that design respins will not be needed in the last phases of the design flow, when they are more costly.

- Higher energy-efficiency. To support the same traffic load, NoCs can operate at a lower frequency than bus-based systems and the data transfer can finish faster. These can lead to a reduction in energy consumption of the system.

Another effect of the shrinking feature size is that the power supply voltage and device  $V_t$  decreases and the wires become unreliable, as they are increasingly susceptible to various noise sources such as cross-talk, coupling noise, soft errors, and process variations [130]. The use of aggressive voltage scaling techniques to reduce the power consumption of the system further increases the susceptibility of the system to various noise sources. Moreover, wires are becoming thicker and taller, but their widths are not increasing proportionally, thereby increasing the effect of coupling capacitance on the delay of wires. As an example, the delay of a wire can vary between  $\tau$  and  $(1 + 4\lambda)\tau$  (where  $\tau$  is the delay of the wire without any capacitive coupling and  $\lambda$  is the ratio of the coupling capacitance to the bulk capacitance) [136]. The wire delay for data transfer on a communication bus depends on the data patterns transferred on the bus. As presented in [121], the data-dependent variations in wire delay can be as large as 50% for the different switching patterns. With technology scaling, the device characteristics fluctuate to a large extent due to process variations and can cause significant variations in wire delay [122]. Wire delay is also affected by other forms of interference such as supply bounce, transmission line effects, etc. [123, 124]. Providing resilience from such transient delay and logic errors is critical for proper system operation.

The variability in process technology and temperature distribution (thermal hotspots) and the effect of various noise sources such as power supply fluctuations and electromagnetic radiations pose major challenges for the reliable operation of current and future MPSoCs. While some of these noise sources (such as thermal effects) cause intermittent or temporary failures in the system, some others (such as process variations) can cause permanent failures of hardware components. With the increased uncertainty of device operation, the time-to-failure period for the hardware components varies widely, with some components having a shorter lifetime than expected. Therefore, new design methodologies and architectural solutions need to be developed to ensure proper system operation. NoCs facilitate the use of error recovery schemes developed for networks to achieve a reliable system operation.

#### 1.2 NoC Design Challenges

Designing an efficient NoC architecture, while satisfying the application performance constraints is a complex process. The design issues span several abstraction levels, ranging from high-level application modeling to physical layout level implementation. Some of the most important phases in designing the NoC include: modeling the application traffic, synthesis of NoC topology for the application, mapping of cores onto the topology, finding paths and reserving resources, verifying performance of the system, developing simulation and synthesis models, and achieving reliable operation of the interconnect.

In order to handle the design complexity and meet the tight time-to-market constraints, it is important to automate most of these NoC design phases. To achieve design closure, the different phases should also be integrated in a seamless manner. The NoC design challenge lies in the capability to design hardware-optimized, customizable platforms for each application domain.

Computer-aided synthesis of NoCs is particularly important in the case of application-specific systems on chip, which usually comprise computing and storage arrays of various dimensions as well as links with various capacity requirements. Moreover, designers may use NoC synthesis as a means for constructing solutions with various characteristics that can be compared effectively only when a detailed model is available. Thus, synthesis of NoCs can be used for comparing prototypes. Needless to say, synthesis may also be very efficient for designing NoCs with regular topologies as, for example, multiprocessing systems with homogeneous cores.

NoC architectures are pushing the evolution of traditional circuit design methodologies to deal effectively with functional diversity and complexity. At the application level, the key design challenge is to expose task-level parallelism and to formally capture concurrent communication in models of computation [28]. Then high-level concurrent tasks have to be mapped to the underlying communication and computation resources. At this level, an abstract model of the hardware architecture is usually exposed to the mapping tool, so that area and power estimates can be given in the early design stage, and different objective functions (e.g., minimization of communication energy) can be considered to evaluate the feasibility of alternative mappings. In this context, a critical step in communication mapping is the NoC architecture synthesis for its significant impact on overall system performance, which is increasingly communication-dominated.

Finally, it is important to achieve a reliable NoC operation by providing resilience from permanent and transient delay and logic errors in the system. In order to protect the system from errors that occur in the communication subsystem, we can use error recovery mechanisms that are used in traditional macro-networks. As the error detection/correction capability, area-power overhead, and performance of the various error detection/correction schemes differ, the choice of the error recovery scheme for an application involves multiple power-performance-reliability trade-offs that have to be explored.

#### **1.3 Book Overview**

In this book, we present methodologies to design reliable and efficient NoCs. We present algorithmic methods to solve many of the important NoC design problems. The novel, state-of-the-art optimization methods provide near optimal solutions for many of the NoC design problems. These methods will be useful for designers to tackle specific problems in NoC design or can even be applied to solve analogous problems in other domains. Most of the time-intensive steps of NoC design are automated and integrated into a complete tool flow. The tool flow can also be used to perform design space exploration of different communication architectures. The proposed tool bridges an important design gap that exists today, in building efficient communication architectures for MPSoCs.

In the rest of this section, a detailed overview of the book is presented.

#### 1.3.1 NoC Design Methods

We first present (in Chapter 2) methods for synthesizing state-of-the-art crossbar based communication architectures. While methodologies that target the design of NoCs are required in the long run, providing design support for the state-of-the-art crossbar based bus designs pose an immediate and pressing problem. Also, as the NoC design process is more complex in nature, synthesis of crossbar-based communication architectures is an ideal starting point for illustration. Moreover, even in complex NoCs, the communication architecture will be hierarchical in nature, with local cores communicating through crossbars and the global communication taking place through a scalable network. In fact, this trend is already followed in many chip multiprocessors, such as the Stanford Smart Memories [101]. From Chapter 3 on, we present the design of NoC architectures.

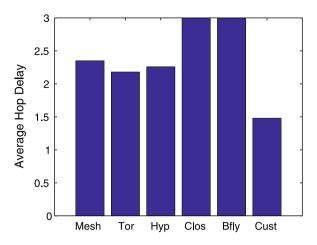

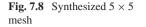

The NoC topology defines the interconnection of the different network switches with the cores and among each other. The NoC topologies can be broadly classified into two main categories: standard and application-specific custom topologies. In the standard topologies, the interconnection structure ensures full connectivity between the cores: that is, any core is reachable from any other core. Examples of such topologies include mesh, torus, hypercube, Clos, and butterfly. In an applicationspecific custom topology, the interconnection between the switches and cores are optimized to match the application traffic patterns. If an application does not require full connectivity between the cores, then the topology is optimized to provide only the required connectivity.

The use of a custom topology for an application almost always leads to a better performance and reduction in area/power overhead. However, there are some situations where a standard topology is desirable for the design:

- When the NoC is to be used across multiple product generations, a standard topology ensures that the same NoC can be reused easily across the different generations. However, when using a custom topology, the designer has restricted options when adding cores in the future, as the NoC may not provide full connectivity.

- When the cores are almost regular (similar sizes), the use of a standard topology leads to better wiring structure, as the floorplan is more predictable.

In this book, we address the design of both standard and application-specific custom topologies.

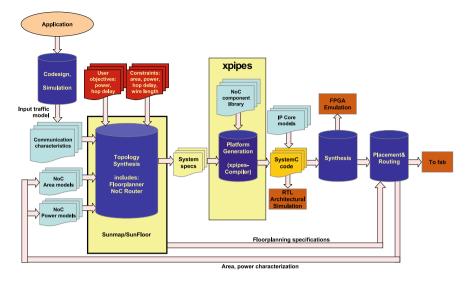

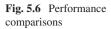

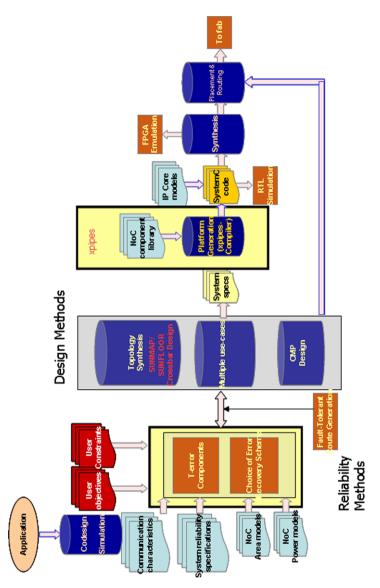

In Chapter 3, we present *Netchip*, a CAD tool flow for designing NoCs. The Netchip tool flow has three main phases and several tools integrated together:

- Front-End Design Phase: In this phase, several key NoC features such as the interconnect structure (or topology), routing scheme, paths for traffic flow, values for the NoC architectural parameters are determined. We present two tools: SUNMAP and SUNFLOOR to design application-specific standard and custom topologies, thereby automating this phase. The synthesis methods used in these tools are the subject of discussions in Chapters 4 and 5.

- Architectural Design Phase: In this phase, the RTL code of the NoC architecture is instantiated. For this, *×pipes*, a library of soft-macros for the network components and *×pipesCompiler*, a tool to generate the RTL design using the component library are developed. This is further explained in Chapter 3.

- Back-End Phase: In this phase, simulation, FPGA emulation, and layout generation of the NoC are carried out. For this, several standard industrial tool chains have been integrated with the tool flow, so that most of the back-end processes can be automatically obtained. This is also further explained in Chapter 3.

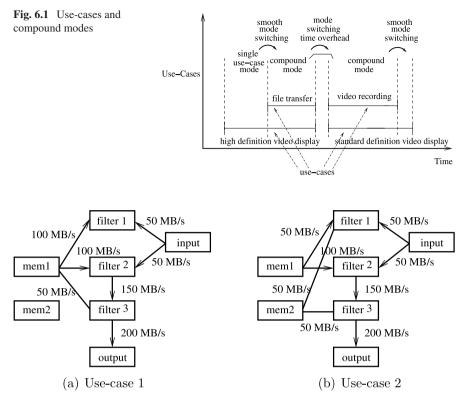

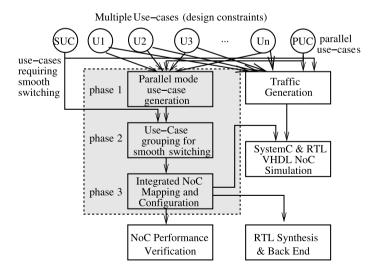

The NoC design process in Netchip is tuned to satisfy the requirements of the specific application that is to be run on the SoC. However, in today's systems, multiple applications (or use-cases) can run on the same chip. As an example, a set-top box SoC has multiple resolution video processing capabilities (like high definition, standard definition), multiple picture modes (like split-screen, picture-in-picture), video recording features, high speed Internet access, file transfer services, etc. In Chapter 6, we present the extensions to the synthesis process to handle the multiple use-case scenario. Even though, in Chapters 3–5, we present the NoC synthesis processes for the ×pipes architecture, the methods are quite general in nature and can be applied to any architecture. Toward this end, in Chapter 6, we show the process of designing the NoC for the Æthereal architecture (from NXP research).

So far, for the design process, we have assumed that the application traffic is statically known. However, what happens if there are large dynamic variations in traffic or if the traffic cannot be precharacterized at all? As an example, this would

be the case when tasks are assigned dynamically to the different cores. In Chapter 7, we present methods to design the NoC architecture for handling dynamic traffic patterns, while still yielding predictable performance.

Thus, in the first part of the book, we will be covering methods to synthesize NoCs under almost all possible design conditions.

#### **1.3.2** NoC Reliability Mechanisms

In the second part, we will be presenting the different mechanisms that can be used to obtain a reliable NoC and system operation.

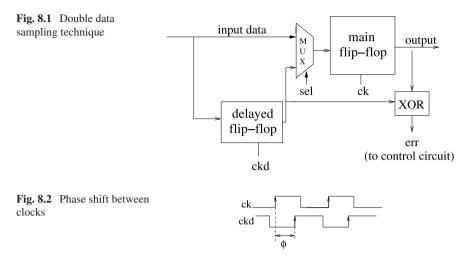

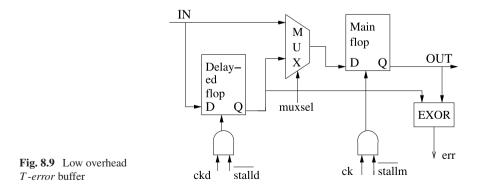

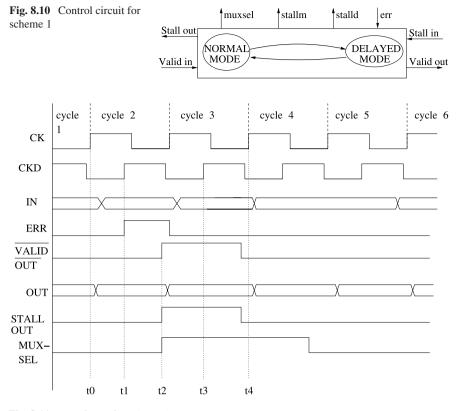

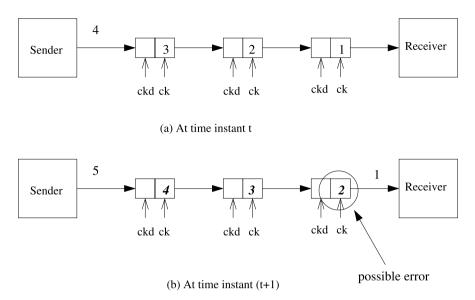

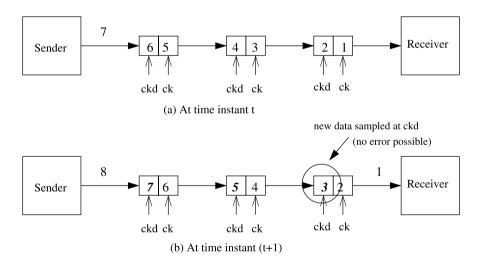

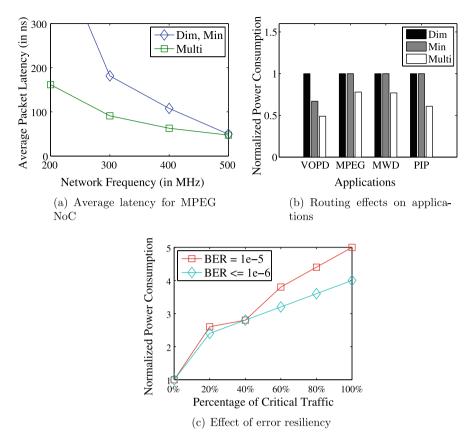

With technology scaling, the device characteristics fluctuate to a large extent due to process variations and can cause significant variations in wire delay [122]. Wire delay is also affected by other forms of interference such as supply bounce, transmission line effects, etc. [123, 124]. As such delay variations can affect multiple bits simultaneously, special mechanisms are needed to handle timing errors. In Chapter 8, we present *T-error*, a timing-error tolerant mechanism to make the interconnect resilient against timing errors arising due to such delay variations on wires.

Once the NoC components are made timing-error tolerant, we need to still handle other transient and permanent errors that can occur in the system, such as softerrors. To handle such errors, we need support at the design level, as well as at the architectural level. In Chapter 9, we present an analysis of the power efficiency of traditional error detection/correction mechanisms, to choose the best scheme for the application, so that we can achieve the required reliability level with minimum area-power overhead. In Chapter 10, we present routing mechanisms that achieve an application-specific reliability level against temporary and permanent failures.

NoCs not only allow a reliable interconnect operation, but also facilitate achieving a reliable operation of the entire system. The high flexibility of NoCs allows the designer to add redundant cores in the same chip (e.g., processing elements, backup memories) without largely increasing the design complexity. In Chapter 11, we show how the NoC can be used to support the design of a reliable on-chip memory subsystem.

Finally, in Chapter 12, we conclude the book by integrating the reliability mechanisms with the design methods and showing how a complete NoC can be designed using the tool chain.

#### 1.4 Related Work

In this section, we summarize some of the research that has been performed in the fields of NoC design and interconnect reliability.

The design issues in macro-networks (e.g., the LAN, WAN, Internet) have received unprecedented focus in the last several decades. In the last decade, the design of chip-to-chip interconnection networks for parallel processing has also received considerable focus.

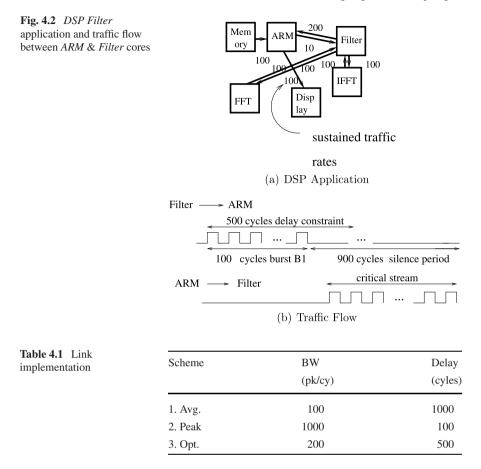

However, the challenges encountered in the design of on-chip networks for SoCs is quite different from the design of such macro-networks. Some major differences are: (1) The communication between the various cores can be statically analyzed for many SoCs and the NoC can be tailored for the particular application behavior. Whereas in the case of macro-networks, it is impossible to obtain a global knowl-edge of the traffic patterns of all the users. (2) The design objectives and constraints are different. As most SoCs are used in mobile and hand-held devices, having a network with minimum power consumption becomes an important design objective. Many SoCs also need to respond in real-time for certain inputs, for which the NoC has to support different criticality levels for the different traffic streams. (3) The design process should also consider VLSI issues, such as the structure (floorplan requirements) and wiring complexity of the resulting interconnect.

In this section, we present the state-of-the-art in the domain of NoC architectures, design methodologies, and fault-tolerant communication architectures.

#### 1.4.1 NoC Architectures and Design Methods

The most advanced state-of-the-art SoC communication architectures represent evolutionary solutions with respect to shared buses. Sonics MicroNetwork [4] is a TDMA-based bus which can easily adapt to the data-word width, burst attributes, interrupt schemes, and other critical parameters of the integrated cores, while providing very high bandwidth utilization. STBus interconnect [3] is a high performance communication infrastructure that allows to instantiate shared buses as well as more advanced topologies such as partial or full crossbars. Although evolutionary from a topology viewpoint, these solutions can rely on advanced and highly automated design methodologies for the implementation of generic communication subsystems, allowing designers to rapidly assemble, synthesize, and verify their SoCs using the MicroNetwork or the STBUS interconnect as integration platforms.

However, the early works in [20, 22] pointed out the need for more scalable architectures for on-chip communication and, therefore, to progressively replace shared buses with on-chip networks. Many NoC architectures have therefore been proposed in the open literature so far, but in most cases, the design methodologies and tools are still in the early stage.

One of the earliest contributions in this area is the Maia heterogeneous signal processing architecture, proposed by Zhang et al., based on a hierarchical mesh network [24]. Unfortunately, Maia's interconnect is fully instance-specific. Furthermore, routing is static at configuration time and communication is based on circuit switching, as opposed to packet switching. In this direction, Dally and Lacy sketch the architecture of a VLSI multi-computer using 2009 technology [9]. A chip with 64 processor-memory tiles is envisioned. Communication is based on packet switching. This seminal work draws upon past experiences in designing parallel computers and reconfigurable architectures (FPGAs and their evolutions) [65, 66].

Most proposed NoC platforms are packet switched and exhibit regular structure. An example is a mesh interconnection, which can rely on a simple layout and the switch independence on the network size.

The *Scalable Programmable Integrated Network* (*SPIN*) described in [31] is a regular, fat-tree-based network architecture. It adopts cut-through switching to minimize message latency and storage requirements in the design of network switches.

The NOSTRUM network described in [32] also takes this approach: The platform includes both a mesh topology and the relative design methodology, wherein a concrete architecture is derived from a general NoC template, then application mapping follows.

The *Linkoeping SoCBUS* [69] is a two-dimensional mesh network which uses a packet connected circuit (PCC) to set up routes through the network: a packet is switched through the network locking the circuit as it goes. This notion of virtual circuit leads to deterministic communication behavior, but restricts routing flexibility for the rest of the communication traffic.

In [10], the use of *octagon* communication topology for network processors is presented. Instead, the implementation of a *star-connected* on-chip network supporting *plesiochronous communication* among system components is described in [27].

The Æthereal NoC design framework presented in [30] aims at providing a complete infrastructure for developing heterogeneous NoC with end-to-end quality of service guarantees. The network supports *guaranteed throughput* (*GT*) for real time applications and *best effort* (*BE*) traffic for timing unconstrained applications. Support for heterogeneous architectures requires highly configurable network building blocks, customizable at instantiation time for a specific application domain. For instance, the *Proteo NoC* [26] consists of a small library of predefined, parameterized components that allow the implementation of a large range of different topologies, protocols, and configurations. ×pipes interconnect [61] and its synthesizer ×pipesCompiler [62] push this approach to the limit, by instantiating an application specific NoC from a library of composable soft macros (network interface, link, and switch).

Today, several NoC architectures have been developed [42, 74–76] with each architecture having a different structure, switch/NI design, routing scheme, QoS support, and clocking methodology. In [73], the state-of-the-art in the NoC field is presented in detail.

The synthesis and instantiation of single bus and multiple bridged buses has been explored in many research works such as [35–38, 47, 77]. In [39], the authors present an approach for mapping the system's communication requirements and optimizing the protocols for a given communication architecture template. In [40], the use of communication architecture tuners to adapt to runtime variability needs of a system is presented. A floorplan aware method for designing point-to-point links and buses are presented in [77] and [53]. In [56], the authors present an exact approach to crossbar synthesis, where they integrate the NoC architecture parameter setting with the synthesis process.

Methods to collect and analyze traffic information that can be fed as input to the bus and NoC design processes have been presented in [39]. Mappings of cores onto

standard NoC topologies have been explored in [43, 44]. In [6], a unified approach to mapping, routing, and resource reservation has been presented.

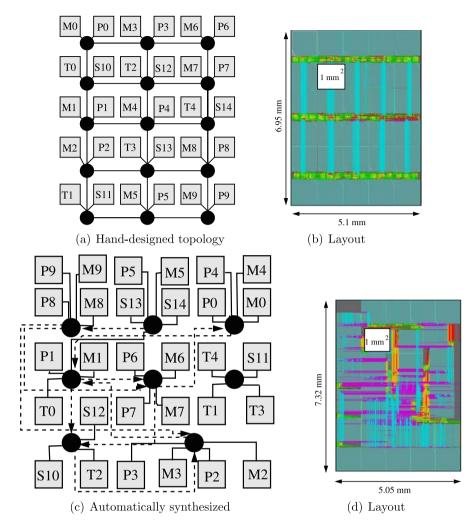

Important research in macro-networks has considered the topology generation problem [41]. As the traffic patterns on these networks are difficult to predict, most approaches are tree-based (like spanning or Steiner trees) and only ensure connectivity with node degree constraints [41]. Hence, these techniques cannot be directly extended to address the NoC synthesis problem. Application-specific custom topology design has been explored in [25, 48–51]. In [49], a physical planner is used during topology design to reduce power consumption on wires. A method to obtain application-specific NoC topologies with floorplan estimation is presented in [78]. In [67], memory optimization in single chip network fabrics is explored. In [96], a tool flow to design NoCs with QoS guarantees is presented.

In [12], a low latency router architecture for supporting dynamic routing is presented. In [13], a routing scheme that switches between deterministic and adaptive modes, depending on the application requirements is presented. Several works in the multiprocessor field have focused on the design of efficient routing strategies [94]. In the Avici router [16], packets that need to be in-order at the receiver are grouped together into a *flow*. Packets of a single flow follow a single path, while different flows can use different paths. In the IBM SP2 network [17], source-based oblivious routing is used for a multi-stage interconnection network. In [14], the authors present a source-based dynamic routing algorithm for multi-stage networks. Building area and power models for on-chip networks has been addressed in [68, 79–81].

In this book, we present a streamlined design methodology for NoC topology synthesis that is completely integrated with the state-of-the-art commercial tools for back-end physical design. We present a floorplan aware topology design method for NoCs that leads to detecting timing violations on the NoC links early in the design cycle, with the resulting designs fully verified for timing correctness using standard place&route tools. Our custom NoC topology synthesis process guarantees a complete deadlock-free network operation without requiring special hardware mechanisms, which is critical for using NoCs in real designs. The topology synthesis process is integrated with NoC architectural parameter setting and uses accurate switch area, power models, and link power models that are obtained from layouts of the components. We address the design of both regular and custom NoC topologies and present methods to design NoCs under different application scenarios. Moreover, we also address the design of NoCs, when the application traffic characteristics cannot be predicted in advance. The presented design processes are both performance and power consumption aware, which are two of the important design objectives in SoC design.

#### 1.4.2 Reliability Support for NoCs

The quest for reliable and energy efficient NoC architectures has been the focus of multiple researchers. Error protection can be applied at several levels within a NoC design. For example, fault-tolerant routing algorithms have been proposed in [138, 140]. The use of nonintersecting paths for achieving fault-tolerant routing has been utilized in many designs, such as the IBM Vulcan [94]. The use of temporal and spatial redundancy in NoCs to achieve resilience from transient failures is presented in [15]. In this work, we present a fault-tolerant routing scheme and an associated design method for NoCs, which has low area-power overhead when compared to the existing schemes and is practical to be used in the on-chip domain.

A methodology for trading off power and reliability using error control codes for Systems on Chip (*SoC*) signaling is presented in [126, 147]. In [127], the energy behavior of different error detection and correction schemes for on-chip data buses is explored. In [129], a fault model notation is presented and the use of multiple encoding schemes for different parts of a packet is explored. In [128], the use of single error correction and parity based error detection schemes for NoCs is explored. Even though some of these works consider the use of error recovery schemes for NoCs, there is no framework available today for systematic analysis of the different error recovery schemes. To tackle this issue, we present a systematic power-reliability analysis methodology for the different error detection/correction schemes for NoCs. The presented method will be useful to NoC designers for choosing the appropriate error-recovery scheme for their applications.

In [139], the supply voltage is varied dynamically based on the error rate on the links. In [132], the data bus is monitored to detect adverse switching patterns (that increase the wire delay) and the clock frequency is changed dynamically to avoid timing errors on the bus. Many bus encoding techniques such as [134] have been proposed that decrease cross-talk between wires and avoid adversarial switching patterns on the data bus. There have been several approaches in the design space to detect and correct timing errors. The use of *double data sampling techniques* has been shown in self-checking testing circuits [116, 117] and for clock recovery in digital systems [120]. Recently, these techniques have been used for online timing and soft-error recovery in systems. The *TEAtime* [115] architecture tracks logic delay variations and dynamically adjusts the clock frequency to accommodate the changes in logic delay.

In *Razor* [113, 114], an aggressive, better than worst-case design approach is presented for processor pipelines. In this work, *double sampling* of data is used to control supply voltage (and hence power consumption) by monitoring the error rate. Favalli et al. [117] assume an encoded data signal which is checked by a small decoder present at the input of each flip-flop. In case of an error, the clock is delayed for one cycle, until the correct value of data settles. *Mousetrap* [118] is a high speed asynchronous pipeline which ensures correct data availability to consecutive stages. The *Iroc* [119] design uses a latch with delayed clock to detect transient faults due to soft errors. In [72], a method to reuse the scan flip-flops to achieve soft-error tolerance is presented. The method significantly reduces the soft-error rate of the system, with minimal overhead.

In this book, we present the application of the double sampling data technique to NoCs. By efficiently integrating the technique with the flow control of the NoCs, we show that large power/area savings can be achieved, when compared to the

general double sampling techniques. We also present ways to dynamically activate/deactivate the technique to adapt to the application error rates. We present novel methods for achieving error protection at both design level and architectural level. We also show how NoCs can be used to provide error resiliency for the entire SoC. Finally, we integrate the different error recovery methods presented in this thesis with the NoC design flow, thereby automating the design of fault-tolerant NoC architectures.

# Part I NoC Design Methods

## Chapter 2 Designing Crossbar Based Systems

Over the last decade, the communication architecture of SoCs has evolved from single shared bus systems to multi-bus systems. Today, state-of-the-art bus based systems, such as the AMBA AXI [2] or the STBUS platform [3] supports the instantiation of crossbar matrices, where multiple buses operate in parallel, providing a high bandwidth communication infrastructure. While methodologies that target the design of NoCs are required in the long run, providing design support for the state-of-the-art crossbar based bus designs pose an immediate and pressing problem.

A crossbar matrix can be viewed as an evolutionary NoC architecture, where a single switch is used for the communication traffic flows. As the design process for building a general NoC is more complex in nature, synthesis of crossbar-based communication architectures is an ideal starting point for illustration of the design methods.

Despite some similarities, there is one important difference between the design of a crossbar matrix and a general NoC architecture. As the crossbar matrix design is simpler, exact algorithms can be utilized to build the system, thereby leading to fully optimum solutions. Even in cases where completely optimum solutions cannot be obtained, a large portion of the design space can be explored. Thus, we can design the crossbar system to handle more efficiently the local variations in traffic rates and burstiness in traffic flows, when compared to a general NoC system.

Even in complex NoCs, the communication architecture will be hierarchical in nature, with local cores communicating through crossbars and the global communication taking place through a scalable network. Thus, it is important to have efficient methods to design such crossbar systems.

In this chapter, we present the design of state-of-the-art crossbar based bus systems. We present methods to automatically design the *most power efficient crossbar* configuration for a MPSoC, satisfying the performance characteristics of the applications [52]. The communication architecture for the design should closely match the application traffic characteristics and performance requirements.

As an example, let us consider an image-processing MPSoC (detailed explanation of the MPSoC and experimental set-up is presented later in Section 2.5) with three different communication architectures used to connect the cores: a shared bus (all the cores are connected to a single bus), a full crossbar (each core is connected to a separate bus), and a partial crossbar (some of the cores share a bus). In Table 2.1, the average and maximum latencies incurred for a transaction (transfer of a single data word), obtained from SystemC simulation of the design using the different communication architectures are presented. The sizes of the crossbars (in terms of number of components used) normalized with respect to the size of the shared bus are also presented in the table. As seen from the table, as expected, both the average

| Table 2.1Crossbarperformance and cost for anexample image-processingMPSoC | Туре             | Average<br>latency<br>(cycles) | Maximum<br>latency<br>(cycles) | Size<br>ratio |

|---------------------------------------------------------------------------|------------------|--------------------------------|--------------------------------|---------------|

|                                                                           | Shared bus       | 35                             | 51                             | 1             |

|                                                                           | Full crossbar    | 6                              | 9                              | 11            |

|                                                                           | Partial crossbar | 10                             | 20                             | 4             |

and the maximum transaction latencies are much higher for a single shared bus than the partial or full crossbars. However, it is interesting to note that an optimal partial crossbar gives almost the same performance as a full crossbar, even though it uses fewer resources than a full crossbar.

The proposed design methodology is based on actual functional traffic analysis of the application, and the generated crossbar configuration is validated by cycleaccurate SystemC simulation of the application using that crossbar. Most previous works on bus generation and NoC topology generation (which are somewhat similar to crossbar generation) are either based on average communication traffic flow between the various cores or based on statistical traffic generating functions [43–51]. While the former approaches fail to capture local variations in traffic patterns (as the average bandwidth of communication is a single metric that is calculated based on the entire simulation time), the latter approaches are only based on approximations to the functional traffic.

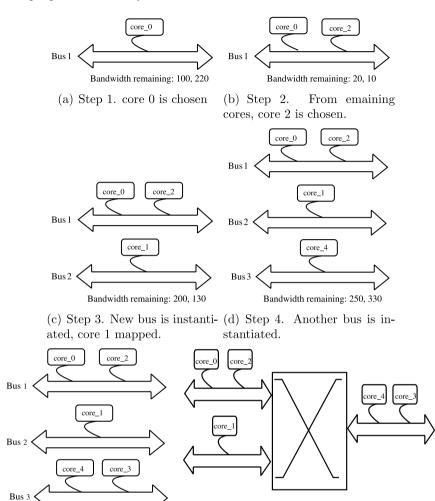

The proposed design methodology differs from existing approaches [43–50] in the fact that it is based on the analysis of simulated traffic patterns in windows. The entire simulation period is divided into a number of fixed-sized windows. The crossbar is designed such that, within each window, the application communication requirements (such as the bandwidth requirements) are met. Moreover, the overlap among traffic streams mapped onto the same resource is minimized, thereby reducing the latency for data transfer. The criticality and real-time requirements of streams are also considered and the overlapping critical streams are mapped onto different crossbar resources.

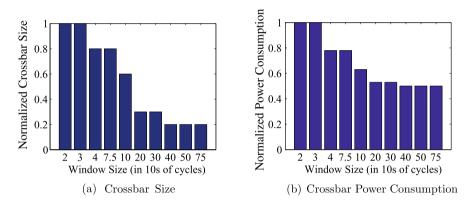

The methodology spans an entire design space spectrum with the analysis based on average communication traffic (as done in many previous works [43-50]) and on-peak bandwidth (as done in [51]) being the two extreme design points. Thus, the methodology also applies to cases where application traces are not available and only rough estimates of the traffic flows between the various cores are known. The design point in the spectrum is varied by controlling the window size used for the traffic analysis and design.

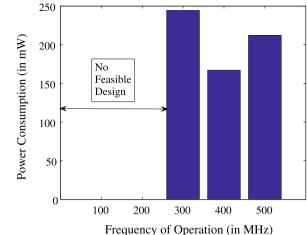

We also integrate the setting up of several communication architecture parameters (such as the frequency of operation) with the crossbar synthesis phase. The wiring complexity of the interconnect should also be considered during the communication architecture synthesis procedure. For this, the floorplan of the design is performed, where the accurate physical locations of the cores and the crossbar matrix are determined. From the resulting floorplan, the wire-lengths in the design are obtained. Based on the length of the wires and the operating frequency of the crossbar (which is automatically tuned by the synthesis procedure), any timing violations on the wires are obtained early in the design cycle. Thus, the crossbar architecture generated by the procedure is also validated for timing correctness, which is a key step to bridge the gap between the higher level architectural models and the actual physical design models of the crossbar architecture. From the wire-length estimates, accurate estimates of the power consumption of the interconnect wires are also obtained. The crossbar matrix power consumption values are based on the synthesis of the RTL models of the design, obtained using industry standard tools. From the wire and crossbar matrix power consumption, the total communication architecture power consumption is obtained, which is used to guide the synthesis procedure to obtain the most power efficient crossbar architecture.

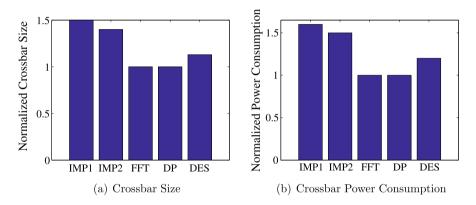

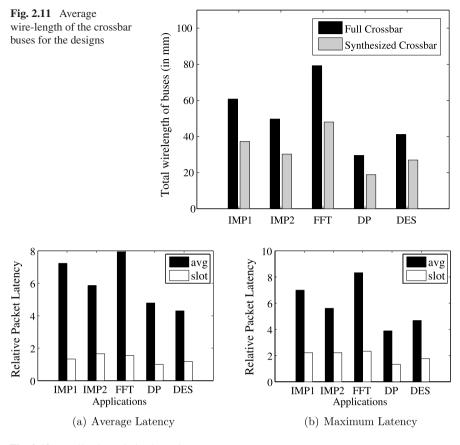

We present experiments on several different MPSoC designs that show large reduction in power consumption of the communication architecture (45.3% on average) and total wire-length of the crossbar buses (38.0% on average) when compared to the traditional full crossbar based design approaches. Compared to the existing design methods, the proposed methodology results in crossbar platforms that lead to large reduction in transaction latencies (up to  $7\times$ ). The experiments also show that the proposed approach is highly scalable to a large number of cores and to a large number of simulation windows in the design.

#### 2.1 Problem Motivation and Application Traffic Analysis

#### 2.1.1 Problem Motivation

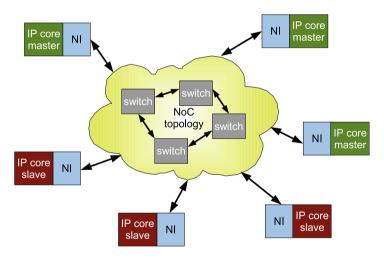

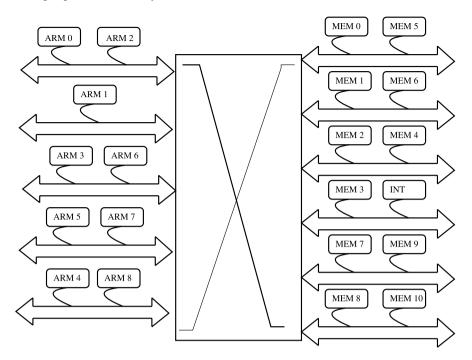

There are three possible ways in which a crossbar can be instantiated: as a shared bus, a partial crossbar, or a full crossbar. The partial and full crossbars are actually composed of many buses to which the processor/memory cores are connected. Examples of partial and full crossbars are presented in Figure 2.1. In the partial crossbar architecture, some of the cores (such as the Master 0 and Master 1) share the same bus, while in the full crossbar, each core is connected to a separate bus. The objective of the crossbar synthesis procedure is to obtain an efficient clustering

Fig. 2.1 STbus crossbars

Fig. 2.2 Power consumption of switch matrix and wires

of the master and slave cores onto the crossbar buses, such that a communication architecture with low power consumption is obtained.

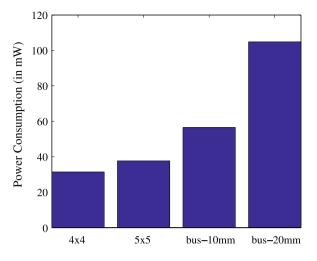

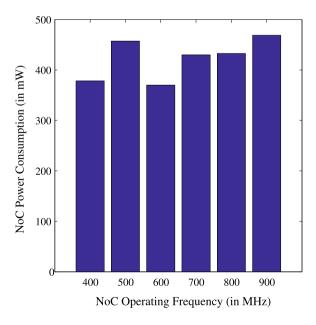

When choosing the most power efficient crossbar configuration, it is also important to account for the wiring complexity of the different configurations. As an example, the power consumption of the crossbar components (switch matrix and arbiters) for two different configurations and the power consumption of the wires for two different total wire-lengths (assuming a design with 30 cores and data width of 32-bits for the crossbar buses) are presented in Figure 2.2. For most MPSoC designs, the total length of the wires of the crossbar buses is of the order of few tens of millimeters. For the power consumption values presented in the figure, a 130 nm process technology is used, with an operating frequency of 500 MHz and an operating voltage of 1.2 V. The methods and assumptions used for estimating the power consumption of the crossbar matrices and wires are presented in detail in the experimental section. From the figure, we can infer that the wire power consumption is a significant fraction of the total communication architecture power consumption for crossbar based systems. Thus, it is important to consider the length of wires during the synthesis process, as the design point can be far from the optimum design point if such information is not accounted for. In order to have accurate wire-length estimates, we need to have accurate floorplan information of the design.

Another point worth noting is that in many crossbar architectures, the underlying protocol may not support pipelining of the buses (as an example, the Type 1 protocol of STbus [3]). In this case, the frequency of operation of the communication architecture is limited by the length of the longest bus in the design. For a chosen frequency point, it is then important to evaluate whether the length of the wires are lower than the threshold limit, so that they can be traversed in one clock cycle. We would also require the accurate floorplan and wire-length estimates to apply such feasibility checks.

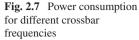

#### 2.1.2 Application Traffic Analysis

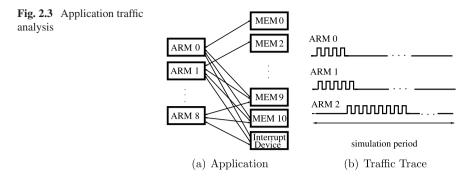

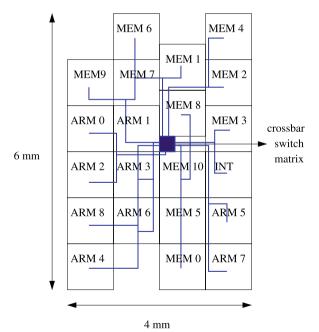

In this subsection, we explore the traffic characteristics of applications to model the performance constraints to be satisfied by the crossbar designed for the system. As an example, consider the 21-core image processing application, shown in Figure 2.3(a). In this example, there are 9 ARM cores, 11 on-chip memories, with some of the memories used for interprocessor communication and an interrupt device. The ARM cores act as masters and the memory cores act as slaves. The ARM cores run a set of image processing benchmarks that involve accesses to different memories. A cycle-accurate simulation of the system with a full crossbar design was performed, using the STbus crossbar architecture. A small trace of the traffic to three of the cores is shown in Figure 2.3(b).

Even though the aggregate traffic (measured over the entire simulation period) to the three cores is lower than that can be supported by a single bus, using a single bus to connect all three cores will lead to high average and peak latency due to overlap in traffic patterns during some regions of the simulation. Another related point is that if overlaps are not considered, connecting ARM 0 and ARM 1 on to the same bus is better than connecting ARM 0 and ARM 2 onto the same bus, as the former results in lower bandwidth needs. However, the latter solution will result in better performance (reduced transaction latency) while still satisfying the bandwidth needs. Note that using peak bandwidth instead of the average bandwidth will solve this problem, but lead to an over-design of the crossbar (in terms of number of buses needed or their frequency of operation). The design methodology needs to consider overlap among the various traffic streams into account and should consider local variations in traffic rates. Also, some of the traffic streams can be critical and to facilitate providing real-time guarantees; real-time traffic streams that overlap in time should not be mapped onto the same crossbar bus.

#### 2.2 Design Methodology

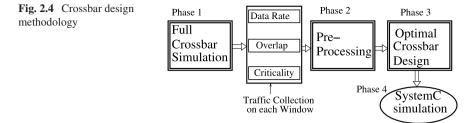

The design flow for the crossbar design is shown in Figure 2.4, which consists of four distinct phases. In the first phase, the application is initially designed using a

full crossbar communication architecture and a SystemC simulation of the design is carried out. As the full crossbar architecture is nonblocking in nature (no contention between the cores if they are accessing different cores), it helps in modeling the application traffic requirements under ideal operating conditions. For the simulations, we use the *MPARM* simulation environment [57] that allows interconnection of ARM cores to several interconnection platforms (such as AMBA, STbus, ...) and to perform cycle accurate simulations for a variety of benchmark applications.

To effectively capture local variations in traffic patterns and to perform overlap calculations, we define a window-based traffic analysis. The entire simulation period is divided into a number of windows and the traffic characteristics to the various cores in each window are obtained. The traffic characteristics recorded include: the amount of data sent and received by each core in every window, amount of pair-wise overlap between the traffic streams between the different cores in every window, the real-time requirements of traffic streams, etc. Without loss of generality, in the rest of this chapter, we assume that all the windows are of equal size, although the methodology also applies to windows with varying sizes. The size of the window is parameterizable and depends on the application characteristics and performance requirements.

After the data collection phase, a preprocessing phase is carried out in which the cores that have traffic flows with large overlaps in any window and need to be put on different buses are identified. In this phase, the overlapping critical streams that need to be on separate buses are also identified.

In the next phase, the optimal crossbar configuration for the application, satisfying the performance constraints is synthesized. To generate the optimal crossbar configuration, we use the traffic information collected in each window and check whether the bandwidth, overlap, and criticality constraints are satisfied in each window. In the final phase, the designed crossbar matrix is instantiated in the MPARM environment and SystemC simulations are carried out.

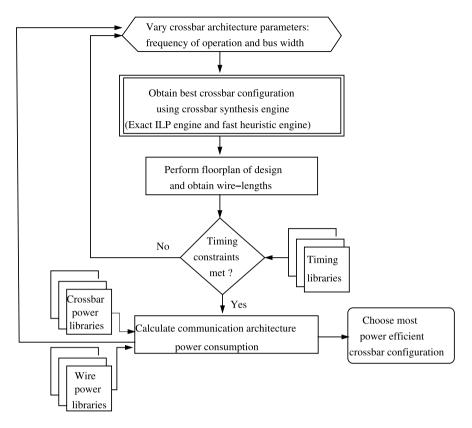

The details of the crossbar synthesis phase are presented in Figure 2.5. In the outer loop of the synthesis process, the communication architectural parameters (such as the frequency of operation and bus width) are varied in several user defined steps. The interesting range for the parameters are obtained from the user. For each architectural parameter point, the most power efficient crossbar configuration is synthesized. For synthesis, we present two approaches: one approach is based on solving the problem exactly using *Integer Linear Program (ILP)* formulation, which is applicable for small problem instances, and the other is a more scalable approach based on fast and efficient heuristics. In the next step of the synthesis phase,

Fig. 2.5 The crossbar synthesis phase

floorplan of the synthesized design is performed. Floorplanning is the process of determining the exact 2D positions of the different cores and the switch matrix in the design. For obtaining the floorplan, we use Parquet [92], a fast and accurate floorplanner that minimizes the design area as well as the average wire-length. As the cores in the MPSoC are usually predesigned hardware blocks, we realistically assume that the size of the cores (either the width and height or the aspect ratio and area) are provided as an input to the synthesis process.

From the floorplan of the design, the length of the wires (based on the Manhattan distance), and hence the power consumption on the wires are obtained. In the next step, for the chosen frequency point, the wire-lengths are checked to see whether the maximum wire-length exceeds the length that the data can traverse in a single clock cycle. In the next step, from the switch matrix power consumption and the wire power consumption, the power consumption of the synthesized communication architecture is obtained. From the set of generated crossbar architectures for each architectural design point, the most power efficient architecture that satisfies the performance and timing constraints is chosen.

#### 2.3 Exact Approach to Crossbar Synthesis

In this section, we formulate the mathematical models of the crossbar design problem and present the exact ILP formulation to synthesize the most efficient architecture for a chosen architectural parameter design point.

#### 2.3.1 Problem Formulation

**Definition 1** The set of all cores in the design is represented by the set T. The set of all windows used for traffic analysis is represented by the set W, with the bandwidth available (product of frequency of operation and bus width) in each window represented by WS. The set of buses used in the crossbar is represented by the set B.

**Definition 2** The bandwidth requirement of each core  $t_i$ ,  $\forall i \in 1, ..., |T|$ , in every window m,  $\forall m \in 1, ..., |W|$ , is represented by  $comm_{i,m}$ .<sup>1</sup> The amount of data overlap between every pair of cores  $(t_i, t_j)$  in each window m is represented by  $wo_{i,j,m}$ .

The overlap between every pair of cores  $t_i$  and  $t_j$ , over the entire simulation period is obtained by summing the overlap between them in all the windows and represented by the entries of the overlap matrix *OM*:

$$om_{i,j} = \sum_{m} wo_{i,j,m} \quad \forall i,j$$

(2.1)

In the preprocessing phase of the design flow (refer to Figure 2.4), those pair of cores that have overlap exceeding the threshold value (which is parameterizable) in any window are identified. By mapping the traffic flows of such cores onto separate buses, the maximum and average latency of data transmission can be reduced, and in some cases can also speed up the process of finding the optimal crossbar configuration. Also, in this preprocessing step, the real-time traffic streams that overlap with each other in any window are identified. Such cores with overlapping real-time streams should not be placed on the same bus, as real-time communication guarantee to the streams cannot be given in this case. Also, as noted earlier, most crossbar architectures do not allow masters and shared slaves of the design to be mapped onto the same bus. The set of all cores that cannot be on the same bus by the conflict matrix is defined by:

$$c_{i,j} = \begin{cases} 1, & \text{if } t_i \& t_j \text{ should be on different buses} \\ 0, & \text{otherwise} \end{cases} \quad \forall i, j \qquad (2.2)$$

The performance constraints that need to be satisfied by the crossbar configuration in each window are modeled as constraints of an ILP.

<sup>&</sup>lt;sup>1</sup>In the rest of this chapter, we follow the convention that variables *i* and *j* are defined for  $1, \ldots, |T|$ , variable *k* is defined for  $1, \ldots, |B|$ , and *m* for  $1, \ldots, |W|$ .

**Definition 3** The set *X* represents the set of binding variables  $x_{i,k}$ , such that  $x_{i,k}$  is one when core  $t_i$  is connected to the bus  $b_k$  and zero otherwise.

In the crossbar design, each core has to be connected to a single bus (while a single bus can connect multiple cores). This is implemented by the following constraint:

$$\sum_{k} x_{i,k} = 1 \quad \forall i \tag{2.3}$$

In every window used for traffic analysis, the individual buses of the crossbar have to support the traffic through them in that window. By evaluating the bandwidth constraints over a smaller sample space of a window (which is typically a few hundred or thousand cycles), instead of the entire simulation sample space (which can be millions of cycles), we are better able to track the local variations in the traffic characteristics.

This window-based bandwidth constraint is represented by the equation:

$$\sum_{i} comm_{i,m} \times x_{i,k} \le WS \quad \forall k,m$$

(2.4)

**Definition 4** The set *SB* represents the set of sharing variables  $sb_{i,j,k}$ , such that  $sb_{i,j,k}$  is one when cores  $t_i$  and  $t_j$  share the same bus  $b_k$  and zero otherwise. The set *S* represents the set of sharing variables  $s_{i,j}$ , such that  $s_{i,j}$  is one when cores  $t_i$  and  $t_j$  share any of the buses of the crossbar and zero otherwise.

The  $sb_{i,j,k}$  can be computed as a product of  $x_{i,k}$  and  $x_{j,k}$ . However, this results in nonlinear (quadratic) equality constraints. To break the quadratic equalities into linear inequalities, the following set of inequalities are used:

$$sb_{i,j,k} \in \{0, 1\}$$

$$x_{i,k} + x_{j,k} - 1 \le sb_{i,j,k}$$

$$0.5x_{i,k} + 0.5x_{j,k} \ge sb_{i,j,k} \quad \forall i, j, k$$

(2.5)

and the  $s_{i, j}$  are computed using the equation:

$$s_{i,j} = \sum_{k} sb_{i,j,k} \quad \forall i, j$$

(2.6)

The condition that certain cores are forbidden to be on the same bus, obtained from equation (2.2), is represented by:

$$c_{i,j} \times s_{i,j} = 0 \quad \forall i,j \tag{2.7}$$

The fact that all the integer variables introduced above take values of either 0 or 1 only, is represented by:

$$x_{i,k}, s_{i,j}, c_{i,j} \in \{0, 1\} \quad \forall i, j, k$$

(2.8)

#### 2.3.2 Exact Crossbar Synthesis Algorithm

The exact algorithm for the crossbar design has two major steps: the first is to find the best crossbar configuration that satisfies the performance constraints (that were presented in the above subsection) and the second step is to find the optimal binding of the cores to the chosen crossbar configuration.

In order to find the best crossbar configuration, we vary the number of buses in the design, from the maximum number (equal to the number of cores in the design, modeling a full crossbar) to one (modeling a single shared bus), in a binary search manner. For each configuration of bus count, we check whether a feasible solution that satisfies the constraints of the ILP (formed by the set of inequalities from equations (2.3) to (2.8)) exists. Once the minimum number of buses have been identified from applying the ILP, possibly multiple times, the buses used by the masters and slaves of the design are separated, thereby generating the optimal crossbar configuration.

Once the best crossbar configuration is obtained in the next step, the optimal binding of the cores onto buses of the crossbar is obtained. A binding of cores to the buses that minimizes the amount of overlap of traffic on each bus will result in lower average and peak latency for data transfer.

For this, the above ILP is solved with the objective of reducing the maximum overlap on each of the bus (the maximum overlap over all the buses is represented by the variable *maxov*), and satisfying the performance constraints as follows:

min maxov

s.t.

$$\sum_{i} \sum_{j} om_{i,j} \times sb_{i,j,k} \le maxov \quad \forall k$$

and subject to equations (2.3) to (2.8) (2.9)

By splitting the problem into two ILPs, the execution time of the algorithm is reduced, as solving ILP 1 for feasibility check is usually faster than solving the ILP 2 with objective function and additional constraints. The ILPs are solved using the CPLEX package [59].

#### 2.4 Heuristic Approach to Crossbar Synthesis

As the exact ILP approach is not scalable to large problem instances, either when the number of cores in the design is large or when the number of simulation windows used for analysis is large, in this section we present fast and efficient heuristic approach for crossbar synthesis.

The problem of assigning cores to the minimum number of buses, subject to the performance constraints is a special instance of the general problem of *constrained bin-packing* [60]. There are several efficient heuristics that have been developed for

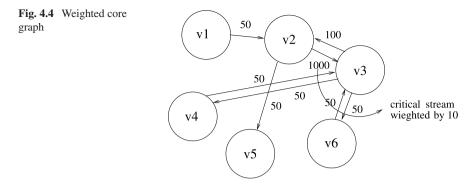

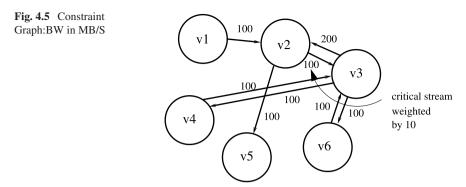

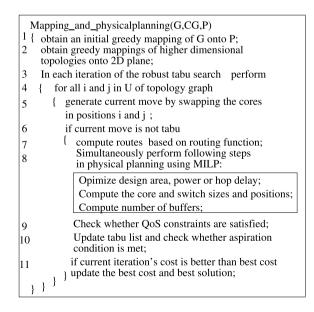

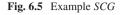

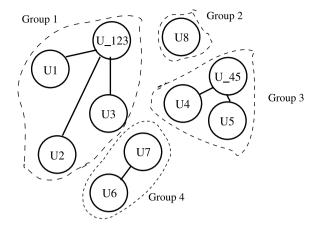

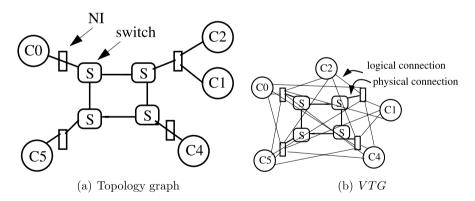

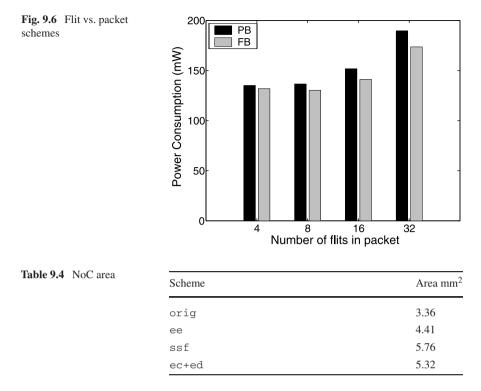

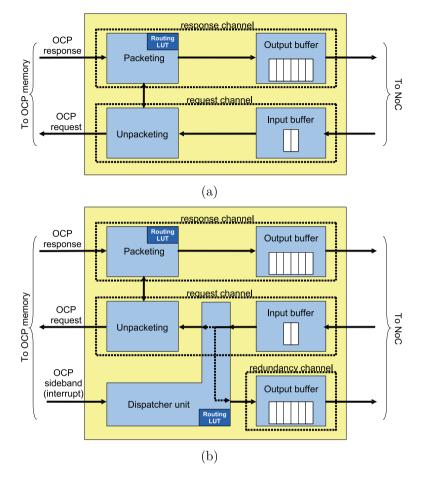

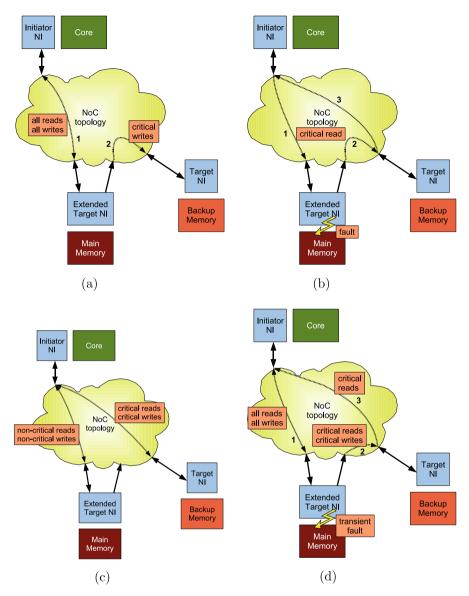

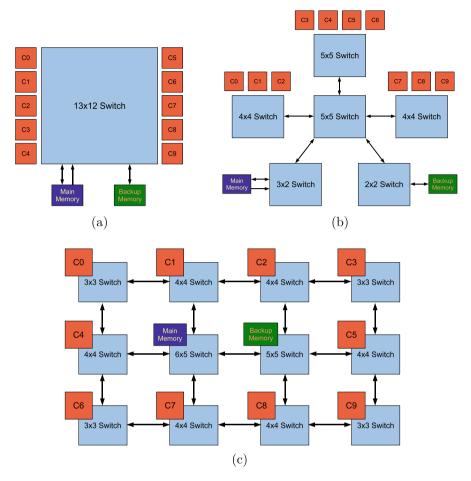

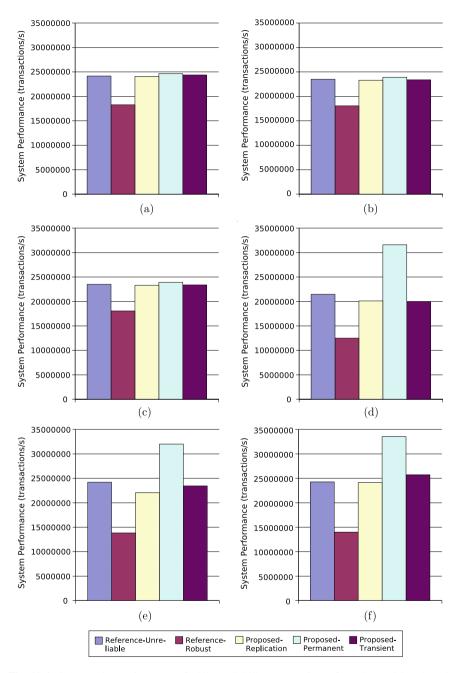

the bin-packing problem [60]. In this work, we use an approach that is based on the *first-fit* heuristic to bin-packing. We chose this heuristic for several reasons. When the performance constraints are removed, the heuristic procedure is theoretically guaranteed to provide solutions that are within two times the optimum solution that would be obtained by an exact algorithm [60]. Practically, we found that the solutions obtained by the heuristic are close to the optimum solution possible for experiments on several SoC benchmarks. Moreover, the heuristics are relatively simple to implement and have a very low run-time complexity, making the approach scalable to large designs and allowing the use of large number of simulation windows for analysis.