Günter Grossmann Christian Zardini *Editors*

# The ELFNET Book on Failure Mechanisms, Testing Methods, and Quality Issues of Lead-Free Solder Interconnects

The ELFNET Book on Failure Mechanisms, Testing Methods, and Quality Issues of Lead-Free Solder Interconnects Günter Grossmann · Christian Zardini Editors

## The ELFNET Book on Failure Mechanisms, Testing Methods, and Quality Issues of Lead-Free Solder Interconnects

*Editors* Günter Grossmann EMPA Überlandstrasse 129 Dübendorf CH-8600 Switzerland e-mail: guenter.grossmann@empa.ch

Prof. Christian Zardini ENSEIRB Talence Cedex France

ISBN 978-0-85729-235-3

e-ISBN 978-0-85729-236-0

DOI 10.1007/978-0-85729-236-0

Springer London Dordrecht Heidelberg New York

British Library Cataloguing in Publication Data A Catalogue record for this book is available from the British Library

© Springer-Verlag London Limited 2011

Apart from any fair dealing for the purposes of research or private study, or criticism or review, as permitted under the Copyright, Designs and Patents Act 1988, this publication may only be reproduced, stored or transmitted, in any form or by any means, with the prior permission in writing of the publishers, or in the case of reprographic reproduction in accordance with the terms of licenses issued by the Copyright Licensing Agency. Enquiries concerning reproduction outside those terms should be sent to the publishers.

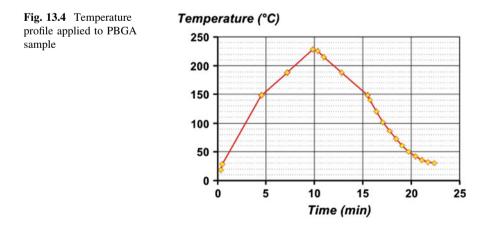

The use of registered names, trademarks, etc., in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant laws and regulations and therefore free for general use.

The publisher makes no representation, express or implied, with regard to the accuracy of the information contained in this book and cannot accept any legal responsibility or liability for any errors or omissions that may be made.

Cover design: eStudio Calamar S.L.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

## Contents

| 1 | <b>Deformation and Fatigue of Solders</b>                                                                                              | 1   |

|---|----------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2 | Factors Affecting the Bulk Embrittlementof Pb-Free Solder JointsK. Lambrinou                                                           | 19  |

| 3 | Thermal Fatigue Analysis                                                                                                               | 65  |

| 4 | Electrochemical Behavior of Solder Alloys                                                                                              | 81  |

| 5 | Void Formation by Kirkendall Effect in Solder Joints M. J. M. Hermans and M. H. Biglari                                                | 105 |

| 6 | Tin Whiskers                                                                                                                           | 123 |

| 7 | Electromigration in Solder Interconnects                                                                                               | 161 |

| 8 | Impact of Black Pad and Intermetallic Layers on the Riskfor Fractures in Solder Joints to ElectrolessNickel/Immersion GoldPE. Tegehall | 179 |

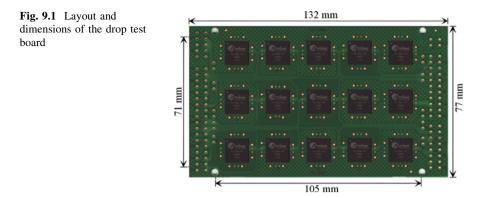

| 9 | Reliability of Electronic Assemblies Under Mechanical<br>Shock Loading<br>T. T. Mattila, T. Laurila, V. Vuorinen and J. K. Kivilahti   | 197 |

| 10 | Impact of Humidity and Contamination on SurfaceInsulation Resistance and Electrochemical MigrationPE. Tegehall                                               | 227 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 11 | Lead-Free and Other Process Effects on Conductive<br>Anodic Filamentation Resistance of<br>Glass-Reinforced Epoxy Laminates<br>C. Zou, A. Brewin and C. Hunt | 255 |

| 12 | PCB Delamination                                                                                                                                             | 275 |

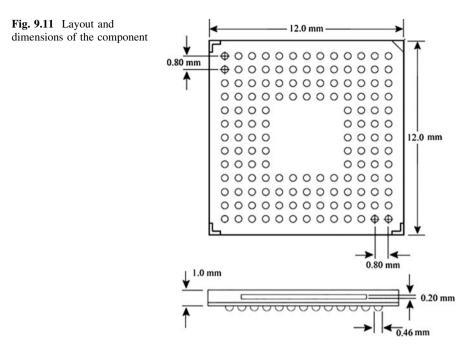

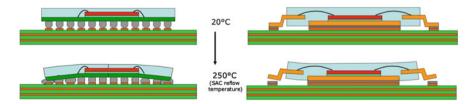

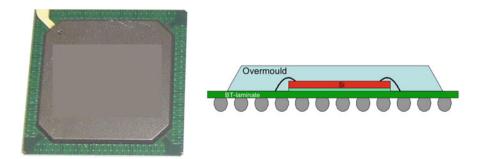

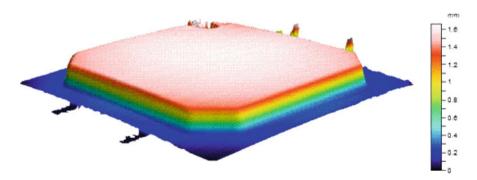

| 13 | Excessive Warpage of Large Packages During<br>Reflow Soldering<br>Bart Vandevelde                                                                            | 283 |

| 14 | Popcorn Cracking                                                                                                                                             | 297 |

| 15 | Thermal Capability of Components<br>C. Zardini and JY. Deletage                                                                                              | 305 |

## List of Contributors

**E. Auerswald**, Micro Materials Center Berlin and Chemnitz, Fraunhofer IZM, Volmerstr. 9 B, 12489, Berlin, Germany

I. Baylakoglu, TÜBİTAK UZAY, Ankara, Turkey

M. H. Biglari, Mat-Tech BV, Ekkersrijt 4605, Eindhoven, The Netherlands

A. Brewin, National Physical Laboratory, Teddington, Middlesex, UK

J.-Y. Deletage, Laboratoire IMS, 351 cours de la libération, 33405, Talence, France

**R. Dudek**, Micro Materials Center Berlin and Chemnitz, Fraunhofer ENAS, Technologie-Campus 3, 09126, Chemnitz, Germany

**G. Grossmann**, Swiss Federal Laboratories, EMPA, Überlandstrasse 129, Dübendorf CH-8600, Switzerland

E. Hedin, ERICSSON AB, Stockholm, Sweden

**M. J. M. Hermans**, Materials Science and Engineering Joining and Mechanical Behaviour, Delft University of Technology, Mekelweg 2, Delft, The Netherlands

C. Hunt, National Physical Laboratory, Teddington, Middlesex, TW11 0LW, UK

**J. K. Kivilathi**, Department of Electrical and Communications Engineering, Helsinki University of Technology, P.O. Box 3000, Otakaari 7A, 02015 TKK, Finland

R. Labie, IMEC, Kapeldreef 75, B-3001, Leuven, Belgium

K. Lambrinou, IMEC, Kapeldreef 75, B-3001, Leuven, Belgium

**T. Laurila**, Department of Electrical and Communications Engineering, Helsinki University of Technology, P.O. Box 3000, Otakaari 7A, 02015 TKK, Finland

**T. T. Mattila**, Department of Electrical and Communications Engineering, Helsinki University of Technology, P.O. Box 3000, Otakaari 7A, 02015 TKK, Finland

P.-E. Tegehall, Swerea IVF AB, Box 104, SE-431 22, Mölndal, Sweden

B. Vandevelde, IMEC, Kapeldreef 75, B-3001, Leuven, Belgium

**A. Vicenzo**, Dipartimento di Chimica, Materiali, Ingegneria Chimica "Giulio Natta", Politecnico di Milano, Via L. Mancinelli 7, 20131, Milano, Italy

V. Vuorinen, Department of Electrical and Communications Engineering, Helsinki University of Technology, P.O. Box 3000, Otakaari 7A, 02015 TKK, Finland

C. Zardini, Laboratoire IMS, 351 cours de la libération, 33405, Talence, France

C. Zou, NPL, Hampton Road, Teddington, Middlesex, TW11 0LW, UK

## **Chapter 1 Deformation and Fatigue of Solders**

Günter Grossmann

In this chapter, a brief introduction in the definition of cyclic load as well as in the deformation mechanisms and their corresponding degradation mechanisms is given. For more in-depth information, there is ample literature available.

#### **1.1 Deformation**

#### 1.1.1 Time-Independent Deformation

Every material deforms if stress is applied. The deformation can be either elastic, which means that the deformation is reversible as soon as the load is removed or instantaneous plastic if the stress is above the so-called yield stress.

The elastic deformation has its origin in the stretching of interatomic bonds.

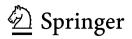

The bonds are a combination of attractive and repulsive forces with the net force being zero when the bond is at equilibrium. Clearly, when the atoms are far apart, the attractive part must dominate and when they are very close together, the repulsive part is greater; both contributions decay away as the separation increases. The combination of attractive and repulsive forces manifest in the general atomic force (F)–atomic spacing (r) graph (Fig. 1.1).

A tensile force will lengthen the interatomic bonds and will be opposed by the attractive part of the interatomic force. As soon as the minimum of the F-r graph is reached, the external force will dominate and the bond will break.

G. Grossmann (🖂)

EMPA, Überlandstrasse 129, Dübendorf, CH-8600, Switzerland e-mail: guenter.grossmann@empa.ch

Fig. 1.1 Atomic force-atomic spacing graph

This behaviour can be illustrated with a spring. As a load is applied, the spring extends following a linear law

$$F = C \cdot \Delta l \tag{1.1}$$

F load, C spring constant,  $\Delta l$  deformation.

In construction materials, this relationship is expressed as

$$\sigma = E \cdot \varepsilon \tag{1.2}$$

$\sigma$  stress, E modulus of elasticity or Young's modulus,  $\varepsilon$  strain or under shear load.

$$\tau = G \cdot \gamma \tag{1.3}$$

$\tau$  shear stress, G shear modulus,  $\gamma$  shear strain.

The elastic deformation is principally time independent. This means the specimen deforms as soon as a load is applied.

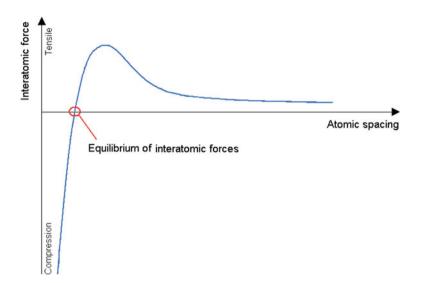

As soon as the spring is stretched above a certain amount, it will relax the maximum elastic amount but also the spring will show a remaining deformation if the load is removed. This behaviour is visible in most metals. If a metal is strained more than 0.5%, the stress–strain behaviour is clearly no more a straight line but a curve and a not-recoverable deformation called plastic deformation takes place. The plastic deformation is caused by the movement of crystal layers above each other. As soon as a certain stress is exceeded, dislocations in the crystal lattice will be activated to move through the crystal lattice and thus two plains of atoms are moving across each other. The point where the elastic deformation gradually merges to the plastic deformation is called the proportional limit. However, this

1 Deformation and Fatigue of Solders

Fig. 1.2 Definition of yield strength

point cannot be defined precisely. To overcome this problem, a line with the same slope as the elastic line is drawn, originating from a given strain, usually 0.2%. The intersection of this line with the curved line of the stress–strain diagram is called the yield strength (Fig. 1.2).

#### 1.1.2 Time-Dependent Deformation

There is also a time-dependent elastic deformation. This means that under a constant load, a material deforms and after the load is removed, the deformation goes back to 0 over time. This behaviour is called anelastic deformation.

If a material under load experiences an elevated temperature, time-dependent plastic deformation takes place, which means that the material shows an ongoing deformation under constant load. This deformation is called creep.

In contrast to the spring example, a material that creeps can be compared with a wet chewing gum. If one applies a constant load to such a specimen, it will constantly deform until it breaks. Varying the load results in differences in the deformation rate. The heavier the load, the faster the chewing gum deforms. If the specimen is cooled down, the deformation will come to an end as soon as the chewing gum is frozen.

How fast a material deforms if a certain load is applied depends on how close it is to its solidus temperature. How close the temperature of the application is to the solidus temperature is expressed with the homologues temperature

$$T_{\rm H} = \frac{T_{\rm A}}{T_{\rm S}} \tag{1.4}$$

$T_{\rm A}$  temperature of application (K),  $T_{\rm S}$  temperature of solidus (K).

Note that absolute temperatures in Kelvin are to be used.

As soon as a material surpasses a  $T_{\rm H}$  of 0.5, creep becomes an important part of the deformation history.

In creep, two deformation mechanisms are dominant: grain boundary sliding and dislocation creep. In grain boundary sliding (GBS), the crystals that make up the metal slide above each other along their grain boundaries. Since the grains fit only in one configuration, they have to move on complex paths combining rotation and lateral movement in all three dimensions to come around each other. As soon as the stress applied exceeds a certain value, dislocations will start to glide through the grains (DC), thus deforming the grains. Again in both cases the deformation causes microvoids to form that have to be filled up by diffusion.

Thus, GBS occurs if low stress results in a slow deformation, DC is the dominant deformation mechanism if large stress is applied to a specimen.

In reality, GBS and DC never occur on their own. Also, with a low overall stress that would activate GBS only, local stress build-up can cause local DC.

In contrast to the elastic deformation, creep is time dependent as already mentioned earlier. Thus, the load does not cause a certain deformation but a deformation rate.

$$F = f\left(\frac{\Delta l}{\Delta t}\right) \tag{1.5}$$

F force,  $\Delta l$  elongation,  $\Delta t$  time; or as stress-strain.

$$\sigma = f(\dot{\varepsilon}) \tag{1.6}$$

$\sigma$  normal stress,  $\dot{\varepsilon}$  strain rate; or under shear load

$$\tau = f(\dot{\gamma}) \tag{1.7}$$

$\tau$  shear stress,  $\dot{\gamma}$  shear strain rate.

This means the more load one applies to a specimen, the faster it deforms, and the longer one waits, the more the specimen deforms; in other words, every deformation can be achieved with every load—it is just a question of time. Thus, it is senseless to speak of a yield strength when characterising soft solder: Since Creep is the main deformation mechanism in soft solders due to their high homologues temperature even at room temperature (Table 1.1), every deformation rate will result in another yield strength.

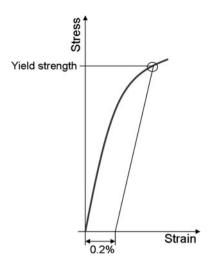

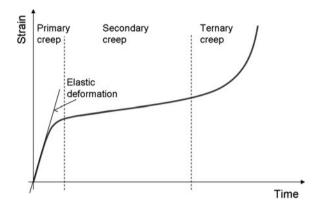

If a creep test is done, where a constant load is applied to the specimen and the deformation is monitored, one sees that the strain often varies over time (Fig. 1.3). After an initial elastic deformation, primary creep with a varying strain rate takes place followed by a regime with mostly constant creep rate called secondary creep. In the end, the creep rate starts to increase due to damage in the material until the specimen fails.

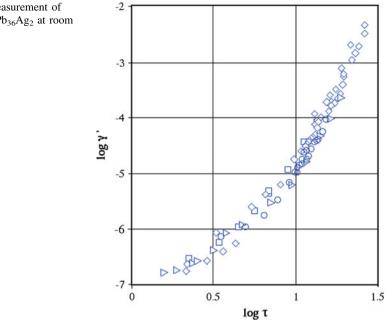

If the creep rate of metals is plotted against the stress applied in a double logarithmic plot, one sees that over a limited interval, the measurement points are located on a straight line.

| <b>Table 1.1</b> $T_{\rm H}$ at 20°C of | Alloy                                 | $T_{ m L}$   | $T_{\rm H}~(20^{\circ}{\rm C})$ |

|-----------------------------------------|---------------------------------------|--------------|---------------------------------|

| some soft solder alloys                 | SnPb <sub>36</sub> Ag <sub>2</sub>    | 183°C, 456 K | 0.643                           |

|                                         | SnAg <sub>3.8</sub> Cu <sub>0.7</sub> | 217°C, 490 K | 0.598                           |

|                                         | SnAg <sub>3.5</sub>                   | 221°C, 494 K | 0.593                           |

|                                         | SnCu <sub>0.7</sub>                   | 227°C, 500 K | 0.586                           |

Norton [1] surveyed creep in steel and described the nearly linear relationship of the secondary creep in the double logarithmic plot with

$$\dot{\gamma} = A \left(\frac{\tau}{G}\right)^n \exp\left[\frac{Q}{RT}\right]$$

(1.8)

$\dot{\gamma}$  creep rate, A constant,  $\tau$  shear stress, G shear modulus, n exponent, Q activation energy, R gas constant, T temperature in K

where  $\tau$  is normalised with the shear modulus G in order to eliminate the units of  $\tau$  and an Arrhenius term is used to account for the influence of the temperature.

However, in solder, over an extended measurement range of stress vs. strain rate, one sees that the measurement points are no more located on a straight line (Fig. 1.4).

Several models have been used to describe this behaviour.

A very popular model is the approach of Garofalo [2] who approximated the curve where the points are located with a sinh-relationship:

$$\dot{\gamma} = C_1 [\sinh(C_2 \tau)]^n \tag{1.9}$$

$\dot{\gamma}$  creep rate,  $C_1$ ,  $C_2$  constant,  $\tau$  shear stress, *n* exponent.

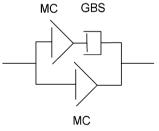

Another possibility has been proposed by Hart [3] who treated the system of grain boundary sliding (GBS) and matrix creep (MC which is the same as DC) with a rheological analogue (Fig. 1.5). Hart modelled GBS with a linear viscous law and MC by a power law.

Fig. 1.5 Analogous model of Hart

The system of Fig. 1.5 can be modelled with

$$\sigma = \sigma_0 [y + (1 - y)Z]\dot{\varepsilon}^{\mu} \tag{1.10}$$

$\sigma$  stress,  $\dot{\varepsilon}$  strain rate,  $\sigma_0$  material constant,  $\mu$  material constant, y parameter for the grain size; with

$$Z = \frac{\sigma_{\rm b}}{\sigma_{\rm m}} \tag{1.11}$$

$\sigma_{\rm b}$  stress in the grain boundaries,  $\sigma_{\rm m}$  stress in the matrix.

Another constitutive equation proposed by Weber and Grossmann [4] models the deformation behaviour of soft solder as the sum of the two deformation mechanisms GBS and DC, both expressed with a Norton equation:

#### 1 Deformation and Fatigue of Solders

$$\dot{\gamma} = A \left(\frac{\tau}{G}\right)^n \exp\left[\frac{-Q_{\text{GBS}}}{RT}\right] + B \left(\frac{\tau}{G}\right)^m \exp\left[\frac{-Q_{\text{DC}}}{RT}\right]$$

(1.12)

$\dot{\gamma}$  strain rate,  $\tau$  shear stress, G dynamic shear modulus,  $Q_{\text{GBS}}$  activation energy GBS,  $Q_{\text{DC}}$  activation energy DC, n exponent GBS, m exponent DC.

#### **1.2 Degradation Due to Cyclic Load**

#### 1.2.1 Definition of a Cyclic Load

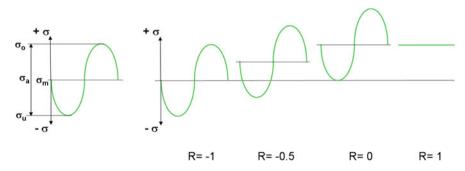

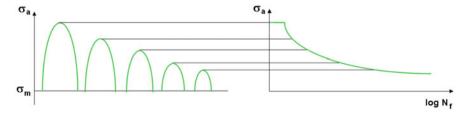

A regular cyclic load is defined by its stress amplitude  $\sigma_a$ , its mean stress  $\sigma_m$  as well as the upper stress level  $\sigma_u$ , the lower stress level  $\sigma_1$  and the period of a cycle *t* (Fig. 1.6) with

$$\sigma_{\rm a} = \sigma_{\rm u} - \sigma_{\rm l} \tag{1.13}$$

$\sigma_a$  stress amplitude,  $\sigma_u$  upper stress level,  $\sigma_1$  lower stress level or with the stress quotient *R*:

$$R = \frac{\sigma_1}{\sigma_u} \tag{1.14}$$

$\sigma_1$  lower stress level,  $\sigma_u$  upper stress level; and

$$f = \frac{1}{t} \tag{1.15}$$

f frequency, t time for 1 period.

A cyclic load can be single-levelled with  $\sigma_m$  and  $\sigma_a$  constant or multi-levelled with varying  $\sigma_m$  and  $\sigma_a$ . The frequency *f* is rarely varied since if *f* is varied, the evaluation of the resistance of a material against fatigue becomes multidimensional and extremely complex.

Fig. 1.6 Definition of a cyclic load

#### 1.2.2 Fatigue Testing

The resistance of a material against cycle fatigue is evaluated by cyclic fatigue testing with two kind of testing set-up: In one set-up,  $\sigma_m$  is held constant and  $\sigma_a$  varies and in the second set-up, both,  $\sigma_m$  and  $\sigma_a$ , are varied.

#### 1.2.2.1 $\sigma_{\rm m}$ Constant, $\sigma_{\rm a}$ Varying

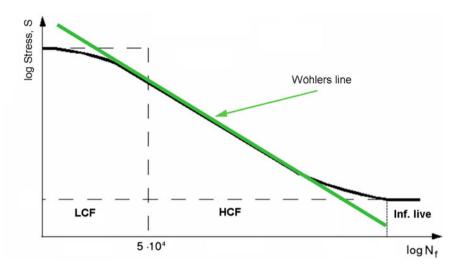

Usually  $\sigma_{\rm m}$  is 0, which means that the specimen encounters cyclic tensile and compressive stress. By varying  $\sigma_{\rm a}$ , the average number of cycles to failure ( $N_{\rm f}$ ) is determined for each level of  $\sigma_{\rm r}$  (Fig. 1.7). The resulting curve of  $N_{\rm f} = f \cdot (\sigma_{\rm a})$  is called Wöhler's curve.

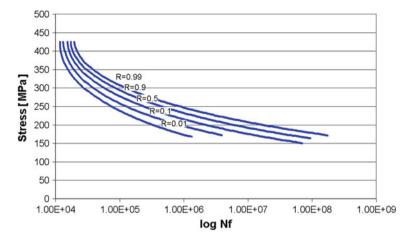

Of course there is a considerable spread in the measurements of Wöhler's curve. Thus, the failure probability has to be included in the measurements to describe the resistance of a material against high-cycle fatigue (Fig. 1.8).

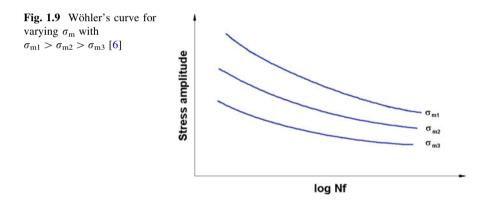

#### **1.2.2.2** $\sigma_{\rm m}$ and $\sigma_{\rm a}$ Varying

If both parameters are varied, there are 2 ways to look at the results. The straightforward one is to draw the average Wöhler's curve for various  $\sigma_m$  in one diagram (Fig. 1.9).

The other possibility is to fix a desired  $N_{\rm f}$  for a specimen and plot the  $\sigma_{\rm a}$  and  $\sigma_{\rm m}$  combinations leading to this particular  $N_{\rm f}$  in the Haigh diagram (Fig. 1.10).

#### 1.2.3 Brittleness

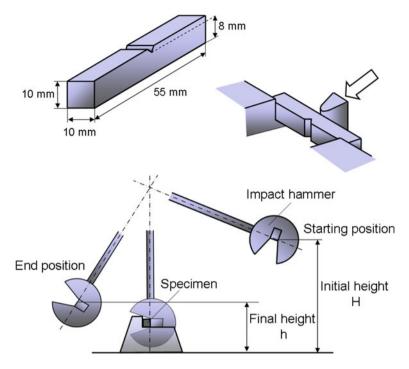

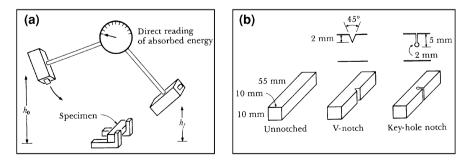

The brittleness of a material is measured in the Charpy test with an impact tester where a pendulum hits a specimen that bears a notch (Fig. 1.11). The geometry of the specimen and the notch are standardised in EN10045.

Fig. 1.7 Determination of Wöhler's curve [5]

Fig. 1.8 Wöhler's curve of an Al-alloy with  $\sigma_m = 0$  with the probability of occurrence as free parameter [6]

The energy loss of the pendulum given by the difference of height between the starting position and the end position of the pendulum (H-h) is a measure for the brittleness of the specimen. A ductile material will absorb more kinetic energy than a brittle material and thus h will be smaller if a ductile material is tested than for a brittle material. The brittleness of a material depends on the crystal structure, on grain size and on shape and size of particles to name a few influencing factors. Whether a material is brittle or not depends also on its temperature. Many materials show a transformation from ductile to brittle as a function of temperature called the transition temperature.

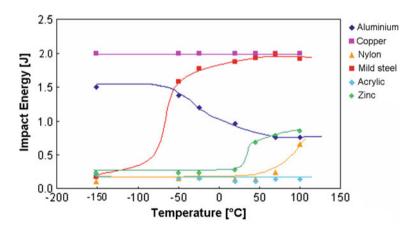

This transition from brittle to ductile is influenced by the crystal lattice. Cubic face-centred (fcc) materials such as Pb, Al or Cu retain their plasticity at low temperature where cubic body-centred materials such as Fe, Cr or W show a clear transition temperature (Fig. 1.12).

Fig. 1.10 Haigh diagram for a given  $N_{\rm f}$  [6]

Various parameters influence the brittleness of solder, as discussed in Chap. 2. There seems to be no widely accepted parameter or index (in ASTM, or ASM or Mil Handbook standards or elsewhere) for distinguishing brittleness from ductile failure. The best statement might come from the qualitative guidance offered by Charpy impact toughness measurements (either as a function of temperature or strain rate), where failures below the transition toughness level are considered as generally brittle and those above that as ductile. For tensile tests, it is common to report failure strains, and let readers make the judgement in the context it was presented. In industry, anything below a few % failure strain such as 5 or 10% (from a room temperature tension test, for example) would be considered to be brittle. Thus, there can be an "arbitrary" industry basis, with some understandable justification, to call a material brittle for failure strains less than a few percent.

Regarding shear failure strains, it is difficult to apply such a definition. Microscopically, some single crystals of ductile metals will fail by pure shear along slip planes when suitably oriented in tension tests, but in shear, they can exhibit very large strain to fracture, often like 20, 50%, due to accumulation of sliding on planes across the gage section.

Fig. 1.11 Charpy test

Fig. 1.12 Transition of some materials [7]

On the other hand, under biaxial pure shear load, one could have a material fail with an overall strain at rupture above 10%. However, taking the strain to failure in either stress direction, it could be that in one direction high strain occurs thus being

Fig. 1.13 Zones in Wohlers curve

characterised as ductile failure while in the other direction the material deforms only a few per cent and should be declared as brittle

#### 1.2.4 Modes of Fatigue

In Wöhlers curve, three areas can be identified (Fig. 1.13). On the left side, one can see that the stress applied has nearly no influence on  $N_{\rm f}$ . Degradation in this area appears early and is called low-cycle fatigue (LCF). In order to have a more precise definition, it is common sense that failures below  $5 \times 10^4$  are assigned to LCF. If a specimen fails, later it is attributed to high-cycle fatigue (HCF). Some materials, such as steel, show a fatigue limit, a stress level below which no failures occur which is assigned as infinite life. This limit is not easy to determine because the limit occurs at low stress levels where tests usually run for a long time and where it is difficult to distinguish between a slow degradation and a real fatigue limit.

#### **1.2.4.1** Low-Cycle Fatigue

As already mentioned, in LCF, the stress amplitude applied has no direct influence on  $N_f$ . This is due to the fact that in LCF, the degradation is strain driven. Be it time-independent or time-dependent strain. In slow cycles where time-dependent deformation takes place, not only the stress applied to a specimen has to be considered but also the time (the frequency) is important. This applies specially to ductile materials such as solder where creep is essential.

#### 1 Deformation and Fatigue of Solders

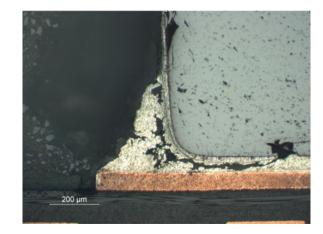

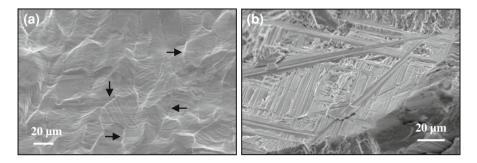

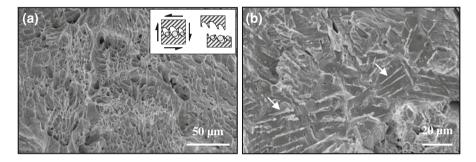

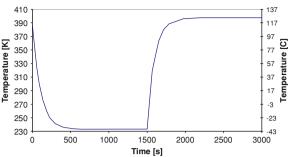

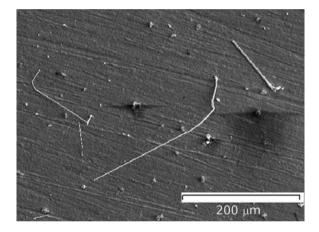

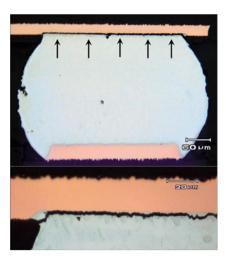

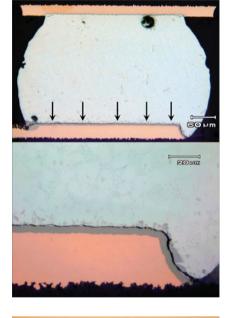

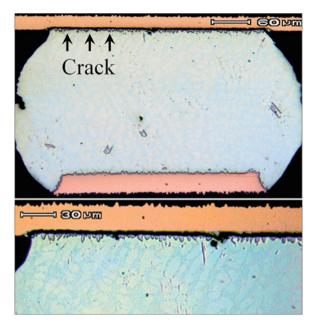

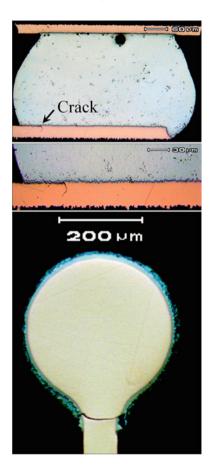

Each cycle will leave some microvoids because the grains only fit in one configuration and every plastic deformation due to GBS will cause voids due to the geometric mismatch. Along the grain boundaries, atoms will diffuse from areas with compressive stress to the voids and fill them up. The longer one waits, the more atoms will diffuse into the voids, and the higher the temperature, the faster the diffusion takes place. However, usually the cycle will be reversed before the voids are totally filled up, thus leaving a microvoid. With every cycle, new microvoids form and coalescent to large defects. The larger the deformation per cycle is, the larger are the microvoids that form. This means that in LCF, a degradation field develops where microvoids coalesce during the cyclic load to crack like separations. This degradation field corresponds to the strain filed in a material which means that degradation is well visible in lead-free solder after thermal cycling (Fig. 1.14).

The degradation due to LCF has been modelled by Coffin and Manson with

$$N_{\rm f} \cdot \varepsilon_{\rm pl}^{\alpha} = C \tag{1.16}$$

$N_{\rm f}$  number of cycles to failure,  $\varepsilon_{\rm pl}$  plastic deformation per cycle,  $\alpha$  degradation exponent, *C* constant as well as by Morrow with

$$N_{\rm f} \cdot E^{\beta} = C \tag{1.17}$$

$N_{\rm f}$  number of cycles to failure,  $E_{\rm pl}$  strain energy per cycle,  $\beta$  degradation exponent, C constant.

The strain energy can be derived from the area in the stress–strain hysteresis, which occurs in a material under cyclic load with plastic deformation. The main difference of the two models is the fact that in the Coffin–Manson approach, only the strain is the driving force for the degradation. The model of Morrow assumes that also the stress applied influences the degradation. With the approach of

**Fig. 1.14** Degraded solder joint made of SnAg<sub>3.5</sub>Cu<sub>0.7</sub> after 4,000 thermal cycles (-20°C/+120°C)

Morrow, this means in practical applications that short thermal cycles (e.g. in an accelerated test with steep temperature ramps and large temperature excursion) with large stress but small strain result in an equivalent degradation as in a slow cycle with reduced temperature excursion which, due to creep, will induce large strain with small stress because the area in the stress–strain hysteresis is the same in both cases. The Coffin Manson approach restricts the possibility of accelerated testing since in any test, the cycles must be long enough to allow the material to creep. Generally, it does not make a big difference which of the two models is used. Since it is easier do determine the strain per cycle than the strain energy, the Coffin–Manson relationship is more popular than Morrows equation. Assuming total relaxation during each thermal cycle in the solder joint of an electronic component, the strain can be estimated by:

$$\varepsilon_{\rm pl} = \frac{\Delta \alpha \cdot \Delta \vartheta \cdot l_0}{d} \tag{1.18}$$

$\Delta \alpha$  difference of the coefficients of thermal expansion between the component and the PCB,  $\Delta \vartheta$  temperature swing,  $l_0$  half-length of the component, *d* thickness of solder gap.

Of course this is only an estimate. The deformation field can only be determined with FEM simulation as it is outlined in Chap. 3. However, also the simulation has its limitations. It shows the deformation field for a given idealised geometry only. In reality, the geometry and also the structure of the solder, which influences the creep behaviour of the solder, change continuously as the degradation evolves. And, due to differences in the geometry and in the structure of the solder joints, the degradation evolves different in each joint. The consequence is evident in a component with two connectors such as a chip resistor. One of the solder joints will degrade faster than the other. This means that over time, the loadbearing area of one joint becomes smaller than the one of the other joint, which again means that in the end of the process, the weaker joint only will be deformed and degrade. As a consequence, in Eq. (1.18), the full length of the component has to be used for  $l_0$  instead of its half-length.

However, for a first approximation of the live time of a solder joint, one can say that the estimate as shown above is often precise enough despite its shortcomings.

#### 1.2.4.2 High-Cycle Fatigue

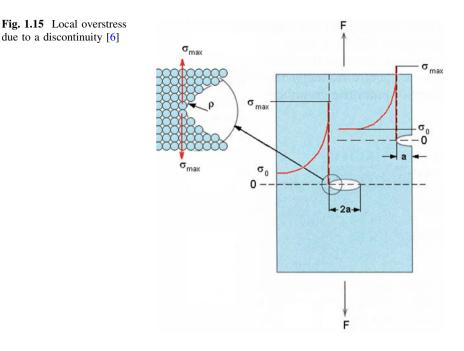

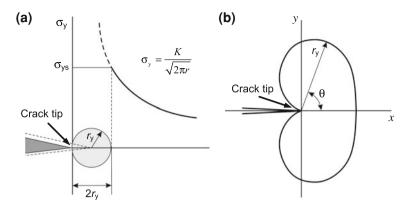

HCF is stress driven in contrast to LCF. If a load is applied to a homogeneous specimen, the stress is evenly distributed. However, if the bearing cross-section of the specimen contains a discontinuity, stress amplification at the tip will occur (Fig. 1.15). The maximum stress occurring at the tip can be calculated with

$$\sigma_{\max} = 2\sigma_0 \sqrt{\frac{a}{\rho}} \tag{1.19}$$

$\sigma_{\text{max}}$  maximum stress,  $\sigma_0$  average stress, *a* length of discontinuity,  $\rho$  radius of discontinuity.

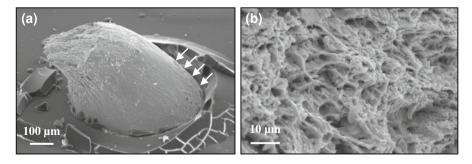

Due to a certain plasticity in metals,  $\sigma_{max}$  is transformed to strain in a limited zone around the tip. The radius of this zone depends on the mechanical properties of the material. In a brittle material, the radius  $\rho$  is smaller than in a ductile material and because of the term  $1/\rho$ ,  $\sigma_{max}$  becomes infinite if  $\rho$  is converging to 0, independently of the applied load. This maximum stress can be high enough to break up the bonds of the atoms that are right at the end of the tip. As a result, a crack will grow as long as a positive load is applied in a cycle even if the load is far below the yield strength of the material. In other words, the more brittle a material is, the more HCF becomes a thread. The progress of a crack due to highcycle fatigue can be seen on the surface of a rupture. From an initial site, the stairlike striations indicate the path of the fatigue until the bearing area is so small that the yield strength of the material is exceeded and a forced rupture occurs (Fig. 1.16).

Because in the HCF zone, the Wöhler curve is very close to a straight line, the degradation has been modelled by Basquin with

$$\sigma \cdot N_{\rm f}^{\alpha} = C \tag{1.20}$$

$\sigma$  stress amplitude,  $N_{\rm f}$  number of cycles to failure,  $\alpha$  degradation exponent, *C* constant.

Fig. 1.16 High-cycle fatigue damage

Generally, high-cycle fatigue is not a concern for solder joints, since due to the ductility of the material, the critical radius will never converge to 0. With SnPb solder also the brittle interfaces with intermetallic compounds which are prone to high-cycle fatigue rarely see enough load to exhibit failure due to rapid cycling. Usually the leads of components fail before the solder joint shows significant degradation.

Lead-free solders on the other hand show some properties that make the occurrence of high-cycle fatigue in the solder joint more probable:

- The lower creep rate of lead-free solder causes larger stress in the intermetallic compound, thus provoking high-cycle fatigue in the interface of the solder with the substrate.

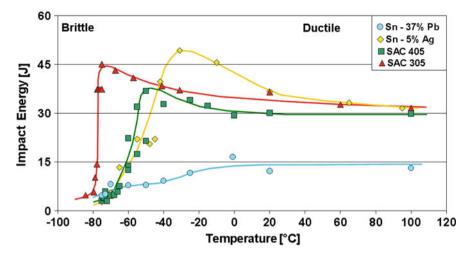

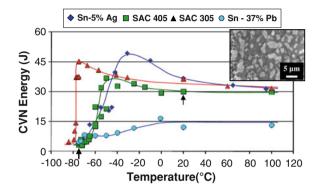

- Lead-free solder containing Ag shows a clear transition temperature as shown at IMEC with a mini-Charpy tester on specimen measuring  $10 \times 10 \times 55$  mm (Fig. 1.17). The outcome of the investigation was that SnPb shows a gradual transition below  $-20^{\circ}$ C. The Sn–Cu alloys show a clear transition between -140 and  $-120^{\circ}$ C. The most interesting result was that Sn–Ag shows a transition temperature depending on the amount of Ag in the alloy. The alloy with 5% Ag had its transition between -60 and  $-20^{\circ}$ C, which is in the range technical applications with lead-free solder are subject to.

The same damaging characteristic as in high-cycle fatigue (incremental growth of a crack due to local overstress in brittle materials) has been observed in tests on lead-free solders but the number of cycles to failure is not necessarily  $>10^5$  cycles as expected in high-cycle fatigue. Thus, in solder joints, it might be more appropriate to talk about stress-induced fatigue rather than high-cycle fatigue.

Fig. 1.17 Transition of solders [8]

This means that in certain mission profiles, high-cycle fatigue in lead-free solder might become important:

- Low temperature

- High Ag content

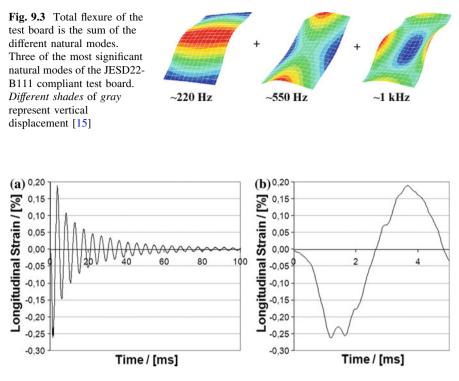

- Fast alternating load such as bending of a PCB due to vibration or drop. Tony Mattila at HUT Helsinki found that a PCB starts to vibrate after impact in a drop test with bending modes occurring at various natural frequencies of the specimen [9]. This is discussed in depth in Chap. 9.

#### 1.2.4.3 More than One Degradation Mechanism

Of course usually more than one degradation mechanisms occur in a material in real-field applications. As it is implied in Eq. (1.12), GBS and DC are always effective in varying proportions. But also HCF and LCF might occur under combined vibration and thermal cycle load in a temperature range close to the transition temperature where creep is active. This has been modelled by Miner and Palmgren with

$$\sum_{i=1}^{n} \frac{n_i}{N_{\rm fi}} = 1 \text{ at failure}$$

(1.21)

$n_i$  number of cycles with degradation mechanism *i*,  $N_{fi}$  number of cycles to failure with degradation mechanism *i*.

For the special case where different degradation mechanisms are active in one load cycle, Eq. (1.21) can be modified as proposed by Halford and Manson:

$$\sum_{i=1}^{n} \frac{f_i}{N_{\rm fi}} = \frac{1}{N_{\rm f}} \tag{1.22}$$

$f_i$  fraction of a cycle with degradation mechanism *i*,  $N_f$  number of cycles all mechanisms combined.

In [10], it has been shown in a joined work between CRF and IMEC within the EC-IMECAT project that a combined load of temperature cycling and vibration, as encountered in automotive applications, has a more severe effect on the degradation of a solder joint than the same stress history applied sequentially, incorporating a considerable amount of stress-induced fatigue.

#### References

- 1. Norton FH (1929) The creep of steels at high temperatures. Mc. Graw-Hill, New York

- 2. Garofalo F (1963) Trans Metall Soc AIME 227

- 3. Hart EW (1967) Acta Metall 15:1545 ff

- Grossmann G, Weber L (1999) The deformation behaviour of Sn62Pb36Ag2 and its implications on the design of thermal cycling tests. IEEE Trans Electron Packag Manufact 22:71

- 5. Bargel HJ, Schulze G (2004) Werkstoffkunde, 8th edn. Springer, Berlin

- 6. Callister WD Jr (2003) Materials science and engineering. Wiley, London

- 7. University of Cambridge, http://www.doitpoms.ac.uk/tlplib/BD6/results.php. Accessed June 2009

- Lambrinou K et al (2009) A novel mechanism of embrittlement affecting the impact reliability of tin-based lead-free solder joints. J Electron Mater. doi:10.1007/ s11664-009-0841-0

- Marjamäki P, Mattila TT, Kivilahti JK (2006) A comparative study of the failure mechanisms encountered in drop and large amplitude vibration tests. In: Proceedings 56th electronic component and technology conference, San Diego, CA, May 30–June 2, pp 95–101

- 10. Vandevelde B et al FP5-CSG-IMECAT: highlights of a EC funded project on lead-free materials and assembly development technology, IPC Barcelona

## **Chapter 2 Factors Affecting the Bulk Embrittlement of Pb-Free Solder Joints**

#### K. Lambrinou

#### Abbreviations

| ASTM     | American Society for Testing and Materials    |

|----------|-----------------------------------------------|

| bcc      | Body-centred cubic                            |

| bct      | Body-centred tetragonal                       |

| BSE      | Back scattered electron                       |

| CAT      | Crack-arrest temperature                      |

| CMOD     | Crack-mouth opening displacement              |

| CTOD     | Crack-tip opening displacement                |

| CVN      | Charpy V-notch                                |

| DBTT     | Ductile-to-brittle transition temperature     |

| fcc      | Face-centred cubic                            |

| FTE      | Fracture transition elastic temperature       |

| FTP      | Fracture transition plastic temperature       |

| hcp      | Hexagonal close-packed                        |

| IMC(s)   | Intermetallic(s) or intermetallic compound(s) |

| LLD      | Load line displacement                        |

| NDT      | Nil ductility temperature                     |

| Pb-free  | Lead-free                                     |

| SAC      | Sn–Ag–Cu                                      |

| SE       | Secondary electron                            |

| SEM      | Scanning electron microscopy                  |

| Sn-based | Tin-based                                     |

K. Lambrinou IMEC, Kapeldreef 75, 3001 Leuven, Belgium

Present Address: K. Lambrinou (⊠) SCK-CEN, Boeretang 200, 2400 Mol, Belgium e-mail: klambrin@sckcen.be

#### **Special Symbols**

- []\* Figure adapted from the reference given in []

- []<sup>§</sup> From "The Science and Engineering of Materials", 5th edition, by Askeland and Phulé. © 2006 by Nelson. Reprinted with permission of Nelson, a division of Thomson Learning: www.tomsonrights.com. Fax: 800 730 2215

- []<sup>#</sup> From "The Science and Engineering of Materials", 1st edition, by Askeland. © 1984 by Wadsworth, Inc. Reprinted with permission of Brooks/Cole, a division of Thomson Learning: www.tomsonrights.com. Fax: 800 730 2215

- []<sup>&</sup> From "Deformation and Fracture Mechanics of Engineering Materials", 4th edition, by Hertzberg. © 1996 by John Wiley & Sons, Inc. Reprinted with permission of John Wiley and Sons, Inc

- []<sup>†</sup> From "Fracture and Fatigue Control in Structures: Applications of Fracture Mechanics", 3rd edition, by Barsom and Rolfe. © 1999 by ASTM International. Reprinted with permission of ASTM International

- []<sup>∞</sup> Reproduced with permission of Emerald Group Publishing Ltd. © 2000 by MCB University Press

#### 2.1 Introduction

The fracture behaviour of all materials is affected by several factors, some of which are 'intrinsic', i.e. reflecting the material constitution, and some 'extrinsic', i.e. relating to the processing or service conditions. Examples of 'intrinsic' factors are the material composition, crystal structure, and microstructure, while examples of 'extrinsic' factors include the cooling rate during processing, as well as the temperature, strain rate, or constraint of the material during service. Changes in the processing or service conditions often alter the crystal structure, microstructure, or even composition of the material (e.g. by contamination), which might affect its fracture behaviour. Electronic materials, like the lead-free (Pb-free) solders studied in the framework of ELFNET, are no exception to the above general rules of thumb. It has already been observed, for example, that the fracture behaviour of tin-based (Sn-based) solders changes from ductile to brittle under solder-specific service conditions. This type of brittle fracture occurs in the solder joint unlike the typical brittle failures occurring in the intermetallic layers that are present between solder joint and bond pad; therefore, it is often referred to as 'bulk solder embrittlement'. This chapter attempts to identify the factors affecting the bulk embrittlement of Sn-based Pb-free solder joints, as this type of embrittlement may occur during the solder joint life cycle, depending on the requirements of the 'mission profile'. Identifying these factors and understanding how they facilitate embrittlement is the first step in finding ways to limit, delay, or even avoid bulk solder joint embrittlement during service. However, due to the limited available data, the factors affecting the bulk embrittlement of Pb-free solder joints will be addressed by referring to data acquired from studying other metallic materials with similar behaviour, e.g. ferritic steels.

#### 2.1.1 Comparing Ductile to Brittle Fractures

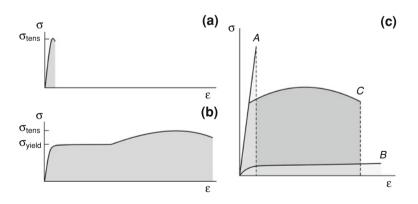

It is common knowledge that *brittle fractures* occur with little or no plastic deformation prior to failure and are characterised by very limited energy absorption. This is the type of failure that occurs at extremely high speeds (up to 2,000 m/s or 7,000 ft/s in steels) [1]. An example of the stress–strain behaviour of a brittle material subjected to tension is given in Fig. 2.1a, where one may observe the essential absence of strain (i.e. deformation) before failure of the material at the ultimate tensile strength,  $\sigma_{tens}$ .

Contrary to brittle fractures, ductile fractures are characterised by appreciable plastic deformation prior to failure and high energy consumption [1]. When a ductile material is subjected to tension, as shown in Fig. 2.1b, an appreciable amount of strain usually results from loading the material above its yield strength,  $\sigma_{yield}$ . The fact that ductile materials deform a lot before failing, and that this failure is relatively slow, makes ductile fractures more appealing than brittle ones in the eyes of the design engineer.

Two notions very closely related to the type of material failure (i.e. ductile vs. brittle) are those of toughness and ductility. *Toughness* is the ability of a material to resist fracture and represents the energy absorbed during failure [2, 3]. A brittle material, for example, absorbs small amounts of energy during fracture, while a tough/ductile material absorbs large energy amounts. For an unnotched tensile bar, the energy dissipated during failure can be estimated from the area under the stress–strain curve (Fig. 2.1), as follows [2]:

Energy/volume =

$$\int_{0}^{\varepsilon_{f}} \sigma d\varepsilon$$

(2.1)

**Fig. 2.1** Typical stress-strain curves of (a) brittle materials and (b) ductile materials  $[1]^*$ . **c** Superposition of the stress-strain curves of a strong material with little capability for plastic flow (*A*), a material with low strength but high ductility (*B*), and a material with optimum combination of strength and ductility for maximum toughness (*C*) [2]\*. \* Figure adapted from the Reference in []. The meaning of symbol \* is the same throughout this text

where  $\sigma$  is the stress,  $\varepsilon$  is the strain, and  $\varepsilon_f$  is the strain at failure.

On the other hand, *ductility* is the ability of a material to deform plastically without fracturing. Ductility is commonly expressed either as % elongation in the gage length, or % reduction in the area of a tensile specimen tested to failure [4]. It must be emphasised that maximum toughness requires a combination of strength and ductility [2], since high strength or good ductility alone cannot guarantee an enhanced toughness (Fig. 2.1c).

#### 2.1.2 Factors Affecting the Type of Fracture

It is often erroneously believed that the type of fracture of a certain material is either ductile or brittle and that defining the fracture type is quite straightforward. This could, for example, be based on the fact that the deformation and fracture characteristics of materials depend on very material-specific properties, such as the nature of the electron bond, the crystal structure, and the degree of atomic order [2]. Another way to predict the type of failure of a material would be to consider its fundamental engineering properties, such as the yield strength, tensile strength, and tensile ductility [2], since high-toughness materials combine good strength and ductility. However, the job of a design engineer is not that simple, because some materials (like many metals) that fail in a ductile manner under mild service conditions might embrittle if subjected to low temperatures, high strain rates, or multiaxial stress states related to the presence of notches or defects [1-3]. The Sn-based Pb-free solders extensively addressed in this chapter fall into that category, for example. Moreover, some materials (like many ceramics) that fail in a brittle manner at mild ambient temperatures will certainly increase their ductility when exposed to sufficiently high temperatures; for ceramics, this change in fracture behaviour occurs usually above 1,000°C [5].

#### 2.2 Crystal Structure, Microstructure, and Fracture Resistance

As mentioned in Sect. 2.1.2, the deformation and fracture characteristics of a material are affected by the nature of the electron bond, the crystal structure, and the degree of atomic order in the material. For example, the more rigidly fixed the valence electrons, the greater the propensity of a material to fail in a brittle manner [2]. In ionic solids, the valence electrons are tightly bound to their respective atoms inside the crystal [6], which explains their high propensity to brittle failure. In both covalent and metallic crystals, the valence electrons are shared between atoms [6]; however, their fracture behaviour is different due to the following reasons: in covalent solids, the valence electrons are shared between an

atom and its nearest neighbours, while in metallic solids, the valence electrons are shared equally by all atoms in the material. The greater restriction in the movement of valence electrons experienced by covalent materials (e.g. diamond, silicon, carbides, nitrides, and silicates) accounts for their tendency to fail in a brittle manner, while materials held together by metallic bonds are the easiest to deform, failing usually in a ductile manner [2].

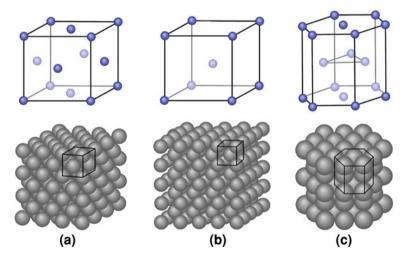

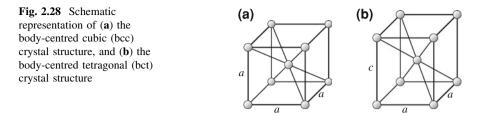

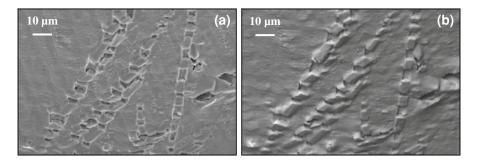

Materials with a low crystal symmetry, where slip is difficult, show a greater tendency to fail in a brittle manner. On the contrary, close-packed crystals characterised by high crystal symmetry are capable of considerable plastic deformation. For example, *face-centred cubic* (*fcc*) and *hexagonal close-packed* (*hcp*) crystals are less prone to brittle failure than *body-centred cubic* (*bcc*) crystals. Moreover, bcc metals show a much higher propensity to low-temperature embrittlement than fcc and hcp metals, as will be discussed more extensively later on. Figure 2.2 shows schematic representations of the fcc, bcc, and hcp crystal structures.

Another structural factor that affects the fracture resistance of a material is the degree of order in the atomic arrangement. It has been observed that the tendency for brittle failure increases as the degree of order in the atomic arrangement increases. In fact, the addition of a solute to a crystal lattice progressively suppresses plastic flow, as the solid solution that results from this addition changes gradually from disordered to short-range ordered first, and subsequently to long-range ordered [2].

The above-discussed theoretical aspects of the material structure have a great impact on the material's fracture resistance, but might be difficult to grasp and put

**Fig. 2.2** a The face-centred cubic (fcc) crystal structure is shown as a reduced-sphere unit cell and an atomic aggregate [5]\*. b The body-centred cubic (bcc) crystal structure is shown as a reduced-sphere unit cell and an atomic aggregate [5]\*. c The hexagonal close-packed (hcp) crystal structure is shown as a reduced-sphere unit cell and an atomic aggregate [5]\*

in practice by the design engineer. A simple question remains: What are the practical ways one could use to limit the tendency for brittle failure of a structural material? And if embrittlement cannot be avoided, as often happens at extreme service conditions, what are the available testing methods that can provide accurate information on the limitations of a specific material?

#### 2.2.1 Elements of Fracture Mechanics

Before attempting to answer the above critical questions, it would be useful to introduce and put into perspective the following two concepts: (a) the stressintensity factor and (b) the fracture toughness. It is common knowledge that the materials used to build any structure are not perfect, since they contain cracks, sharp notches, and discontinuities of various kinds. These defects create stress concentrations within the material, increasing its tendency to failure. Therefore, the design engineer needs a tool that allows the quantitative determination of the allowable stress levels in such structures, so as to avoid fracture during service. This tool is the scientific discipline of Fracture Mechanics, which envisages the intensity of stress concentration as the *driving force* to failure, and the material's fracture toughness as the *resistance force* against failure [1].

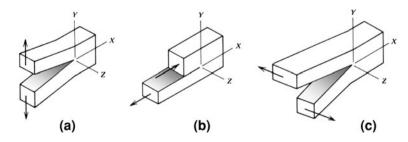

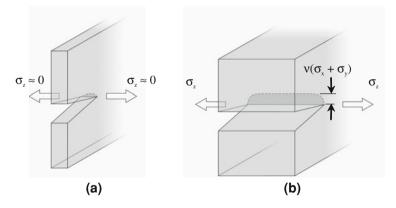

Depending on the mode of loading, the fracture of flaw-containing components may be described by a stress analysis based on principles of elasticity theory. Figure 2.3 illustrates the three major modes of loading, which are [1, 2]:

- 1. *Mode I*: the opening or tensile mode, where the crack surfaces move directly away from each other,

- 2. *Mode II*: the sliding or in-plane shear mode, where the crack surfaces slide over one another in a direction perpendicular to the crack leading edge, and

- 3. Mode III: the tearing or anti-plane shear mode, where the crack surfaces also move relative to one another, but in this case parallel to the crack leading edge. Since mode I loading is the most frequently encountered in structural applications involving cracked components, both the stress-intensity factor and the fracture toughness are defined with respect to that loading mode in the present text.

Fig. 2.3 The three basic loading modes: a Mode I, b Mode II, and c Mode III [1, 2]\*

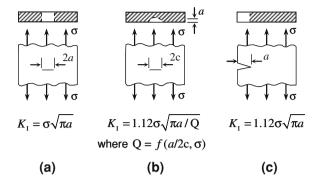

**Fig. 2.4** Equations relating the stress-intensity factor,  $K_I$ , with the stress,  $\sigma$ , and the crack size, a, for the following crack configurations: **a** through-thickness crack, **b** surface crack, and **c** edge crack. These equations describe the elastic-stress field in the vicinity of a crack tip inside a body subjected to tension [1]\*

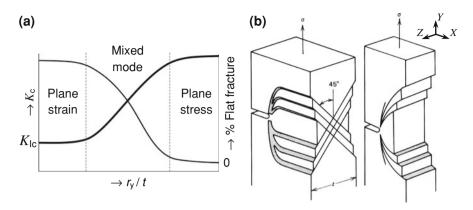

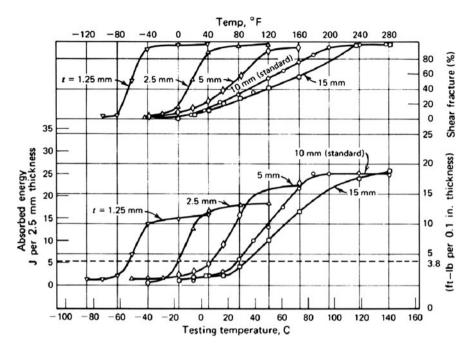

In linear-elastic fracture mechanics, the stress field ahead of a sharp crack subjected to mode I loading is characterised by the stress-intensity factor,  $K_{I}$ , which has units of MPa $\sqrt{m}$  or ksi $\sqrt{in}$ . [1]. This parameter is related to both the stress level,  $\sigma$ , and the flaw size, a. Figure 2.4 provides equations describing the elastic-stress field near the tip of cracks with different configurations, inside a body stressed in tension. In summary,  $K_I$  is affected by the specimen geometry, the applied load, as well as the size and shape of the flaw [1]. When the combination of  $\sigma$  and a results in a critical  $K_I$  value, unstable crack growth (related to brittle failure) occurs. This critical value of the stress-intensity factor at failure,  $K_{Ic}$ , is the so-called *fracture toughness*, and it is a material property [1]. The fracture toughness represents the resistance of a certain test specimen against crack propagation. It must be emphasised, however, that determining the fracture toughness of a structural material is not always an easy task, as the fracture toughness is influenced by the service temperature, loading rate, and degree of material constraint. Therefore, the  $K_{Ic}$  of a certain material can be determined for a specimen with a given thickness at a specified temperature and loading rate. In general, the fracture toughness decreases by decreasing the temperature, increasing the loading rate, and/or increasing the material thickness [1, 2]. Special reference will be made to each one of these factors later in the text, as they are also expected to affect the fracture behaviour of certain Pb-free solders.

#### 2.2.2 Metallurgical Aspects of Fracture Resistance

It has already been mentioned that high toughness demands the combination of strength and ductility. However, metallurgists take this concept one step further and strive for the production of structural materials that exhibit both high strength

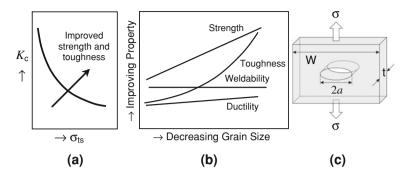

Fig. 2.5 a Inverse relation between the tensile strength,  $\sigma_{ts}$ , and the fracture toughness,  $K_c$ , of an alloy. Optimising the alloy properties would ideally result in a shift of the tensile strength-fracture toughness curve in the direction of the *arrow* [2]\*. **b** Grain size refinement results in a simultaneous improvement in the strength and the toughness of the alloy. Reduction in the grain size does not affect adversely the alloy's weldability or ductility [2]\*. **c** Through-thickness crack in a large plate subjected to a tensile stress  $\sigma$ . *W* is the plate width, t the plate thickness, and 2*a* the crack length [2]\*

and fracture toughness. This is asking for a lot, since the strengthening of a material happens almost invariably at the detriment of its fracture toughness, as shown in Fig. 2.5a. Still, there are ways to improve both the strength and the fracture toughness of a material [2]; these ways should also be considered for the improvement of the in-service performance of commercially available Pb-free solders. The simultaneous improvement in strength and toughness may be achieved in one of the following ways:

- 1. By modifying the alloy chemistry and melting/processing process to improve the toughness; this could, for example, happen by removing or neutralising certain undesirable elements that degrade the toughness,

- 2. By optimising the microstructure and phase distribution to maximise the toughness, and/or

- 3. By refining the microstructure, or in other words, by opting for finer grain sizes.

Point (3) is quite obvious for all materials, and its effect on strength, toughness, and weldability is graphically presented in Fig. 2.5b. In order to provide a better insight into the benefits of microstructural refinement, the following could be said: strengthening occurs because smaller grains are likely to contain smaller flaws; smaller inherent flaws imply the need of a greater stress to achieve failure.

In terms of equations, Griffith [1, 2] suggested that the stress required for failure is given by:

$$\sigma = \sqrt{\frac{2E\gamma_s}{\pi a}}$$

for plane-stress (biaxial stress) conditions (2.2)

and

$$\sigma = \sqrt{\frac{2E\gamma_s}{\pi a(1-v^2)}} \quad \text{for plane-strain (triaxial stress) conditions}$$

(2.3)

where *E* is the material's modulus of elasticity,  $\gamma_S$  is the specific energy of the surface created during fracture, 2*a* is the crack length, and *v* is the Poisson's ratio of the material. Obviously, the larger the size of the flaw/crack, the lower the stress required to fracture the material. A model crack may be visualised in Fig. 2.5c. With respect to the toughening of a single-phase material by grain refinement, one could think that the finer the grain size, the more often will a crack cross grain boundaries during its propagation. Since grain boundaries tend to decelerate or even stop cracks, the travelling crack will spend more energy to propagate in a finer-grained material than in a coarser-grained one. The higher the energy absorbed during fracture, the tougher the material.

Examples of improving the properties of Pb-free solders based on the suggestions made in points (1) and (2) include the addition of special retardants to avoid tin pest on tin-based (Sn-based) solder alloys (in relation to point 1), and/or the control of the size, shape, and acuity (i.e. sharpness) of the intermetallic (IMC) particles in the solder bulk (in relation to point 2). Reference to the last two examples will be made later in the text. Before moving to the next section, however, it would be useful to briefly underline the role of IMC particles in the in-service embrittlement of Pb-free solder alloys.

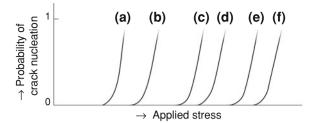

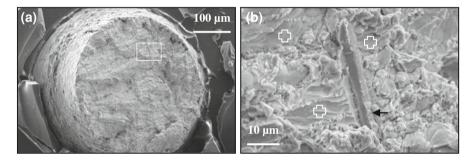

Intermetallics or intermetallic compounds (IMCs) are discrete chemical compounds made by the mixing, in a certain proportion, of two or more metals with each other or with non-metals [5, 7]. An example of a widely known intermetallic compound formed in steels is cementite ( $Fe_3C$ ). It is quite important to realise that the structure and properties of intermetallics are different from those of the constituent metals; for example, IMCs are characterised by enhanced atomic order and mixed (metallic and covalent/ionic) bonding. Moreover, their properties are a compromise between the typical properties of ceramics and those of metals: when compared to most metals, they exhibit higher hardness and refractoriness, together with poorer toughness and workability (and, hence, ductility). It has also been shown that the presence of brittle second-phase particles in an otherwise ductile matrix is a major cause of embrittlement [2]. Figure 2.6 illustrates this principle, showing that the probability of crack initiation at particles such as the IMCs in Pb-free solders is very high. The above indicates that the presence of IMCs in the bulk of Pb-free solder alloys is a major concern when it comes to the fracture behaviour of these alloys, as will be illustrated later in the text.

#### 2.2.3 Elements of Dislocation Theory

Dislocations are very important, especially for metals and metallic alloys, since they provide a mechanism for plastic deformation, which may be regarded as the

**Fig. 2.6** Probability as a function of the applied stress that one of the following microcrack formation mechanisms is active: [*a*] embrittled grain boundaries, [*b*] brittle second-phase particles, [*c*] twin–twin intersections, [*d*] twin–grain boundary intersections, [*e*] slip-induced grain boundary opening (e.g. at triple points), and [*f*] slip band-slip band intersections. From a study conducted on high-purity iron-containing carbides as brittle second-phase particles [2]\*

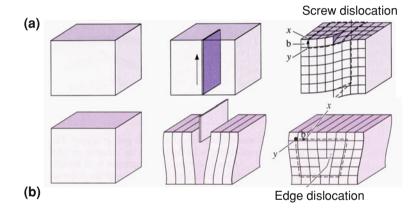

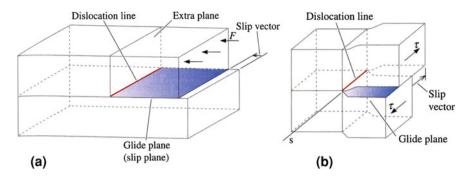

**Fig. 2.7 a** For the creation of a screw dislocation, the perfect crystal is cut and sheared one atom spacing; the screw dislocation is the line across which shearing occurs  $[7]^{\$}$ . **b** For the creation of an edge dislocation, the perfect crystal is cut and an extra plane of atoms is inserted; the edge dislocation is the bottom edge of the extra plane  $[7]^{\$}$ . In both types of dislocations, a Burgers vector (**b**) is required to close a loop of equal atom spacings around the dislocation. <sup>§</sup> From "The Science and Engineering of Materials", 5th edition, by Askeland and Phulé. © 2006 by Nelson. Reprinted with permission of Nelson, a division of Thomson Learning: www.tomsonrights.com. Fax: 800 730 2215. The meaning of symbol <sup>§</sup> is the same throughout this text

cumulative effect of the slip of numerous dislocations [7]. *Dislocations* are line imperfections in an otherwise perfect crystal, where they are usually introduced either during solidification or permanent (i.e. plastic) deformation [7]. There are three known types of dislocations: the screw dislocation, the edge dislocation, and the mixed dislocation. Figure 2.7 gives a visual impression of two of them: the screw dislocation and the edge dislocation.

*Slip* is the process by which a dislocation moves in a material, resulting in the deformation of this material [7]. Figure 2.8 illustrates the slip process for both an edge dislocation and a screw dislocation. Slip explains why the strength of a metal

**Fig. 2.8** Schematic representation of the slip line, slip plane, and slip (Burgers) vector for (**a**) an edge dislocation and (**b**) a screw dislocation [7]<sup>§</sup>

is much lower than the theoretical strength predicted from the metallic bond. In this sense, slip is responsible for the ductility and, therefore, the workability of metals. On the other hand, the presence of dislocations offers also the possibility of strengthening a certain metallic material by introducing obstacles (e.g. second-phase particles) that interfere with the dislocation motion [2, 8].

It has by now become clear that the movement of dislocations is a prerequisite for plastic deformation before fracture, and it should ideally occur even at extreme service conditions (e.g. low temperatures, high strain rates), if brittle failures were to be avoided. Unfortunately, the lattice resistance to dislocation movement changes with temperature, and this is the basis of the low-temperature embrittlement encountered in Sn-based Pb-free solders, which will be addressed later in the text. The resistance of a lattice to dislocation movement is expressed by the magnitude of the force required to move a dislocation through this lattice. This is known as the *Peierls–Nabarro force*, and the corresponding stress is the *Peierls–Nabarro stress* [2].

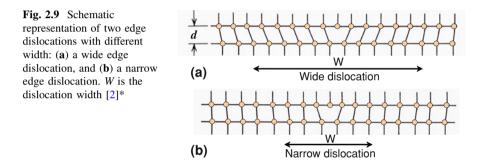

The magnitude of the Peierls–Nabarro stress decreases as the width of the dislocation, W, or the distance between similar planes, d, increases (Fig. 2.9). Since the interplanar spacing, d, increases with the planar atomic density, it is easier to have slip on close-packed planes. Moreover, the dislocation width, which

represents the distance over which the lattice is distorted due to the presence of the dislocation, is large when the bonding forces are spherical in distribution and act along the line between atomic centres. This type of bonding characterises the close-packed structures of fcc and hcp crystals. On the other hand, highly directional bonding forces, as in the case of bcc, ionic, or covalent crystals, result in narrow dislocations. Therefore, the Peierls–Nabarro stress is low in fcc and hcp crystals, moderate in bcc crystals, and large in ionic or covalent crystals (e.g. ceramic materials) [2].

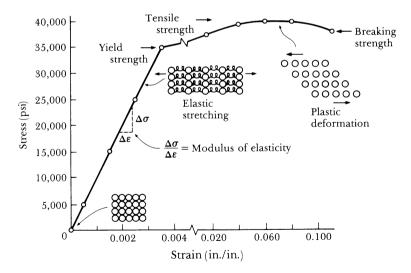

The Peierls–Nabarro stress is sensitive to the lattice thermal energy and, hence, to the ambient temperature [2]. Decreasing the temperature limits the thermal energy available for dislocation motion, which increases the Peierls–Nabarro stress, especially for crystals with a high starting Peierls–Nabarro stress (e.g. bcc). However, crystals with a negligible starting Peierls–Nabarro stress (e.g. fcc and hcp) experience little increase in their Peierls–Nabarro stress when the ambient temperature decreases. It is also quite important to realise that the temperature dependence of the Peierls–Nabarro stress is related to the temperature dependence of the yield strength of a material [2]. Before going deeper into the last phenomenon, it might be useful to introduce the yield strength and the (ultimate) tensile strength of a metallic material with the help of Fig. 2.10, which shows the stress–strain curve resulting from the tensile testing of an aluminium (Al) alloy to failure. Upon stress application in the elastic regime, the material deforms elastically, which means that the strain will be completely recovered as soon as the

**Fig. 2.10** The stress–strain curve resulting from the tensile testing of an Al alloy  $[9]^{\#}$ . <sup>#</sup> From "The Science and Engineering of Materials", 1st edition, by Askeland. © 1984 by Wadsworth, Inc. Reprinted with permission of Brooks/Cole, a division of Thomson Learning: www.tomsonrights.com. Fax: 800 730 2215. The meaning of symbol <sup>#</sup> is the same throughout this text

stress is withdrawn. The slope of the stress-strain curve in the elastic region is the material's modulus of elasticity or Young's modulus, E. As the applied stress increases, the material starts to deform both elastically and plastically. The critical stress value required to initiate plastic deformation is defined as the *elastic limit* of the material [3, 7]. In metallic materials, this is usually the stress required for dislocation motion or slip to be initiated. On the other hand, the stress level above which the relationship between stress and strain is not linear is the so-called proportional limit [3, 7]. In most materials, the elastic and proportional limits are quite close, but neither of them can be determined accurately since the measured values depend on the sensitivity of the equipment. Therefore, an offset strain value (typically, 0.002 or 0.2%) is defined, from which a line is drawn parallel to the linear portion of the stress-strain curve. The stress value corresponding to the intersection of this line and the stress-strain curve is the 0.2% offset yield strength or *yield strength* [3, 7]. At stresses higher than the yield strength, plastic deformation occurs. The stress corresponding to the highest applied force is the *tensile strength* of the tested material. In ductile materials, the tensile strength is the stress at which *necking* begins. Necking refers to the formation of an area in the tensile specimen that is locally much more deformed (i.e. thinner) than the rest of the specimen.

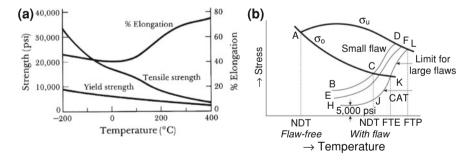

The fact that the temperature dependence of the Peierls–Nabarro stress is related to that of the yield strength is the reason why the yield strength of fcc metals like Al, copper (Cu), and austenitic stainless steel alloys has a limited temperature dependence [2, 4, 9]. Figure 2.11a shows the temperature dependence of the tensile properties of an Al alloy [9]. This plot shows that as the temperature decreases, both the yield and tensile strength of the Al alloy increase. However, the

**Fig. 2.11** a The effect of temperature on the tensile properties of an Al alloy  $[9]^{\#}$ . b The temperature dependence of the yield, tensile, and fracture strength (the latter is given by curves BCD, EF, and HJKL) of a steel containing flaws of various sizes. CAT is the crack-arrest temperature curve: it gives the stress required for the unstable propagation of a large flaw as a function of temperature; fracture does not occur at any point on the right of that curve. FTE is the fracture transition elastic temperature, i.e. the temperature above which elastic stresses cannot propagate a crack. Above FTP, which is the fracture transition plastic temperature, the material behaves as if it were flaw-free; this means that a crack (irrespective of its size) cannot propagate in an unstable manner [8]

yield strength increases less rapidly than the tensile strength, which allows the Al alloy to retain some of its ductility at low service temperatures. The reason for the not-so-steep increase in the yield strength with lowering the temperature is related to the limited temperature dependence of the Peierls–Nabarro stress of this alloy. Examples of other fcc metals that for the same reason remain ductile at low temperatures include nickel (Ni), lead (Pb), and silver (Ag) [4].

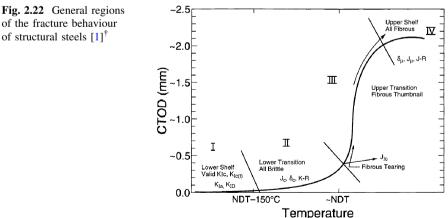

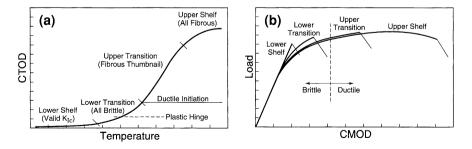

On the contrary, the Peierls-Nabarro stress in bcc metals like iron (Fe), chromium (Cr), molybdenum (Mo), tantalum (Ta), tungsten (W), and ferritic stainless steel alloys rises rapidly with decreasing temperature [2, 4, 9]. This happens due to the strong temperature dependence of the Peierls-Nabarro stress, which becomes a large part of the yield strength in the low-temperature regime [2]. Figure 2.11b shows the temperature dependence of the tensile properties of a ferritic stainless steel alloy [8]. This plot shows that as the temperature decreases, the yield strength,  $\sigma_{\alpha}$ , of the alloy increases faster than its tensile strength,  $\sigma_{\mu}$ . For an unnotched, flaw-free specimen, ductility is retained until a very low temperature, where  $\sigma_o = \sigma_\mu$  (point A). This temperature is known as the *nil ductility* temperature (NDT); at temperatures lower than the NDT, fracture becomes 100% brittle [1, 2, 8]. One may also see that the presence of a small flaw (a < 0.1 in.) raises substantially the NDT of the steel from point A (flaw-free) to point C; for that particular case, the NDT was observed to increase by  $\sim 200^{\circ}$ F, i.e. 110°C [8]! With materials like bcc metals, the presence of flaws/cracks/notches does not only influence the material's strength, but its toughness as well. The notch sensitivity of a material and the description of available testing methods to estimate it will be discussed in Sect. 2.3.

# 2.3 Impact Test: Work Principle and Interpretation of Results

The ability of a material to absorb energy in the presence of a sharp notch, often when subjected to impact, is known as *notch toughness* [1]. Materials may be divided into three categories based on their notch toughness [8]:

- 1. Low- and medium-strength fcc metals and most hcp metals exhibit very high notch toughness; these materials tend to fail invariably in a ductile manner.

- 2. High-strength materials ( $\sigma_o > E/150$ ) with very low notch toughness; these materials fail in a brittle manner even when the applied stress is in the elastic range. High-strength steels, aluminium, and titanium (Ti; hcp) alloys belong to this category.

- 3. Low- and medium-strength bcc metals, ceramics, beryllium (Be; hexagonal), and zinc (Zn; hcp) fail in a brittle manner at low temperatures and in a ductile manner at high temperatures. In other words, their notch toughness is temperature dependent. The transition from ductile to brittle fracture for the metals in this category occurs at 0.1–0.2 of their absolute melting temperature, Tm; for ceramics, this transition occurs between 0.5 and 0.7 Tm.

The *notch sensitivity* of a certain material may be evaluated by comparing the absorbed energies of notched and unnotched specimens during impact [2, 9]. Since notches are often present in structural materials (due to poor machining, fabrication, or design), knowing the notch toughness of the materials used in any structure is very useful for the design engineer. Moreover, since the same engineer is interested in the worst possible combination of service conditions that might lead to failure, experimental testing methods were devised that intentionally suppress the ability of the material to deform plastically.

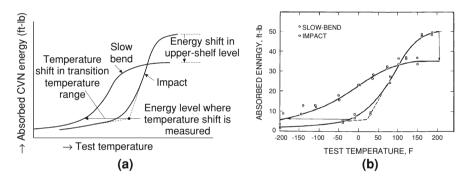

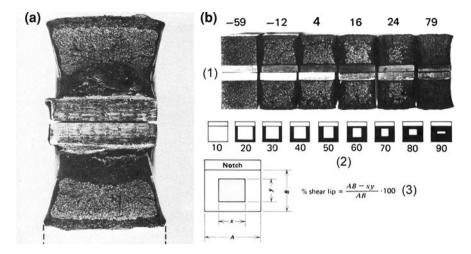

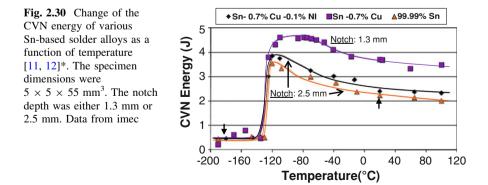

An example of such a test is the Charpy V-notch impact test, which (a) imposes high strain rates, and (b) creates a triaxial stress state by introducing a sharp notch to the test specimen. Furthermore, the Charpy V-notch (CVN) impact test can also be performed at low temperatures, limiting even further the ability of the test specimen to deform plastically. Figure 2.12 shows a Charpy impact test set-up, together with various possible test specimen configurations [9]. During testing, a heavy pendulum, starting at an elevation  $h_0$ , swings through its arc, strikes, and breaks the specimen, reaching a lower final elevation,  $h_f$ . Knowing the initial and final pendulum elevations allows the calculation of the potential energy difference. This difference is mainly the *impact energy* absorbed by the test specimen during fracture. For the Charpy test, this energy is expressed in joules (J) or foot-pounds (ft-lb). The ability of a material to withstand impact is often referred to as impact toughness; the impact toughness of a test specimen represents the energy absorbed during its fracture [7]. In this section, the factors affecting the impact toughness of a test specimen will be extensively addressed, so as to ensure (a) the correct evaluation of experimental results and (b) the understanding of the limitations of this testing method.

One could roughly divide the factors affecting impact toughness into (a) factors that are related with the service conditions and (b) factors that are related with the material microstructure. It is important to realise that the factors in these two categories are interlinked in more than one way. Examples of factors in the first category include temperature, loading/strain rate, and degree of material constraint; the response of a certain metal/alloy to these factors is largely determined

**Fig. 2.12** a The Charpy impact test set-up  $[9]^{\#}$ . b Typical test specimen configurations designed for Charpy impact testing  $[9]^{\#}$

by its crystal structure. For dense (i.e. non-porous) materials, factors belonging to the second category include the alloy composition as well as the volume fraction, size distribution and spacing of brittle second-phase particles, like the IMCs in Pb-free solders. At this point, one could also indicate that the volume fraction, size distribution, and spacing of second-phase particles are dictated by the alloy composition and the processing/service conditions experienced by the alloy. For example, the volume fraction of second-phase particles in an alloy is in principle defined by equilibrium thermodynamics. However, the size distribution and spacing of such precipitates is usually evolving in time, depending on the initial material microstructure (i.e. the microstructure at the end of processing) and the service conditions. The initial microstructure is greatly influenced by the chosen processing conditions, like cooling rate, temperature, and pressure; on the other hand, the service conditions are responsible for the growth and ripening of secondphase particles or the phase transformations that could take place in the material. For porous/cracked materials, the material response to impact is also dictated by the amount, spatial distribution, and orientation of material defects. Figure 2.13a illustrates the influence of the flaw size and flaw orientation on the probability of failure occurrence.

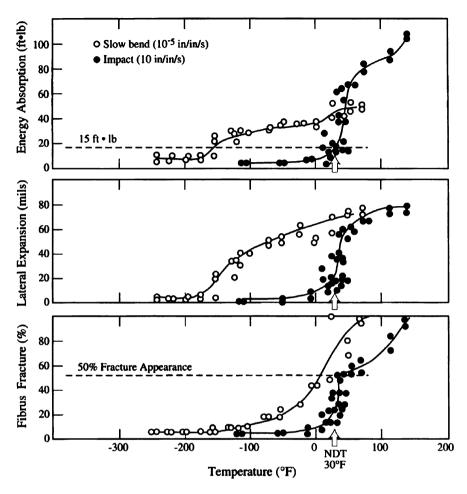

# 2.3.1 Temperature on Impact Toughness

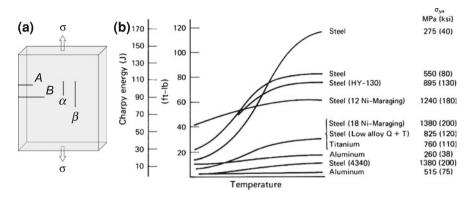

As mentioned in Sect. 2.2.3, the temperature dependence of the Peierls-Nabarro stress, i.e. the stress required to move a dislocation through a crystal lattice, is more pronounced in bcc metals than in fcc or hcp metals. Since the Peierls-Nabarro stress and the yield strength are interrelated, the yield strength of bcc metals depends on temperature more strongly than the yield strength of fcc or hcp metals. The relative faster increase in the yield strength with respect to the tensile strength upon cooling is the main reason for the low-temperature embrittlement of bcc metals. Figure 2.13b shows the Charpy impact energy of several structural materials as a function of temperature. Some of the materials in this figure exhibit low impact toughness at all temperatures (e.g. the 75-ksi yield strength Al), while others show a high level of impact toughness at all temperatures (e.g. the 180-ksi vield strength steel). As may be seen from the same figure, the impact energy of some materials (Al alloys and high-strength steels) does not change with temperature; these are fcc alloys. On the other hand, the impact energy of some materials (e.g. the 40-ksi yield strength steel) changes dramatically with temperature: these are bcc alloys. Embrittlement occurs around a temperature known as the ductile-to-brittle transition temperature (DBTT).

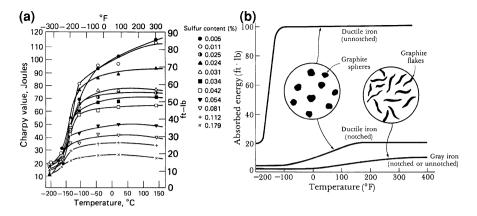

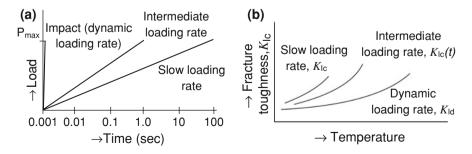

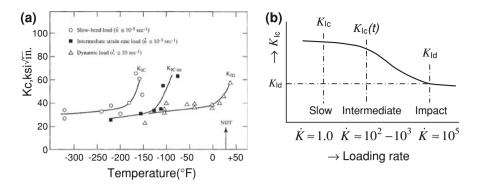

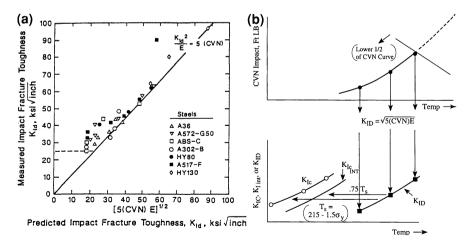

The exact location of DBTT on the temperature axis and the magnitude of embrittlement are affected by several factors that include the alloy composition, the amount, shape/sharpness, size and spatial distribution of brittle second-phase particles, the loading/strain rate, and the degree of material constraint. Figure 2.14a illustrates the change in the Charpy impact energy of steel as a

**Fig. 2.13** a Arbitrary cracks in a solid body subjected to tension; the body contains cracks *A*, *B*,  $\alpha$ , and  $\beta$ , where  $\alpha = A$  and  $\beta = B$ . Since cracks  $\alpha$  and  $\beta$  are parallel to the direction of stress, failure will occur in association with cracks *A* and *B*. The fact that A < B increases the probability of failure originating from crack B [2]\*. **b** Change of the Charpy impact energy of several engineering alloys with temperature [2] <sup>&</sup>. <sup>&</sup> From "Deformation and Fracture Mechanics of Engineering Materials", 4th edition, by Hertzberg. © 1996 by John Wiley and Sons, Inc. Reprinted with permission of John Wiley and Sons, Inc. The meaning of symbol <sup>&</sup> is the same throughout this text

function of its sulphur (S) content. The observed impact toughness change is attributed to the change in the volume fraction of sulphide inclusions in this steel. Figure 2.14b shows the effect of the shape and sharpness of graphite precipitates on the impact toughness of ferrous alloys: spherical precipitates are quite innocuous, while flake-like precipitates with sharp edges decrease the material's impact toughness. In fact, sharp and brittle second-phase particles, like several IMCs in Pb-free solders, act as *'internal notches'*, reducing the impact toughness of the otherwise ductile metallic matrix in which they have precipitated. These 'internal notches' play the role of stress concentrators inside the matrix material, facilitating the onset of brittle failure. Their impact on material properties is similar to the effect of external notches/cracks on the properties of notch-sensitive materials, like the ductile iron of Fig. 2.14b.

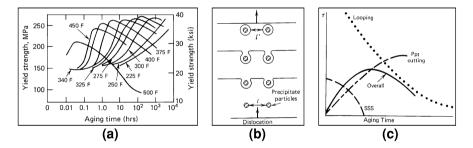

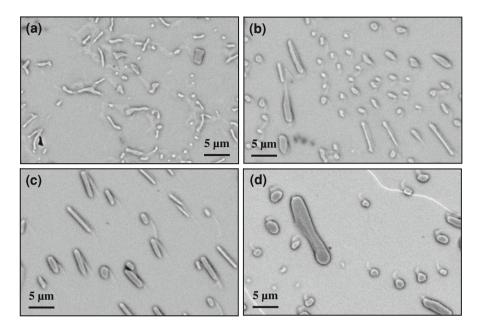

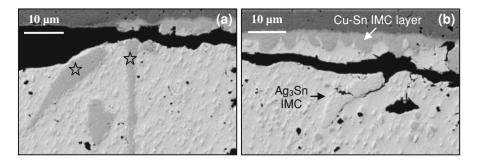

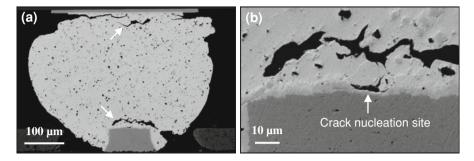

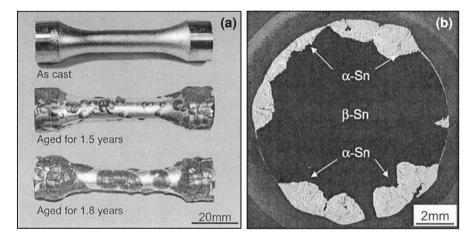

It has been mentioned more than once that the Peierls–Nabarro stress and the yield strength of a certain material are interrelated, and so are their temperature dependences. Since the Peierls–Nabarro stress expresses the resistance of a crystal lattice to dislocation motion, it would be interesting to see how the movement of dislocations is affected by the size and spatial distribution of second-phase particles. In general, second-phase particles in a metallic matrix are obstacles to dislocation motion [2]. After precipitation, the hardness and yield strength of the host alloy increases initially with time, but eventually decreases with prolonged annealing. This trend is demonstrated in Fig. 2.15a, which shows ageing curves of the 6061-T4 aluminium alloy [2]. These curves could be interpreted as follows: after solution treatment and quenching, the alloy is characterised by a maximum potential for solid solution strengthening, since most of the solute is present in the