Wolfgang E. Nagel Wolfgang V. Walter Wolfgang Lehner (Eds.)

# -NCS 4128

# Euro-Par 2006 Parallel Processing

12th International Euro-Par Conference Dresden, Germany, August/September 2006 Proceedings

# Lecture Notes in Computer Science 4128

Commenced Publication in 1973 Founding and Former Series Editors: Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

#### Editorial Board

David Hutchison Lancaster University, UK Takeo Kanade Carnegie Mellon University, Pittsburgh, PA, USA Josef Kittler University of Surrey, Guildford, UK Jon M. Kleinberg Cornell University, Ithaca, NY, USA Friedemann Mattern ETH Zurich, Switzerland John C. Mitchell Stanford University, CA, USA Moni Naor Weizmann Institute of Science, Rehovot, Israel Oscar Nierstrasz University of Bern, Switzerland C. Pandu Rangan Indian Institute of Technology, Madras, India Bernhard Steffen University of Dortmund, Germany Madhu Sudan Massachusetts Institute of Technology, MA, USA Demetri Terzopoulos University of California, Los Angeles, CA, USA Doug Tygar University of California, Berkeley, CA, USA Moshe Y. Vardi Rice University, Houston, TX, USA Gerhard Weikum Max-Planck Institute of Computer Science, Saarbruecken, Germany Wolfgang E. Nagel Wolfgang V. Walter Wolfgang Lehner (Eds.)

# Euro-Par 2006 Parallel Processing

12th International Euro-Par Conference Dresden, Germany, August 28 – September 1, 2006 Proceedings

#### Volume Editors

Wolfgang E. Nagel TU Dresden Zentrum für Informationsdienste und Hochleistungsrechnen Fakultät Informatik, Institut für Technische Informatik 01062 Dresden, Germany E-mail: wolfgang.nagel@tu-dresden.de

Wolfgang V. Walter TU Dresden Fakultät Mathematik und Naturwissenschaften Institut für Wissenschaftliches Rechnen 01062 Dresden, Germany E-mail: wolfgang.walter@tu-dresden.de

Wolfgang Lehner TU Dresden Fakultät Informatik, Institut für Systemarchitektur 01062 Dresden, Germany E-mail: wolfgang.lehner@tu-dresden.de

#### Library of Congress Control Number: 2006930999

#### CR Subject Classification (1998): C.1-4, D.1-4, F.1-3, G.1-2, H.2

LNCS Sublibrary: SL 1 - Theoretical Computer Science and General Issues

| ISSN    | 0302-9743                                             |

|---------|-------------------------------------------------------|

| ISBN-10 | 3-540-37783-2 Springer Berlin Heidelberg New York     |

| ISBN-13 | 978-3-540-37783-2 Springer Berlin Heidelberg New York |

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springer.com

© Springer-Verlag Berlin Heidelberg 2006 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 11823285 06/3142 5 4 3 2 1 0

# Preface

#### **Euro-Par Conference Series**

Euro-Par is an annual series of international conferences dedicated to the promotion and advancement of all aspects of parallel computing. The major themes can be divided into the broad categories of hardware, software, algorithms and applications for parallel computing. The objective of Euro-Par is to provide a forum within which to promote the development of parallel computing both as an industrial technique and an academic discipline, extending the frontier of both the state of the art and the state of the practice. This is particularly important at a time when parallel computing is undergoing strong and sustained development and experiencing real industrial take-up. The main audience for, and participants in, Euro-Par are researchers in academic departments, government laboratories and industrial organizations. Euro-Par's objective is to be the primary choice of such professionals for the presentation of new results in their specific fields of expertise. Euro-Par is also interested in applications that demonstrate the effectiveness of the main Euro-Par themes.

Previous Euro-Par conferences took place in Stockholm, Lyon, Passau, Southampton, Toulouse, Munich, Manchester, Paderborn, Klagenfurt, Pisa, and Lisbon. The next conference will take place in Rennes. The Euro-Par conference series is traditionally organized in cooperation with the International Federation for Information Processing (IFIP), the Association for Computer Machinery (ACM), and the Institute of Electrical and Electronics Engineers (IEEE) Computer Society, Technical Committee on Parallel Processing (TCPP). Euro-Par has a permanent website where its history and organization are described: http://www.europar.org.

#### Euro-Par 2006 in Dresden, Germany

Euro-Par 2006, the 12th conference in the Euro-Par series, was chiefly organized by the Center for Information Services and High Performance Computing (ZIH) in collaboration with the Department of Informatics and the Institute of Scientific Computing at the Technische Universität Dresden.

Three prominent workshops were collocated with the conference: the Core-Grid Workshop on Grid Middleware, the UNICORE Summit Workshop, and the Petascale Computational Biology and Bioinformatics Workshop. For the first time at a Euro-Par conference, real-time applications requiring high bandwidth were presented as part of a Grid Village exhibit complementing the Industrial Exhibition. A special Industrial Session was reserved within the main conference program for technical presentations by the exhibitors.

Euro-Par 2006 was able to attract three renowned invited speakers. Their talks highlighted some of the most recent trends:

- Dominik Marx (Theoretical Chemistry, Ruhr-Univ. Bochum): The Virtual Laboratory: Scientific Computing Beyond the Cutting Edge.

- Ajay K. Royyuru (Computational Biology Center, IBM T.J. Watson Research Center): Deep Computing in Biology: Challenges and Progress.

- Alistair Dunlop (OMII-Europe, the Open Middleware Infrastructure Institute, Univ. of Southampton): Integrating and Interoperability of Grid Infrastructures in OMII-Europe.

## Euro-Par 2006 Statistics

Compared with the traditional conference format, Euro-Par 2006 introduced two new topics — *High-Performance Bioinformatics* and *Embedded Parallel Systems* — for a total of 18 topics covering a large variety of aspects of parallel and distributed computing. Each topic was supervised by a committee of four: a global chair, a local chair, and two vice-chairs. The call for papers attracted a total of 290 submissions. For most of the submitted papers, at least three and often four individual review reports were collected. A total of 110 full papers were finally accepted, of which 5 received the special honor of distinguished paper. The acceptance rate was thus below 38 %. The submitting authors of accepted papers are from 26 countries, with the four main contributing countries — Germany, Spain, France and the USA — accounting for 67 accepted papers.

#### Acknowledgments

Euro-Par 2006 was made possible through the generous support and diligent work of many individuals and organizations. At the Technische Universität Dresden, the Center for Information Services and High Performance Computing (ZIH), the Department of Informatics, and the Institute of Scientific Computing were heavily involved in the organizational tasks, contributing their staff and their infrastructure.

Furthermore, a number of institutional and industrial sponsors made contributions and participated in the Industrial Exhibition and the Grid Village. Their names and logos appear on the Euro-Par 2006 website at http://www.tudresden.de/europar2006/. We gratefully acknowledge their support.

At the ZIH, Claudia Schmidt undoubtedly bore the brunt of the administrative and organizational chores, all the while keeping her good humor (and her senses), Stefan Pflüger did a superb job in organizing and setting up the Industrial Exhibition and the Grid Village, and Guido Juckeland took on the difficult task of assembling the present volume of proceedings. The organizers are greatly indebted to them and the numerous other helping hands who donated their valuable time and went to great lengths to make Euro-Par 2006 a success.

We are greatly indebted to José Cunha, the organizer of Euro-Par 2005 in Lisbon, who never failed to give us prompt advice regarding any organizational matters. We are also grateful to the members of the Euro-Par Steering Committee for their support. We owe special thanks to Christian Lengauer, chairman of the Steering Committee, who was always available to share with us his experience in the organization of Euro-Par, for giving us friendly advice, support, and encouragement. We also thank Luc Bougé, vice-chair, for his vision and contributions to improve Euro-Par conferences.

Specific thanks are due to the authors of all the submitted papers, the 72 members of the 18 topic committees, and the vast number of reviewers, for contributing to the success of this conference.

Last, but not least, we are grateful to Springer for agreeing to publish these proceedings, thus continuing a long and successful Euro-Par tradition.

It was a pleasure and an honor to host Euro-Par 2006 at the Technische Universität Dresden. We hope that we were able to make it a memorable event for all participants.

Dresden, June 2006

Wolfgang E. Nagel Wolfgang V. Walter Wolfgang Lehner

# Organization

# Euro-Par Steering Committee

#### Chair

| Christian Lengauer | University of Passau, Germany |

|--------------------|-------------------------------|

|                    |                               |

#### Vice-Chair

| Luc Bougé | ENS Cachan, France |

|-----------|--------------------|

|-----------|--------------------|

#### **European Representatives**

| José Cunha          | New University of Lisbon, Portugal       |

|---------------------|------------------------------------------|

| Marco Danelutto     | University of Pisa, Italy                |

| Rainer Feldmann     | University of Paderborn, Germany         |

| Christos Kaklamanis | Computer Technology Institute, Greece    |

| Paul Kelly          | Imperial College, UK                     |

| Harald Kosch        | University of Passau, Germany            |

| Thomas Ludwig       | University of Heidelberg, Germany        |

| Emilio Luque        | Universitat Autònoma de Barcelona, Spain |

| Luc Moreau          | University of Southampton, UK            |

| Rizos Sakellariou   | University of Manchester, UK             |

#### Non-European Representatives

| Jack Dongarra | University of Tennessee at Knoxville, USA |

|---------------|-------------------------------------------|

| Shinji Tomita | Kyoto University, Japan                   |

#### **Honorary Members**

| Ron Perrott          | Queen's University Belfast, UK            |

|----------------------|-------------------------------------------|

| Karl Dieter Reinartz | University of Erlangen-Nuremberg, Germany |

#### Observers

| Wolfgang E. Nagel    | Technische Universität Dresden, Germany |

|----------------------|-----------------------------------------|

| Anne-Marie Kermarrec | IRISA Rennes, France                    |

# Euro-Par 2006 Local Organization

Euro-Par 2006 was organized by the Center for Information Services and High Perfomance Computing (ZIH) of the Technische Universität Dresden.

#### **Conference Chairs**

| Wolfgang E. Nagel  | Center for Information Services and High<br>Performance Computing (ZIH) and Dept. of<br>Computer Science, Inst. for Computer<br>Engineering, Technische Universität Dresden |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wolfgang V. Walter | Dept. of Mathematics, Inst. for Scientific<br>Computing, Technische Universität Dresden                                                                                     |

| Wolfgang Lehner    | Dept. of Computer Science, Inst. for System<br>Architecture, Technische Universität<br>Dresden                                                                              |

#### General Organization

Claudia Schmidt

#### **Technical Support**

Kirsten Kern, Ronny Zschitzschmann

#### Grid Village, Exhibits

Dietmar Augustin, Stefan Pflüger

#### Proceedings

Guido Juckeland

#### Secretariat

Jenny Baumann

# Euro-Par 2006 Program Committee

#### **Topic 1: Support Tools and Environments**

| <b>Global Chair</b><br>Bronis R. de Supinski | Lawrence Livermore National Laboratory,<br>Center for Applied Scientific Computing,<br>Livermore, CA, USA |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| <b>Local Chair</b>                           | Leibniz-Rechenzentrum, High Performance                                                                   |

| Matthias Brehm                               | Computing Group, Munich, Germany                                                                          |

| Vice Chairs    |                                       |

|----------------|---------------------------------------|

| Tomas Margalef | Univ. Autònoma de Barcelona, Computer |

|                | Architecture and Operating            |

|                | Systems Dept., Barcelona, Spain       |

| Luiz DeRose    | Cray Inc., USA                        |

#### **Topic 2: Performance Prediction and Evaluation**

#### **Global Chair**

| Jesús Labarta  | Technical University of Catalunya (UPC),<br>Barcelona Supercomputing Center (BSC),<br>Barcelona, Spain |

|----------------|--------------------------------------------------------------------------------------------------------|

| Local Chair    |                                                                                                        |

| Bernd Mohr     | Forschungszentrum Jülich, ZAM, Jülich,<br>Germany                                                      |

| Vice Chairs    |                                                                                                        |

| Allan Snavely  | San Diego Supercomputer Center, University of<br>California, San Diego, USA                            |

| Jeffrey Vetter | Oak Ridge National Laboratory, Oak Ridge,<br>Tennessee, USA                                            |

#### **Topic 3: Scheduling and Load Balancing**

| Global Chair       |                                                                                                         |

|--------------------|---------------------------------------------------------------------------------------------------------|

| Michael A. Bender  | State University of New York at Stony Brook,<br>Department of Computer Science, Stony<br>Brook, NY, USA |

| Local Chair        |                                                                                                         |

| Uwe Schwiegelshohn | University Dortmund, Robotics Research<br>Institute, Dortmund, Germany                                  |

| Vice Chairs        |                                                                                                         |

| Dror Feitelson     | The Hebrew University, School of Computer<br>Science and Engineering, Jerusalem, Israel                 |

| Allan Gottlieb     | New York University, Computer Science<br>Department, New York, NY, USA                                  |

# **Topic 4: Compilers for High Performance**

| Global Chair  |                                              |

|---------------|----------------------------------------------|

| William Jalby | University of Versailles Saint Quentin ARPA, |

|               | France                                       |

#### Local Chair

| Oscar Plata     | University of Malaga, Department of Computer<br>Architecture, Malaga, Spain |

|-----------------|-----------------------------------------------------------------------------|

| Vice Chairs     |                                                                             |

| Barbara Chapman | University of Houston, Department of<br>Computer Science, Houston, USA      |

| Paul Kelly      | Imperial College London, Department of<br>Computing, London, UK             |

#### Topic 5: Parallel and Distributed Databases, Data Mining and Knowledge Discovery

| <b>Global Chair</b><br>Patrick Valduriez | INRIA and LINA, Nantes, France                                                                |

|------------------------------------------|-----------------------------------------------------------------------------------------------|

| Local Chair                              |                                                                                               |

| Wolfgang Lehner                          | TU Dresden, Dept. of Computer Science,<br>Dresden, Germany                                    |

| Vice Chairs                              |                                                                                               |

| Domenico Talia                           | DEIS, University of Calabria, Rende CS, Italy                                                 |

| Paul Watson                              | University of Newcastle Upon Tyne, School of<br>Computing Science, Newcastle Upon<br>Tyne, UK |

# Topic 6: Grid and Cluster Computing: Models, Middleware and Architectures

#### **Global Chair** Domenico Laforenza Istituto di Scienza e Tecnologie dell'Informazione (ISTI-CNR), Pisa, Italy Local Chair Alexander Reinefeld Zuse Institute Berlin, Berlin, Germany Vice Chairs Dieter Kranzlmüller Johannes Kepler Universität Linz, GUP -Institute of Graphics and Parallel Processing, Linz, Austria Luc Moreau University of Southampton, School of Electronics & Computer Science, Southampton, UK

| <b>Global Chair</b><br>Eduard Ayguade | Barcelona Supercomputing Center (BSC),<br>Technical University of Catalunya (UPC),<br>Spain |

|---------------------------------------|---------------------------------------------------------------------------------------------|

| <b>Local Chair</b><br>Wolfgang Karl   | Universität Karlsruhe (TH), Institut für<br>Technische Informatik, Karlsruhe, Germany       |

| Vice Chairs                           |                                                                                             |

| Koen De Bosschere                     | Ghent University, ELIS Department, Ghent,<br>Belgium                                        |

| Jean-François Collard                 | Hewlett-Packard Laboratories, Palo Alto, CA, USA                                            |

#### Topic 7: Parallel Computer Architecure and Instruction-Level Parallelism

#### **Topic 8: Distributed Systems and Algorithms**

| Global Chair         |                                                                             |

|----------------------|-----------------------------------------------------------------------------|

| Andrzej M. Goscinski | Deakin University, School of Information<br>Technology, Victoria, Australia |

| Local Chair          |                                                                             |

| Gudula Rünger        | TU Chemnitz, Dept. of Computer Science,<br>Chemnitz, Germany                |

| Vice Chairs          |                                                                             |

| Christine Morin      | Campus universitaire de Beaulieu, IRISA / INRIA, France                     |

| Edgar Gabriel        | University of Houston, Computer Science<br>Department, Houston, TX, USA     |

#### Topic 9: Parallel Programming: Models, Methods, and Languages

| Global Chair    |                                                                                                                            |

|-----------------|----------------------------------------------------------------------------------------------------------------------------|

| José C. Cunha   | New University of Lisbon, Faculty of Sciences<br>and Technology, Department of Informatics,<br>Monte de Caparica, Portugal |

| Local Chair     |                                                                                                                            |

| Sergei Gorlatch | TU Berlin, Faculty of Electrical Engineering<br>and Computer Science Berlin, Germany                                       |

| Vice Chairs                                           |                                                                                                           |  |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--|

| Daniel Quinlan                                        | Lawrence Livermore National Laboratory,<br>Center for Applied Scientific Computing,<br>Livermore, CA, USA |  |

| Peter H. Welch                                        | University of Kent, Computing Laboratory,<br>Kent, UK                                                     |  |

| Topic 10: Parallel Numeric                            | cal Algorithms                                                                                            |  |

| Global Chair                                          |                                                                                                           |  |

| Michel Cosnard                                        | INRIA & Université de Nice - Sophia Antipolis,<br>France                                                  |  |

| Local Chair                                           |                                                                                                           |  |

| Hans-Joachim Bungartz                                 | TU München, Dept. of Computer Science,<br>Munich, Germany                                                 |  |

| Vice Chairs                                           |                                                                                                           |  |

| Efstratios Gallopoulos                                | University of Patras, Dept. of Computer<br>Engineering & Informatics, Patras, Greece                      |  |

| Yousef Saad                                           | University of Minnesota, Dept. of Computer<br>Science and Engineering, Minneapolis, USA                   |  |

| Topic 11: Distributed and High-Performance Multimedia |                                                                                                           |  |

| Global Chair                                          |                                                                                                           |  |

| Geoff Coulson                                         | Lancaster University, Computing Department,<br>Lancaster, UK                                              |  |

| Local Chair                                           |                                                                                                           |  |

| Harald Kosch                                          | University of Passau, Department of<br>Mathematics and Informatics, Passau,<br>Germany                    |  |

| Vice Chairs                                           |                                                                                                           |  |

| Frank Seinstra                                        | University of Amsterdam, Intelligent Systems<br>Lab Amsterdam ISLA, Amsterdam,<br>The Netherlands         |  |

| Odej Kao                                              | University of Paderborn, Dept. of Computer<br>Science, Paderborn, Germany                                 |  |

| Topic 12: Theory and Algo                             | orithms for Parallel Computation                                                                          |  |

| Global Chair                                          |                                                                                                           |  |

| Giobai chan   |                                       |

|---------------|---------------------------------------|

| Danny Krizanc | Wesleyan University, Mathematics and  |

|               | Computer Science, Middletown, CT, USA |

#### Local Chair

| Michael Kaufmann    | University of Tuebingen, Wilhelm Schickard<br>Institute of Informatics, Tuebingen,<br>Germany |

|---------------------|-----------------------------------------------------------------------------------------------|

| Vice Chairs         |                                                                                               |

| Pierre Fraigniaud   | CNRS, LRI, University of Paris Sud, Paris,<br>France                                          |

| Christos Zaroliagis | CTI, and Dept. of Computer Eng. &<br>Informatics, University of Patras, Patras,<br>Greece     |

#### Topic 13: Routing and Communication in Interconnection Networks

| Global Chair     |                                                                           |

|------------------|---------------------------------------------------------------------------|

| Jose A. Gregorio | University of Cantabria, Computer Architecture<br>Group, Santander, Spain |

| Local Chair      |                                                                           |

| Bettina Schnor   | University Potsdam, Dept. of Computer                                     |

|                  | Science, Potsdam, Germany                                                 |

| Vice Chairs      |                                                                           |

| Angelos Bilas    | ICS-FORTH & University of Crete, Greece                                   |

| Olav Lysne       | University of Oslo and Simula Research                                    |

|                  | Laboratory, Lysaker, Norway                                               |

#### Topic 14: Mobile and Ubiquitous Computing

| Johannes Kepler University Linz, Dept. of<br>Pervasive Computing, Linz, Austria |

|---------------------------------------------------------------------------------|

|                                                                                 |

| TU Dresden, Dept. of Computer Science,<br>Dresden, Germany                      |

|                                                                                 |

| University of Pisa, Computer Science<br>Department, Pisa, Italy                 |

| INRIA-Rocquencourt, Domaine de<br>Voluceau,Rocquencourt, France                 |

|                                                                                 |

#### Topic 15: Peer-to-Peer and Web Computing

| Global Chair                                                  |                                                                                    |

|---------------------------------------------------------------|------------------------------------------------------------------------------------|

| Henrique J. Domingos                                          | New University of Lisbon, Department of<br>Informatics, Caparica, Lisbon, Portugal |

| Local Chair                                                   |                                                                                    |

| Anne-Marie Kermarrec                                          | INRIA/IRISA, Campus Universitaire de<br>Beaulieu, Rennes, France                   |

| Vice Chairs                                                   |                                                                                    |

| Pascal Felber                                                 | University of Neuchâtel, Department of<br>Computer Science, Switzerland            |

| Márk Jelasity                                                 | Dept. of Computer Science, University of<br>Bologna, Bologna, Italy                |

| Topic 16: Applications of High-Performance and Grid Computing |                                                                                    |

| Global Chair                                                  |                                                                                    |

| Simon J. Cox                                                  | University of Southampton, School of<br>Engineering Science, Southamton, UK        |

#### Local Chair

Thomas Lippert

#### Vice Chairs

| Giovanni Erbacci | CINECA, High Performance Systems |

|------------------|----------------------------------|

|                  | Department, Bologna, Italy       |

| Denis Trystram   | ID-IMAG, Grenoble, France        |

Research Center Juelich, Central Institute for Applied Mathematics, Juelich, Germany

#### **Topic 17: High-Performance Bioinformatics**

| Global Chair<br>Craig A. Stewart | Indiana University, University Information<br>Technology Services, Indiana, USA |

|----------------------------------|---------------------------------------------------------------------------------|

| Local Chair<br>Michael Schroeder | TU Dresden, Biotec, Dresden, Germany                                            |

| Vice Chairs                      |                                                                                 |

| Concettina Guerra                | University of Padova, Padova, Italy, and<br>Georgia Tech, Atlanta, USA          |

| Konagaya Akihiko                 | Riken Genomic Sciences Center, Yokohama<br>City, Japan                          |

## Topic 18: Embedded Parallel Systems

| Global Chair       |                                                                                                    |

|--------------------|----------------------------------------------------------------------------------------------------|

| Stefanos Kaxiras   | University of Patras Department of Electrical<br>and Computational Engineering, Patras,<br>Greece  |

| Local Chair        |                                                                                                    |

| Jürgen Teich       | University of Erlangen-Nuremberg, Dept. of<br>Computer Science, Erlangen, Germany                  |

| Vice Chairs        |                                                                                                    |

| Toomas Plaks       | South Bank University, School of Computing,<br>Information, Systems and Mathematics,<br>London, UK |

| Krisztian Flautner | ARM Ltd.                                                                                           |

# Euro-Par 2006 Referees

Not including members of the Program and Steering Committees.

| Pablo Abad                                                                       | E. Bampis                                                                                                       |

|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| J. H. Abawajy                                                                    | Cyril Banino-Rokkones                                                                                           |

| Maha Abdallah                                                                    | Francoise Baude                                                                                                 |

| Ana Paula Afonso                                                                 | Oliver Beaumount                                                                                                |

| Adnan Agbaria                                                                    | Simon Becher                                                                                                    |

| Marco Aldinucci                                                                  | Christian Becker                                                                                                |

| Pinar Alper                                                                      | Olav Beckmann                                                                                                   |

| Martin Alt                                                                       | Andrzej Bednarski                                                                                               |

| Patrick Amestoy                                                                  | Ramon Beivide                                                                                                   |

| Emmanuelle Anceaume                                                              | Domingo Benítez                                                                                                 |

| Peter Andras                                                                     | Petra Berenbrink                                                                                                |

| Artur Andrzejak                                                                  | Martin Bernreuther                                                                                              |

| Eric Angel                                                                       | Marin Bertier                                                                                                   |

| George Apostolopoulos                                                            | Carlo Bertolli                                                                                                  |

| Shawki Areibi<br>Masanori Arita                                                  | Kristof Beyls                                                                                                   |

| Kubilay Atasu                                                                    | Christoph Biardzki<br>Florent Blachot                                                                           |

| David A. Bader<br>Michael Bader<br>Rosa M. Badia<br>R. Badrinath<br>Arati Baliga | Lars Ailo Bongo<br>Markus Borschbach<br>Mireille Bossy<br>Jacob Bower<br>Andrea Bracciali<br>Luis Diego Briceno |

Mats Brorsson Ashley Brown Ulrich Bruening Marian Bubak Rainer Buchty Marzia Buscemi Yann Busnel **Oiong** Cai Luis Caires Rui Camacho Blanca Caminero Mario Cannataro Mauro Caporuscio Ioannis Caragiannis Franco Alberto Cardilli Roberto Speicys Cardoso Denis Caromel Laura Carrington Carmen Carrion Antonio Caruso Carlo Cavazzoni Eduardo César Eugenio Cesario Damien Charlet Guillaume Chazarain Zheng Chen Nikolaos Chrysos Tarik Cicic Marcelo Cintra Giovanni Ciriello Antonio Cisternino Peter Clayton Diego Colombo John Colguhoun Matteo Comin Carmela Comito Antonio Congiusta George A. Constantinides Massimo Coppola Jav Cornwall Vitor Santos Costa Adrian Cristal

Marco Danelutto Karen Devine Robert Dew Erik D'Hollander Marios D. Dikaiakos Robert Dimond Gero Dittmann Ramon Doallo Mario Döller Henrique Domingos Andreas Doms Rubing Duan Sergio Duarte Vitor Duarte Jose Duato Jan Dünnweber Pierre-Francois Dutot

Lieven Eeckhout Pål Engelstad Dick Epema Jocelyne Erhel Yoav Etsion Stijn Eyerman

Thomas Fahringer Weijian Fang Paolo Ferragina Brigid Ferrari Rainer Fischer José Flich Dimitris Fotakis Damien Fournier Carsten Franke Manoj Franklin Manel Fredj C. F. Freytag Holger Froening K. Fürlinger

Giulio Galante Luis Garcés-Erice Claudio Garutti Thierry Gautier Markus Geimer Ingolf Geist Cecile Germain-Renaud Michael Gerndt

Vladimir Getov Stein Gjessing Brighten Godfrey Roberto Gori Anastasios Gounaris Paul Grace Xavier Granier Phil Greenwood Dan Grigoras Laura Grigori Paul Groth Roberto Guanciale Mitchell Gusat Eladio Gutierrez Pål Halvorsen Frank Hannig Audun Fosselie Hansen Laurent Hascoet Jiahua He Manfred Hechinger Frank Heller Jörg Henkel Pascal Henon Andreas Henschel Wim H. Hesselink Elisa Heymann Günther Höbling Mikael Hoegqvist J. Hofer Bo Hong Thomas Huckle Danny Hughes Sascha Hunold Felix Hupfeld Hitoshi Iba Liviu Iftode

David Janovy Mohamed Jemni Morris Jette Sheng Jiang Josep Jorba

Peter Kacsuk Marcus Kaiser Helen Karatza Sven Karlsson Darren J. Kerbyson Arie Keren Omid Khalili Thilo Kielmann Andv King Dirk Koch Spyros Kontogiannis Pierre Kuonen Amund Kvalbein Oren Laadan **Tobias Langhammer** Stéphane Lanteri Isabelle Guérin Lassous Gregor von Laszewski Michael Laurenzano Mario Lauria Cynthia Bailey Lee Sang Ik Lee Arnaud Legrand Michael H. Leitner Joachim Lepping Jean-Yves L`Excellent Frank Li Hui Li Keqin Li Zhongze Li Stefan Liske Jinshan Liu Angel Llano Josep Llosa Luis Lopes Phillip Lord Joao Lourenco Andre Luckow Scott MacLachlan Amine Mahjoub

Amine Mahjoub Paolo Malfetti Andrew Maloney Anirban Mandal Paolo Manghi Manolis Marazakis Annalisa Marsico Maxime Martinasso Tsutomu Maruyama Gaia Maselli Carlo Mastroianni Ludek Matvska John M. May Michael O. McCracken Sallv McKee Pedro Medeiros Miriam Mehl Michael Mellor **Bafael** Menendez Andre Merzky Michael Messig Norbert Meyer Klaus Meyer-Wegener Alessio Micheli Jose Miguel-Alonso Simon Miles Sonia Ben Mokhtar Burkhard Monien Aad van Moorsel Anna Moraiko Jose Moreira Francesco Moscato Andreas Moshovos Achour Mostefaoui Athanasios Mouchtaris Irene Moulitsas Gregory Mounie Juan Carlos Moure Gero Muehl Jens Müller Bruno Müller-Clostermann **Balf-Peter** Mundani Steven Munroe

Francesco Nidito Nils Agne Nordbotten

Adam J. Oliner Catherine Olschanowsky Salvatore Orlando Motonori Ota

Esther Pacitti Vijay S. Pai D. K. Panda **Evaggelos** Papapetrou Alexander Papaspyrou Nikos Parlavantzas Fanny Pascual David J. Pearce Johnatan Pecero Sanchez Miquel Pericas Panos Periorellis Kathrin Peter Stefan Petri Antonio Pinizzotto Steven Plimpton Eleftherios Polychronopoulos Francesco Potorti Nuno Preguica Giuseppe Prencipe Thierry Priol Valentin Puente Diego Puppin

Jun Qin

Rolf Rabenseifner Bruno Raffin Omer F. Rana Thomas Rauber Pierre-Guillaume Raverdy Sebastian Richly Fco. Javier Ridruejo Andreas Riener Louis Rilling Etienne Riviere Yves Robert Thomas Roeblitz Jean Roman Marie-Christine Rousset Sean Rul

Francoise Sailhan Rizos Sakellariou Oliverio J. Santana Eike Schallehn Thomas Scheffler Maraike Schellmann

**Olaf Schenk** Isaac D. Scherson Enrico Schiattarella Florian Schintke Thomas Schlichter Bertil Schmidt Lars Schneidenbach Anke Schneidewind Thorsten Schuett Andreas S. Schulz Martin Schulz Frank Olaf Sem-Jacobsen Miquel A. Senar H. J. Siegel Fernando Silva Fabrizio Silvestri Bernd Simeon Brett Sinclair Vasilios Siris Garry Smith Jim Smith Peter Sobe Angela C. Sodan Thomas Sødring Masha Sosonkina Paul Spirakis Parthasarathy Srinivasan G. S. Stiles Heinz Stockinger Achim Streit Martin Streubühr Jaspal Subhlok Remo Suppi F. Suter Bjorn De Sutter Duane Szafron

Andrea Tagarelli Victor Tan Jie Tao Christian Tenllado J. Thiyagalingam Fernando Tinetti Nicola Tonellotto Paolo Trunfio George Tsaggouris Konstantinos Tserpes Giovanni Turi Enrique Vallejo Fernando Vallejo Frederik Vandeputte Hans Vandierendonck Dora Varvarigou Luis Veiga Pierangelo Veltri Salvatore Venticinque K. V. Viswanathan Frédéric Vivien Thomas Wächter Marcel Waldvogel Chris Walshaw Bin Wang Rolf Wanka Tan Tin Wee Jonathan Weinberg Matthias Werner Stefan Wesner Sebastian Winkel Christoph Winter Felix Wolf Adam K.L. Wong Brian J.N. Wylie

Polychronis Xekalakis Gaogang Xie Cheng-Zhong Xu

Ramin Yahyapour Yoshiki Yamaguchi Robert K. Yates Han Yu

Serafeim Zanikolas Apostolos Zarras Rong Zheng Yunkai Zhou Fujun Zhu Wolfgang Ziegler Stefan Zimmer Wolf Zimmermann Martina Zitterbart

# Table of Contents

# **Topic 1: Support Tools and Environments**

| Introduction                                                                                                                                                  | 1  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Bronis R. de Supinski, Matthias Brehm, Luiz DeRose,<br>Tomás Margalef (Topic Chairs)                                                                          |    |

| IOAgent: A Parallel I/O Workload Generator<br>Sergio Gómez-Villamor, Victor Muntés-Mulero,<br>Marta Pérez-Casany, John Tran, Steve Rees, Josep-L. Larriba-Pey | 3  |

| TDP_SHELL: An Interoperability Framework for Resource Management<br>Systems and Run-Time Monitoring Tools<br>Vicente Ivars, Ana Cortes, Miquel A. Senar       | 15 |

| Supporting Cache Locality Optimization with a Toolset<br>Jie Tao, Wolfgang Karl                                                                               | 25 |

| Model-Based Performance Diagnosis of Master-Worker Parallel<br>Computations<br>Li Li, Allen D. Malony                                                         | 35 |

| Specification of Inefficiency Patterns for MPI-2 One-Sided<br>Communication                                                                                   | 47 |

# **Topic 2: Performance Prediction and Evaluation**

| Introduction<br>Jesús Labarta, Bernd Mohr, Allan Snavely, Jeffrey Vetter<br>(Topic Chairs)                                                                                              | 63 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Hierarchical Model Validation of Symbolic Performance Models of<br>Scientific Kernels                                                                                                   | 65 |

| Tuning Application in a Multi-cluster Environment<br>Eduardo Argollo, Adriana Gaudiani, Dolores Rexachs,<br>Emilio Luque                                                                | 78 |

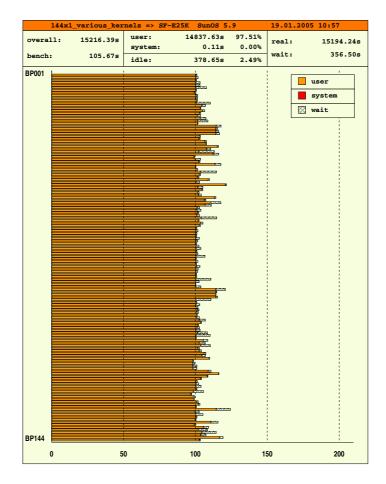

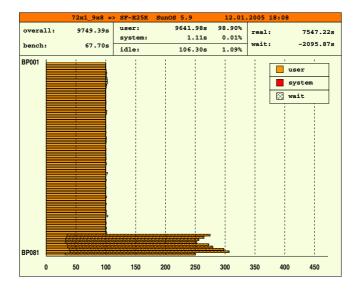

| Analyzing the Interaction of OpenMP Programs Within<br>Multiprogramming Environments on a Sun Fire E25K System<br>with PARbench<br><i>Rick Janda, Wolfgang E. Nagel, Bernd Trenkler</i> | 89 |

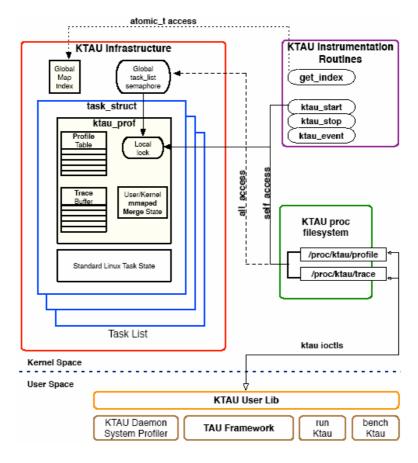

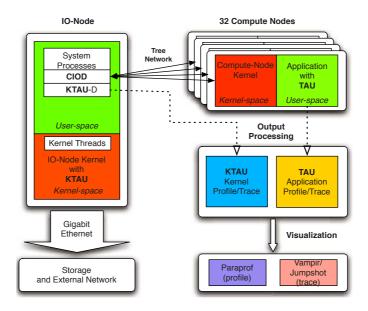

| Early Experiences with KTAU on the IBM BG/L<br>Aroon Nataraj, Allen D. Malony, Alan Morris, Sameer Shende                                                                                 | 99  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| PAM-SoC: A Toolchain for Predicting MPSoC Performance<br>Ana Lucia Varbanescu, Henk Sips, Arjan van Gemund                                                                                | 111 |

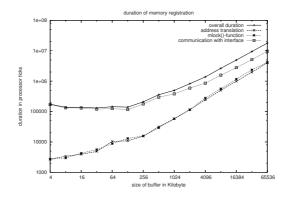

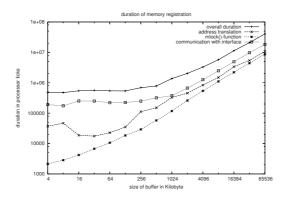

| Analysis of the Memory Registration Process in the Mellanox<br>InfiniBand Software Stack<br>Frank Mietke, Robert Rex, Robert Baumgartl, Torsten Mehlan,<br>Torsten Hoefler, Wolfgang Rehm | 124 |

| Optimization of Dense Matrix Multiplication on IBM Cyclops-64:<br>Challenges and Experiences                                                                                              | 134 |

| Optimizing OpenMP Parallelized DGEMM Calls on SGI Altix 3700<br>Daniel Hackenberg, Robert Schöne, Wolfgang E. Nagel,                                                                      | 145 |

#### Stefan Pflüger

# **Topic 3: Scheduling and Load Balancing**

| Introduction<br>Michael Bender, Dror Feitelson, Allan Gottlieb, Uwe Schwiegelshohn<br>(Topic Chairs)                           | 155 |

|--------------------------------------------------------------------------------------------------------------------------------|-----|

| The Price of Approximate Stability for Scheduling Selfish Tasks on<br>Two Links<br>Eric Angel, Evripidis Bampis, Fanny Pascual | 157 |

| Master-Slave Tasking on Asymmetric Networks<br>Cyril Banino-Rokkones, Olivier Beaumont, Lasse Natvig                           | 167 |

| Using On-the-Fly Simulation for Estimating the Turnaround Time<br>on Non-dedicated Clusters                                    | 177 |

| An Adaptive Scheduling Method for Grid Computing<br>Salah-Salim Boutammine, Daniel Millot, Christian Parrot                    | 188 |

| On the Placement of Reservations into Job Schedules<br>Thomas Röblitz, Krzysztof Rzadca                                        | 198 |

| A Practical Approach of Diffusion Load Balancing Algorithms<br>Emmanuel Jeannot, Flavien Vernier                               | 211 |

| Fast Diffusion Load Balancing Algorithms on Torus Graphs<br>Gregory Karagiorgos, Nikolaos M. Missirlis, Filippos Tzaferis      | 222 |

| A Parallel Shape Optimizing Load Balancer<br>Henning Meyerhenke, Stefan Schamberger                                                                                        | 232 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Improvement of the Efficiency of Genetic Algorithms for Scalable<br>Parallel Graph Partitioning in a Multi-level Framework<br><i>Cédric Chevalier, François Pellegrini</i> | 243 |

| Probablistic Self-Scheduling<br>Milind Girkar, Arun Kejariwal, Xinmin Tian,<br>Hideki Saito, Alexandru Nicolau, Alexander Veidenbaum,<br>Constantine Polychronopoulos      | 253 |

| Data Sharing Conscious Scheduling for Multi-threaded<br>Applications on SMP Machines<br>Shlomit S. Pinter, Marcel Zalmanovici                                              | 265 |

## **Topic 4: Compilers for High Performance**

| Introduction<br>William Jalby, Oscar Plata, Barbara Chapman, Paul Kelly<br>(Topic Chairs)                                  | 277 |

|----------------------------------------------------------------------------------------------------------------------------|-----|

| Compiler Technology for Blue Gene Systems<br>Stefan Kral, Markus Triska, Christoph W. Ueberhuber                           | 279 |

| SCAN: A Heuristic for Near-Optimal Software Pipelining<br>Florent Blachot, Benoît Dupont de Dinechin, Guillaume Huard      | 289 |

| Code Generation for STA Architecture<br>J. Guo, T. Limberg, E. Matus, B. Mennenga, R. Klemm,<br>G. Fettweis                | 299 |

| Multi-dimensional Kernel Generation for Loop Nest Software<br>Pipelining<br>Alban Douillet, Hongbo Rong, Guang R. Gao      | 311 |

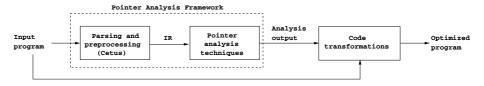

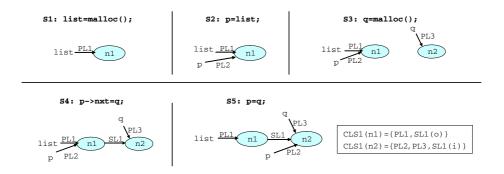

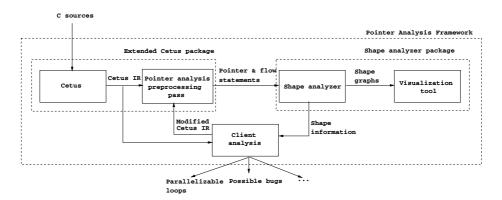

| Towards a Versatile Pointer Analysis Framework<br>R. Castillo, A. Tineo, F. Corbera, A. Navarro, R. Asenjo,<br>E.L. Zapata | 323 |

#### Topic 5: Parallel and Distributed Databases, Data Mining and Knowledge Discovery

| Dynamic and Distributed Reconciliation in P2P-DHT Networks<br>Vidal Martins, Esther Pacitti                                                      | 337 |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| HyParSVM – A New Hybrid Parallel Software for Support Vector<br>Machine Learning on SMP Clusters<br>Tatjana Eitrich, Wolfgang Frings, Bruno Lang | 350 |

| Supporting a Real-Time Distributed Intrusion Detection Application<br>on GATES                                                                   | 360 |

| On the Use of Semantic Annotations for Supporting Provenance<br>in Grids<br><i>Liming Chen, Zhuoan Jiao, Simon J. Cox</i>                        | 371 |

| Topic 6: Grid and Cluster Computing: Models,<br>Middleware and Architectures                                                                     |     |

| Introduction<br>Domenico Laforenza, Alexander Reinefeld, Dieter Kranzlmüller,<br>Luc Moreau (Topic Chairs)                                       | 381 |

| Supporting Efficient Execution of MPI Applications Across<br>Multiple Sites<br>Enol Fernández, Elisa Heymann, Miquel Àngel Senar                 | 383 |

| Private Virtual Cluster: Infrastructure and Protocol for Instant<br>Grids                                                                        | 393 |

| Ala Rezmerita, Tangui Morlier, Vincent Neri, Franck Cappello                                                                                     | 090 |

| Reducing Communication Overhead and Page Faults in SDSM<br>Platforms<br>Artemis A. Christopoulou, Eleftherios D. Polychronopoulos                | 405 |

| Flexible I/O Support for Reconfigurable Grid Environments<br>Marc-André Hermanns, Rudolf Berrendorf, Marcel Birkner,<br>Jan Seidel               | 415 |

| Storage Exchange: A Global Trading Platform for Storage Services<br>Martin Placek, Rajkumar Buyya                                                | 425 |

| Vigne: Towards a Self-healing Grid Operating System<br>Louis Rilling                                                                             | 437 |

| Problems for Resource Brokering in Large and Dynamic Grid<br>Environments<br>Catalin L. Dumitrescu                                               | 448 |

# Topic 7: Parallel Computer Architecture and Instruction Level Parallelism

| Introduction<br>Eduard Ayguadé, Wolfgang Karl, Koen De Bosschere,<br>Jean-Francois Collard (Topic Chairs)                                                                                                                        | 459 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Optimal Integrated VLIW Code Generation with Integer Linear<br>Programming<br>Andrzej Bednarski, Christoph Kessler                                                                                                               | 461 |

| Speeding-Up Synchronizations in DSM Multiprocessors<br>A. de Dios, B. Sahelices, P. Ibáñez, V. Viñals, J.M. Llabería                                                                                                             | 473 |

| Design and Effectiveness of Small-Sized Decoupled Dispatch Queues<br>Won W. Ro, Jean-Luc Gaudiot                                                                                                                                 | 485 |

| <ul> <li>Sim-async: An Architectural Simulator for Asynchronous Processor</li> <li>Modeling Using Distribution Functions</li> <li>J.M. Colmenar, O. Garnica, J. Lanchares, J.I. Hidalgo,</li> <li>G. Miñana, S. Lopez</li> </ul> | 495 |

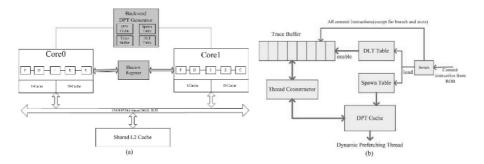

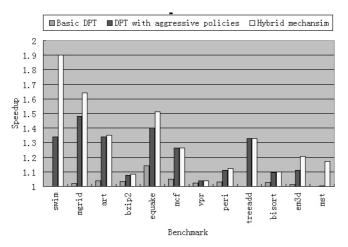

| A Hybrid Hardware/Software Generated Prefetching Thread<br>Mechanism on Chip Multiprocessors<br>Hou Rui, Longbing Zhang, Weiwu Hu                                                                                                | 506 |

| Topic 8: Distributed Systems and Algorithms                                                                                                                                                                                      |     |

| Introduction<br>Andrzej Goscinski, Gudula Rünger, Edgar Gabriel,<br>Christine Morin (Topic Chairs)                                                                                                                               | 517 |

| Distributed Approximation Allocation Resources Algorithm for<br>Connecting Groups<br>Fabien Baille, Lelia Blin, Christian Laforest                                                                                               | 519 |

| Rollback-Recovery Protocol Guarantying MR Session Guarantee<br>in Distributed Systems with Mobile Clients<br>Jerzy Brzeziński, Anna Kobusińska, Michał Szychowiak                                                                | 530 |

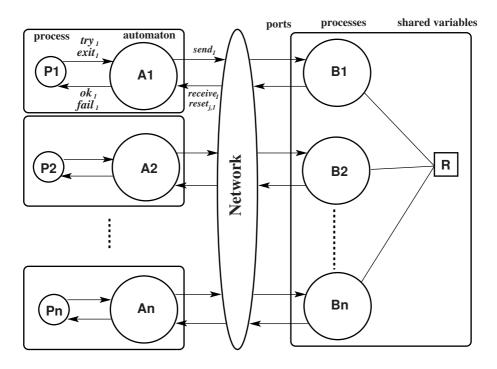

| A Practical Single-Register Wait-Free Mutual Exclusion Algorithm<br>on Asynchronous Networks                                                                                                                                     | 539 |

| Optimal and Practical WAB-Based Consensus Algorithms<br>Lasaro Camargos, Edmundo R.M. Madeira, Fernando Pedone                                                                                                                   | 549 |

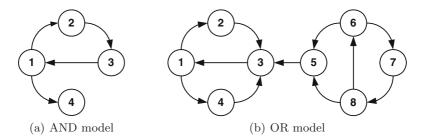

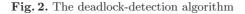

| Self-stabilizing Deadlock Detection Under the OR Requirement                                                                                                                                                                     | FFO |

| Model<br>Christian F. Orellana, Cristian Ruz, Yadran Eterovic S.                                                                                                                                                                 | 559 |

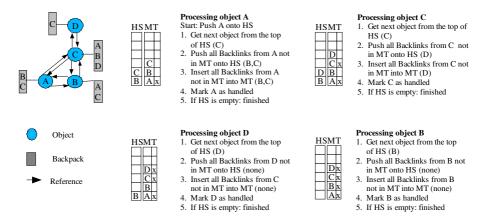

| Incremental Distributed Garbage Collection Using Reverse<br>Reference Tracking                                                                                                                 | 571 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Run-Time Switching Between Total Order Algorithms<br>José Mocito, Luís Rodrigues                                                                                                               | 582 |

| On Greedy Graph Coloring in the Distributed Model<br>Adrian Kosowski, Lukasz Kuszner                                                                                                           | 592 |

| Topic 9: Parallel Programming: Models, Methods<br>and Languages                                                                                                                                |     |

| Introduction<br>José C. Cunha, Sergei Gorlatch, Daniel Quinlan, Peter H. Welch<br>(Topic Chairs)                                                                                               | 603 |

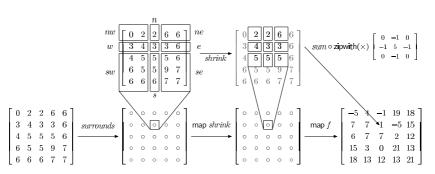

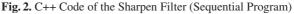

| Surrounding Theorem: Developing Parallel Programs for<br>Matrix-Convolutions<br>Kento Emoto, Kiminori Matsuzaki, Zhenjiang Hu, Masato Takeichi                                                 | 605 |

| Dynamic Task Generation and Transformation Within a Nestable<br>Workpool Skeleton                                                                                                              | 615 |

| Data Parallel Iterators for Hierarchical Grid and Tree Algorithms<br>Gerhard Zumbusch                                                                                                          | 625 |

| Implementing Irregular Parallel Algorithms with OpenMP<br>Michael Süβ, Claudia Leopold                                                                                                         | 635 |

| Toward Enhancing OpenMP's Work-Sharing Directives<br>Barbara M. Chapman, Lei Huang, Haoqiang Jin, Gabriele Jost,<br>Bronis R. de Supinski                                                      | 645 |

| Toward a Definition of and Linguistic Support for Partial<br>Quiescence<br>Billy Yan-Kit Man, Hiu Ning (Angela) Chan, Andrew J. Gallagher,<br>Appu S. Goundan, Aaron W. Keen, Ronald A. Olsson | 655 |

| Tying Memory Management to Parallel Programming Models<br>Ioannis E. Venetis, Theodore S. Papatheodorou                                                                                        | 666 |

| Topic 10: Parallel Numerical Algorithms                                                                                                                                                        |     |

| Parallel LOD Scheme for 3D Parabolic Problem with Nonlocal<br>Boundary Condition<br><i>Raimondas Čiegis</i>                                                                                                   | 679 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Online Checkpointing for Parallel Adjoint Computation in PDEs:<br>Application to Goal-Oriented Adaptivity and Flow Control<br>Vincent Heuveline, Andrea Walther                                               | 689 |

| Parallel Fault Tolerant Algorithms for Parabolic Problems<br>Hatem Ltaief, Marc Garbey, Edgar Gabriel                                                                                                         | 700 |

| Parallel Solution of Large-Scale and Sparse Generalized Algebraic<br>Riccati Equations<br>José M. Badía, Peter Benner, Rafael Mayo,<br>Enrique S. Quintana-Ortí                                               | 710 |

| Applicability of Load Balancing Strategies to Data-Parallel Embedded<br>Runge-Kutta Integrators<br>Matthias Korch, Thomas Rauber                                                                              | 720 |

| A Software Framework for the Portable Parallelization<br>of Particle-Mesh Simulations<br>I.F. Sbalzarini, J.H. Walther, B. Polasek, P. Chatelain, M. Bergdorf,<br>S.E. Hieber, E.M. Kotsalis, P. Koumoutsakos | 730 |

| Parallelization of a Discrete Radiosity Method<br>Rita Zrour, Pierre Chatelier, Fabien Feschet, Rémy Malgouyres                                                                                               | 740 |

| Parallelising Matrix Operations on Clusters for an Optimal<br>Control-Based Quantum Compiler<br><i>T. Gradl, A. Spörl, T. Huckle, S.J. Glaser, T. Schulte-Herbrüggen</i>                                      | 751 |

| Topic 11: Distributed and High-Performance<br>Multimedia                                                                                                                                                      |     |

| Introduction<br>Geoff Coulson, Harald Kosch, Odej Kao, Frank Seinstra<br>(Topic Chairs)                                                                                                                       | 763 |

| Supporting Reconfigurable Parallel Multimedia Applications<br>Maik Nijhuis, Herbert Bos, Henri E. Bal                                                                                                         | 765 |

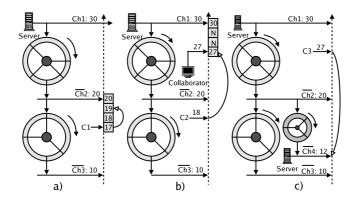

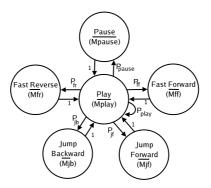

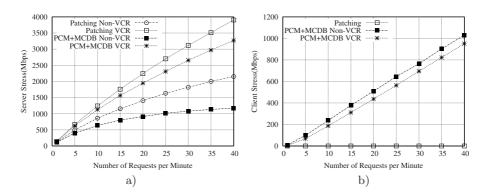

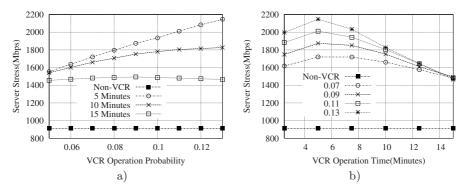

| Providing VCR in a Distributed Client Collaborative Multicast<br>Video Delivery Scheme<br>X.Y. Yang, P. Hernández, F. Cores, A. Ripoll, R. Suppi, E. Luque                                                    | 777 |

| Linear Hashtable Motion Estimation Algorithm for Distributed<br>Video Processing<br>Yunsong Wu, Graham Megson                                                                                                 | 788 |

# Topic 12: Theory and Algorithms for Parallel Computation

| Introduction<br>Danny Krizanc, Michael Kaufmann, Pierre Fraigniaud,<br>Christos Zaroliagis (Topic Chairs)                                                                     | 799 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| A Hierarchical CLH Queue Lock<br>Victor Luchangco, Dan Nussbaum, Nir Shavit                                                                                                   | 801 |

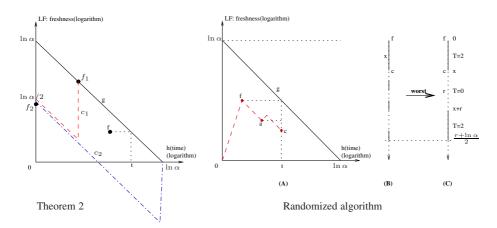

| Competitive Freshness Algorithms for Wait-Free Data Objects<br>Peter Damaschke, Phuong Hoai Ha, Philippas Tsigas                                                              | 811 |

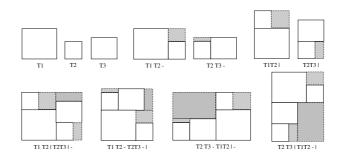

| A Parallel Algorithm for the Two-Dimensional Cutting Stock<br>Problem<br>Luis García, Coromoto León, Gara Miranda, Casiano Rodríguez                                          | 821 |

| A BSP/CGM Algorithm for Finding All Maximal Contiguous<br>Subsequences of a Sequence of Numbers<br>Carlos Eduardo Rodrigues Alves, Edson Norberto Cáceres,<br>Siang Wun Song  | 831 |

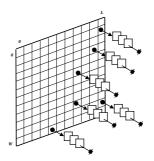

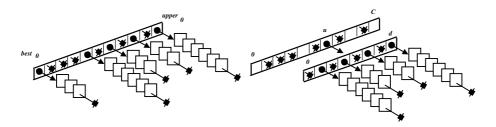

| On-Line Adaptive Parallel Prefix Computation<br>Jean-Louis Roch, Daouda Traoré, Julien Bernard                                                                                | 841 |

| Topic 13: Routing and Communication in<br>Interconnection Networks                                                                                                            |     |

| Introduction<br>Jose A. Gregorio, Bettina Schnor, Angelos Bilas, Olav Lysne<br>(Topic Chairs)                                                                                 | 851 |

|                                                                                                                                                                               |     |

| A Model for the Development of AS Fabric Management Protocols<br>Antonio Robles-Gómez, Eva M. García, Aurelio Bermúdez,<br>Rafael Casado, Francisco J. Quiles                 | 853 |

| Antonio Robles-Gómez, Eva M. García, Aurelio Bermúdez,                                                                                                                        |     |

| Antonio Robles-Gómez, Eva M. García, Aurelio Bermúdez,<br>Rafael Casado, Francisco J. Quiles<br>On the Influence of the Selection Function on the Performance of<br>Fat-Trees | 864 |

## **Topic 14: Mobile and Ubiquitous Computing**

| Introduction                                                                                                                                                                                   | 897 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Multi-rated Packet Transmission Scheme for IEEE 802.11 WLAN<br>Networks<br>Namgi Kim                                                                                                           | 899 |

| Comparison of Different Methods for Next Location Prediction<br>Jan Petzold, Faruk Bagci, Wolfgang Trumler, Theo Ungerer                                                                       | 909 |

| SEER: Scalable Energy Efficient Relay Schemes in MANETs<br>Lin-Fei Sung, Cheng-Lin Wu, Yi-Kai Chiang, Shyh-In Hwang                                                                            | 919 |

| Multicost Routing over an Infinite Time Horizon in Energy and<br>Capacity Constrained Wireless Ad-Hoc Networks<br>Christos A. Papageorgiou, Panagiotis C. Kokkinos,<br>Emmanouel A. Varvarigos | 931 |

| An Adaptive Self-organization Protocol for Wireless Sensor<br>Networks                                                                                                                         | 941 |

| COPRA – A Communication Processing Architecture for Wireless<br>Sensor Networks<br><i>Reinhardt Karnapke, Joerg Nolte</i>                                                                      | 951 |

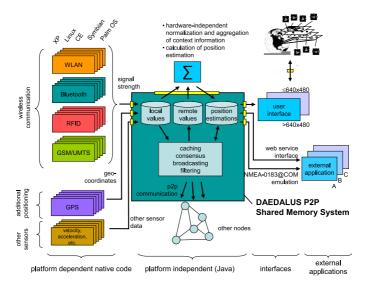

| DAEDALUS – A Peer-to-Peer Shared Memory System for<br>Ubiquitous Computing<br>Peter Ibach, Vladimir Stantchev, Christian Keller                                                                | 961 |

| Context Awareness: An Experiment with Hoarding<br>João Garcia, Luís Veiga, Paulo Ferreira                                                                                                      | 971 |

| A Client-Server Approach to Enhance Interactive Virtual<br>Environments on Mobile Devices over Wireless Ad Hoc Networks<br>Azzedine Boukerche, Richard Werner Nelem Pazzi, Tingxue Huang       | 981 |

| Topic 15: Peer-to-Peer and Web Computing                                                                                                                                                       |     |

| Roogle: Supporting Efficient High-Dimensional Range Queries<br>in P2P Systems                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------|

| Di Wu, Ye Tian, Kam-Wing Ng                                                                                                                |

| Creating and Maintaining Replicas in Unstructured Peer-to-Peer<br>Systems                                                                  |

| DOH: A Content Delivery Peer-to-Peer Network                                                                                               |

| Topic 16: Applications of High-Performance and<br>Grid Computing                                                                           |

| Introduction                                                                                                                               |

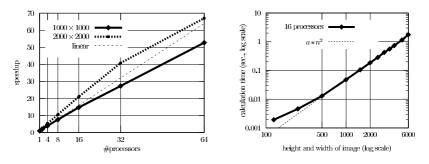

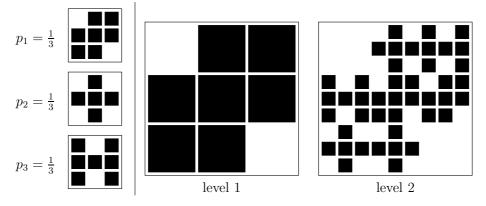

| Task Pool Teams Implementation of the Master Equation Approach forRandom Sierpinski CarpetsK.H. Hoffmann, M. Hofmann, G. Rünger, S. Seeger |

| A Preliminary Out-of-Core Extension of a Parallel Multifrontal<br>Solver                                                                   |

| A Parallel Adaptive Cartesian PDE Solver Using Space–Filling<br>Curves                                                                     |

| Load Balanced Parallel Simulated Annealing on a Cluster of SMP<br>Nodes                                                                    |

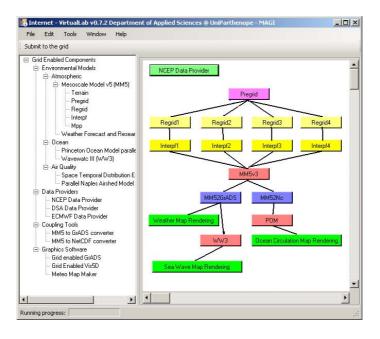

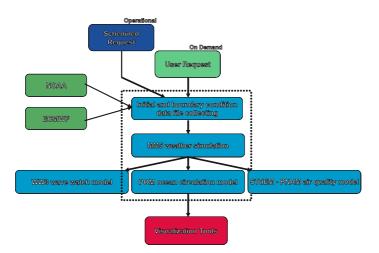

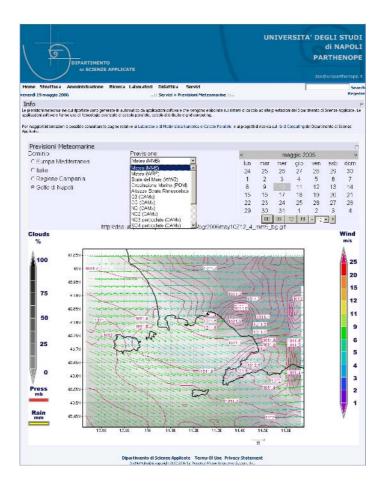

| <ul> <li>A Grid Computing Based Virtual Laboratory for Environmental</li> <li>Simulations</li></ul>                                        |

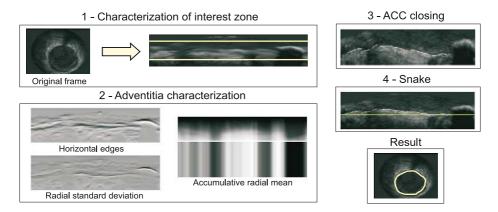

| <ul><li>Exploiting Throughput for Pipeline Execution in Streaming Image</li><li>Processing Applications</li></ul>                          |

| dCache, Storage System for the Future                                                                                                      |

| Computing the Diameter of 17-Pancake Graph Using a PC Cluster 1114<br>Shogo Asai, Yuusuke Kounoike, Yuji Shinano, Keiichi Kaneko           |

# **Topic 17: High-Performance Bioinformatics**

| Introduction                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Multidimensional Dynamic Programming for Homology Search on<br>Distributed Systems                                                                                          |

| Load Balancing and Parallel Multiple Sequence Alignment<br>with Tree Accumulation                                                                                           |

| ZIB Structure Prediction Pipeline: Composing a Complex Biological<br>Workflow Through Web Services                                                                          |

| Evaluation of Parallel Paradigms on Anisotropic Nonlinear Diffusion 1159<br>S. Tabik, E.M. Garzón, I. García, J.J. Fernández                                                |

| <ul> <li>Improving the Research Environment of High Performance</li> <li>Computing for Non-cluster Experts Based on Knoppix</li> <li>Instant Computing Technology</li></ul> |

# Topic 18: Embedded Parallel Systems

| Introduction                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------|

| Efficient Realization of Data Dependencies in Algorithm Partitioning<br>Under Resource Constraints                |

| FPGA Implementation of a Prototype Hierarchical Control Network<br>for Large-Scale Signal Processing Applications |

| An Embedded Systems Programming Environment for C                                                                 |

| Author Index                                                                                                      |

# **Topic 1: Support Tools and Environments**

Bronis R. de Supinski, Matthias Brehm, Luiz DeRose, and Tomás Margalef

Topic Chairs

Support tools and environments are vital to the production of efficient parallel and distributed applications. This year, eleven papers were submitted to this topic area, from which five were accepted as full papers.

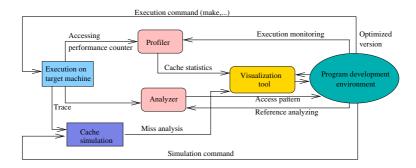

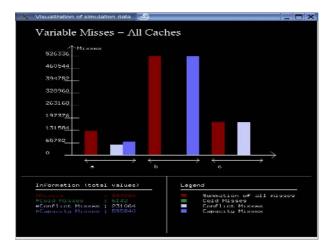

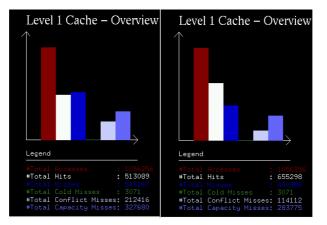

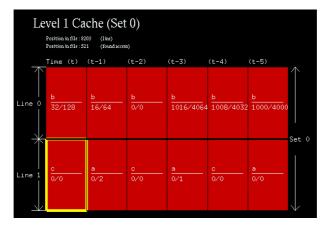

As in previous years, many submitted papers focused on the internal behaviour of applications, including how to enhance cache locality, how to detect inefficiency patterns in MPI applications and how to profile performance effectively. The infrastructure of the tools ranges from profiling, analysis, and simulation to visualization tools for graphical representation and code development.

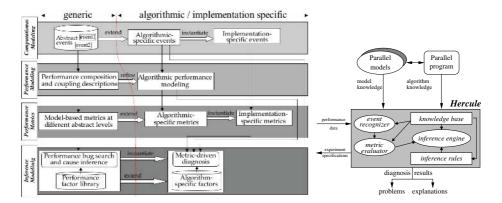

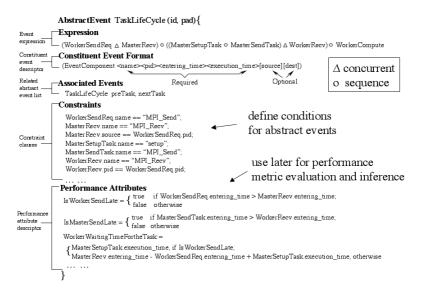

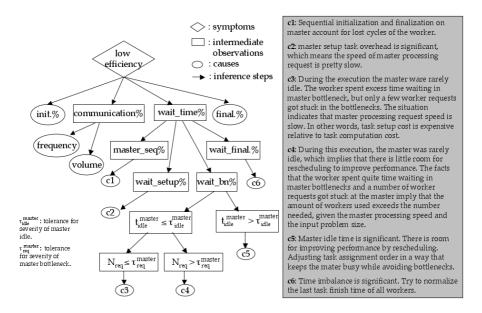

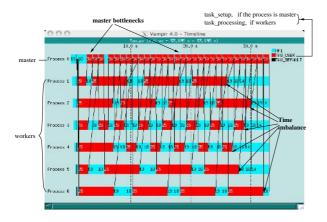

Automatic performance analysis that can detect bottlenecks related to code regions or to data structures were of particular interest. Pattern-based performance diagnosis is not only applied to master-worker computations, but also, in a distinguished paper, to patterns that arise from inefficiencies in one-sided communication. Another paper presents an automatic synthetic I/O workload in which multiple factor analysis describes the behaviour of the I/O subsystem.

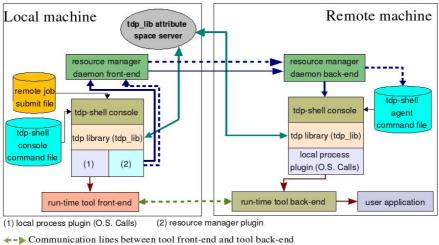

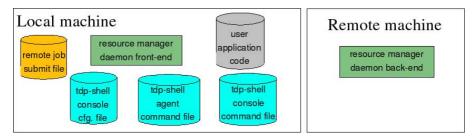

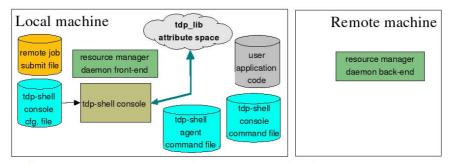

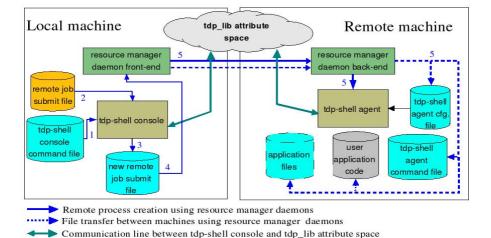

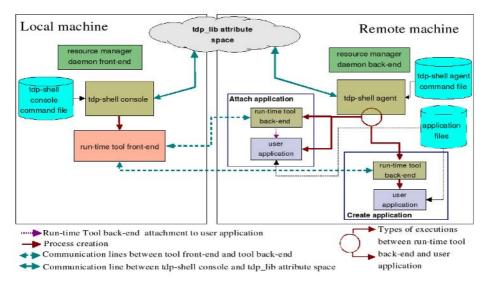

Other submitted papers this year focused on tools for grid and P2P infrastructures, particularly on resource management. An accepted paper with this focus presents a generic framework that enables run-time monitoring tools to be launched under the control of a resource management system. The crucial issues of process creation, tool creation, process monitoring and control and front-end/back-end coordination are addressed.

The qualified papers demonstrate significant tool improvement and maturation. We look forward to the stimulating discussions during session meetings that they will engender.

# IOAgent: A Parallel I/O Workload Generator

Sergio Gómez-Villamor<sup>1</sup>, Victor Muntés-Mulero<sup>1</sup>, Marta Pérez-Casany<sup>1</sup>, John Tran<sup>2</sup>, Steve Rees<sup>2</sup>, and Josep-L. Larriba-Pey<sup>1,\*</sup>

$^{1}$  DAMA-UPC

Computer Architecture Dept., Universitat Politècnica de Catalunya Jordi Girona 1-3, Campus Nord-UPC, Modul C6, 08034 Barcelona {sgomez, vmuntes, larri}@ac.upc.edu, marta.perez@upc.edu http://www.dama.upc.edu <sup>2</sup> IBM Toronto Lab. 8200 Warden Ave., Markham, ON L6G1C7, Canada {jbtran, srees}@ca.ibm.com

Abstract. The purpose of this paper is twofold. First, we present IOAgent, a tool that allows to generate synthetic workloads for parallel environments in a simple way. IOAgent has been implemented for Linux and takes into account different I/O characteristics like synchronous and asynchronous calls, buffered and unbuffered accesses, as well as different numbers of disks, intermediate buffers and number of agents simulating the workload. Second, we propose statistical models that help us to analyze the I/O behaviour of an IBM e-server OpenPower 710, with 4 SCSI drives. The observations used to build the model have been obtained using IOAgent.

**Keywords:** parallel I/O, synthetic workload generator, Linux, performance evaluation, statistical modelling.

#### 1 Introduction

The quest for tools that generate workloads for the evaluation of parallel I/O comes from long ago [1]. It is a need both as an aid for the optimum configuration of complex applications on complex computer architectures, and for the evaluation of research on Operating Systems and storage performance. The reason for such tools to exist is that they can emulate the behaviour of complex applications, avoiding the use of such applications for evaluation.

Bonnie [2], LMbench [3] and FileBench [4] are examples of tools that allow this type of workload emulation for Unix-like environments. However, such tools are restricted from many different points of view, like the number of threads and the type of I/O operating system calls that they can trigger.

<sup>\*</sup> The authors at UPC thank Generalitat de Catalunya for its support through grant GRE-00352. Sergio Gómez-Villamor thanks IBM for its support through a CAS grant.

W.E. Nagel et al. (Eds.): Euro-Par 2006, LNCS 4128, pp. 3–14, 2006.

<sup>©</sup> Springer-Verlag Berlin Heidelberg 2006

In order to give access to a generic workload generator for the evaluation of parallel I/O subsystems, we present IOAgent. Our tool sits on top of the Operating System in the same way as an application would do, and allows for the generation of workloads tailored to the needs of the system to evaluate. IOAgent allows users to generate synthetic application-level requests and defines a considerable number of behaviour-variables that allow to mimic an application. Our tool has been tested in large environments with up to 24 disks to emulate the accesses caused by a DBMS with a transactional processing workload [5].

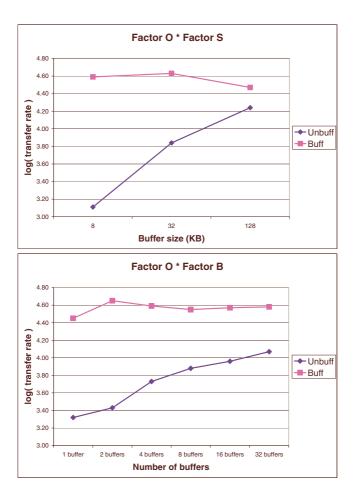

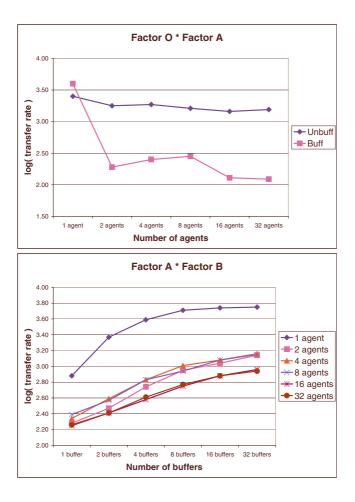

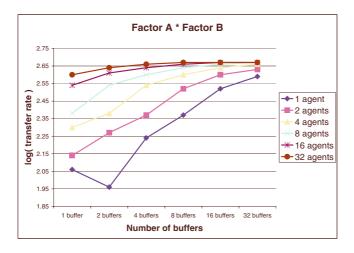

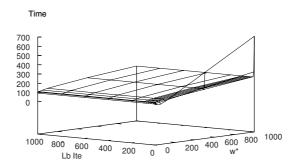

In addition, as an example of the use of IOAgent, we evaluate an Open-Power 710 I/O subsystem. For the evaluation, we generate different workloads that stress the I/O subsystem in different ways and execute them to obtain more than 10 thousand execution time measures. With all those data, we propose a statistical model of the system using the Analysis of Variance (ANOVA). We show that using statistical tools it is easier and more reliable to extract conclusions.

The rest of this paper is organized as follows. In Section 2 we explain IOAgent. Then, in Section 3, we describe the environment and tests performed. In Section 4 we describe the statistical models obtained and in Section 5 we discuss the results with the help of the models. In Section 6 we give a short overview of the literature on the topic and, finally, we conclude.

#### 2 IOAgent

IOAgent offers the possibility to mimic the stress imposed by an application on the I/O subsystem. This is done by simulating processes that exercise read and write predefined patterns on the accessed devices. Thus, IOAgent allows to evaluate parallel environments, both from the processing and the I/O points of view.

Currently, most OSs provide different system calls to execute I/O operations in a synchronous or asynchronous manner. Also, depending on whether the data blocks involved in I/O operations are mapped onto kernel buffers we can distinguish between *buffered* or *unbuffered* I/O. IOAgent allows for all those possibilities.

At this moment, IOAgent is implemented for Linux but could be ported to any other OS with little effort. IOAgent can be freely accessed in [6].

#### 2.1 Basic Structures

The synthetic workload configuration of IOAgent is set by means of (i) a set of per-thread access-patterns, also called *agents*, and (ii) a set of pseudo-devices, also called *files*.

Agents are responsible for performing the desired stress. Every agent is a thread which performs one access pattern. The mixed execution of different agents will determine the desired global workload. Each agent in a simulation will have specific values for the following fields:

- File. The file used to perform the I/O operations.

- Operation mode. There are four simultaneously compatible operation modes:

- Synchronous or asynchronous. Synchronous I/O operations block a process until the I/O is performed while asynchronous I/O operations do not block the process.

- Number of buffers. IOAgent associates each I/O operation to a buffer. Synchronous operations are performed sequentially, thus, IOAgent requires only one buffer for synchronous agents. Asynchronous operations can be performed concurrently, thus, asynchronous agents require as many buffers as I/O operations on the fly. The buffers of IOAgent emulate those provided by the application it is emulating.

- Buffered or unbuffered. With buffered I/O, IOAgent uses its own buffers, and indirectly those provided by the OS as an intermediate step for the I/O operations. With unbuffered I/O, IOAgent only uses its own buffers. Unbuffered I/O can be specified using raw devices or the *Direct I/O* mode, which can be associated to a block device interface or a file of some file systems (*i.e.* some file systems do not allow *Direct I/O* mode).

- **Read or write.** Each agent will perform exclusively read or write operations.

- Sequential or random. Sequential accesses perform a set of consecutive or strided I/O operations. Random accesses perform a number of read or writes over each position of the file following a certain probability distribution. At present, it is possible to choose among *Uniform* or *Poisson* distributions.

- Operation size. The size of the I/O operations is fixed for an *agent*.

- Inter-arrival times. We fix this per-agent value as the number of I/O operations per unit of time that each agent must generate.

Files are used in our environment to encapsulate the different storage capabilities of a system. Therefore, every *agent* is associated to a *file* which represents where the *agent* performs its I/O operations. *Files* are devices or common files on which I/O operations are executed. Regarding the storage system support, IOAgent allows for:

- File systems. The most common way to access hard disks (or its logical partitions) is through files of a built-in file system (*e.g. ext3, ext2, reiserfs, xfs, jfs*, etc.).

- Block devices interface. Different block devices (*e.g.* hard disks) of UNIXtype systems can be accessed through the /dev interface.