# Chapter 14

# MOLECULAR AND NANOSCALE COMPUTING AND TECHNOLOGY

Mary M. Eshaghian-Wilner, Amar H. Flood, Alex Khitun, J. Fraser Stoddart, and Kang Wang University of California, Los Angeles

Due to the continued scaling of CMOS chips, it is expected that the feature size of devices will reach the atomic and molecular scales in the next decades. However, there is concern that this scaling effort may come to an end. Nanoscale CMOS and other novel nano-devices promise improved performance for information processing. But there are many issues and challenges associated with the design of such nano-systems. This chapter attempts to present a very brief overview of nanoscale and molecular computing technology. Several nanoscale and molecular computing elements and architectures proposed by the authors are described, and their performance and limitations are discussed. The chapter includes a brief tutorial on various existing nanoscale and molecular devices. These include molecular switches, resonant tunnel diodes, tunnel diodes, single electron transistors, carbon nanotube field-effect transistors, quantum dots, and spin systems. Nanoscale computing modules such as quantum- and spin-based cellular logic arrays and molecularbased cellular automata, all made from the switches presented here, are discussed. These modules are an integral part of a hierarchical 3-D multiscale architecture presented. A set of nano quantum and molecular self-assembled structures, including molecular crossbars are also shown. The materials presented here are compiled from the reference articles listed at the end of the chapter.

# **1** INTRODUCTION

Nanotechnology may offer a potentially viable manufacturing technology that allows precise control of the structure of matter by working with atoms and molecules [68]. It entails the ability to build molecular systems with atom-by-atom precision, yielding a variety of systems and nanomachines. It will allow many things to be manufactured at low cost. It will lead to the production of systems including nanoelectronic circuits and nanomachines. The development of nanotechnology in the broadest sense has immediate implications, since we can design a whole new range of machines from nanoscale objects. These nano objects may be made of bits of crystal of inorganic, organic, and even biological materials. The development and use of molecular nanotechnology – the building up from atoms – will be slower because it will take time to find the exact point where changing only a few atoms in a structure will make a difference. The single electron device (e.g., memory) may be a case where molecular technology research will be commercialized more easily.

A consequence of Moore's Law is that the individual feature sizes of electronic components decrease every year despite the continued difficulty in fabricating smaller and smaller electronic components. Following on from Moore's Law, ITRS (*The International Technology Roadmap for Semiconductors*, 2003 edition) anticipates that by the year 2009 the feature sizes of devices will become less than 45 nm, where the electronic properties of the materials will change from obeying classical physics to the wave nature of quantum physics. Transistors may eventually reach a limit of one electron per bit. Current CMOS technology has reached the 90-nm feature size in manufacture.

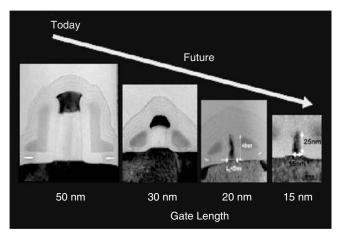

The scaling effort is intended to increase device density, functionality, and performance along with cost benefits. Therefore, shrinking of the device feature size will continue in the future until the limits and cost benefits are reached. In research, devices with a gate feature size of about 10 nm have been demonstrated, as is schematically shown in Figure 14.1 (from INTEL Components Research). The ultimate feature size of CMOS may reach 5–7 nm, for which the tunneling between source and drain may be the limiting factor. As devices are scaled down, there are many technical challenges and fundamental limits. The challenging issues range from lithography, power dissipation (power supply), short-channel effect, and gate oxide to interconnect delays.

Figure 14.1. Current and future gate sizes (from INTEL Components Research 2002).

In the nanoscale regime, electrons in a solid no longer flow like particles; rather, they can better be described as quantum mechanical-as a wave. This wave behavior makes it possible for electrons to do remarkable things, such as instantly tunneling through an insulating layer that normally would be impermeable. To understand how and when quantum effects come into play, we must consider what happens to a semiconductor device as it becomes smaller. As we reduce the size, the net electron transit time through the devices is shorter, and hence there is an incentive for making electronic devices smaller and smaller. However, there are more fundamental effects, such as the fact that for individual atoms and molecules the electronic states are discrete and quantized. Quantum effects become observable when the separation between these energy levels becomes larger than the thermal energy that allows rapid transitions at operating temperature. As the physical dimensions of the devices are reduced, the separation between the discrete energy levels increases and quantum effects persist to higher temperatures. A school of thought believes that these effects might be used to our advantageif we knew how to control them. Nanoelectronics is the emerging field of building electronic devices at the atomic level to harness these small-scale "quantum" properties of nature. The field unites physicists, chemists and biologists in order to understand how nature works at the atomic scale and how we can control it. For more details, see [14, 39, 41, 75, 83, 87].

Another new and exciting interdisciplinary field is the area of molecular electronics, which is concerned with the exploitation of organic compounds in electronic and optoelectronic devices. It is possible to build electronic devices based on molecular switches of different designs [47, 48, 62, 76, 84]. The key issue in designing a molecular-based switch, as compared with a scaled switch such as a transistor, is being able to control the flow of electrons. Use of a molecule that switches by the relative mechanical movements of its component parts, as in bistable [2] rotaxanes and [2] catenanes, is one method, from which it has been possible to fabricate a 64-bit RAM device [82]. Another way to do this in a molecule is to control the overlap of electronic orbitals. For example, with the right overlap it may be possible for electrons to flow, but if the overlap can be controllably perturbed, it may be possible to block the flow.

The task of fabricating and testing such tiny molecular devices is possible by utilizing one of two simple methods, based on (1) the use of a scanning tunneling microscope (STM), and (2) the fabrication of electrode-molecule-electrode (EME) devices. STMs use a sharpened conducting tip with a bias voltage applied between the tip and the substrate. When the tip is brought within < 1 nm of a molecular layer that is on the surface of a substrate, electrons from the molecular sample begin to tunnel across the 1 nm gap into the tip or vice versa, depending upon the sign of the bias voltage. The tunneling process is quantum mechanical, and therefore, it takes advantage of wave properties to move an electron through an energy barrier at lower energies than if the electron was a particle. EME devices can be prepared by utilizing closely packed molecular monolayers deposited onto a bottom electrode, using the Langmuir-Blodgett (LB) technique [7], such that a Ti [62] or Au [97] electrode can be vapor deposited on top without damaging, or penetrating through, the molecules. The electronic properties of the EME device can be interrogated using simple I-V measurements.

Over the past 40 years, scientists have investigated and tried to understand unusual quantum phenomena, but an important question is whether or not it is possible that a new kind of computer can be designed based entirely on quantum principles. The extraordinary power of the quantum computer is a result of a phenomenon called *quantum parallelism*, a mechanism that enables multiple calculations to be performed simultaneously. This is in contrast to a classical computer that can only perform operations one at a time, albeit very quickly [80]. The field of quantum computation had remained a largely academic one until the 1990s, when it was shown that, for certain key problems, quantum computers could, in principle, outperform their classical counterparts. Since then, research groups around the world have been racing to pioneer a practical system. However, trying to construct a quantum computer at the atomic scale is far from easy, since it requires the ability to manipulate and control single atoms. "Wiring" quantum bits together via coherent wave interactions is a challenging task. In addition, it requires the manipulation of electrons and protons within individual atoms without disturbing the coherence of the particle's spins. These systems may need to be constructed with molecular mimics or even using biological materials.

The objective of the present chapter is to present a very brief overview of nanoscale computing elements, structures, and architectures. Nanoscale elements include nano CMOS, SET, molecular devices, and others. We will study the design and fabrication of nanoscale chips for computing using Nano and Molecular elements. While the architectures presented may employ quantum and tunneling effects because of the device feature size being below 10 nm, the style of the computation used is classical rather than quantum.

The rest of the chapter is organized as follows. In the next section, we present a brief tutorial on various existing nanoscale and molecular devices. These include molecular switches, resonant tunnel diodes, tunnel diodes, single electron transistors, carbon nanotube field-effect transistors, quantum dots, and spin systems. Next, in Section 3, we review a set of nanoscale computing modules, such as quantum and spin-based cellular logic arrays, and molecular-based cellular automata, all made from the switches presented here. These modules will be an integral part of a hierarchical 3-D multi-scale architecture. In Section 5, we discuss self-assembled structures including molecular and quantum-based selfassemblies. A discussion of design issues and challenges for nanoscale and molecular computing is presented in Section 6. Concluding remarks and future research are presented in Section 7.

#### **2** SWITCHING ELEMENTS

In this section, we present a very brief description of various basic elements, devices, and units used in designing molecular and nanoscale computing structures and architectures. The basic devices presented here are used in the architectures and structures presented in the later Sections of this chapter. For a more detailed overview of some of these devices, refer to an earlier publication by Goldbaher-Gordon et al. [24].

# 2.1 Molecular Switches

Solid-state electronic devices based on molecular switches have been proposed as the active units in both nonvolatile random access memory circuits and as the reconfigurable bits for a custom configurable logic-based computing machine [82]. The central element of such devices is based on the simple EME configuration, which forms a molecular switch tunnel junction that can be electrically switched between high and low conductance states. The mounting evidence, both experimental and theoretical, is consistent with the molecule's role in the devices' switching mechanism [82, 90, 96, 98]. Consequently, it may be possible for device characteristics, such as volatility, on/off current ratios, and absolute conductance, to be tuned by altering the internal structure of the molecules. Furthermore, the molecules are designed to operate individually, which is anticipated to allow these devices to be scaled, ultimately to a very small number of molecules, if not a single one.

An integrated systems-oriented approach has guided the team of Heath and Stoddart [82] to develop and demonstrate molecular-switch tunnel junctions (MSTJs) capable of 64-bit RAM with multiple write, read and erase cycles. The MSTJ devices have been scaled from microns down to nanometer-sized devices and, further, to a situation where [91] a single semiconducting carbon nanotube is utilized as one of the electrodes. These devices are essentially fabricated the same way at each length scale. A silicon nanowire or single semiconducting carbon nanotube is prepared, and wired for electrical connectivity, on an SiO<sub>2</sub> substrate. An LB monolayer of closely packed molecular switches is transferred to the substrate, and a Ti top electrode is vapor-deposited on top of the monolayer through a mask at an angle orthogonal to the bottom electrode. An Al electrode is deposited on top of the Ti one for electrical connectivity. The remaining part of the monolayer, which is not covered by the crossbar, is finally washed away. The mechanism of switching and electrical transport in these devices relies on molecular properties and hence represents a significant development in the design and integration of organic compounds within an electronics paradigm.

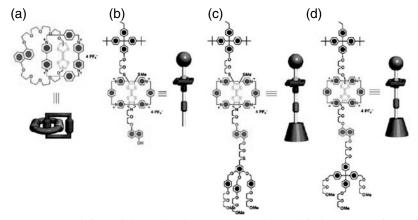

The Stoddart group at UCLA has been developing voltage-driven molecular switches from the classes of compounds known as bistable [2] catenanes, [2] rotaxanes, and [2] pseudorotaxanes for their use as the active components in solid-state molecular switch devices.

These molecules, shown in Figure 14.2 can be rationally designed to provide many advantages. First, voltage-addressable bistability can be designed into these molecules, and this bistability can be thoroughly characterized in the solution phase using various optical and NMR spectroscopies. Second, the bistable [2]catenanes, [2]rotaxanes and [2]pseudorotaxanes display slightly different overall structures, yet they contain the same voltage-activated subunits that allow their switching mechanisms to behave in a similar way within the devices. Third, these compounds are prepared using a modular synthetic approach that allows them to be optimized and customized. For example, to facilitate the formation of Langmuir monolayers, amphiphilicity can be incorporated into their molecular structures. This property allows for the preparation of closely packed monolayers that can easily be deposited on Si electrodes. The quality of the films is paramount

**Figure 14.2.** From left to right, molecular structures and graphical representations of the switchable molecules. (a) A bistable [2]catenane. (b) An amphiphilic, bistable [2]pseudorotaxane. (c, d) Two versions of amphiphilic, bistable [2]rotaxanes. In all these molecular switches, the solution-phase switching mechanism is based on voltage-driven oxidation of the tetrathiafulvalene (TTF) unit, followed by Coulombic repulsion-driven motion of the tetracationic cyclophane component so that it encircles the dioxynaphthalene (DNP) ring system.

for obtaining a working device and is assured using in-situ techniques prior to deposition of the top electrode.

The MSTJs based on bistable [2] catenanes, [2] rotaxanes and [2] pseudrotaxanes are as dependent on the electrode material as they are on the molecule [93]. While MSTJs based on the three different molecular structures have demonstrated switching characteristics in devices, it is noteworthy that the same result has not been obtained when wholly metallic materials have been employed as both of the electrodes. In all cases, operational devices were only obtained when the bottom electrode was either polycrystalline silicon, with its native oxide layer, or a single semiconducting carbon nanotube. The switching voltages were all about +2 V (switch on) or -2 V (switch off), the on/off current ratios were about 10, the device's switching was observed to be thermally activated and displayed volatility, and only switchable molecules defined a binary character in the device, in contrast to nonswitchable control compounds. However, when Pt was used as the bottom electrode, in place of Si or C, the results were different [88, 89]. Although switching of the device between on and off states was observed, it was a phenomenon that was not isolated to switchable molecules. The switching mechanism from devices built on Pt electrodes was ultimately determined to be due to electromigratory nanofilament growth [100]. Moreover, in single-molecule break junction measurements [101] conducted at low temperature, the differential conductance between two platinum wires, across a switchable rotaxane, indicate that the electron transport properties of the single-molecule EME are dominated by the electrode-molecule interface. It is conceivable that a Schottky-like barrier is present at this novel type of heterojunction. One useful rule of thumb that is suggested from these observations is that, in order to resolve the contribution of the molecule to the device's electrical transport properties, it may be important to utilize electrodes that are made of materials with a similar work function to those of the carbon that constitute organic compounds.

The design of switchable molecules and MSTJ structures alike has resulted from an interplay between synthetic chemists and device builders. This approach has allowed for both elements to evolve in order to fit the boundary conditions determined by the other one. In this way, a new technology – switchable molecules – has been integrated successfully into memory devices. Moreover, the potential to perform logic also invites investigation. The challenge faced when utilizing crossbars, or 2-D networks at the nanoscale, is one of circuit design [88] and one that has not been outside the team's consideration. Specifically, Williams' research group at HP – the third team member with Heath and Stoddart – has developed a demultiplexer and multiplexer system, thus providing the necessary proof of principle demonstration of how to electrically address nanoscale wires and junctions. Such an integrated systems-oriented approach supports the efforts of a team of many research groups geared towards the development of molecular electronic devices.

#### 2.2 Devices with Negative Differential Resistance

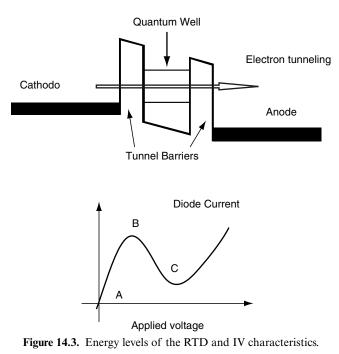

The first tunneling diode was proposed by Esaki and Tsu in 1970 [2], and the first negative-differential resistance was observed in 1973 [3]. In 1974, resonant tunneling through a double-barrier resonant-tunneling diode (RTD) was reported [4]. Among the many nanoelectronic devices proposed, the RTD has been very extensively explored for nanoelectronic circuit applications because of its compact size, high speed, device design flexibility, and negative differential resistance. RTD has been realized with nanofabrication techniques such as molecular beam epitaxy (MBE), atomic layer deposition (ALD), and metal-organic chemical vapor deposition (MOCVD). Figure 14.3 shows a typical band diagram with quantized energy levels of the RTD and *I-V* characteristics.

Initially, with low voltage across the RTD (point A in Figure 14.3), the electrons are below the resonance level, so the probability for the electrons to tunnel is extremely small. As the voltage through the RTD increases, the emitter region is wrapped upwards, and the collector region is warped downwards. Eventually, the band of electrons in the emitter is lined up with the resonant level, allowing tunneling to the collector (peak point B). With higher voltage, the electrons are pushed past the resonant energy level, which decreases the tunneling probability (point C). If the voltage increases further, some electrons become able to flow over the top of the quantum barriers, and the current will rise.

For RTD devices, two material characteristics are important for achieving high current density and high peak-to-valley ratio. These are (1) large enough energy band discontinuities and (2) material compatibility (lattice mismatch). The best performance of RTDs has been achieved with a III-V semiconductor [45]. An oscillator of InAs/AlGaAs RTD demonstrated works at over 700 GHz [21]. Also, a few logic circuits using RTDs have been proposed [37]. Among these are logic gates consisting of RTDs and HBT, Boolean function circuits, cellular neural networks, etc. The first tunnel diode SRAM cell was proposed by Goto et al., and it consisted of only one FET and two tunnel diodes [2]. Since then, tunneling devices [6, 41, 42] have attracted a great deal of interest, particularly in SRAM applications [33]. In a tunneling-based SRAM cell [60], tunneling current flows continuously to maintain one of several stable states. Figure 14.14 shows forward

Figure 14.4. I-V characteristics of the Si-Based SRAM cell.

I-V characteristics of the Si-Based SRAM cell [16]. The lower branch of the curve, which is marked as state I, occurs as the diode is brought from zero bias. As the forward bias is increased above a transition voltage (3.5V in the figure), the diode switches to the low-resistance branch, which is marked as state II. It has recently been shown that for tunneling-based SRAM, the standby power/bit can approach the limit of technology-dependent leakage by reducing the NDR tunneling current [44]. (Large-scale integration (LSI) transistor/RTD technology has been demonstrated in compound semiconductor material systems [31].) Tunneling-based static and dynamic RAMs are expected to reduce the standby power/bit (less than 1 pW for gigabit applications) [10, 17].

In contrast, the silicon-based Si/SiGe RTD demonstrated to date has a relative power current density and a smaller peak-to-valley ratio than those of III-IV materials [77]. The small peak-to-valley ratio is due to the fact that the band offsets are too small and the effective mass is too large. Even though silicon-based RTDs have not been integrated with CMOS, silicon tunnel RTD devices have recently been reported [22, 28, 29], and they can be readily integrated with current Si technologies [7].

Negative differential resistance is the key property of RTDs to be used in computational devices. It can be exploited to design compact bistable–multistable circuits [15], Cellular Neural Networks (CNN) [70], Neuromorphic Architecture [23], and Cellular Automata [94].

#### 2.3 Carbon Nano-Tube Field Effect Transistors

Nanotubes (NTs) form another class of nanostructures. The first experimental realization of individual Y-junction carbon NT diodes was recently accomplished [59]. The I-V measurements on these diodes show rectifying behavior at room temperature, suggesting potential device applications. Other earlier studies on carbon p-n junction diodes can be seen in the references [49, 50, 52]. These simple devices demonstrate the general concept of rectifying operation. Besides the rectifying behavior, Leonard and Tersoff [63] recently recognized that in NT two-terminal devices, tunneling through a potential barrier can lead to negative differential resistance (NDR). They treated theoretically both a nanotube p-n junction and an undoped metal-nanotube-metal junction by calculating quantum transport, using a self-consistent potential in tight-binding approximation. The predicted peak-to-valley current ratio, even at room temperature, exceeds by orders of magnitude those seen in existing devices.

Molecular field-effect transistors (FETs), three-terminal switching devices with single-wall and multiwall carbon NTs, were fabricated and demonstrated [38, 43]. With the application of a voltage to a gate electrode, the nanotube can be switched from a conducting to an insulating gate. At room temperature, some devices show a transistor action similar to that of p-channel field-effect transistors [54], whereas others behave like gate-voltage independent wires. At room temperature, power law behaviors are observed in the bias and temperature dependences of conductance. With the use of the gate electrode, the conductance of a single-wall NT-FET could be modulated by more than five orders of magnitude. However, large-diameter multiwall NTs typically show no gate effect; on the other hand, structural deformation can modify their electronic structure sufficiently to yield the FET behavior.

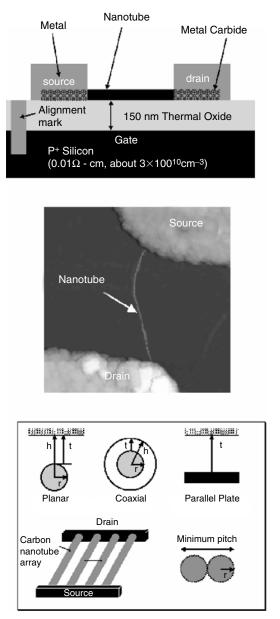

It should be noted that the above NT-FETs were fabricated on top of highwork-function metal electrodes such as platinum or gold. These devices have generally high-contact resistance and were unipolar with hole-transport characteristics. To investigate the origin of the p-type characteristics of semiconducting NTs, Martel et al. [73] fabricated carbon NT FETs with titanium carbide contacts and passivated with a uniform SiO<sub>2</sub> layer (see Figure 14.5). In contrast to the above-mentioned devices, the titanium-carbide-contacted FET showed that an apparent barrier height for carrier injection could be modulated by the gate

**Figure 14.5.** Carbon nanotube FET (CNFETs); see Martel et. al. [67]. Two gate electrode configurations (planar and coaxial) CNFETs.

field, allowing the FETs to be ambipolar with a low contact resistance for both n- and p-type conduction. This finding suggests that the usual p-type characteristic of NT FETs is not an intrinsic property of a nanotube, but rather appears to be a property of the nanotube-metal junction contacts. Moreover, the ambipolar properties of NT FETs may therefore be exploited for implementation of complementary logics. Significant progress in CNT fabrication has been made possible by utilizing electric-field-directed deposition. Single-walled carbon nanotubes were synthesized by chemical vapor deposition of methane at controlled locations on a substrate using patterned catalytic island [58]. Combined synthesis and microfabrication techniques allows a large number of ohmically contacted nanotube devices with controllable length to be placed on a single substrate.

#### 2.4 Single Electron Transistors

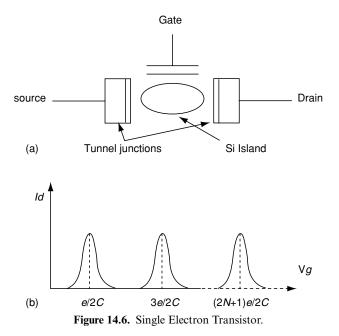

As the feature size goes to the nanometer scale, the number of electrons that the gate controls will continue to decrease and eventually reach a single electron. Device functions may be realized by controlling a single electron, referred to as a *single-electron transistor (SET)*. The SET emits an electron to a small silicon island coupled to two external reservoirs (source and drain) through a tunneling barrier, and the potential barrier of the island can be controlled by a gate or multiple gates, as shown in Figure 14.6. Because the size of the island is on the order of nanometers, the capacitance may be on the order of aF, and the charging energy ( $e^2/2C$ ) becomes more than tens of meV. In this case, the Coulomb blockade is even visible at room temperature. The drain current controlled by the gate voltage exhibits periodic oscillations with a period of ( $e/C_g$ ), called *Coulomb oscillations*.

Due to the unique features described above, single-electron transistors offer the following advantages for some circuit applications: (1) good scalability, in which the principle of the Coulomb blockade permits single-electron devices to operate at very small physical dimensions, down to the atomic scale, making ultra-large-scale integration possible; (2) ultra-low-power dissipation, simply

because these transistors use a very small number of electrons and there is little or no standby power dissipation; and (3) faster operation, with a small capacitance, even though the current is low [61]. The single-electron transistor has another interesting feature in that a large-threshold voltage shift can be achieved by adding only one electron to charge the gate [32]. As the size of the floating is shrunk to tens of nanometers, the storage of a single electron results in a threshold voltage shift much greater than the charging energy.

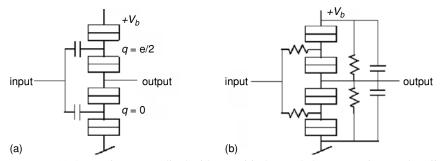

Based on the Coulomb blockade effect, several circuit applications in logic and memory have been proposed and simulated [11, 13, 55, 64, 72]. Single-electron flash memory is the first single-electron device demonstrated to operate at room temperature, in which one electron stored in the floating gate represents one bit of information [25]. Single-electron transistor with multiple gates was proposed to implement complicated logic functions, with a small number of devices with respect to the conventional CMOS, by making full use of a unique feature of SETs of an oscillatory conductance as a function of the gate voltage. Takahashi et al. [67] confirmed that a two-gate SET functioned as an XOR gate operating at 40 K. Figure 14.7 shows (a) a SET inverter realized with capacitively coupled SET transistors (the offset charges q are specified to insure proper inverter operation) and (b) a SET inverter realized with resistively coupled SET transistors.

Note that, although many logic schemes have been proposed, no logic family has been thoroughly characterized experimentally. One of the problems is that it has been difficult to fabricate complex circuits with the very small feature sizes necessary (< 100 nm) for single electronics circuits. In order for SET circuits to function, the energy that is necessary to add an electron to a device must be larger than the characteristic thermal energy  $k_BT$ . According to the published data [72], the speed of SET logic circuits is very slow, and the gate delay is more than tens of milliseconds. Actually, this large delay is not a fundamental characteristic of SET itself but results from the interconnect.

The main challenge in integration of SET devices in VLSI circuits is the charge offset problem. This problem manifests itself as a random offset due to the presence of spurious charge in the island or the region near to it. Since the source-drain current versus the gate voltage is periodic (see Figure 14.6), the random

Figure 14.7. (a) A SET inverter realized with capacitively coupled SET transistors. The offset charges q are specified to insure proper inverter operation. (b) A SET inverter realized with resistively coupled SET transistors.

offset makes the threshold voltage of each island different, and thus it is impossible to predict the "high" or "low" state. An anticipated solution to this problem may come from the use of fault-tolerant architecture [23] compensating for the deviation in a single device performance.

#### 2.5 Quantum Dots

Quantum dots (QDs) are nano-sized deposits of one semiconductor embedded in another semiconductor. Since the dot material has an energy band gap that is smaller than that of the surrounding material, it can trap charge carriers. While quantum dots are particles made up of hundreds to thousands of atoms, in many of their characteristics they behave like a single gigantic atom. The optical and transport properties of quantum dots – particularly the ease of customizing those properties by adjusting the size or composition of the dots – make them very suitable for molecular electronics. In the category of QDs, there are individual dots (a.k.a. *artificial atoms*), as well as coupled dots (*quantum-dot molecules*), and a composite device of four or five QDs called a *QD cell*. The integration of these into various architectures is shown later in this chapter. The following is a brief discussion on how quantum dots compare with RTD and SETs as explained in [24].

The essential structural feature that all three of these devices (RTD, SET, and QD) have in common is a small "island" composed of semiconductor or metal in which electrons may be confined. The island's role is analogous to that of the channel in an FET. The extent of confinement of the electrons in the island is different in these three devices. In QD, the island confines electrons with *zero* classical degrees of freedom remaining. In RTDs, because of the size, the island confines electrons with *one or two* classical degrees of freedom. And in SETs, the island confines electrons with *three* classical degrees of solid-state nanoelectronic devices their distinct properties. It should be noted that as the feature size of RTD and equivalent devices get smaller, they eventually behave as SET.

# 2.6 Spins

As explained in the overview article by Awschalom et al. [78], devices that rely on an electron's spin to perform their functions form the foundation of spintronics or magnetoelectronics. Electrons have a property called spin that can be orientated in one direction or the other – called *spin-up* or *spin-down*. When electron spins are aligned, they create a large-scale net magnetic moment. Magnetism is an intrinsic physical property associated with the spins of electrons in a material.

In an ordinary electric current, spins are oriented at random and hence play no role in determining the resistance of a wire or the amplification of a transistor circuit. Spintronic devices, in contrast, rely on differences in the transport of spin-up and spin-down electrons. In a ferromagnet, such as iron or cobalt, the spins of certain electrons on neighboring atoms tend to line up. In a strongly magnetized piece of iron, this alignment extends throughout much of the metal. When a current passes through the ferromagnet, electrons of one spin direction tend to be obstructed. The result is a spin-polarized current in which all the electron spins point in the other direction.

In 1990, Supriyo Datta and Biswajit A. Das, then at Purdue University, proposed a design for a spin-polarized field-effect transistor, or spin FET. The Datta–Das spin FET has a ferromagnetic source and drain so that the current flowing into the channel is spin-polarized. When a voltage is applied to the gate, the spins rotate as they pass through the channel and the drain rejects these antialigned electrons. Macroscopic spin transport was first demonstrated in ndoped gallium arsenide. Recent experiments have successfully driven coherent spins across complex interfaces between semiconductor crystals of different composition. For more information, refer to the cited overview article [78].

# **3** COMPUTING MODULES

Having presented the basic nano and molecular switching elements, we now proceed with an overview of a set of computing modules that can be built using those switches. These modules will be integrated to form the high-level architectures presented in the next section. The computing modules presented here are Quantum-based, Spin-based, and Molecular-based.

# 3.1 Quantum-Based Computing Modules

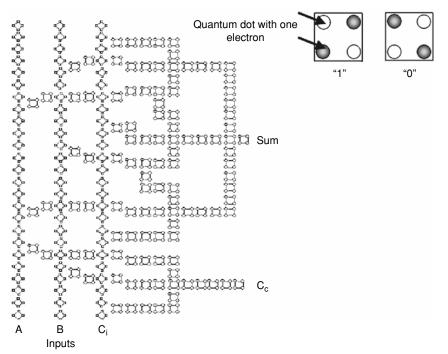

The Quantum Cellular Automata (QCA) has been extensively studied by a group of researchers at the University of Notre Dame for several years [12, 57]. The basic idea behind QCA is that when the level of integration is very small, then cells interact with each other through quantum effects and tunneling. By utilizing quantum dots, the size of an elementary cell can be shrunk down to hundreds or tens of nanometers, and the intercell interaction can be realized via quantum tunneling without wires. Moreover, the product of energy of switching, *E*, and of switching time,  $\tau$ , may approach the fundamental limit  $E \cdot \tau \leq \hbar$ . Through use of this concept, simple cells have been developed mainly using five quantum dots called a *quantum dot molecule*. The five dots are close enough to enable electrons to tunnel between the dots. The barriers between cells are assumed to be sufficient to completely suppress intercellular tunneling. Two electrons occupy each cell. The occupancy can be stabilized because of the large energy splitting between different charge states of the cell. The Coulomb interaction between electrons in a cell acts to produce two distinct cell states with different charge configurations. If the barriers to tunneling are sufficiently high, the two-electron ground-state wave function in the cell will localize the two electrons on antipodal sites. This localization is due to Coulomb exclusion, a phenomenon closely related to the well-known Coulomb blockade of current, and results in nearly exact quantization of charge in each dot.

There are two possible configurations with the electrons on opposite corners of the dots, as shown in Figure 14.8. The polarization of the states is defined as +1 and -1. Binary information can be encoded using cell polarization. A cell polarization of +1 corresponds to a bit value of 1; a cell polarization of -1 corresponds to a bit value of 0. The Coulomb interaction between cells causes the

#### Empty Quantum dot

Figure 14.8. An implementation of a binary Full Adder using QCA (adapted from the QCA website)

state of one cell to affect the state of a neighboring cell. Even a slight polarization in a neighboring cell induces essentially complete polarization in the target cell. This means that at every stage the signal level is restored. This restoration will enable a line of QCA cells to act as a robust binary wire. Similarly, a series of logic gates can be built using a specific arrangement of such cells. Therefore, it is possible to implement logic circuits in QCA. A schematic for a full adder is shown in Figure 14.8.

The details of how to lay out the QCA circuit arrays in 3-D is shown in the next section. However, at the moment, there are a number of difficulties in making QCA work efficiently. One of the main difficulties at this time is that its operation is limited to low temperatures. One solution here may be to implement the QCA molecularly.

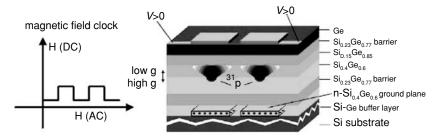

# **3.2 Spin-Based Computing Modules**

Eventually, an atomic-level Cellular Automota (CA) may be built on individual nuclear or electron spins. The original idea to use nuclear spins for quantum computing was proposed by Kane [36] (see Figure 14.9).

Initially, the aim of associating nuclear spins via hyperfine interaction was to perform a quantum superposition (entangled state) of all spins in an array.

**Figure 14.9.** Magnetic field-driven spin CA. A single electron spin device may be used as an elementary cell. The nearest neighboring spins are coupled by exchange interaction. The strength of coupling is controlled by the local electric and global magnetic fields.

However, as we explained before, our focus is just on classical computations subject to quantum effects and not "quantum computing." The problem is significantly simplified if we eliminate the very stringent demand of quantum coherency and consider nuclear spins as semiclassical two-state systems. When using spins, the maximum cell density is defined not by the cell size itself but by the intercell distance, which in turn is restricted by the interatom distance.

Similar to the QCA presented in the last section, logical functions and circuits can be implemented using spins, where the spin's direction can act as a binary switch. A binary signal is communicated from one electron to the next by spin coupling. There are no physical wires; the quantum-mechanical interaction plays the role of wires. Figure 14.10 shows how spins implement various logic functions. For a more detailed description, refer to the paper on Granular Nanoelectronics [20].

# 3.3 Molecular-Based Computing Modules

Cellular Automata (CA) is a distributed data-processing system that consists of many identical processing elements (cells) regularly arrayed on a plane. The data that the CA manipulates are a pattern of the cell states. Each cell changes its state in each discrete time through interactions with its nearest neighbors. The cellular automation receives an input pattern and converts the pattern into different patterns in next time steps using a set of rules. Finally, it renders the result as the output. We discuss here a molecular-based CA. Molecular electronics has recently attracted attention, since there is great potential in implementing new molecules (mainly organic) for a variety of electronics and optoelectronic functionalities [25]. A significant feature offered by molecular electronics is the possibility of building an intelligent molecule, that can be self-assembled by chemical syntheses and whose state can be linked to its nearest connecting neighboring molecules. The intelligent molecules may function as an ALU. It has only recently become possible to obtain some kinds of intelligent polymer molecules attached to solid surfaces [35]. Powerful chemical methods are now available for creating polymeric modules that can be assembled in a variety of ways to perform useful, intelligent molecule functions. An example of an optically driven NAND logic gate based on intelligent molecules is described in an article by Crandall and Lewis [9].

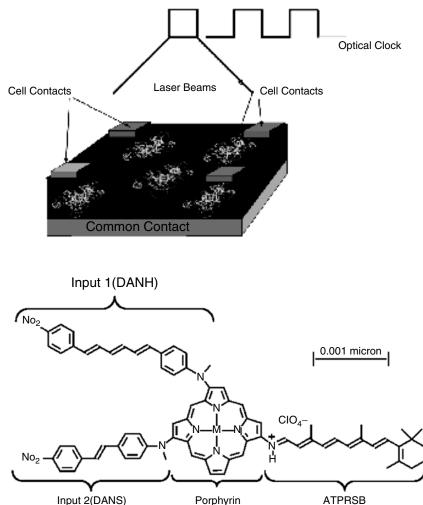

**Figure 14.10.** Optically driven molecular CA. An elementary cell is built by "smart molecules." Interactions among the nearest molecules may be initiated by optical pulses.

In Figure 14.10, we have schematically shown such a "smart molecular"-based CA. An elementary cell consists of one smart molecule with a driving electrode. The electrode serves to initiate the molecule to the initial state and also to provide the reading of the final resultant state. Association among the neighboring molecules is done though chemical bonds. Time-step synchronization may be done by optical pulses. Potentially, a number of different logic functions can be realized by one smart molecule, for example, activated by optical pulses at different wavelengths.

There are several significant drawbacks intrinsic to molecular schemes. The most important one is thermal instability. Indeed, most polymers become unstable and decomposed at several hundred degrees, implying thermal budget restrictions in fabrication. Thermal instability can also cause reliability problems due to breakdown of chemical bonds. The minimum size of the molecular CA is limited by the size of the intelligent molecule, which usually exceeds a few nanometers.

# 4 HIGH-LEVEL ARCHITECTURES

The computing modules presented in the previous sections can be assembled together to form various computing architectures. Here we present two high-level architectures. The first one is a hierarchical multiscale architecture whose basic computing modules can be any of the three modules presented in the previous section. The second architecture is neuromorphic, which presents a different style of computing paradigm. This high-level architecture also can be implemented with quantum dots, RTDs, and/or spins.

# 4.1 Multiscale Architecture Design

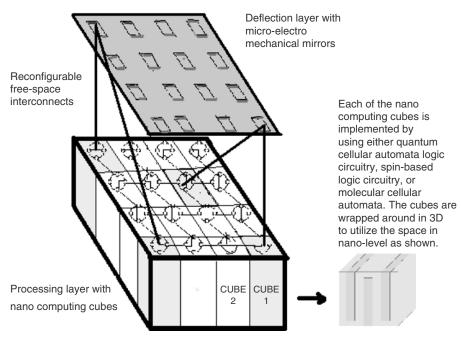

Here we discuss the integration of the nanoscale computing modules, described in the last section, into a three-dimensional hierarchical multiscale computer architecture, as shown in Figure 14.11. In this architecture, there are two layers: the processing layer below, and the deflecting layer on top. The processors can intercommunicate by using a standard reconfigurable mesh through the local switchable connections and also by using the reconfigurable microelectromechanical (MEMS) mirrors with free-space optical interconnects. Each of the processors contains some local memory and is attached to a nanoscale computing cube. In each cube there are nanoscale cells laid out in a three-dimensional format as shown. Each cube essentially can be the 3-D implementation of either the QCA, spin-based circuitry, or the molecular cellular automata.

The implementation of the architecture shown in Figure 14.11, using the quantum dot cellular automata logic circuitry that is quite well known from the work of researchers at Notre Dame University, has a low-temperature operation limitation. A solution to this problem could be to implement the cells using molecules, as described in the previous section. By using molecular magnetic switches, we can simulate the QCA that operates at room temperature. For more details, refer to [92].

In the QCA implementation, the computations within each QCA cube are done in a similar fashion as a standard QCA, except that the two-dimensional QCA logic circuits are laid out in three dimensions, as shown at the bottom right of Figure 14.11. In other words, the QCA blocks can be used to compute millions of logic operations locally by techniques already developed for QCA. The computations are done as the neighboring cells interact with each other through quantum tunneling effects. Once the local computations within each cube are completed, the results are forwarded to their corresponding processing units. The processors can then store the data in their local memory and/or intercommunicate with other processing units using the electronically reconfigured mesh and/or the micro-electromechanical mirrors.

It is possible to replace the QCA cubes with spin-based computational cubes. The overall operation at the architectural level is still the same. Computations are done within the cubes using quantum effects but based on spins instead of based on the polarities of the quantum cells. Once the cubes complete the computations, they send their results to their cube-designated processor, which will intercommunicate with other cubes using electro-optical interconnectivity. The cubes can also be replaced by molecular cellular automata units, where the computations within the cubes are governed by a set of rules as described in the previous section. Once the results of each cube are obtained, the operation among the MEMS-level processors proceeds via the electro-optical connectivity available.

Figure 14.11. A hierarchical multiscale architecture.

Whether the cells are implemented using quantum dots, spins, and/or molecules, it is easy to see that the space-time trade-offs of this multiscale model are similar to those for three-dimensional VLSI, which is  $VT^{3/2} = \Omega(I)^{3/2}$ . The difference here is that the VLSI three-dimensional model was not implementable due to fabrication limitations on the number of layers, but now we have a technology that could eventually allow a 3-D construction at the nanoscale level.

# 4.2 Neuromorphic Architecture Design

Neuromorphic architectures, shown below, are a class of nanoelectronic circuits that exploit the charging behavior in resistively/capacitively linked arrays of nanometer-sized metallic islands (quantum dots), self-assembled on a resonant tunneling diode, to perform neuromorphic computation. These circuits produce associated memory effects and realize the additive short-term memory or content-addressable memory models of neural networks without requiring either large-area/high-power operational amplifiers or massive interconnectivity between devices. These two requirements had seriously hindered the application of neural networks in the past. Additionally, the circuits can solve NP-complete optimization problems (such as the traveling salesman problem) using single electron charge dynamics, exhibit rudimentary image-processing capability, and operate at room temperature, unlike most quantum devices. Two-dimensional (2-D) processors, with a  $100 \times 100$  pixel capacity, can be fabricated in a nanoscale area. For more details, see the publication by Roychowdhury et. al. [23].

#### 5 SELF-ASSEMBLED STRUCTURES

As anticipated, the device feature size will be reduced to the nanometer regime. Self-assembly appears to be one of the most promising techniques to reach such scales economically. However, several barriers exist. The most critical are the control of the placement, the size, the uniformity, and the placement of self-assembled nanostructures. In what follows, we talk about two different types of self-assembly. One is regular arrays of quantum dots and the other is a molecular approach.

# 5.1 Regular Arrays of Quantum Dots

The control of the placement of nano-islands is of high practical importance for a number of potential applications, such as quantum dot-based lasers, singleelectron transistors, and quantum computers. On most occasions, the self-assembled quantum dots are randomly distributed on substrate surfaces due to the spontaneous nucleation process.

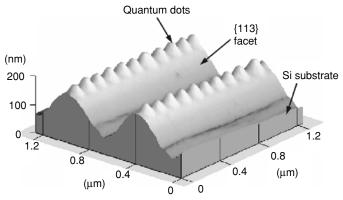

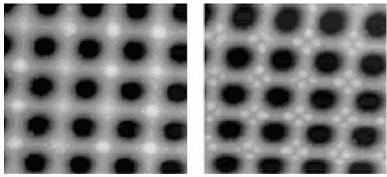

Only recently, an ordered arrangement of self-assembled nano-island has been reported [27,51]. First, Kamins et al. [27] reported that Ge dots were well aligned along the two edges of the pre-grown Si stripe mesas on patterned Si (001) substrates. Then, G. Jin et al. [51] observed a cooperative arrangement of self-assembled dots on one-dimensional (1-D) ridges of Si stripe mesas formed by selective epitaxial growth. The cooperative arrangement of Ge dots was obtained with a degree of periodicity to place the dots at the desired location – an essential requirement for information processing. Moreover, the aligned Ge dots on the ridges had a *mono*-modal distribution, in contrast with a *bi*-(even *multi*-) modal distribution of self-assembled Ge dots normally observed on planar Si (001) substrates. Figures 14.12 and 14.13 show ordered arrangement of self-assembled Ge quantum dots on selectively grown Si mesas on pattern substrates prepared with a conventional photolithography [51]. This approach enables us to realize regimented arrays of high-density nano-structures at low cost and free of defects and damages.

This approach of using substrate patterns to achieve the regimented placement also provides self-assembly of the nearest neighbor interconnects. Moreover, using tilted substrates, we are able to form regular surface steps via appropriate surface treatments, such as annealing. These regular atomic steps have been used as a template for the formation of ordered dot arrays. It is also possible to control the surface reconstruction via a surface modification to accomplish the ordering structures in an atomic scale. What has been demonstrated is just the beginning, and there are abundant opportunities to explore new principles and methods not yet discovered to achieve regimented structures for scales down to the atomic level.

# 5.2 Molecular Self-Assembly

An interesting alternative for circuit fabrication, when devices are scaled to a few tens of nanometers in size and smaller, is the bottom-up, self-assembly-based manufacturing approach being developed in molecular electronics research programs.

**Figure 14.12.** Three-dimensional AFM image of the cooperative arrangement of self-assembled Ge dots on <110>-oriented Si stripe mesas with a window width of 0.6  $\mu$ m. Self-aligned and well-spaced 1D arrays of Ge dots are formed on the ridges of the Si mesas after the deposition of 10 ML Ge. The growth temperature is 630°C. The sidewall facets of the Si stripe mesas are confirmed to be {113} facets. The dimensions of the Ge islands are about 80 nm wide and about 20 nm high, and the period of the Ge islands is about 110 nm.

(a)

**Figure 14.13.** AFM images of the 2-D arrangement of Ge dots on Si mesas with different Ge amounts. (a) 0.4 nm – one dot; (b) 1.3 nm – four dots. The growth temperature is 600° C. The scale of the images is  $4\times4 \ \mu\text{m}^2$ .

However, at this time there are many challenges in developing circuitry by this approach. For example, self-assembly leads most readily to periodic structures, and, while the starting material for such approaches may be highly purified, the assembly steps themselves are unlikely to be perfect. Furthermore, various structural parameters of a circuit that are obtained through lithographic patterning, such as the length, diameter, orientation, and separation of the wires, can be substantially more difficult to control by using chemical assembly. Also, nanowires with the most desirable electrical characteristics, such as single-walled carbon nanotubes, do not necessarily have the chemical properties required for controlled self-assembly.

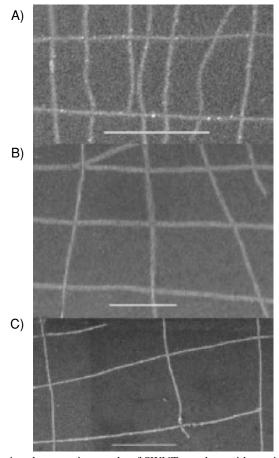

Single Crossbars: The relevance of the crossbar circuit for molecular electronics was first reported by Heath et al. [34]. Later a room-temperature, minimallithography technique for chemically assembling small deterministic crossbars of single-walled carbon nanotubes (SWNT) was presented [79]. Results indicate that it is possible to fabricate deterministic wiring networks from SWNTs by using chemical self-assembly. While this process is currently limited to the fabrication of relatively small crossbars ( $4 \times 4$  and less), preliminary results indicate that the optimization of several experimental handles may lead to the assembly of large-scale structures without requiring the use of lithographic techniques. Thus, relatively inexpensive routes toward fabricating designed circuits with characteristic dimensions on the order of a few nanometers may be possible. Three SWNT crossbars of varying structural characteristics are shown in Figure 14.14. A key result of this work is that the pitch of the crossbar was controllable and correlated with the length of the SWNT ropes. Although progress is being made, it has been difficult, up until recently, to exercise the level of control required in order to attain the

**Figure 14.14.** Scanning electron micrographs of SWNT crossbars with varying pitch. Scale bars are 500 nm for A) and B), and 1  $\mu$ m for C). The diameter of the ropes is not well measured with this technique, but can be measured with force microscopy. The shortest (500 nm) wires are characterized by diameters of 1–2 nm, while the longest (20 $\mu$ m) wires possess diameters ranging from 10 to 15 nm. SWNT rope lengths [ $\mu$ m]: A) 3.7 ± 0.3 & 1.2 ± 0.33; B) 2.8 ± 0.53; C) 3.8 ± 1.2.

required density and complexity by utilizing processes that are amenable to largescale manufacture. Lieber's group has demonstrated the large-scale alignment and multilevel fabrication of ultra-high-density Si nanowire elements for electronic applications [99]. The precise alignment of the nanowires was provided by the self-organizational principle inherent in large-aspect ratio wires orienting at the air-water interface, like the timber in a log run. These arrays of nanowires, deposited as LB films and patterned using lithographic techniques, form the basis for one class of circuitry based on crossbars.

The crossbar junction represents one of the simplest elements that can be considered as an active device when the two wires are separated by an insulating dielectric or a molecular switch. Bistable nanotube mechanical junctions [66], as well as various EME junction devices-diodes [98], molecular switch tunnel junctions [62], and junctions exhibiting negative differential resistance [65], have all been demonstrated at the device level.

The opportunity to build functional electronic components from semiconducting nanowires offers ultra-high-density circuitry, which has been facilitated by recent advances in nanowire fabrication. Lieber has developed a method for growing nanowires that provide the ability to modulate the doping along a Si nanowire between high and low levels [95]. In addition, nanowires can be grown with core shell structures [81] from two different materials, wherein the sheath can be removed, exposing the inner core. While these new classes of nanowires provide a similar level of nanometer-scaled control over the electronic structure, which is displayed in molecular electronic components, they do not display the facility to undergo a molecule's geometry rearrangements. When these highly structured nanomaterials are coupled with the new handling techniques for laying down nanowires in a controlled way using the LB method, the door to a new class of nanoelectronic devices founded on custom-designed nanowires may be opening.

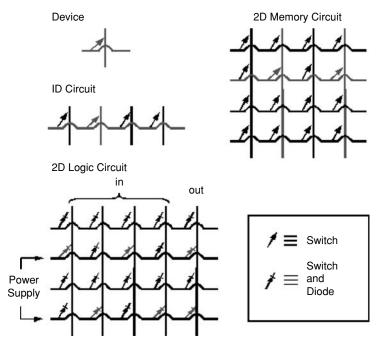

**Crossbar Networks**: During the development of nanometer scale switches, traditional circuit designs may not be able to take maximum advantage of the unique properties and scale conferred. Consequently, the crossbar junction appears to be the basis from which to consider (see Figure 14.15) higher levels of complexity for the formation of crossbar networks. It is possible to conceive of different schemes to design 1-D [48, 69, 71] or 2-D networks for memory or logic purposes.

The state-of-the-art crossbar networks are tiled in 2-D, in which each crossbar is a two-terminal switching device. This higher level of complexity in circuit design sets one fundamental limitation: each crossbar has to be independently addressable. In cases where the 2-D networks have been fabricated in the past, as in ferroelectric [18] and magnetoresistive [56] crosspoint memories, the key issue has been that of half-select. In a crossbar network, each wire crosses many others at their crosspoints and this can lead to a situation where switches are incorrectly selected. However, when a rotaxane-based molecular switch is used at the crossbar, half select is no longer a problem. The bistable molecular switches are voltage gated, which means that only those crosspoints that are defined by a potential difference, which exceeds a certain threshold voltage, will lead to an addressed crosspoint. All the other wires crossing the two that are used to address the crosspoint of interest are below the switching threshold and are therefore not mistakenly switched. Through use of bistable [2] rotaxane-based molecular switches, it has been possible to generate a memory array and to perform simple logic such as an AND or XOR gate [82].

**Figure 14.15.** It is possible to utilize a crossbar in increasing levels of complexity to attain memory and perform logic. The crossbar networks can be composed of switches or diodes, in which molecules may provide the key active component in order to realize such devices. (Adapted from [82].)

#### 6 DESIGN ISSUES AND CHALLENGES

In this section, we talk about the design issues and challenges in nanoscale and molecular computing architectures.

# 6.1 Unidirectionality Issues

A major drawback of the proposals for logic implementations based on bistable devices without directionality such as the QCA lies in their failure to ensure propagation of the logic signal from the input to the output. That is, if two bistable devices are connected together in series, then there must be some isolation between the input and output so that the input drives the output and not the reverse. Coulomb interactions between two identical charge polarizations are reciprocal, so it is impossible to distinguish the input polarization from the output polarization. In other words, the output influences the input just as much as the input influences the output. Consequently, logic signals cannot propagate unidirectionally from the input to the output, from one stage to the next, leading to an operational failure. This occurs because the input cannot uniquely and predictably determine the output. This problem is pathological in many proposed schemes of nano-electronic architecture: one needs to ensure that the signals propagate from the input to the outputs and that the whole system does not get stuck in metastable states. For more details, see the article by Anantrand and Roychowdhury [46].

On the other hand, the cellular automata-based architectures with local connectivity also have shortcomings: they offer no mechanism for loading the initial program into the cellular array of quantum devices. As a result, they are also of questionable efficacy.

In neuromorphic schemes, unidirectional signal propagation from the input to the output is effected through a *clocking mechanism*. For example, when the OR gates in the first layer are operational, the AND gate in the succeeding stage is disabled. Once the OR gates have reached stable states, then a clock pulse is applied to initialize the AND gate. This scheme avoids the potential problem of the AND gate acting as an input to the OR gates, and instead allows the OR gates to drive the AND gate. The same strategy can be extended to the case of multilevel circuits. Such a scheme of multiphase clocking ("push-clock" and "dropclock") is also used in conventional charge-coupled devices (CCDs). Moreover, this multiphase clocking scheme will enable *pipelining*. That is, every other level in a multilevel circuit can operate simultaneously, and a new set of inputs can be fed to the circuit every other clock cycle. This setup allows the implementation of a high throughput logic block.

#### 6.2 Fault-Tolerant Designs

In order to replace conventional CMOS circuits with nanoscale devices, we first have to demonstrate nano-devices with combined memory and logic functions. Recent investigations suggest that "smart molecules" could be a possible first step toward constructing molecular nanoscale computing modules. To date, the unprecedented accuracy required for positioning single molecules into an array of growing, perfectly ordered quantum dots to form a controlled array is a road block for practical realization of the proposed schemes. In general, any attempt to construct a large number of identically operating devices integrated on a large scale usually suffers from inevitable material imperfections. Potentially, this problem may be resolved by progress in advanced fabrication techniques (for example, a high level of self-assembly). Another possible solution is the use of fault tolerance or self-correction mechanisms to allow for faults in logic functionalities, rather than simply working toward perfecting fabrication processes [19, 23, 30]. Clearly, progress in both areas will be helpful.

Any computational architecture at the nanoscale level should display inherent fault-tolerant properties. Nanostructure devices will probably have more variability in their characteristics than their earlier-generation microstructure counterparts. Any scheme that ignores this fact and relies on every quantum dot being perfect will almost inevitably be impractical. In order to ensure fault tolerance, one can allow a cluster of islands to represent a gate, rather than a single dot or just a few dots. Note that the size of the arrays for each gate can be varied depending on the state of the technology. By providing larger arrays, one can increase fault tolerance.

# 6.3 Challenges of Molecular Computing

There are a number of issues facing the emerging field of molecular electronics that need to be addressed. At a fundamental level, bistable [2] rotaxane-based switches are believed to permit electron transport primarily by tunneling through quantized energy levels. Consequently, by tuning the molecular subunits that constitute the rotaxanes, it may be possible to enhance the on/off current ratio and therefore widen the areas of applicability of molecular computing. One other key area relates to how exactly molecular electronic components can be fully harnessed by employing unique computer circuits. This is a salient thesis in this chapter, and therefore an integrated systems-oriented approach forms a central feature and returns the problem to one of interdisciplinary description–what are molecular properties, and how do they impact on the architecture? The driving force to face this challenge may be provided less by fundamental discovery than by market forces. This situation is not unfamiliar in the area of electronics, where it is Moore's Law that has guided scientists and engineers alike into the molecular and quantum domains.

#### 7 CONCLUSION

In this chapter, we have presented an overview of various nanoscale and molecular computing architectures. We have given a brief tutorial on various existing nanoscale and molecular devices. These include molecular switches, resonant tunnel diodes, tunnel diodes, single electron transistors, carbon nanotube field-effect transistors, quantum dots, and spin systems. We have next discussed a set of nanoscale computing modules, such as quantum and spin-based cellular logic arrays, and molecular-based cellular automata, all made from the switches presented here. These modules are an integral part of the hierarchical 3-D multiscale architecture presented. We have also showed a set of quantum and molecular self-assembled structures including molecular crossbars. The fabrication of these architectures currently faces a number of challenges, as discussed in this chapter. Nanoscale and molecular computing is a promising alternative to today's CMOS technology but is in an infancy stage, with many interesting design issues yet to be studied and resolved.

# ACKNOWLEGMENTS

We acknowledge with great thanks Dr. Vwani Roychowdhry for his contributions as a consultant to this project.

#### REFERENCES

[1] [1960-01] E. Goto, K. Mutara, K. Nakazawa, T. Moto-Oka, Y. Matsuoka, Y. Ishibashi, T. Soma, and E. Wada. (1960): Esaki diode high speed logical circuits, *IRE Transactions on Electronics and Computing* 9, 25.

- [2] [1970-01] L. Esaki and R. Tsu (1970): Superlattice and negative differential conductivity in semiconductors, IBM *Journal of Research and Development* 14, 61.

- [3] [1973-01] L.L. Chang, L. Esaki, W.E. Hpoward, and R. Ludeke (1973): Structures grown by molecular beam epitaxy (GaAs and GaAs-Ga/sub 1x/Al/sub x/As), *Journal of Vac. Science and Technology 10*, 11, 9.

- [4] [1974-01] L.L. Chang, L. Esaki, and R. Tsu (1974): Resonant tunneling in semiconductor double barriers, *Applied Physics Letters 24*, 593.

- [5] [1976-01] J. Holland (1976): Studies of the spontaneous emergence of selfreplicating systems using cellular automata and formal grammars, *in Automata Languages Development*, North-Holland Publishing Co., Amsterdam, The Netherlands, pp. 385.

- [6] [1987-01] V.J. Goldman, D.C. Tsui, and J.E. Cunningham (1987): Observation of intrinsic bistability in resonant-tunneling structures, *Physical Review Letters* 58, 1256.

- [7] [1990-01] A. Miura, T. Yakihara, S. Uchida, S. Oka, S. Kobayashi, H. Kamada, and M. Dobashi (1990): Monolithic sampling head IC, *IEEE Trans. Microwave Theory and Technology 38*, 1980.

- [8] [1991-01] A. Ulman (1991): An Introduction to Ultrathin Organic Films from Langmuir-Blodgett to Self-assembly, Academic Press, San Diego.

- [9] [1992-01] B.C. Crandall and J. Lewis (1992): Nanotechnology Research and Perspectives, The MIT Press Cambridge, pp. 149–170.

- [10] [1992-02] Y.-C. Kao, A.C. Seabaugh, and H.-T. Yuan (1992): Vertical integration of structured resonant tunneling diodes on InP for multi-valued memory applications, *Int. Conference on Indium Phosphide and Related Materials* 489.

- [11] [1992-03] J.R. Tucker (1992): Complementary digital logic based on the Coulomb blockade,' *Journal of Applied Physics*, 72, 4399.

- [12] [1993-01] C.S. Lent, P.D. Togaw, and W. Porod (1993): Bistable saturation in coupled quantum dots for quantum cellular automata, *Applied Physics Letters* 62, 714.

- [13] [1993-02] K. Yano, T. Ishii, T. Hashimoto, T. Kobayashi, F. Murai, and K. Seki (1993): A room-temperature single-electron memory device using fine-grain polycrystalline silicon, *IEDM Technical Digest 541*.

- [14] [1994-01] P. Balasingam and V.P. Roychowdhury (1994): Nanoelectronic functional devices, Purdue University Technical Report: TR-EE 94-24.

- [15] [1994-02] K. Maezawa, T. Akeyoshi and T. Mizutani (1994): Functions and applications of monostable-bistable transition logic elements (MOBILE's) having multiple-input terminals, *IEEE Transactions On Electron Devices* 41, 148.

- [16] [1995-01] T.K. Carns, X. Zheng, and K.L. Wang (1995): A novel high speed, three element Si-based static random memory (SRAM) cell, *IEEE Electron Device Letters 16*, 256.

- [17] [1995-02] K. Itoh, K. Sasaki, and Y. Nakagome (1995): Trends in low-power RAM circuit technologies, *Proceedings of IEEE 83*, 524.

- [18] [1995-03] R.E. Jones, Jr., P.D. Maniar, R. Moazzami, P. Zurcher, J.Z. Witowski, Y.T. Lii, P. Chu, and S.J. Gillispie (1995): Ferroelectric nonvolatile memories for low-voltage, low-power applications, *Thin Solid Films* 270, 584.

- [19] [1996-01] S. Bandyopadhyay and V.P. Roychowdhury (1996): Computational paradigms in nanoelectronics: quantum coupled single electron logic and neuromorphic networks, *Japan. J. Appl. Phys.* 35, 3350.

- [20] [1996-02] S. Bandyopodhyay and V.P. Roychowdhury (1996): Granular nanoelectronics: The logical gateway to the 21<sup>st</sup> Century, *IEEE Potentials*.

- [21] [1996-03] E.R. Brown and C.D. Parker (1996): Resonant tunnel diodes as submillimetre-wave sources, *Philos. Trans. R. Soc. London, Ser. A 354*, 2365.

- [22] [1996-04] J.Koga and A. Toriumi (1996): Room temperature negative differential conductance in three-terminal silicon surface tunneling device, *IEDM Technical Digest 265*.

- [23] [1996-05] V.P. Roychowdhury, D.B. Janes, S. Bandyopadhyay, and X. Wang (1996): Collective computational activity in self-assembled arrays of quantum dots: a novel neuromorphic architecture for nanoelectronics, *IEEE Transactions on Electron Devices* 43, 1688.

- [24] [1997-01] D. Goldhaber-Gordon, M.S. Montermerlo, J.C. Love, G.J. Opiteck, and J.C. Ellenbogen (1997): Overview of nanoelectronic devices, *Proceedings of IEEE*.

- [25] [1997-02] J. Jortner and M. Ratner (1997): Molecular Electronics, Oxford, U.K.

- [26] [1997-03] T.I. Kamins, E.C. Carr, R.S. Williams, and S.J. Rosner (1997): Deposition of three-dimensional Ge islands on Si(001) by chemical vapor deposition at atmospheric and reduced pressures, *Journal of Applied Physics 81*, 211.

- [27] [1997-04] T.I. Kamins and R.S. Williams (1997): Lithographic positioning of self-assembled Ge islands on Si(001), *Physical Letters* 71, 1201.

- [28] [1997-05] S.J. Koester, K. Ismail, K.Y. Lee, and J.O. Chua (1997): Operation of a novel negative differential conductance transistor fabricated in a strained Si quantum well, *IEEE Electron Device Letters 118*, 432.

- [29] [1997-06] K. Morita, K. Morimoto, H. Sorada, K. Araki, K. Yuki, M. Niwa, T. Uenoyama, and K. Ohnaka (1997): Si interband tunnelling diode through a thin oxide with a degenerate poly-Si electrode, *in Extended Abstracts from the 3<sup>rd</sup> International Workshop Quantum Functional Devices 175.*

- [30] [1997-07] V.P. Roychowdry, D.B. Janes and S. Bandyopadhyay (1997): Nanoelectronic architecture for Boolean logic, *Proc. IEEE 85*, 574.

- [31] [1997-08] A. Seabaugh, B. Brar, T. Broekaert, G. Frazier, P. van der Wagt, and E. Beam (1997): Resonant tunneling circuit technology: has it arrived?, *GaAs IC Symposium and Technology Digest 119*.

- [32] [1997-09] J.J. Welser, S. Tiwari, S. Rishton, K.Y. Lee, and Y. Lee (1997): Room temperature operation of a quantum-dot flash memory, *IEEE Electron Devices Letters 18*, 278.

- [33] [1997-10] X. Zhu, X. Zheng, M. Pak, M.O. Tanner, and K.L. Wang (1997): Si bistable diode utilizing interband tunneling junctions, *Applied Phyics Letters* 71, 2190.

- [34] [1998-01] J.R. Heath, P.J. Kuekes, G.S. Snider, R.S. Williams (1998): A defect tolerant computer architecture: Opportunities for nanotechnology, *Science 280*, 1716.

- [35] [1998-02] K.M. Horn, B.S. Swartzentruber, G.C. Osbourn, A. Bouchard, and J.W. Bartholomew (1998): Electronic structure classifications using scanning tunneling microscopy conductance imaging, *Journal of Applied Physics 84*, 2487.

- [36] [1998-03] B.E. Kane (1998): A silicon-based nuclear spin quantum computer, *Nature 393*, 133.

- [37] [1998-04] C.H. Lin, K. Yang, M. Bhattacharya, X. Wang, X. Zhang, J.R. East, P. Mazumder, and G.I. Haddad (1998): Monolithically integrated InP-based minority logic gate using an RTD/HBT heterostructure, *International Conference on Indium Phosphide and Related Materials* 419.

- [38] [1998-05] R. Martel, T. Schmidt, H.R. Sea, T. Hertel, and P. Avouris (1998): Single- and multi-wall carbon nanotube field-effect transistors, *Applied Physics Letters* 73, 2447.

- [39] [1998-06] J.H. Reif (1998): Alternative computational models: A comparison of biomolecular and quantum computation, *Proceeding of the 18<sup>th</sup> International Conference on Foundations of Software Technology and Theoretical Computer Science.*

- [40] [1998-07] M. Rodder, S. Hattangady, N. Yu, W. Shiau, P. Nicolllian, T. Laaksonen, C.P. Chao, M. Mehrota, C. Lee, S. Murtaza, and S. Aur (1998): IEDM Tech. Dig. 623.

- [41] [1998-08] A.C. Seabaugh and R. Lake (1998): Beyond-the-roadmap technology: Silicon heterojunctions, optoelectronics, and quantum devices, *Encyclopedia of Physics 22*, 335.

- [42] [1998-09] J.P. Sun, G.I. Haddad, P. Mazumder, and J.N. Shulman (1998): Resonant tunneling diodes: models and properties, *Proceedings of IEEE 86*, 641.

- [43] [1998-10] S.J. Tans, R.M. Verschueren, and C Dekker (1998): Room temperature transistor based on a single carbon nanotube, *Nature 393*, 49.

- [44] [1998-11] J.P.A. van der Wagt, A.C. Seabaugh, and E.A. Beam (1998): RTD/HFET low standby power SRAM gain cell, *IEEE Electron Device Letters 19*, 7.

- [45] [1998-12] T. Waho, T. Itoh, and M. Yamamoto (1998): Ultrahigh-speed resonant tunneling circuits, in Second International Workshop on Physics and Modeling of Devices based on Low-Dimensional Structures, p.73.

- [46] [1999-01] M.P. Anantram and V.P. Roychowdhury (1999): Metastable states and information propagation in a one-dimensional array of locally coupled bistable cells, *Journal of Applied Physics* 85.

- [47] [1999-02] J. Chen, M.A. Reed, A.M. Rawlett, and J.M. Tour (1999): Large on-off ratios and negative differential resistance in a molecular electronic device, *Science 286*, 1550.

- [48] [1999-03] C.P. Collier, E.W. Wong, M. Belohradsky, F.M. Raymo, J. F. Stoddart, P.J. Kuekes, R.S. Williams, and J. R. Heath (1999): Electronically configurable molecular-based logic gates, *Science 285*, 391.

- [49] [1999-04] K. Esfarjani, A.A. Farajian, Y. Hashi, and Y. Kawazoe (1999): Electronic and transport properties of N-P doped nanotubes, *Applied Physics Letters* 74, 79.

- [50] [1999-05] A.A. Farajian, K. Esfarjani, and Y. Kawazoe (1999): Nonlinear coherent transport through doped nanotube junctions, *Physical Review Letters* 82, 5084.

- [51] [1999-06] G. Jin, J. L. Liu, S. G. Thomas, Y. H. Luo, K. L. Wang, and B. Y. Nguyen (1999): Controlled arrangement of self-organized Ge islands on patterned Si (001) substrates, *Applied Physics Letters* 75, 2752.

- [52] [1999-07] F. Leonard and J. Tersoff (1999): Novel length scales in nanotube devices, *Physical Review Letters* 83, 5174.

- [53] [1999-08] K. Likharev (1999): Single-electron devices and their applications, *Proceedings of IEEE*, 87.

- [54] [1999-09] J. Nygard, D.H. Cobden, M. Bockrath, P.L. McEuen, and P.E. Lindelof (1999): Electrical transport measurements on single-walled carbon nanotubes, *Applied. Physics A* 69, 297.

- [55] [1999-10] Y. Ono, Y. Takahashi, K. Yamazaki, H. Namatsu, K. Kurihara, and K. Murase (1999): Si complementary single-electron inverter, *IEDM Technical Digest 367*.

- [56] [1999-11] S.S.P. Parkin, K.P. Roche, M.G. Samant, P.M. Rice, R.B. Beyers, R.E. Scheuerlein, E.J. O'Sullivan, S.L. Brown, J. Bucchigano, D.W. Abraham, Y. Lu, M. Rooks, P.L. Trouilloud, R.A. Wanner, and W.J. Gallagher (1999): Exchange-biased magnetic tunnel junctions and application to nonvolatile magnetic random access memory, J. Appl. Phys. 85, 5828.

- [57] [1999-12] G. Snider, A. Orlov, I. Amlani, X. Zuo, G. B. Stein, C. Lent, J. Mez, and W. Porod (1999): Quantum-dot cellular automata, *Journal of Applied Physics*.

- [58] [1999-13] H.T. Soh, C.F. Quate, A.F. Morpurgo, C.M. Marcus, J. Kong, and H. Dai (1999): Integrated nanotube circuits: Controlled growth and ohmic contacting of single-walled carbon nanotubes, *Appl. Phys. Lett.* 75, 627.

- [59] [1999-14] A.S. Vedeneev, J. Li, C. Papadopoulos, A. Rakitin, A.J. Bennett, H.W. Chik, and J.M. Xu (1999): Molecular-scale rectifying diodes based on Y-junction carbon nanotubes, *Proceedings of IEDM 231*.

- [60] [1999-15] J.P.A. van der Wagt (1999): Tunneling-based SRAM, *Proceedings* of IEEE, 87, 571.

- [61] [1999-16] K. Yano, T. Ishii, T. Sano, T. Mine, F. Muri, T. Hashimoto, T. Kobayashi, T. Kure, and K Seki (1999): Single-electron memory for gigato-tera bit storage, *Proceedings of IEEE 87*, 633.

- [62] [2000-01] C.P. Collier, G. Mattersteig, E.W. Wong, Y. Luo, K. Beverly, J. Sampaio, F.M. Raymo, J.F. Stoddart, and J.R. Heath (2000): A [2]catenane-based solid state electronically reconfigurable switch, *Science 289*, 1172.

- [63] [2000-02] F. Leonard and J. Tersoff (2000): Negative differential resistance in nanotube devices, *Physical Review Letters* 85, 4767.

- [64] [2000-03] Y. Ono and Y. Takahashi (2000): Single-electron pass-transistor logic: operation of its elemental circuit, *IEDM Technical Digest 297*.

- [65] [2000-04] M.A. Reed and J.M. Tour (2000): Computing with molecules, Sci. Am. 282, 86.

- [66] [2000-05] T. Rueckes, K. Kim, E. Joselevich, G.Y. Tseng, C.-L. Cheung, and C.M. Lieber (2000): Carbon nanotube-based nonvolatile random access memory for molecular computing, *Science 289*, 94.

- [67] [2000-06] Y. Takahashi, A. Fujiwara, K. Yamazaki, H. Namtsu, K. Kurihara, and K.Murase (2000): Multigate single-electron transistors and their application to an exclusive-OR gate, *Applied Physics Letters* 76, 637.

- [68] [2000-07] M. Wilson, K. Kannangara, G. Smith, M. Simmons, B. Raguse (2000): Nanotechnology, Basic Science and Emerging Technologies, Chapman & Hall/CRC.

- [69] [2001-01] A. Bachtold, P. Hadley, T. Nakanaishi, and C. Dekker (2001): Logic circuits with carbon nanotube transistors, *Science 294*, 1317.

- [70] [2001-02] M. Hanggi and L.O. Chua (2001): Cellular neural networks based on resonant tunneling diodes, *Int. Journal of Circuit Theory and Applications 29*, 487.

- [71] [2001-03] Y. Huang, X. Duan, Y. Cui, L. J. Lauhon, K.-H. Kim, and C.M. Lieber (2001): Logic gates and computation from assembled nanowire building blocks, *Science 294*, 1313.

- [72] [2001-04] D.H. Kim, S.-K. Sung, J.S. Sim, K.R. Kim, J.D. Lee, B.-G. Park, B.H. Choi, S.W. Hwang, and D. Ahn (2001): Single-electron transistor based on a silicon-on-insulator quantum wire fabricated by a side-wall patterning method, *Appl. Phys. Lett.* 79, 3812.

- [73] [2001-05] R. Martel, V. Derycke, C. Lavoie, J. Appenzeller, K.K. Chan, J. Tersoff, and P. Avouris (2001): Ambipolar electrical transport in semiconducting single-wall carbon nanotubes, *Physics Review Letters* 87, 256805.

- [74] [2001-06] R. Martel, H.-S.P. Wong, K. Chan, and P. Avouris (2001): Carbon nanotube field effect transistors for logic applications, *International Electron Devices Meeting. Technical Digest* (Cat. No.01CH37224) IEEE 751.

- [75] [2001-07] M.T. Niemier and Peter Kogge (2001): Exploring and exploiting wire-level pipelining in emerging technologies, 28<sup>th</sup> Annual Symposium on Computer Architecture.

- [76] [2001-08] M.A. Reed, J. Chen, A.M. Rawlett, D.W. Price, and J.M. Tour (2001): Molecular random access memory cell, *Appl. Phys. Lett.* 78, 3735.

- [77] [2001-09] P. See, D.J. Paul, B. Hollander, S. Mantl, I.V. Zozoulenko, and K.-F. Berggren (2001): High performance Si/Si/sub 1-x/Ge/sub x/ resonant tunneling diodes, *IEEE Electron Device Letters 22*, 182.

- [78] [2002-01] D.D. Awschalom, M.E. Flatté, and N. Samarth (2002): Spintronics, *Scientific American*, May.