# Chapter 13

# IMPLEMENTING NEURAL MODELS IN SILICON

Leslie S. Smith University of Stirling

#### Abstract

Neural models are used in both computational neuroscience and in pattern recognition. The aim of the first is understanding of real neural systems, and of the second is gaining better, possibly brainlike performance for systems being built. In both cases, the highly parallel nature of the neural system contrasts with the sequential nature of computer systems, resulting in slow and complex simulation software. More direct implementation in hardware (whether digital or analogue) holds out the promise of faster emulation both because hardware implementation is inherently faster than software and the operation is much more parallel. There are costs to this: modifying the system (for example, to test out variants of the system) is much harder when a full application-specific integrated circuit has been built. Fast emulation can permit direct incorporation of a neural model into a system, permitting real-time input and output. Appropriate selection of implementation technology can help to make simplify interfacing the system to external devices. We review the technologies involved and discuss some example systems.

# 1 WHY IMPLEMENT NEURAL MODELS IN SILICON?

There are two primary reasons for implementing neural models: one is to attempt to gain better and possibly brainlike performance for some system, and the other is to study how some particular neural model performs. Current computer systems do not approach brainlike system performance in many areas (sensing, motor control, and pattern recognition, for example, to say nothing of the higher level capabilities of mammalian brains). There has been considerable research into how the neural system attains its capabilities. Implementing neural systems in silicon can permit direct applications of this research by permitting neural models to run rapidly enough to be applied directly to data. It is true that

increases in workstation performance have allowed some software implementations of neural models to run in real time, but the highly parallel nature of neural systems, coupled with increasing interest in the application of more sophisticated (and computationally more expensive) neural models, has caused interest in more direct implementation to be maintained. Interest in applying neural models to sensory and sensory-motor systems has made attaining real-time performance a critical factor. Real sensory systems are highly parallel, with multiple parallel channels of information, so even though each channel might be implementable in real-time in software, implementing multiple channels implies hardware implementation.

The study of how particular models of neural systems perform is one aspect of computational neuroscience. Such studies are usually carried out in software, since this allows easy alteration of and experimentation with systems. However, models of the highly parallel architecture of neural systems run slowly on standard computers. This has led to interest in the use of parallel computer systems for such models [1, 2] and to interest in silicon implementations. Some researchers in computational neuroscience would like to apply their models directly to real data (implying real-time operation). Even if parallel computers can provide the speed required, it is easier and cheaper to interface silicon implementations to external hardware.

Recently, another motivation for silicon implementation has arisen as well. The continuing applicability of Moore's Law (which states that the number of transistors on a chip doubles every 18 to 24 months) suggests that we shall soon have chips with more than 10<sup>8</sup> transistors but that we may also have chips whose transistors may be relatively noisy. Such large numbers of transistors seem to entail highly parallel algorithms if these transistors are not to sit unused almost all of the time [3]. Further, biological systems seem to produce relatively robust solutions with relatively noisy components, something that standard computer systems cannot achieve. This has led to increased interest in the study and implementation of neural models directly in silicon.

### 1.1 What this review covers—and what it omits

This review covers the implementation of a number of different types of model neuron, ranging from the very simple McCulloch–Pitts neuron to highly complex multicompartment models. It includes implementations of integrate-and-fire neurons and other models of intermediate complexity. It does not cover those silicon chips that are primarily concerned with using these neural models to solve a particular problem. We do describe some of the implementation techniques used for the back-propagated delta rule and the Boltzmann machine, but we do not review all these chips, concentrating instead on specific issues such as synapse implementation or noise. A more detailed review of such chips may be found in [4].

# 1.2 Organization of this review

We start by outlining the organization and structure of a real neuron. This overview will allow us to see the different aspects of neuron behavior that are

being modelled. We review the different types of models for neural systems that have been proposed, differentiating between those that deal with simple vector input (in which time is either irrelevant or occurs only in terms of the order in which the input vectors are presented), and those in which the precise timing of the inputs matters. We then discuss the different technologies for implementation and describe how different types of model neurons have been implemented. We discuss some applications, and consider what has been and can be expected to be achieved by using these different implementation technologies.

### 2 AN OUTLINE OF A REAL NEURON

Real neurons, like all real cells, are very complex. The aim of this subsection is to describe a neuron at a level of detail and in a language that is informative to a wide range of scientists and that can also be used to illustrate what is actually being modeled in particular implementations. A detailed neurophysiological description of real neuron operation may be found in [5], part II, and in [6].

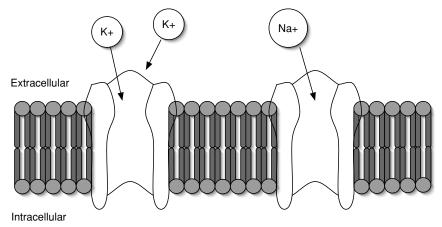

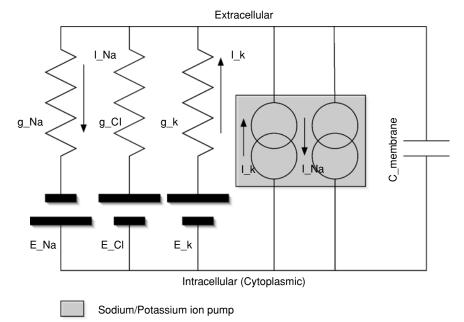

There are many different types of neurons, and these very enormously in morphology (shape) and extent, as well as in the details of their biophysics. Neurons are found in a very wide range of animal species: invertebrate, insect, and vertebrate. What they all share is operation using electric charge. The operation of the neuron relies on the neuron's excitable membrane. The membrane of any cell is its outermost layer: its boundary. In neurons, this membrane is a bilipid membrane that contains ionic channels (see Figure 13.2). What makes the membrane excitable is the way in which its characteristics alter depending on the (localized) voltage across the membrane. The purely bilipid part of the membrane is essentially a very thin insulator, separating the relatively conducting electrolytes inside and outside the cell. The ionic channels (and there are many different types of ionic channel) embedded in this membrane allow selected (charged) ions to cross the membrane. Unbalanced movement of ions into and out of the neuron alters the potential difference between the inside and the outside of the neuron (see Figure 13.3). The ions of particular significance here are potassium  $(K^+)$ , sodium (Na<sup>+</sup>), and calcium (Ca<sup>++</sup>). There is some disagreement as to whether ion channels are static or can move around inside the membrane [7].

In the absence of any input to the neuron, the excitable membrane will maintain the inside of the neuron at a particular potential relative to the outside of the neuron. This resting membrane potential is usually on the order of -65 mV (millivolts) (though this does vary across different populations of neurons). This resting potential results from the movement of ions, primarily due to the different ionic concentrations inside and outside of the neurons, and this is maintained by the Na<sup>+</sup>-K<sup>+</sup> pump which keeps the Na<sup>+</sup> concentration inside the cell low and the K<sup>+</sup> concentration inside the cell high (see Figure 13.3). External inputs to the neuron result in the increase of this potential (known as *depolarization* in the neurophysiology community) or decrease of this potential (*hyperpolarization*).

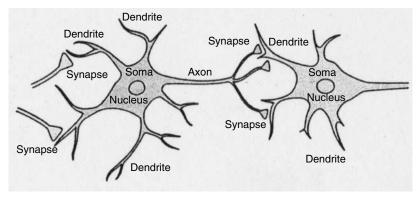

Before discussing the details of how this potential changes, we consider the overall structure of a neuron: see Figure 13.1. The neuron has a cell body (the soma), and in most neurons, this has projections. These projections are of two types: the dendrites and the axon. The dendrites have a treelike structure (hence

**Figure 13.1.** Overall structure of a neuron (actually, a local interneuron). Figure modified from [5] (Figure 2.8), with permission.

**Figure 13.2.** Patch of cell neuron membrane. Ion channels are embedded in the bilipid membrane. The membrane is made up of molecules each with a hydrophilic end (circle) and a hydrophobic end (lines), and is impermeable to ions. There are many types of ion channels, each consisting of a protein embedded in the membrane: different proteins have different permeabilities to ions because of the conformation of the protein. Additionally, the protein confirmation itself may be dependent on the voltage across the membrane, so the ion channel's behavior may be dependent on the voltage across the membrane as well.

their name, which comes from the Greek  $\delta\epsilon\nu\delta\rho\rho\nu$  [dendron], a tree) and are located where inputs to the neuron arrive. The axon, which also has a branching structure, transfers the output of the neuron to other neurons. These two projections can be difficult to tell apart in electron micrographs, but they have different populations of ion channels in their membranes, and they function in different ways.

Connections between neurons take place at synapses. Mostly, each synapse is between the axon of one neuron (the presynaptic neuron) and the dendrite of

<sup>&</sup>lt;sup>1</sup>There are also axo-axonic and dendro-dendritic synapses, as well as axonic synapses that contact the cell body.

**Figure 13.3.** Equivalent circuit of a patch of membrane. The arrows show the direction of the ion movement (which is the same direction as current transfer). The sodium–potassium pump maintains the inside of the cell at a negative potential (more  $Na^+$  ions are transferred out than  $K^+$  ions are transferred in). The capacitance is provided by the (insulating) bilipid membrane.

another neuron (the postsynaptic neuron). It is through the synapse that the potential at that point in the presynaptic axon alters the potential at that point in the postsynaptic neuron's dendrite. Brains contain a large number of highly interconnected neurons, and each interconnection consists of a synapse. Some neurons (e.g., cortical pyramidal neurons) may have as many as 10,000 synapses on their dendrites. There are therefore a very large number of synapses in animal brains. According to Koch [6], in primates there are about 100,000 cells, and about  $6 \times 10^8$  synapses per cubic mm in the cortex.

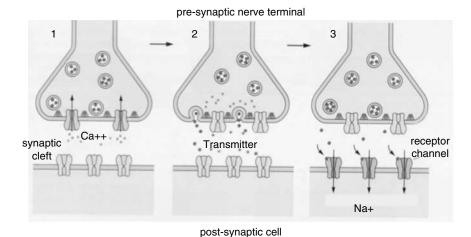

In an animal brain, synapses are of many different types. Actual synaptic operation is complex. Many synapses operate by releasing small bubbles (called *vesicles*) of a chemical (called a *neurotransmitter*) from the presynaptic axon into the space (called the *cleft*) between the presynaptic axon and the postsynaptic dendrite (see Figure 13.4). In one type of synapse (ionotropic), this process directly affects the ionic channels on the dendrite, causing some of them to open and to allow influx or efflux of ions, altering the potential at that point in the postsynaptic dendrite. In another type of synapse (metabotropic), the effect is less direct, altering the ion transport of neighboring proteins. Clearly, both types of synapse require some time for the effect of the presynaptic pulse to be felt post-synaptically, and this effect (called *postsynaptic potentiation* or *PSP*) takes some time to decay as well. There are many types of both ionotropic and metabotropic synapses (often classified by the neurotransmitters used). Ionotropic synapses are faster in operation than metabotropic synapses.

**Figure 13.4.** Diagram showing the operation of an ionotropic synapse. Modified with permission from [5] (Figure 10.7).

When the potential alteration is depolarizing, the synapse is said to be *excitatory*, and when the potential alteration is hyperpolarizing, the synapse is said to be *inhibitory*. These small alterations in potential are summed on the dendrites. On many neurons, this summation appears to be essentially linear within a certain range of potentials: outside of this range, ion channels alter their configuration, and the dendrite ceases to be linear. This nonlinearity may occur at some small portion of the dendrite, due, for example, to many nearby synapses being simultaneously stimulated. On some neurons, synapses are located on spines on the dendrite (spiny neurons, as opposed to smooth neurons), leading, it is believed, to greater ionic and electrical isolation of each synapse. Some researchers believe that the dendrites perform a considerable amount of processing (the neurophysiology is discussed in Section 19.3.2 of [6], and modeling in [8]), and that there are essentially nonlinear processes operating on the neuron that provide neurons with considerable information processing power.

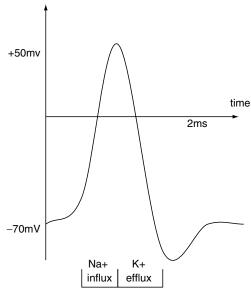

In many neurons, it is the potential at a particular part of the neuron, the axon hillock (located on the soma of the neuron, at the root of the axon projection) that is of particular importance. At this trigger zone on the neuron, there is a large concentration of particular types of sodium channels. The result is that when the voltage at this location increases beyond a certain threshold value (usually about -48 mv), a particular set of voltage-sensitive ion channels opens and allows the influx of Na<sup>+</sup> ions, rapidly increasing the depolarization. This results in even more of these channels opening, causing a very fast and large rise in the membrane potential. As a result of this increased depolarization, two things occur: firstly, the sodium ion channels close, and secondly, another set of ionic channels opens, allowing the efflux of a different set of ions (K<sup>+</sup>), causing the potential to drop nearly as rapidly as it rose (see Figure 13.5). This potential increase and decrease is regenerated along the axon, resulting in a spikelike signal passing along the axon, arriving at the synapses that this axon makes. Because the spike is regenerated, its shape is characteristic of the mechanism of its production and does not carry information. It is worth noting that (1) the sodium ion

Figure 13.5. Graph of depolarization on an axon during an action potential (spike).

channels are not able to reopen immediately, so there is an inbuilt maximal rate at which these spikes can be produced by the neuron, and (2) the potassium efflux normally overshoots, causing a brief after-spike hyperpolarization. The delay in the reusability of the sodium channels results in the neuron's absolute and relative refractory period: that is, the period during which the neuron cannot fire again, and the period during which it is more difficult for the neuron to fire again.

The actual propagation speed of the spike is relatively slow due to both the nature of the conductance and the distributed resistance and capacitance of the axon. It can be speeded up by a process known as myelinization. In myelinization, glial cells form a myelin insulation a round the axon, reducing its capacitance, and allowing the spike to jump (by electrical conductivity, rather than by regeneration) from point to point (actually, to breaks in the myelin, known as Nodes of Ranvier) along the axon. Actual propagation speeds vary from 1 mm/sec to 100 mm/s inside brains (and faster along peripheral nerves).

Not all neurons actually produce spikes: some output graded potentials. Indeed, not all neurons have actual dendrites: some receive synapses only on the soma itself. In many synapses, the alteration in potential produced depends also on the potential at the synapse. In particular, some synapses (shunting synapses) tend to drive the potential back towards the resting potential (and thus are either excitatory or inhibitory, depending on the local potential). In addition, synapses do not always have exactly the same effect postsynaptically as a result of a presynaptic spike. Many synapses are depressing synapses: the effect of the first few spikes (after a period of presynaptic inactivity) is much larger than that caused by later spikes. Other synapses are facilitating: after a period of presynaptic inactivity, the effect of a train of spikes gradually increases. These effects appear to be due partly to depletion of presynaptic neurotransmitter, and partly to changes at the membrane on the postsynaptic dendrite (see [9], chapter 10).

One important aspect of real neural systems is that they alter in response to their inputs. They adapt, so identical inputs at different times can have different effects. This adaptation takes place over many time scales: it may occur rapidly, as a result of a single event, or very slowly over the lifetime of the animal. Early in the animal's life, the neural system grows. There is a great deal of evidence that the stimulation it receives is critical in adjusting the processing that takes place to the actual input arriving (e.g., in vision: see chapter 56 of [5]). In mammals many synapses are formed but do not last. Changes inside the system take many forms: in addition to growth and decay of synapses, there are structural and biochemical alterations at synapses, alterations in neuron morphology, and subtler changes due to hormones and diffusable neurotransmitters such as nitrous oxide (NO) and peptides. Neural models have tended to focus almost exclusively on changes at synapses. In addition to the short-term synaptic alteration above (called dynamic synapse behavior), synapses can also become stronger over a longer period (long-term potentiation, LTP), or become weaker over a longer period (long-term depression, LTD). Somehow, out of all these forms of adaptation, the system appears to learn: we see systemwide changes that provide appropriate changes in behavior.

There are many views on how much of the detail of the behavior of neurons is important for understanding their information-processing capabilities. These views range from the view that only the firing of the neuron matters to views that voltage-based processing on the dendrite is crucial in information processing, to views that it is the detail of the quantum effects upon the movement of ions and the conformation of proteins that matter. Some believe that the firing of neurons is essentially for information transfer, and that what happens on the dendrites is critical to information processing (see [6] chapter 20, and [10]). These differences in beliefs are at the root of the many models that we will now describe.

# 3 SIMPLE (TIME-FREE) NEURON MODELS

The simplest neural models do not include time: that is, each neuron's input is considered as a vector, and the output is computed from this input without regard for what the neuron's previous input (or output) had been. There is no internal state inside the neuron that would allow previous inputs to affect current operation. Networks of such neurons can be made sensitive to previous inputs if the network contains loops (because the state information is contained in these new inputs), but even then, these networks are sensitive only to the order of the inputs and not to their actual timing. This type of neuron model is the basis for most of the current work in neural networks for pattern recognition. Such models have been implemented on analogue computers, digital computers, and in various types of hardware.

#### 3.1 The McCulloch–Pitts model

The earliest model was the McCulloch-Pitts neuron [11]. This model forms the weighted sum of its (vector) input and produces a binary output, which is 1 if the weighted sum exceeds some threshold, and 0 otherwise. This can be written

$$A = \sum_{i=1}^{n} w_i X_i \tag{1}$$

followed by Y = 1 if  $A > \theta$ , and Y = 0 otherwise. Here  $w_i$  is the weight characterizing the synapse from input i,  $X_i$  is the ith input, A is the activity of the neuron,  $\theta$  is the threshold, and Y is the neuron's output.

The model has been formed by (1) considering each spiking neuron as a two-state device, in which the neuron is either firing (output = 1) or not (output = 0), and (2) considering each synapse as characterized by a single number  $(w_i)$ . An excitatory synapse has  $w_i > 0$ , and an inhibitory synapse has  $w_i < 0$ . The effect of the presynaptic neuron on the postsynaptic neuron is found by simple multiplication. The overall effect of all the presynaptic neurons—the activity, A—is a simple linear sum: the dendrite is reduced to a single point. The nonlinearity is introduced only at the end, where the activity is thresholded to produce the output.

What makes this very simple model interesting is that it can be used to do computation. It is straightforward to design simple NOT, AND, and OR gates, and these can be assembled to provide any logical predicate. The addition of a clock allows one to build a digital computer from such devices.

## 3.2 Learning systems

Many extensions to this simple model have been proposed. In terms of basic operation, these extensions have often been relatively minor, such as graduating the output. The knowledge that real neural systems are not preprogrammed (at least in vertebrates) but adapt or learn has been very influential, partly because useful adaptation has proven very difficult to achieve in traditional computer systems, and partly because there are many problems for which a purely algorithmic solution is virtually impossible to find, whereas examples of correct behavior are quite simple to produce. A system based on learning might be able to solve such problems.

The earliest form of neural learning was suggested by Hebb [12]. In this form of learning, synapses that connect neurons that fire together are strengthened. This type of learning can be applied to make simple learning systems. These have been investigated in the context of both time-free models and models that include time: in the time-free case, they can provide a basis for certain self-organizing systems [13]. We will discuss the case including time in more detail in Section 5.4.3. We first discuss learning systems that have a teacher: that is, learning systems in which there is a known correct output for many of the possible inputs. We return to systems without a teacher in Section 3.3.

#### 3.2.1 Perceptrons

One of the earliest learning systems was the perceptron [14], in which some of the geometry of the dendrite was reintroduced. What the perceptron is best known for is the perceptron learning rule [14]. This rule (described in many Neural Networks textbooks, (e.g., [15,16])) was the first one discussed that allowed the neural model to adapt itself so as to produce the desired input:output mapping. It was limited to a single layer of simple perceptrons (i.e., perceptrons

which had the dendrite geometry removed) with binary outputs (which are the same as McCulloch–Pitts neurons), but was shown to be able to generate any logical predicate that this architecture could permit. This was the first truly adaptive system, and it was hugely influential. It led to various forms of implementation (see Section 5).

#### 3.2.2 The Delta rule

The Delta rule is another learning algorithm for the same architecture [17, 18]. This rule minimizes the Euclidean (least squares) distance between the actual output and the desired output by adjusting the weights (and is sometimes known as the *least mean squares rule*). It is applicable to units whose output is a continuously increasing function of the weighted sum of the inputs. The unit output function may be linear (i.e., the output is simply a constant times the activity A from Equation 1), or may be a squashing function such as a logistic:

$$Y = 1/(1 + \exp(-k_1 A + k_2))$$

(2)

where Y is the output, and  $k_1$  and  $k_2$  are constants that determine the magnitude and location of the maximum slope. The logistic function has a value that is always between 0 and 1. Other squashing functions (e.g., tanh) have also been utilized. Again, it has been shown that the Delta rule can produce any output that the particular single-layer architecture could produce, and given small enough weight changes, will converge to a solution (see, e.g., Section 5.4 of [15]). The way in which the network is used is that a set of (input, output) pairs is produced, and these are then applied to the network as the input and the desired output for this input. The weights are then adjusted to reduce the error: that is, the square of the sum of the differences between the desired and actual outputs.

However, the limited computational ability of the single-layer architecture was proven in [19]. The architecture can only produce linearly separable mappings. Minsky and Papert's doubt as to whether it could be extended either to more complex perceptron networks or to a larger class of functions led to a decrease in the effort extended in neural computing (see [15], Section 1.2) in the 1970s and early 1980s.

### 3.2.3 The Hopfield network and the Boltzmann machine

Two new adaptation algorithms were introduced for similar types of neurons in the early 1980s, one for binary neurons (the Hopfield model, and its extension, the Boltzmann machine), and the other an extension of the Delta rule (the backpropagated Delta rule). Both of these networks were hugely influential, and both were implemented in various forms in hardware.

Hopfield's network [20] is symmetrical: that is,  $w_{ij} = w_{ji}$ , where  $w_{ij}$  is the weight from presynaptic neuron j to postsynaptic neuron i. This network is not a simple layer of neurons, but has cycles. Updating the network was done neuron by neuron, asynchronously, and the Hopfield proved that the network eventually settles into a stable state. It was therefore the first network to have a dynamical behavior, although this was not normally used in its operation. The network is considered to have an overall energy

$$E = -\frac{1}{2} \sum_{i,j=1}^{N} w_{ij} X_i X_j$$

(3)

where the neuron's output,  $X_p$  is either +1 or 1, rather than +1 or 0, and updating each neuron's state minimizes this total energy, E. The network could be trained to be an associative memory by applying the vectors to be stored and then adjusting the weights so as to minimize E. Hopfield and others (as is clearly explained in [15]) showed that such a network could remember a maximum of 0.138N vectors. These could be recalled by providing the network with an incomplete vector, thus providing content-addressable memory.

An important extension to this network was the Boltzmann machine [21]. In this network, the original Hopfield network is extended by adding new nodes that are not connected to the outside world. These so-called hidden nodes can learn to form internal representations that can allow the network to learn additional vectors and can be used to allow the network to classify its inputs by examining the hidden unit state. However, the learning technique also has to change (since the Hopfield learning recipe cannot train weights to and from hidden nodes). The learning algorithm used is statistical in nature: essentially, it uses concepts from statistical physics and Boltzmann distributions (hence the algorithm's name) to set these weights. A comprehensible description may be found in [15], chapter 7 or in [16], chapter 11. Using such techniques in software is exceedingly slow. However, the idea that this type of network could learn some form of internal representation helped rekindle interest in the whole area, and the slowness of the algorithm in software helped motivate implementations of this type of network in silicon.

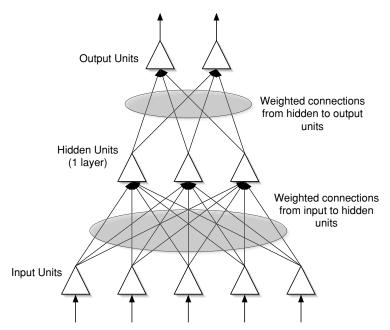

#### 3.2.4 The back-propagated Delta rule

The best known of the simple neural network learning rules is the back-propagated Delta rule. Discovered independently at least five times [22–26], it permits a Delta rule like network to be extended from a simple single layer to a feed-forward network (see Figure 13.6). The basic idea is that errors at the output layer are funneled back to the units of each hidden layer: for details see any book on neural networks, e.g., [15] chapter 6, or [16], chapter 4. Once the error at a unit is known, it can be used to adjust the weights to that unit, essentially using the original Delta rule.

There are two problems with the back-propagated Delta rule: firstly, it is no longer the case that continued application of the learning rule will necessarily allow the network to learn the input:output mapping, even although it may be possible for the architecture to do so; and secondly, learning tends to be slow. The result of the first problem is that one cannot be sure that the network produced is the best network possible given the (input:output) pairs that have been provided. So-called local error minima can result in the network stopping learning before it has done as well as it can. Further, if the (input:output) pairs contain some noise (perhaps the result of measurement errors), it is quite possible for the network to attempt to learn this noise. A great deal has been written about the best ways in which to use this type of network. Certainly, like the Boltzmann machine, it is capable of extracting information about the (input:output) pairs provided and coding this into its weights. Learning is slow because the mapping

**Figure 13.6.** Feed-forward neural network. The input layer simply transfers its inputs through (adjustable) weighted synapses to the hidden layer. There may be a number of hidden layers, with different numbers of units. The radial basis function network [16] has a similar structure, with one hidden layer, whose units have a peak response at one point in the input space.

between the weights and the error (the so-called error surface) can be very complex: gradient descent methods applied to high-dimensional complex surfaces must move slowly because they otherwise risk missing the desired minima of the surface. The error surface may also contain local minima: if the weights are trapped in one of these, the performance will be suboptimal.

Because of the wide possible applicability of this network, and because it is slow to train, many attempts have been made to implement it directly into hardware. These are reviewed in Section 5.3.

Many extensions to this rule have been described and many have been concerned with improving the form of the gradient descent, attempting to make it closer to steepest descent (some are described in [16], chapter 4). Others have attempted to replicate the hidden layer's effects by recoding the input. The idea here is that what the back-propagated Delta rule does in its hidden layers is to recode the input so that the mapping from the recoded input to the output becomes separable, thus permitting the Delta rule to be used. This is essentially the basis for the Radial Basis Function network [27], (see also [16] chapter 5), which performs recoding and uses the simple Delta rule between the recoded input and the desired output.

Bishop [28] has shown that these types of network essentially implement a form of statistical algorithm. This does not reduce the utility of these systems, and indeed helps to explain why they are so useful. However, it does show that the

limitations of this type of algorithm are essentially the same as the limitations of the statistical techniques.

#### 3.2.5 Learning sequences

All the above rules can be turned into systems that learn sequences of inputs, either classifying the sequence or attempting sequence completion. In such sequences it is the order of the elements, not their precise times, that matters. Learning can be achieved in a number of ways: a window through the sequence can be used as the input to the network (i.e., the last *n* elements of the input are used as input, and the output target might be the next element in the sequence), or a network with loops may be used, in which case information about the previous sequence element is held internally inside the network (see, e.g., [29]). What networks of these types cannot achieve is learning anything that requires information about the precise timing (as opposed to order) of the input vectors.

# 3.3 Self-organizing systems

Self-organizing systems are systems that adjust their behavior in response to their input. No correct output is provided: instead, the system adjusts its internal parameters so as to detect some regularity in the input. Such situations commonly occur in sensory perception: the input is of very high dimensionality (for example, there is one value per light sensor in a camera system, or one value per bandpass filter in a sound sensor), yet although this suggests a very high number of possible inputs, real inputs are confined to some relatively small subspace. In other words, the probability distribution functions of each of the (scalar) inputs are not independent. It is usually the case that the aim of self-organizing systems is to adjust the weights in the system so as to produce outputs (usually of lower dimensionality than the input) that catch the important aspects of the variation in the input.

The idea of neural processing as data reduction goes back to [30]. Simple Hebbian learning systems have some utility in this area: consider a number of inputs that converge on a single output. Assume that the synapses are excitatory, and that a number of coincident inputs are required to make the output neuron fire. Inputs which co-occur in large enough numbers to make the output unit fire will tend to increase their weights, making the output neuron more sensitive to these inputs. However, simple Hebbian learning alone fails to work effectively because the weights increase without limit. Below, we discuss two algorithms that add something to Hebbian learning and that have been candidates for silicon implementation. A useful introduction to this field may be found in [16], chapter 8.

#### 3.3.1 Learning vector quantisation

Learning vector quantization (LVQ) is used to map a number of inputs (each with a scalar value) into one of a number of outputs. LVQ is one of a class of algorithms known as competitive learning algorithms (see [15], chapter 9). This class of algorithms clearly produces outputs of lower dimensionality: the mapping is from some subset of  $R^N$  to  $\{1..M\}$  where N is the number of inputs and

M the number of output units. Normally, all the input units have synapses to all the output units, initially with random weights. The learning algorithm has a Hebbian aspect, in that weights between input units and output units that fire are increased. However, usually only one output unit is allowed to be active at a time, and the weights to that unit are adjusted in such a way that the total weight (or the total squared weight) remains the same. Some variants also reduce the weights on some of the synapses on inactive output units.

LVQ algorithms are of particular interest in compressive coding: by replacing the input vector with the code for the output unit that best represents it, a very considerable reduction in data volume can be achieved. Further, the LVQ network adjusts itself to the statistics of the data. Because such coding is frequently required in real time (for example, for transmitting coded images), there is considerable interest in the hardware implementations of LVQ systems.

#### 3.3.2 The Kohonen mapping network

The Kohonen mapping network is a variant of LVQ in which not only the weights of the winning unit are adjusted but also weights to nearby units are adjusted (see [16], chapter 9, or [31]). This description presupposes a definition of "nearby", forcing the designer to place some form of topology on the output units. For example, the output units might be organized in one dimension (as points on a line or a circle) or in two dimensions (as points on a grid or on the surface of a sphere or cylinder or torus). The network is trained by being exposed to many input vectors, and the weights to the output units are adjusted. Usually, the number of units whose weights are adjusted for each winning pattern is gradually reduced.

After training, novel inputs will normally result in some localized area of the output units being activated. In this way, high-dimensional data are mapped into some area on a surface. Such data compression can be very useful for sensory information, for example, in robotics or surveillance. Often the requirement is that training can be relatively slow, but operational results are required quickly for real-time applications. This situation has led to interest in silicon implementations of this technique.

#### 4 MODELS THAT INCLUDE TIME

Model neurons that include time are those in which the actual timing of the input (as opposed to the order of the input) matters. Models of this form can be sensitive to the actual timing of their inputs, as opposed to their order: the neurons contain internal time-varying state. The simplest form of neural model that includes time is the integrate-and-fire model. Such neurons can process general time-varying signals, but their outputs are normally spike trains. In common with spike trains of real neurons, the actual shape of the spike is irrelevant. All that matters is the timing of the spike. Thus, the output can be characterized by

$$S = \{t_i : i = 1 \dots n\}, \, t_i < t_{i+1}$$

where  $t_i$  is the time of the *i*th spike train in a train of *n* spikes. More complex models model the neuron in more detail, sometimes including the membrane itself and sometimes including the actual production of the spike.

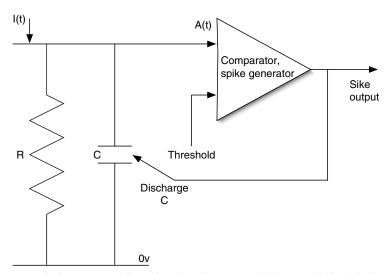

## 4.1 The leaky integrate-and-fire model

The leaky integrate-and-fire neuron has a very long history: the concept can be traced back to 1907 [32]. In this neuron model, the dendrites are modeled as single points at which the synaptic inputs are summed, while current leaks away linearly: a detailed description can be found in [6], chapter 14. Below threshold, the voltagelike state variable at that point, A, is described by the equation

$$\frac{\mathrm{d}A}{\mathrm{d}t} = -\frac{A}{\tau} + I(t) \tag{4}$$

where  $\tau$  is the time constant of the point neuron (i.e., a [reciprocal] measure of its leakiness), and I(t) is the total external input to the neuron (see Figure 13.7). In the presence of positive input, the activity A can rise to the threshold  $\theta$ . When this threshold is crossed from below, the neuron emits a spike, and A is reset to some initial value. The mechanism of spike generation is generally ignored in the model, and the output is characterized entirely by the sequence of spike times. This type of neuron is sometimes known as a *point neuron*, because all the geometry of the dendrite has been shrunk to a single point. If R is infinite, then the neuron is not leaky, and it simply integrates its input until it reaches the threshold. If  $\tau$  is small, then more recent inputs have a larger effect on A. If I(t) is made up of a number of excitatory synaptic inputs, each of which is not large enough to cause A to exceed  $\theta$ , then the neuron will act as a coincidence detector, firing when a number of its excitatory inputs occur at about the same time, allowing A to reach  $\theta$  in spite of the leakage.

**Figure 13.7.** Leaky integrate-and-fire unit. The resistor R models the overall (fixed) leakage of the membrane (if omitted, there is no leakage), and the capacitor C models the overall capacitance of the membrane. The time constant  $\tau = RC$ . When a spike occurs, the capacitor is discharged.

#### 4.1.1 Other point neuron models

The leaky integrate-and-fire model is the best known (and most frequently implemented) of the models that represent the dendrite as a single point. Another important model is Gerstner's spike response model [33,34], in which the threshold is dynamic and the shape of the postsynaptic potential is modeled. The dynamic threshold permits the neuron's refractory period and relative refractory period to be included in this relatively simple model.

In Equation 4, the leakage is linear. Feng and Brown [35] suggest a nonlinear leakage coefficient (equivalent to making  $\tau = \tau(A)$ ), with the result that under certain conditions, inhibitory input can increase the firing rate [36]. Izhikevich [37] reviews a number of point neuron type models, both from the point of view of neural plausibility and computational efficiency. Not surprisingly, the more biologically plausible models take much more computing time. Izhikevich has proposed a new model [38] based on bifurcation analysis, which can generate realistic neural output from a simple simulation.

#### 4.2 More detailed neuron models

Compartmental neuron models divide up the neuron into a number of sections (or compartments), each of which is modeled individually, with electrical current feeding into neighboring sections. The advantage is that the whole neuron (soma, dendrites, and axon) may be modeled with a degree of accuracy that can be determined by the modeller. The morphology may be simulated (at least as far as branching and neurite diameter is concerned), and each section may be given different properties. The usual techniques are based on the Hodgkin–Huxley equations (see [6], chapter 6, and [5] chapter 7), and these allow different populations of ion channels in each compartment to be modeled. Essentially, a nonlinear leakage current is associated with each ion type. There are some standard simulation tools developed for this type of simulation, most notably Neuron [39].

There are also simplified models, often based on the Hodgkin–Huxley equations—for example, the FitzHugh–Nagumo equations and the Morris–Lecar equations (both reviewed in [6], chapter 7, and discussed in terms of computational efficiency in [37]). Indeed, Feng and Brown's model [35] is a version of the FitzHugh–Nagumo model. These models can aid the speed of computation (in software) and possibly the complexity of a hardware implementation.

# 4.3 Learning in models that include time

Neural models that include time generally have a spike-based output. This spike output may be thought of either as coding a value in terms of its instantaneous spiking rate (rate coding) or by the precise timing of the spikes. In rate coding (and also in the case where the output is not a sequence of spikes, but a continuously varying value), it is possible to apply, for example, Hebbian-type learning rules as discussed in section 3.2. There are no equivalents of the Delta rule or the perceptron learning rule that make specific use of these types of code. These learning rules are based on the idea of a single vector input producing a single vector output. One can still use this formulation of a network that uses

rate-coded spiking neurons, but no advantage is being taken of the neurons including time.

Although rate-coded and graded-output neurons clearly can have more sophisticated learning rules, there has been more interest in learning rules for spike timing-coded neurons. This case is of particular interest to computational neuroscientists, since it may inform brain science. There has been particular interest in temporal versions of Hebbian learning rules (reviewed in [40] and also in chapter 10 of [34]). To apply Hebbian learning to spiking neurons, we need to reconsider what "firing together" means: the usual view is that, for excitatory synapses, those whose postsynaptic currents assist in making the postsynaptic neuron fire are strengthened, while those whose postsynaptic currents do not help are weakened. Generally, these new rules do not alter synaptic strength unless the postsynaptic neuron fires: thus their effect is to strengthen synapses that were active just before the postsynaptic neuron fired and to weaken those that were active just after the postsynaptic neuron fired. Although such learning rules have not yet been demonstrated to be effective in applied neural networks, there is considerable interest in silicon implementations of this type of rule (see Section 5.4.3).

# 5 TECHNIQUES FOR HARDWARE IMPLEMENTATION

Hardware implementation of neural models and networks of neural models can allow these systems to operate in real time and to use the massive parallelism inherent in these types of design. Sequential computers cannot provide true parallelism, and parallel computers are expensive: further, there is often a mismatch between the very intense intercommunication required for neural computers and the relatively low bandwidth parallelism provided by the cheaper forms of parallel computer, such as networks of transputers or Beowulf clusters [41].

In fact, direct hardware implementation of neural systems and networks has a relatively long history. Prior to the advent of the workstation, neural modelers were forced either to use mainframe computers or to develop their own hardware. Models of excitable membranes using discrete components were developed [42–45], as well as full neurons [46]. More computationally oriented models of perceptron-based machines were built [47,48]. This chapter is not the place for a full review of this historically interesting material: however, the history does show that dedicated hardware for neural systems is not a new idea. Modern neural hardware developers are primarily interested in chip-based implementation. This focus has certainly made the resulting hardware smaller (the neural model of the avian retina developed by Runge et al. [49] ran to 50 circuit boards!), though more difficult to test and modify.

There are many possible ways of organizing a review of implementations of neural models. In a much earlier article [50], these were organized by chip type. In [4], they are organized by actual chip, and in [51], a table of chips and their characteristics is provided. Here, we review some of the issues, then discuss the analogue versus digital issue, and then look at the question of whether the implementations use static (time-free) or dynamic (including time) approaches.

## 5.1 VLSI implementation of neural models

Chip-based implementations are very attractive to the neural system implementor. Not only are they small (and easily incorporated into complete systems) but also most design systems proffer at least some facilities for testing the design prior to actual chip manufacture. Further, if the implementation is successful, the designer will normally receive a number of chips, allowing more than one researcher to work with the implementation. In addition, reusing designs or sections of designs is relatively straightforward. However, implementors of neural systems in silicon do not have the luxury of developing a new silicon technology, and so must use technologies that were developed for other purposes, such as for high-speed digital processors.

The basic implementation techniques are summarized in Table 13.1. There are many different possibilities within each of these classes of implementation technique. Analogue implementations are normally custom integrated circuits. These may use the linear range of the field-effect transistors (above threshold) or the very-low-power exponential part of their range (subthreshold). Digital implementation techniques range from software (i.e., implementation on a normal computer) to field-programmable gate array (FPGA: a technology in which an array of electrically programmable gates can be interconnected in an electrically programmable way) to application-specific digital integrated circuits (digital ASIC). Of course, these technologies may be mixed, even on the same chip. We note in passing that field-programmable analogue arrays (FPAAs) are in development (see, for example, [52]), although they are not yet nearly large enough to replace complex analogue ASICs. The downside of hardware implementation is the length of the timescale from design (or modification) to implementation. For all the hardware implementation techniques (except FPGA), change of design means refabrication, and this process generally takes months. On occasion, focused ion beam (FIB) machines (see, e.g., http://www.feico.com/support/fiblab.htm) can be used to modify devices, but this option is often not available, or else is inappropriate for the modification required. FPGAs can be reprogrammed quickly: they are a technology with aspects of both hardware and software.

In Table 13.1, the "Degree of Implementation" [53] column relates to the extent to which all the elements of all neurons exist as separate hardware components. Fully implemented systems have identifiable (and different) circuit elements for each entity being modeled. Real neural systems are fully implemented. Most analogue implementations are also fully implemented. However, full imple-

**Table 13.1.** Summary of characteristics of different implementation techniques for implementing neural systems.

|                           | Degree of      | Real-time   | Power       |                |

|---------------------------|----------------|-------------|-------------|----------------|

| Implementation Technology | Implementation | Speed       | System      | Consumption    |

| Subthreshold a VLSI       | High           | High        | Yes         | Very low       |

| Above threshold a VLSI    | High           | Very high   | Yes         | Medium         |

| dVLSI                     | Low            | High        | Possible    | Medium to high |

| FPGA                      | Low-medium     | Medium      | Possible    | Medium to high |

| Workstation software      | Minimally low  | Low         | Not usually | High           |

| DSP based software        | Low            | Medium-high | Possible    | High           |

mentation is not usually possible for digital VLSI implementations since replicating, e.g., digital multipliers at each synapse would make the circuit impossibly large: instead, the same functional unit may be reused frequently. For example, one digital multiplier may well be used as part of the implementation of many synapses. Such a virtual design (again using the terminology of [53]) trades off the speed of the functional unit against its area and the switching involved in multiplexing signals to the functional unit. By careful design, real-time performance may still be possible, but even with fast digital electronics, it is not guaranteed. FPGA- and DSP-based implementation are not normally fully implemented. Depending on the design chosen, component re-use will occur to a greater or lesser extent. Pure software implementations use the CPU(s) of the workstation for all computational tasks and have the lowest degree of implementation. Even implementations on parallel sets of workstations (e.g., Beowulf) simply tend to distribute the different parts of larger simulations across a number of workstations. DSP chips are also software driven and are normally controlled from a workstation. The degree of implementation depends on the details of the design (for example, on the number of chips used). The systems are easily reconfigurable, but because they are special purpose, they require specific software packages and can be difficult to program.

# 5.2 Analogue or digital VLSI

The first choice facing a designer intent on implementing a neural model in VLSI is whether to use an analogue or a digital design. If an ASIC is being produced, it is very likely that the technology being used for chip manufacture might have been developed for digital designs. When the implementor is attempting to build an analogue ASIC, or, indeed, any target except a digital ASIC (for example, a mixed (or hybrid) design: part digital and part analogue), problems arise. The quoted feature size for a particular technology ( $\lambda$ ) is intended for use in the production of digital gates. For such gates, all that matters is that the realized circuit conforms with the designed circuit and that the switching voltage between an FET being on and off is within a particular range. For above-threshold analogue VLSI, the implementor is attempting to use the linear part of the transistor's characteristic, and so is reliant on the actual placing and shape of the transistor's  $I_{ds}/V_{gs}$  characteristic. This reliance can lead to matching problems, though it does appear to be the case that these problems are not major. However, for subthreshold aVLSI, the designer is reliant on the characteristic of the transistors before they turn on (i.e.,  $I_{ds}/V_{gs}$  below threshold). This is not a characteristic that digital chip designers generally care about since it does not impact on their designs.

Why then would anyone consider analogue implementation? We discuss below some of the differences in implementation characteristics implied by these two different approaches.

#### 5.2.1 Signal coding

The primary difference between digital and analogue systems is in how signals are coded. Digital signals are discrete values, valid at specific instants, and analogue

signals are continuous values in continuous time. In a digital system, the two primary parameters of a signal are sampling rate and sample length. In an analogue system, the parameters are bandwidth, slew rate (maximal rate at which a signal can change), noise level, and drift. (Drift causes the analogue signal to change slowly [perhaps due to temperature variation], again reducing overall accuracy.) There is a third form of coding, namely, spike encoding, that provides spikes at specific instants, which we discuss further in Section 5.4.

In a digital system, the sampling rate determines the signal bandwidth: the maximal bandwidth is half the sampling rate. The bandwidth determines the maximal rate at which values (such as postsynaptic potentials) can change, For fully implemented systems, both analogue and digital systems normally have plenty of bandwidth in hand compared with real neural systems. However, digital systems are not normally fully implemented, so they need to have a higher bandwidth. If a particular piece of circuitry is used in *P* different ways (for example, a digital multiplier might be used in *P* different synapses), then its processing bandwidth (or speed) must be at least *P* times the actual required bandwidth. The sampling rate also determines the accuracy with which the time of an event can be determined: this can be important for spiking neurons (see also Section 5.4).

In a digital system, sample length determines the accuracy with which a value can be held: theoretically, an analogue system holds a value precisely, but the effect of noise is that the value is no longer precise, and drift causes further difficulties. Maximizing sample length leads to space problems: for most circuitry, the number of gates required is at best proportional to sample length.

#### 5.2.2 Memory technologies

Memory is required in neural systems to hold constant values (such as thresholds, delays, or characteristics for ion channels) as well as variable values such as those characterizing synapses or any other aspect of the model that can alter. Digital memory techniques are well known: memory consists of a string of bits, each held either as a static RAM (sRAM) or a dynamic RAM (dRAM) cell. dRAM requires frequent refreshing, and both sRAM and dRAM are volatile and thus require reinitializing on power cycling. Another possibility is to use electrically erasable programmable read-only memory (EEPROM or flash memory) techniques to provide nonvolatile but rewritable memories.

Analogue memory elements are more problematic. In discrete systems, fixed values may be held by selecting discrete components (usually resistors and/or capacitors) with particular values. This approach is not practical on analogue VLSI chips: resistors can be fabricated, but their accuracy is low, and capacitors of any reasonable size take up too much space. One method of keeping values in analogue systems is to use a digital storage solution combined with a digital-analogue convertor (DAC). Such a system can provide accurate storage, with storage for each value taking up little space. If many values are required (as might be the case for synapse weight storage), this usually means using a smaller number of DACs and sharing them, with a consequent need for additional routing of signals.

True analogue VLSI storage generally uses either the charge on a capacitor or floating gate technology [54]. The simplest technique relies on simply storing some charge on a capacitor, which is essentially isolated. However, this charge

tends to leak away, and so a refresh system is often introduced. A variant on this technique for increasing the quality of this form of representation is to use the ratio of the charge stored on two neighboring capacitors, relying on them both leaking at the same rate [55]. Such memories are essentially volatile. Restoration of these values often makes use of external digitally held values and an on-chip DAC. Floating-gate technology proffers the possibility of longer-term nonvolatile analogue storage: it is based on the same techniques that are used for EEPROM, but attempts to retain an analogue value [54, 56, 57]. Extended analogue storage is not a requirement of standard digital technology, and so is not supported in design systems. This can make chip development more difficult because the devices are often not supported in simulation environments.

The above techniques are for storing constant values. However, an important aspect of neural simulations (and particularly of neural networks) is adaptivity: we need to be able to adjust values, and to adjust them gradually. This process consists of first determining what the parameter alteration should be (discussed in Sections 5.3.1 and 5.4.3), and second, implementing some mechanism for onchip parameter alteration. For digital storage, there is no difficulty in adjusting a binary string: what is required is either an adder or a step-up/step-down counter, or each value may be rewritten, having been recalculated elsewhere. For analogue systems, the problem requires novel solutions. This is not a new problem: specialized devices for weight storage and updating in the analogue domain have a long history (see Section 8.2 of [53]). The original Perceptron Mark 1 used motordriven potentiometers. Later, Widrow introduced the memistor, a copper/electrolyte variable-resistance electrochemical cell. Some systems expect weight adjustments to be determined and effected from outside of the chip: weights are recalculated and then updated using a digital computer interface (e.g., [55, 58]). If the neural simulation is to be be trained without an external computer, then it should incorporate internal adaptation. For capacitative storage, there must be some mechanism for gradually increasing or gradually decreasing the charge stored on the capacitor. For floating-gate techniques, there needs to be a mechanism for charging and discharging the floating gate. Meador [56] suggested using pairs of floating-gate transistors and transferring charge between them. Diorio [57] uses hot-current injection to add electrons to its floating gate and Fowler-Nordheim tunneling to remove them. External checking of the actual weight may be required because of variations in chip processing. This is still an area of active research: Hsu et al. [59] have developed Diorio's ideas in a competitive learning chip, and Morie et al. [60] are developing a multinanodot floatinggate technique for postsynaptic pulse generation.

#### **5.2.3** Simple arithmetic operations

Whether one is using a simple neuron like that in Equation 1 or a more complex neuron with an explicit dendrite, one needs to use arithmetic operations both for calculating neuron output and for any internal parameter alteration. For example, to calculate the postsynaptic activation one requires at least a multiply; to compute the total activation, one requires addition. In a digital implementation, these process imply the use of adders and multipliers, and in an analogue implementation the use of circuitry that can sum voltages (or currents) and

perform multiplication on whatever circuit value is being used to represent the output, activation, or synaptic data.

Such arithmetic operators occur very frequently in neural models. In real neurons, these operations are accomplished using (for synapses) the effects of altering release probabilities for presynaptic neurotransmitter vesicles and changing the probabilities of opening postsynaptic ion channels, and (for the activation summation) by charge summation inside the dendrite. Both these operations take up very little space indeed. In digital systems, very fast adders and multipliers can easily be built. Adders tend to be relatively small, but multipliers tend to be larger. Depending on the multiplier implementation, one has a choice between having the latency and the size of the multiplier increase linearly with operand length (or having the latency increase as the log of the operand length) and having the size of the multiplier increase as the square of operand length [61]. In either case, it is not practical to use a separate multiplier per synapse for neural network implementation, although it can be practical to use one adder per neuron for activation summation.

In analogue implementation, simple multiplication of positive values (single-quadrant multiplication) is relatively straightforward. Thus, if a neuron's output can be guaranteed to be positive, and the weight is known to be excitatory (inhibitory), the product can be added to (subtracted from) the postsynaptic activity. However, the most popular time-free neural model (back-propagation) has neurons whose weights can be either excitatory or inhibitory, and can change between these during training. In addition, some versions of back-propagation use a tanh(A) output function, rather than a logistic (1/(1 + exp(-A))) function, resulting in outputs being either negative or positive. Thus, either two-quadrant or even four-quadrant multiplication is required. This can be problematic, since it is very easy for the product to be outside the linear range of the multiplier (see [62], chapter 6).

In analogue implementations, it is possible to use the transfer characteristics of MOSFETs (or of circuits of MOSFETs) directly, even when these are nonlinear. This option was one of the driving forces behind the Mead's original proposal to use subthreshold a VLSI for neural modeling (and for neuromorphic systems) [62]. In this way, exponential functions, differentiators, and integrators can be built directly (see also [63]). This approach is clearly much more space efficient than developing digital circuits for the same function, and this is the reason why subthreshold a VLSI systems have a very high degree of implementation. However, design is more difficult (or perhaps more skilled), and one is reliant on the silicon implementation behaving in exactly the same way as the designer's model, which, as discussed earlier, may be difficult to achieve.

# 5.3 Implementing simple time-free neuron model networks

An implementation of a simple time-free neuron model consists of an implementation of the synapses, of the dendrites, and of the generation of the output of the model neuron. In addition, it is necessary to implement the interconnection between the neurons. Further, for adaptive systems, one must also implement both parts of the mechanism for adaptation. The primary difficulties arise at

synapses. The problems are computation of postsynaptic potential and computation (and implementation) of synaptic parameter alterations. If there are many neurons, there may also be problems associated with neuron interconnection.

The dendrites accumulate the activity passed to them by the synapses. This is a simple additive process (see Eq. 1). In a digital implementation, this is simple addition, with the number of bits used determining both the precision of the result and when overflow or underflow might occur. In an analogue implementation, either currents or voltages may be summed. Accuracy is then a function of noise, drift, and the linearity of the system. Analogue equivalents to overflow and underflow occur when the current or voltage reaches its limit.

The output of the neuron may be binary (for McCulloch–Pitts neurons or perceptrons, for example), or it may be graded (for a linear threshold unit, for example). In digital implementations, the former is achieved by numerical comparison with a fixed (binary-coded) threshold, and therefore requires an adder. In analogue implementations, this adder is replaced by a comparator, and the threshold is required to be stable. Where the output is graded (as is the case for Delta rule [plain and and back-propagated] and for the Radial Basis Function networks), some function must be applied to the activity. This may be simple multiplication (for linear units) or a logistic function (Eq. 2) or some other function. Accurate implementation may be quite complex in a digital implementation. Sometimes look-up tables are used to speed up this operation. Generally, the output function is shared between a number of neurons on the same chip (partial implementation). In analogue implementations, it may be virtually impossible to achieve exactly the output function required. However, in both the Delta and back-propagated Delta rule, it is not the exact function that matters but rather that the function is a squashing function, which is smooth and always has a positive derivative. Given suitable limits to the activity of the neuron, this outcome can often be achieved relatively easily and compactly in an analogue implementation. One can claim some biological plausibility for this approach as well, since the activation at the axon hillock (where spiking is initiated) will necessarily limit as it tends towards both positive and negative values due to the opening of additional ion channels. Both this form of limitation and the limitation on maximal spiking rates are likely to have similar forms of characteristics, but are unlikely to follow some analytical mathematical function.

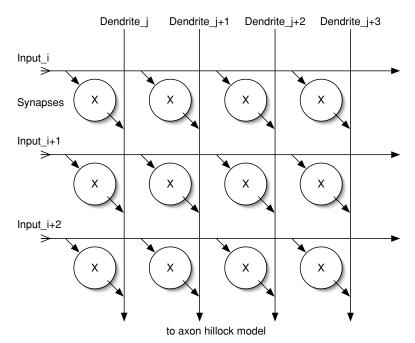

Lastly, model neuron outputs must be connected to the appropriate synapses. Each neuron output may be connected to many different synapses, though each synapse is normally connected to only one neuron output. In a digital implementation, this outcome is best achieved by the use of some form of bus, particularly if the synapses are not fully implemented. The bus allows values to be directed to whichever element of circuitry is implementing that synapse at that time: it is straightforward to calculate whether the bus speed is sufficiently high, and to replicate it if required. In an analogue system, it is more common to use a rectangular array of synapses, as discussed in the next section.

#### 5.3.1 Synapses for time-free neurons

The emulation of synapses is critical in silicon implementations of model neurons. As with real neurons, synapses are by far the most frequently occurring

element of model neural networks. Because a single model neuron may have so many synapses, the system designer is faced with a choice between replicating a small amount of circuitry and hence a simple synapse (full implementation) or sharing the circuitry between a number of synapses (partial implementation). Replicating large amounts of circuitry is generally not practical.

The basic function of a synapse in a network of time-free neurons is to allow a presynaptic input to affect the postsynaptic neuron. Simple implementations of synapses are generally multiplicative: the change in postsynaptic activity is proportional to the presynaptic input, and the constant of proportionality is known as the weight, as in Eq. (1). For simple binary neurons, this set up can be implemented by adding or substracting a constant (weight-dependent) amount from the activity. For graded output neurons, multiplication of the output of the presynaptic neuron and the weight is required. Digital multipliers are standard circuit components but contain a considerable amount of circuitry. Full implementation of such multipliers results in the synapse numbers becoming the limiting factor in what can be placed on a single chip, while partial implementation implies precise switching of the presynaptic input and the appropriate weight, and of the resulting product.

Mechanisms for weight storage were discussed in Section 5.2.2. Chips normally have the weights on-chip, although some may require the weights to be downloaded at start-up. Analogue synapses are often stored in a rectangular array, as illustrated in Figure 13.8. For example, the Intel 80170NX chip [55] has a 160 by 64 array of synapses. Each set of synapses belonging to a single neuron is in a vertical column. The presynaptic inputs from a single neuron are in a hor-

**Figure 13.8.** Synapses (each a simple multiplier) are arranged in a rectangular formation. Dendrites accumulate current from all synapses to that neuron.

izontal line. Where the two meet, there is a synapse (though some may have no effect). The vertical lines accumulate this input (whether as a current  $I_{\rm syn}$  or a voltage  $V_{\rm syn}$ ) and apply this to the simulated axon hillock. Weight storage precision can affect the system in terms of both the system displaying the correct behavior once trained and the system being able to work correctly during training. (This is a general problem in digital signal processing: see [64].) In general, attaining correct behavior once trained is less demanding than attaining appropriate behaviour during training: 4 to 8 bits is enough for almost any application [65,66].

For specific fixed applications, weights may be set externally and fixed. Generally, synaptic adaptivity is attained by weight alteration, which requires that the weights be updatable. We discussed mechanisms for updating the weight in Section 5.2.2: here we are interested in determining what this weight update should be. This calculation may take place on-chip or off-chip. Different neural network algorithms make different changes: with the exception of the perceptron rule and the Hopfield network, however, these changes are often small. Further when using the back-propagated Delta rule, small changes often occur a long way from the best solution due to nearly flat areas in the error/weight space. If the weight update calculation is off-chip, this situation may not present a problem since high-precision arithmetic will be available off-chip. However, if the changes are calculated on-chip, there can be difficulties with digital weight storage update calculation when the weight change becomes less than one bit. (Indeed, these problems apply equally at weight update, even if the changes are calculated at high precision.) This critical point results in a sudden performance breakdown [67] in training, although such precision is not required in recall. Digitally stored analogue weights suffer from exactly the same problem. There has been considerable software exploration of this problem [68]. In a purely analogue system, weights can often be adjusted by very small amounts (exactly how small depends on the details of the implementation), limited by the noise and drift in the system. Failure from this source tends to be less sudden. Changing purely analogue weights can be an imprecise affair, and some systems allow a "chip in the loop" form of updating (e.g., the Intel 80170 [69]), where the effect of the weight update is tested immediately and the update is possibly repeated.

#### **5.3.2** Developed hardware for time-free neurons

Hardware time-free neuron implementations have been around for some time (see [4,51]): a number of chips have been produced commercially and by University Departments (see [70] for a list). A number of the major semiconductor manufacturers have also produced chips: Intel produced the 80170NX (or Electronically Trainable Artificial Neural Network, ETANN) [69], an essentially analogue device directly implementing a number of neurons. Synapses were implemented using the difference between voltages on two neighboring floating gates. The values were externally determined and nonvolatile, with analogue multipliers at each synapse. IBM produced the ZISC036 (ZISC, for zero instruction set computer) [71], a digital chip implementing a radial basis function with onchip learning. This chip could load and evaluate a vector in about 4 microseconds. Motorola collaborated with Adaptive Solutions to develop CNAPS [72], which is essentially a specialized DSP device that can be programmed to implement neural

network applications in a highly efficient fashion. Phillips produced Lneuro [73] and Lneuro 2.3 [74], both digital implementations. Both were intended as special-purpose processors used in conjunction with a computer. Lneuro 2.3 was intended also for other signal and image-processing applications. Siemens produced the SYNAPSE-3 neurocomputer, based on their MA16 chip [75,76], a digital chip that can be programmed to perform many different neural network algorithms at high speed. Many other smaller companies (and many university departments) also developed neural network chips in the early 1990s.

Very few of these chips appear to be currently in production, even though the technology of neural networks is quite widely applied. There are two reasons why neural network chips have not taken off. The first is that workstation prices have tumbled while at the same time their performance has rocketed. The result is that (1) training up neural networks does not take an unreasonably long time, even when large amounts of data are involved, and (2) using neural network software after training is very fast: real-time performance is often possible without special hardware. Since most users do not really care, how long training takes, so long as recall is fast, there is no commercial advantage in building systems a round neural network chips. The second reason is that neural networks themselves (and therefore neural network chips) are components in larger systems. These systems are required in order to massage the data into a form where it can be used directly with a time-free neural network: generally these systems already require a PC, so adding on some neural network software to complete the system is a much more attractive proposition than adding on neural network hardware. Neural network chips tend to be in use either in specialized defense applications (e.g., Irvine Sensors 3DANN devices, see http://www.irvine-sensors.com) or in visual sensors (e.g. NeuriCam, see www.NeuriCam.com). There is still interest in developing neural network chips for algorithms: the Boltzmann machine's capability for generating representations (and for using noise in the algorithm itself) has led to continuing interest in that algorithm ([77,78]). In addition, there has been interest in hardware for the more recent products of expert algorithms [79], resulting in a mixed-signal (hybrid) implementation [80].

Perhaps a third reason can be added as well: as is clear from the paragraph above, there has been no agreement among chip designers as to the best way to implement this type of device. Technologies have varied from specialized analogue systems to specialized digital systems to systems that were essentially adapted digital signal processors. All these approaches work, but none had a specific competitive edge.

# 5.4 Implementing spiking neurons

The earliest implementations of spike-based neurons used existing pulse-based technologies. Interest in this approach appears to have decreased in favor of more biologically plausible systems based on integrate-and-fire neurons.

#### **5.4.1** Pulse-based neuron implementations

Pulse-based techniques have been used in signal processing for many years. Signals take the form of a train of pulses, usually with the signal in an inactive (zero) state most of the time. Such signals have advantages over level coded signals: they are low power (assuming that power consumption is minimal during the zero period), reasonably noise immune, and easily regenerated if the pulse edge is flattened. There are essentially three basic techniques for coding (modulating) values onto pulses: pulse height modulation, pulse width modulation, and pulse frequency modulation. These techniques are, up to a point, independent of each other. One can argue that these pulse-based techniques do have a degree of neural plausibility: pulse frequency modulation is the same as biological spikerate coding. One can argue that pulse height modulation is what is happening at synapses, although the postsynaptic smearing of the precise spike timing could also be interpreted as pulse width modulation.

A number of groups have developed pulse-based neural systems. Murray's group [81–83] used pulse frequency modulation for neuron-to-neuron communication, and pulse width modulation inside the neuron for neuron state (or activity). Their chips were used in robot controllers. Richert's group [84] also used pulse height modulation. Hamilton [83] uses pulse height modulation for postsynaptic currents. The systems produced are relatively compact and low power, and can process and produce time-varying signals (for example, by modulating the pulse frequency). One problem is that it takes time to decode such pulse outputs: one needs to sample pulses for some time in order to estimate the value represented by a pulse frequency coded signal. Lehmann describes circuits for implementing classical conditioning [85] and for biologically inspired learning [86] in pulsed neural networks.

#### 5.4.2 Point neurons