TOPICAL COLLECTION: 59TH ELECTRONIC MATERIALS CONFERENCE 2017

# Electrical Characteristics of 10-kV 4H-SiC MPS Rectifiers with High Schottky Barrier Height

# YIFAN JIANG <sup>1,3</sup> WOONGJE SUNG,<sup>2</sup> JAYANT BALIGA,<sup>1</sup> SIZHEN WANG,<sup>1</sup> BONGMOOK LEE,<sup>1</sup> and ALEX HUANG<sup>1</sup>

1.—FREEDM Systems Center, North Carolina State University, Raleigh, NC 27695, USA. 2.—CNSE, State University of New York (SUNY) Polytechnic Institute, Albany, NY 12203, USA. 3.—e-mail: yjiang12@ncsu.edu

This paper reports the study of the fabrication and characterization results of 10-kilo-volt (kV) 4H-SiC merged PiN/Schottky rectifiers. A metal contact process was developed to make the Schottky contact on *n*-type SiC and ohmic contact on *p*-type SiC at the same time. The diodes with different Schottky contact width were fabricated and characterized for comparison. With the improvement quality of the Schottky contact and the passivation layer, the devices show low leakage current up to 10 kV. The on-state characteristics from room temperature to elevated temperature (423 K) were demonstrated and compared between structures with different Schottky contact width.

**Key words:** Silicon carbide, high voltage, Schottky barrier height, hightemperature electrical performance

## **INTRODUCTION**

With the development of emerging technologies for smart grid applications such as solid-state transformers (SSTs),<sup>1</sup> high-voltage power transistors and diodes play a key role in these technologies. Meanwhile, the development of wide-bandgap material, especially 4H-SiC has enabled single transistors and power rectifiers to block > 20 kV.<sup>2,3</sup> For power rectifiers with blocking voltage of more than 10 kV, most of the results published are using the PiN and junction barrier Schottky (JBS) structures,<sup>3-6</sup> but less based on other concepts like merged PiN/Schottky (MPS), most of which are demonstrated at lower voltage ratings.7-9 The concept of JBS and MPS were both originally proposed by Baliga.<sup>11,12</sup> Though the structures look similar, the difference between the two structures is that MPS rectifiers must be engineered to inject minority carriers from the PN junction at the on state to reduce the on-resistance, while a JBS diode normally works on the unipolar mode. 4H-SiC MPS rectifiers are more difficult to fabricate than silicon

MPS rectifiers, due the large built-in potential of the P-N junction for SiC. One approach has been demonstrated by using a hybrid concept of putting the epitaxial *p*-type region and JBS cells on one cell,<sup>13</sup> which will need extra epitaxial steps and masks. Previous work<sup>10</sup> has demonstrated that injection happens at very small Schottky contact width and high temperature. In this paper, the design and fabrication of SiC MPS rectifiers has been presented using the similar design as the previous study<sup>10</sup> but with improved performance, which will be demonstrated and explained in the following sections.

#### **DEVICE DESIGN AND FABRICATION**

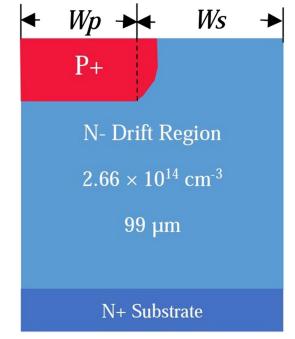

The schematic cross-section of the device half-cell structure is shown in Fig. 1, with the starting material of a highly doped *n*-type 4H-SiC substrate and an n-type 4H-SiC epitaxial layer purchased from Cree, with a thickness of 100  $\mu$ m (tolerance  $\pm 25\%$ ) and low doping concentration of  $2.7 \times 10^{14}$  cm<sup>-3</sup> (tolerance  $\pm 25\%$ ). The lifetime was measured on the wafer before processing, and the average lifetime measured by microwave photoconductance decay ( $\mu$ -PCD) method on the wafer is 1.39  $\mu$ s. The *p*-type region was formed by

<sup>(</sup>Received June 27, 2017; accepted September 13, 2017; published online September 26, 2017)

aluminum ion implantation with a dose of 5e14/ 1e15/2e15/1e14 cm<sup>-1</sup>, and energy of 30/70/140/ 300 keV at a temperature of 600°C, followed by high-temperature annealing up to 1800°C. This ptype region was implemented in the active cell area for the MPS structure, also in the edge termination area as multiple floating rings at the same time. The half-cell width of the Schottky contact  $(W_s)$ , which was also the half-cell width between *p*-type region, was varied from 0.5  $\mu$ m to 2  $\mu$ m and named D1 to D4, and the half-cell width of the *p*-type region  $(W_p)$ was a  $1.5-\mu m$  constant for D1 to D4, as shown in Fig. 1 and Table I. D0 is the PiN diode, in which aluminum was implanted all over the active region. D5 is the Schottky barrier diode (SBD) with the *p*type region only at the edge termination area. All types of devices in Table I have the same active area and edge termination design. For the passivation layer, the atomic layer deposition (ALD) method was used to deposit 30 nm of silicon dioxide, followed by RTA in N<sub>2</sub>O for 1000°C and 1 min, then another layer of silicon dioxide was deposited by vapor plasma-enhanced chemical deposition (PECVD) with a thickness of  $1 \mu m$ . The oxide deposited by ALD and the N2O annealing can reduce the density of interface states and hence improve the device performance under reverse bias.<sup>14,15</sup> The backside ohmic contact was formed by evaporation of nickel and RTA at 950°C for 2 min. Then, the contact metal process was optimized by electron beam evaporation of nickel followed by RTA at 850°C and 1 min under nitrogen, and the Schottky contact on n-type SiC and the ohmic contact on ion implanted p-type SiC was formed with this single process.<sup>18</sup> This process eliminates the alignment of the contact layer to the *p*-type implantation layer, thus reducing the fabrication cost and complexity. At last, the thick metal and polyimide was patterned and deposited on top before electrical characterization.

#### ELECTRICAL CHARACTERIZATION RESULTS

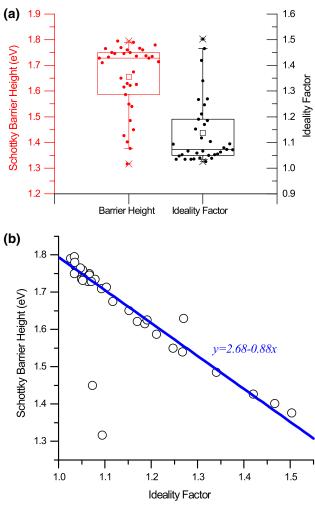

First, the Schottky contact was evaluated through the test structures all over the wafer. The forward IV of Schottky diodes was tested with active an area of  $3.36 \times 10^{-3}$  cm<sup>2</sup>, and the Schottky barrier height (SBH) and ideality factor is extracted by using the Richardson constant of 146 A cm<sup>-2</sup> K<sup>-2</sup> for silicon carbide. The distribution of the SBH and ideality factor is shown in Fig. 2a. Most of the test structures show an ideality factor of less than 1.1 and SBH of over 1.7 eV. The relationship between the SBH and ideality factor was also plotted in Fig. 2b, where most of the values are in a linear relationship, which implies an interface of inhomogeneous distribution of barrier heights.<sup>16</sup> The high SBH helps reduce the leakage current of the diodes under reverse bias,<sup>17</sup> and causes large potential difference between the *P–N* junction, which helps induce the

Fig. 1. Schematic half-cell cross-section of SiC MPS rectifiers.

injection of holes from the P region. The ohmic contact was evaluated using the TLM structures, and the average contact resistance is  $1.4 \times 10^{-4} \ \Omega \ cm^2$ .

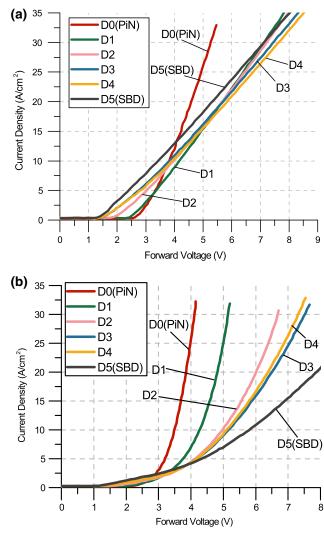

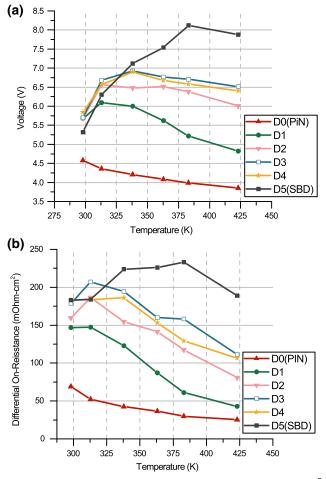

The forward current-voltage characteristics of D0–D5 with an active area of 6.68 mm<sup>2</sup> are shown in Fig. 3a. D5 has the lowest knee voltage of 1.3 V compared to other structures, and the knee voltage increases as  $W_s$  becomes smaller. D0 shows the typical PiN diode behavior with a knee voltage of 2.5 V and smaller differential resistance at higher voltage due to the minority injection. The forward current-voltage characteristics at 423 K are shown in Fig. 3b. All types of devices have non-linear characteristics, which indicates strong minority injection due to the reduced built-in potential of the P-N junction at higher temperature. The forward voltage at 20 A  $cm^{-2}$  at different temperature is shown in Fig. 4. D0 has continued to increase of forward voltage until 380 K, while D0 and D1 show forward voltage decrease obvious at high temperature.

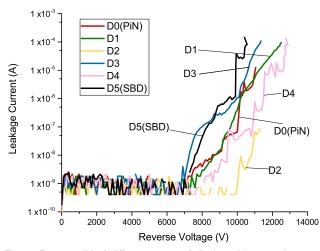

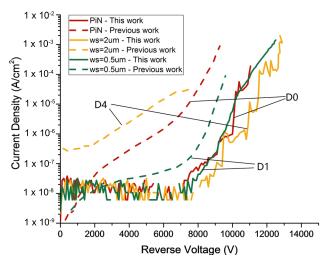

The reverse current–voltage characteristics of device with area of 6.68 mm<sup>2</sup> are plotted in Fig. 5. No significant leakage current difference is found for different structures, and even the SBD (D5) has a very low leakage current due to the high SBH and improved quality of the interface between passivation and SiC. A much lower leakage current and higher breakdown voltage is achieved compared to previous results<sup>19</sup> in Fig. 6. The edge termination design, and the aluminum ion implant dose, energy and conditions in previous work is the same as in this work. The difference is the frontside Schottky contact and the passivation stack on the edge

| Table I. I<br>(W <sub>s</sub> and W | Device types with different contact widths $W_p$ ) |

|-------------------------------------|----------------------------------------------------|

|                                     |                                                    |

| Name     | $W_{s}$ ( $\mu m$ ) | $W_p \ (\mu \mathbf{m})$ |

|----------|---------------------|--------------------------|

| D0 (PiN) | 0                   | _                        |

| D1       | 0.5                 | 1.5                      |

| D2       | 1                   | 1.5                      |

| D3       | 1.5                 | 1.5                      |

| D4       | 2                   | 1.5                      |

| D5 (SBD) | -                   | 0                        |

Fig. 2. (a) Distribution of extracted Schottky contact barrier height and ideality factor on a wafer. (b) Relationship between Schottky barrier height and ideality factor measured on wafer.

termination area. The SBH of the devices in previous study is 0.89 eV with an ideality factor of 2.4, which does not have an annealing process, and current work shows better quality of the Schottky contact. The passivation layer of the previous work only had one PECVD oxide layer and did not go through nitrous oxide annealing.

The edge termination is designed with multiple floating field rings, and with a constant p-type ring

Fig. 3. (a) Forward IV of different types of diodes at room temperature. (b) Forward IV of different types of diodes at 423 K.

width of 4  $\mu m$  and increasing space width as shown below:

$$S_n = S_1 + [(n-1)S_i]^2$$

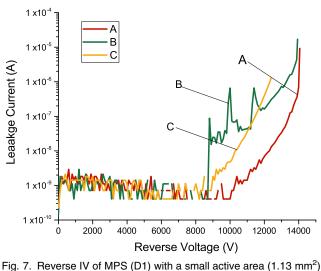

The  $S_n$  means the space width between the (N-1)th ring and the *N*th ring, and  $S_1 = 1 \mu m$ , n = 100. In Fig. 7, type A design means Si = 0.0175, type B design means Si = 0.0225 and type C design means Si = 0.0275. The best reverse *I*-*V* of small devices (area of 1.13 mm<sup>2</sup>) on wafer in Fig. 7 reveals higher breakdown voltage probably due to less process and material defects, and the highest breakdown voltage achieved is 14.0 kV.

#### DISCUSSION

There are two main factors that are contributing to the forward current-voltage characteristics of MPS diodes. One is the mobility of electrons, which

Fig. 4. (a) Forward voltage of different types of diodes at 20 A cm<sup>-2</sup> at different temperatures. (b) Differential on-resistance at 20 A cm<sup>-2</sup> for different types of diodes at different temperature.

Fig. 5. Reverse IV of different types of diodes with an active area  $6.68 \text{ mm}^2$  at room temperature.

are the majority carriers for the unipolar device with an n-type drift region. The mobility decreases with temperature, which contributes to the

Fig. 6. Reverse IV for different types of devices compared to data from Ref. 19.

with different edge termination design.

increased differential resistance at high temperature. Another one is the minority lifetime which is increasing with temperature and leads to decreased differential on-resistance, which has been proved by experimental results<sup>20,21</sup> and may be due to the increased emission rate of carriers from material defects at high temperature. For structure D5, most of the area is covered by the Schottky contact, so the majority current is taking the lead in conduction mode; thus mobility plays a key role in increasing the resistance with temperature. From D5 to D0, with the smaller width of the Schottky contact, more minority injection happens, which leads to the decreasing of resistance with temperature. It is worth noticing that even without a P region at the active region, the forward voltage of D5 decreases at 423 K. It may due to the overlap between the first *p*type ring of the edge termination and the anode

contact, which will also induce hole injection at certain states.

#### CONCLUSION

SiC MPS diodes with different Schottky contact widths were fabricated, and the static characteristics were characterized from room temperature to high temperature (423 K). All types of devices show a low leakage current and high blocking voltages over 10 kV, which are probably due to the high SBH and the improved quality of the passivation layer with ALD oxide followed by N<sub>2</sub>O annealing. The difference of the temperature dependence of forward I-V behavior with different types is due to the varied portion of current from minority carriers, which is larger for structures having narrower Schottky contact width.

### ACKNOWLEDGEMENTS

This work was supported by the ERC Program of the National Science Foundation under award number EEC-08212121. This work was also performed in part at the NCSU Nanofabrication Facility (NNF) and Shared Materials Instrumentation Facility (SMiF) at Duke University, both of which are members of the North Carolina Research Triangle Nanotechnology Network (RTNN), which is supported by the National Science Foundation (Grant ECCS-1542015) as part of the National Nanotechnology Coordinated Infrastructure (NNCI).

#### REFERENCES

- 1. A.Q. Huang, IEEE. Ind. Electron. Mag. 10, 3 (2016).

- E.V. Brant, L. Cheng, M.J. O'Loughlin, J. Richmond, V. Pala, J. Palmour, C.W. Tipton, and C. Scozzie, *Mater. Sci. Forum* 821–823, 847 (2015).

- N. Kaji, H. Niwa, J. Suda, and T. Kimoto, *IEEE. Trans.* Electron. Dev. 62, 2 (2015).

- A. Salemi, H. Elahipanah, B. Buono, A. Hallén, J.U. Hassan, P. Bergman, G. Malm, C. Zetterling, M. Östling, and R. Nicole, in *Proceedings of the 27th International Symposium on Power Semiconductor* (2015). pp. 269–272.

- T. McNutt, Stephen V. Campen, A. Walker, K. Ha, C. Kirby, M. Sherwin, R. Singh, and H. Hearne, *Mater. Sci.* Forum 600-603, 951 (2008).

- H. Runhua, T. Yonghong, C. Pengfei, W. Ling, C. Gang, B. Song, L. Rui, L. Yun, and Z. Zhifei, J. Semicond. 35, 7 (2014).

- M. Draghici, R. Rupp, R. Gerlach, and B. Zippelius, Mater. Sci. Forum 812–813, 608 (2015).

- 8. Y. Huang, T. Erlbacher, J. Buettner, and G. Wachutka, in Proceedings of the 28th International Symposium on Power Semiconductor (2016). pp. 63–66.

- S. Palanisamy, S. Fichtner, J. Lutz, T. Basler, and R. Rupp, in Proceedings of the 28th International Symposium on Power Semiconductor (2016). pp. 235-238.

- Y. Jiang, W. Sung, X. Song, H. Ke, S. Liu, B.J. Baliga, A.Q. Huang, and E.V. Brunt, in *Proceedings of the 28th International Symposium on Power Semiconductor* (2016). pp. 43-46.

- 11. B.J. Baliga, IEEE Electron Device Lett. 5, 6 (1984).

- 12. B.J. Baliga, IEEE Electron Device Lett. 8, 9 (1987).

- H. Niwa, J. Suda, and T. Kimoto, *IEEE Trans. Electron Devices* 64, 3 (2017).

- 14. X. Yang, B. Lee, and V. Misra, *IEEE Electron Device Lett.* 62, 11 (2016).

- S. Nakazawa, T. Okuda, J. Suda, T. Nakamura, and T. Kimoto, *IEEE Electron Device Lett.* 62, 2 (2015).

- R.F. Schmitsdorf, T.U. Kampen, and W. Monch, J. Vac. Sci. Technol. B 15, 1221 (1997).

- 17. B.J. Baliga, Fundamentals of Power Semiconductor Devices (Berlin: Springer, 2008).

- W. Sung and B.J. Baliga, *IEEE Electron Device Lett.* 37, 12 (2016).

- E. Van Brunt, Ph.D Thesis, North Carolina State University (2013).

- R.B. Klein, R. Myers-Ward, K.-K. Lew, B.L. VanMill, C.C.R. Eddy Jr, D.K. Gaskill, A. Shrivastava, and T.S. Sudarshan, J. Appl. Phys. 108, 033713 (2010).

- T. Okuda, T. Miyazawa, H. Tsuchida, T. Kimoto, and J. Suda, Appl. Phys. Express 7, 085501 (2014).