Abstract

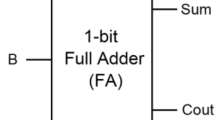

In the current scenario, low power circuits can be designed using the concept of reversible logic. Here in this paper, reversible logic-based digital circuit like full adder is presented. The full adder circuit is implemented by using CMOS BSIM4 model. Design of reversible logic-based full adder circuit is efficient by considering various factors like the number of gates required, quantum cost, number of garbage outputs, and constant inputs. The reversible logic-based design is implemented and simulated with the help of tanner EDA tool having a version of tanner 13.0 tools. It has some performance parameter which is compulsorily considered for the completion of reversible logic circuit. System ideas of reversible logic circuits are cryptography, digital signal processing, computer graphics, and network congestion.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Mahalakshmi, R., Sasilatha, T.: A power efficient carry save adder and modified carry save adder using CMOS technology. In: 2013 IEEE International Conference on Computational Intelligence and Computing Research (ICCIC), pp. 1–5 (2013)

Bruce, J., Thornton, M., Shivakumaraiah, L., Kokate, P., Li, X.: Efficient adder circuits based on a conservative reversible logic gate. In: Proceedings of the IEEE Computer Society Annual Symposium on VLSI, 2002, pp. 74–79 (2002)

Parhami, B.: Fault-tolerant reversible circuits. In: Fortieth Asilomar Conference on Signals, Systems and Computers, ACSSC’06, Oct 2006, pp. 1726–1729 (2006)

Kaur, P., Dhaliwal, B.: Design of fault to learnt full adder/subtractor using reversible gates. In: 2012 International Conference on Computer Communication and Informatics (ICCCI), Jan 2012, pp. 1–5 (2012)

Author information

Authors and Affiliations

Corresponding authors

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2020 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Horke, S., Waje, M., Patil, R. (2020). Performance Analysis of Reversible Logic-Based Full Adder Using BSIM4 Model. In: Iyer, B., Deshpande, P., Sharma, S., Shiurkar, U. (eds) Computing in Engineering and Technology. Advances in Intelligent Systems and Computing, vol 1025. Springer, Singapore. https://doi.org/10.1007/978-981-32-9515-5_62

Download citation

DOI: https://doi.org/10.1007/978-981-32-9515-5_62

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-32-9514-8

Online ISBN: 978-981-32-9515-5

eBook Packages: Intelligent Technologies and RoboticsIntelligent Technologies and Robotics (R0)