Abstract

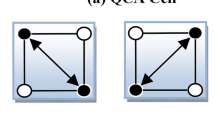

Quantum-dot Cellular Automata (QCA) is the alternative approach to synthesize the logic circuit with high density and low power dissipation to overcome the limitation of current VLSI technology. The underlying regular clocking scheme plays a significant role in the systematic cell layout, scalability, and reliability of the QCA circuit. This work analyzes the impact of genetic algorithm (GA) on regular clock based QCA circuits for less power dissipation. The elitism-based methodology is utilized to effectively realize multi-output boolean functions, embedding regular clocking schemes. A detailed analysis of power dissipation with different regular clocking schemes is reported. QCADesigner is used for logic synthesis, whereas QCAPro and QCADesignerE have been utilized for energy dissipation analysis.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Karim, F., Walus, K.: Efficient simulation of correlated dynamics in quantum-dot cellular automata (qca). IEEE Trans. Nanotechnol. 13(2), 294–307 (2014)

Houshmand, M., Saleh, R.R., Houshmand, M.: Logic Minimization of QCA Circuits Using Genetic Algorithms, pp. 393–403. Springer, Berlin (2011)

Tehrani, M.A., Navi, K., Kia-kojoori, A.: Multi-output majority gate-based design optimization by using evolutionary algorithm. Swarm Evol. Comput. 10, 25–30 (2013)

Vasconcelos, J.A., Ramirez, J.A., Takahashi, R.H.C., Saldanha, R.R.: Improvements in genetic algorithms. IEEE Trans. Magn. 37(5), 3414–3417 (2001)

Ahn, C.W., Ramakrishna, R.S.: Elitism-based compact genetic algorithms. IEEE Trans. Evol. Comput. 7(4), 367–385 (2003)

Vankamamidi, V., Ottavi, M., Lombardi, F.: Two-dimensional schemes for clocking/timing of qca circuits. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 27(1), 34–44 (2007)

Campos, C.A.T., Marciano, A.L., Neto, O.P.V., Torres, F.S.: Use: a universal, scalable, and efficient clocking scheme for qca. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 35(3), 513–517 (2015)

Goswami, M., Mondal, A., Mahalat, M.H., Sen, B., Sikdar, B.K.: An efficient clocking scheme for quantum-dot cellular automata. Int. J. Electron. Lett. 1–14 (2019)

Wang, L., Xie, G., Zhu, R., Yu, C.: An optimized clocking scheme for nanoscale quantum-dot cellular automata circuit. In: 2019 IEEE 14th International Conference on Nano/Micro Engineered and Molecular Systems (NEMS), pp. 336–341. IEEE (2019)

Bennett, C.: Logical reversibility of computation. IBM J. Res. Devel. 525–532 (1973)

Srivastava, S., Sarkar, S., Bhanja, S.: Power dissipation bounds and models for quantum-dot cellular automata circuits. In: 2006 Sixth IEEE Conference on Nanotechnology, vol. 1, pp. 375–378. IEEE (2006)

Lent, C.S., Tougaw, P.D.: A device architecture for computing with quantum dots. Proc. IEEE 85(4), 541–557 (1997)

Hennessy, K., Lent, C.S.: Clocking of molecular quantum-dot cellular automata. J. Vacuum Sci. Technol. B: Microelectron. Nanometer Struct. Process., Measur., Phenom. 19(5), 1752–1755 (2001)

Konak, A., Coit, D.W., Smith, A.E.: Multi-objective optimization using genetic algorithms: a tutorial. Reliab. Eng. Syst. Safety 91(9), 992–1007 (2006)

Deb, K.: Multi-Objective Evolutionary Algorithms, pp. 995–1015. Springer, Berlin (2015)

Coello, C.A.C., Lamont, G.B., Van Veldhuizen, et al. D.A.: Evolutionary Algorithms for Solving Multi-objective Problems, vol. 5. Springer (2007)

Liu, W., Lu, L., O’Neill, M., Swartzlander, E.E.: A first step toward cost functions for quantum-dot cellular automata designs. IEEE Trans. Nanotechnol. 13(3), 476–487 (2014)

Timler, J., Lent, C.S.: Power gain and dissipation in quantum-dot cellular automata. J. Appl. Phys. 91(2), 823–831 (2002)

Srivastava, S., Asthana, A., Bhanja, S., Sarkar, S.: Qcapro-an error-power estimation tool for qca circuit design. In: IEEE International Symposium of Circuits and Systems (ISCAS), pp. 2377–2380. IEEE (2011)

Torres, F.S., Wille, R., Niemann, P., Drechsler, R.: An energy-aware model for the logic synthesis of quantum-dot cellular automata. IEEE Trans. Comput. Aided Des. Integrated Circ. Syst. 37, 3031–3041 (2018)

Acknowledgements

This work is sponsored by the Young Faculty Research Fellowship (YFRF) of Visvesvaraya Ph.D. scheme through the grant number MLA/MUM/GA/10(37)B.

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2022 The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Pramanik, A.K., Pal, J., Sen, B. (2022). Impact of Genetic Algorithm on Low Power QCA Logic Circuit with Regular Clocking. In: Das, S., Martinez, G.J. (eds) Proceedings of First Asian Symposium on Cellular Automata Technology. ASCAT 2022. Advances in Intelligent Systems and Computing, vol 1425. Springer, Singapore. https://doi.org/10.1007/978-981-19-0542-1_14

Download citation

DOI: https://doi.org/10.1007/978-981-19-0542-1_14

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-19-0541-4

Online ISBN: 978-981-19-0542-1

eBook Packages: Intelligent Technologies and RoboticsIntelligent Technologies and Robotics (R0)