Abstract

There is a growing concern regarding the increased standby power and reduced stability of SRAM due to continued scaling in technology node. So, there is a necessity to design a new SRAM cell which addresses the concerns related to SRAM cell. So, 10T SRAM cell is proposed with reduced standby power and enhanced stability in read, write and hold modes of operation. There is a reduction in standby power because of the usage of stacked transistors. P10T SRAM cell has decreased the standby power while holding 1 by 4.9%, 15.99% and 1.68% compared to 8T, 8TG and 9T respectively at the worst process corner FF at 0.9 V VDD. There is an increase of 262.89, 47.566, 261.75% write margin compared to 6T, 8TG, 9T SRAM cells at 0.9 V supply voltage for TT corner. The influence of process and voltage variations on write margin was studied on available and proposed SRAM cells. All designs are designed using in cadence virtuoso in 45 nm CMOS technology node.

Access provided by Autonomous University of Puebla. Download conference paper PDF

Similar content being viewed by others

Keywords

1 Introduction

In computing systems, static random access memory (SRAM) forms the basic building block which occupies considerable area and consumes considerable amount of power. This necessitates stable and low standby power SRAM for portable devices [1]. Applications like implantable biomedical devices, wireless sensor networks (WSN), and battery-based electronic devices often require low power consumption in the present trend. Devices using FPGA are increasingly preferred day by day, because of its reconfigurability and prototyping capability, to develop advanced embedded applications [2, 3]. FPGA based on SRAM forms a significant portion of overall FPGA market. Reduction in power supply voltage quadratically decreases active power and linearly decreases standby power but restricted by PVT variations [4]. As the supply voltage is decreased, standby power dominates the active power [5]. This significant increase in standby power is going to have an increased impact in SRAM cells as most of the cells tend to operate in standby mode [6].

6T SRAM cell suffers from read–write sizing conflict and also the RSNM degradation. In [7], asymmetric sizing was used to improve the stability of SRAM cell but with increased leakage currents. In [8], 4T read port is used to reduce the leakage but at the expense of increased area and less write margin. Chang et al. [9] proposed an 8T SRAM cell which isolates the read path from the storage nodes to increase RSNM. But it suffers from low write margin. A multi-threshold 9T SRAM was proposed in [10] for the energy efficiency, but it requires extra boosted supply. SRAM cell in [11] has P-P-N devices. It has low leakage power, but the cell has degraded write ability. In [12, 13], reduction in leakage power was reported with slight increase in area. In [14], data-dependent power supply SRAM cell for low leakage has been reported.

Static noise margin is used to determine the SRAM cell stability in hold and read modes of operation, respectively. In write operation, stability is determined by write margin (WM).

The paper is comprised of the following. Section 2 explains the existing SRAM designs. Section 3 describes the proposed SRAM design with operation. Section 4 compares the existing SRAM cells with the proposed SRAM cell w.r.t. standby power, HSNM, RSNM, and write margin. Section 5 concludes.

2 Existing SRAM Designs

6T SRAM cell shown in Fig. 1 is the conventional design which is formed using two cross-coupled inverters to latch the data while the access transistors are separately used to perform either read or write operation. Cell ratio and pull up ratio decide the stability in read and write operation, respectively. In 8TG SRAM cell [15] is similar to 6T SRAM cell, but the access transistors are replaced with transmission gates. In [9], read port has been isolated which gives an option to optimize the read and write SNMs individually. In [16], an addition NMOS has been added to the read port for further reduction of leakage power.

3 Proposed 10T SRAM Cell (P10T)

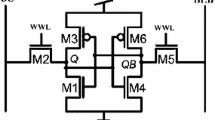

Existing SRAM designs suffer from one of the aspects like high leakage power, less write stability, and less read stability. So, in order to maintain the stability with less leakage power, a new SRAM cell is proposed with 10 transistors (P10T) as shown in Fig. 2. Table 1 lists different control signals status in different modes of operation. Stacked transistors PM3 and MN2 were used which reduces leakage. PM3, PM4, MN2, and MN4 assist in high write ability.

3.1 Write Operation

While performing write operation PM3 and MN2 are disconnected from the power supply rails by keeping the control signals WLPU and WLPD at Logic 1 and 0, respectively. This brings down either Q or QB from its stored value to its complement at a faster pace. When Logic 0 is stored, WL is enabled, BL is set to Logic 1 and its complement to BLB, RWL is disabled, WLB is enabled which performs write 1 into the storage node Q. When Logic 1 is stored, WL is enabled, BL is set to Logic 0 and its complement to BLB, RWL is disabled, WLB is enabled which performs write 0 into the storage node Q.

3.2 Read Operation

In read mode, WL and WLB are disabled, WLPU and WLPD are kept at Logic 0 and Logic 1, respectively, RWL is enabled which turns ON MN6, RBL is precharged to VDD. When Q = 0, MN1 is ON creating a path for RBL to be discharged to ground. When Q = 1 and QB = 0, MN1 is OFF creating no path for RBL to discharge to ground. Based on the value of RBL, sense amplifier senses and gives the output.

3.3 Hold Operation

WL, WLB, and RWL are disabled, WLPU and WLPD are kept at Logic 0 and Logic 1, respectively, which forms the cross-coupled inverters to latch the data.

4 Results and Discussion

4.1 Standby Power

As the majority of SRAM cells operate in standby mode, standby power or leakage power reduction is essential. It is estimated as the multiplication of supply voltage and the current flowing through it [17]. Standby power is analyzed in the proposed SRAM (P10T) cell along with the other SRAM cells available in the literature. Figure 3 shows standby power at different process corners at 0.9 V VDD. There is a significant reduction in standby power due to the usage of stacked transistors in pull down and pull up network. P10T SRAM cell decreased the standby power while holding 1 by 4.91%, 15.99% and 1.68% compared to 8T, 8TG and 9T respectively at the worst process corner FF. Hold 1 power of P10T has also decreased by 7.5%, 4.62%, 19.03% compared to 8TG at TT, FS and SF corners respectively.

4.2 Hold Stability

While SRAM is operating in hold mode, stability can be determined by HSNM which can be estimated by the butterfly curve. As the control signals of transistors PM3 and MN2 are kept at Logic 0 and 1, respectively, both the transistors are turned ON which replicates the two back to back inverters similar to 6T SRAM cell. From Fig. 4, HSNM slightly increased at all process corners except at SF corner.

4.3 Read Stability

Read stability is analyzed using the metric RSNM. Side length of largest square that can be fitted in the butterfly curve gives RSNM [18]. Read current through the storage nodes degrades RSNM. Due to this 6T, 8TG, P10T SRAM cell has lower RSNM. 8T, 9T SRAM cells have isolated the flow of read current through the storages nodes which leads to higher RSNM as shown in Fig. 5.

4.4 Write Stability

In 6T, 8TG SRAM cells, enhancement of write margin is restricted by the sizing of access transistor, pull down and pull up transistors. So read port is isolated in 8T, 9T, and P10T SRAM cells which gives freedom to separately size the devices which further enhances read and write stability individually. In P10T SRAM cell, PM3 and MN2 are disconnected to the power rails by the control signals WLPU and WLPD, respectively, and the usage of transmission gate enhances the write stability. Write margin is calculated using World Line sweep method [19]. Figure 6 shows the estimated write margin values at all process corners.

In Fig. 7, write margin is also observed for wide supply voltage range at TT corner. It clearly indicates P10T has enhanced write stability than other SRAM cells.

5 Conclusion

Design metrics like standby power and stability are the major parameters that need to be considered while designing the SRAM cell. Though available SRAM cells excel in one of the design metrics, they suffer degradation in other design metrics. The proposed 10T (P10T) cell provides less standby power and enhanced write margin while having decent HSNM.

References

Rad JS, Guthaus M, Hughey R (2014) Confronting the variability issues affecting the performance of next generation SRAM design to optimize and predict the speed and yield. IEEE Access 2:577–601

Safarulla IM, Manilal K (2014) Design of soft error tolerance technique for FPGA based soft core processors. In: 2014 international conference on advanced communication control and computing technologies (ICACCCT). IEEE, pp 1036–1040

Ullah Z, Jaiswal MK, Cheung RC (2015) Z-TCAM: an SRAM-based architecture for TCAM. IEEE Trans Very Large Scale (VLSI) Integr Syst 23(2):402–406

Toh SO, Guo Z, Liu T-JK, Nikolic B (2011) Characterization of dynamic SRAM stability in 45 nm CMOS. IEEE J Solid-State Circuits 46(11):2702–2712

Aly RE, Faisal MI, Bayoumi MA (2005) Novel 7T SRAM cell for low power cache design. In: Proceedings of the IEEE international SOC conference, Sept 2005, pp 171–174

Pasandi G, Fakhraie SM (2015) A 256-kb 9T near-threshold SRAM with 1 k cells per bitline and enhanced write and read operations. IEEE Trans VLSI Syst 23(11):2438–2446

Nalam S, Calhoun BH (2011) 5T SRAM with asymmetric sizing for improved read stability. IEEE J Solid-State Circuits 46(10):2431–2442

Calhoun BH, Chandrakasan AP (2007) A 256-kb 65-nm sub-threshold SRAM design for ultra-low-voltage operation. IEEE J Solid-State Circuits 42(3):680–688

Chang L, Montoye RK, Nakamura Y, Batson KA, Eickemeyer RJ, Dennard RH, Haensch W, Jamsek D (2008) An 8T-SRAM for variability tolerance and low-voltage operation in high-performance caches. IEEE J Solid-State Circuits 43(4):956–963

Wang B, Nguyen TQ, Do AT, Zhou J, Je M, Kim TT-H (2015) Design of an ultra-low voltage 9T SRAM with equalized bitline leakage and cam-assisted energy efficiency improvement. IEEE Trans Circ Syst I Reg Pap 62(2):441–448

Lo C-H, Huang S-Y (2011) PPN based 10T SRAM cell for low-leakage and resilient subthreshold operation. IEEE J Solid-State Circuits 46(3):695–704

Gavaskar K, Ragupathy US, Malini V (2019) Design of novel SRAM cell using hybrid VLSI techniques for low leakage and high speed in embedded memories. Wirel Pers Commun 108(4):2311–2339

Mishra JK, Srivastava H, Misra PK, Goswami M (2019) Analytical modelling and design of 9T SRAM cell with leakage control technique. Anal Integr Circ Sig Process 101(1):31–43

Sharma V, Gopal M, Singh P, Vishvakarma SK, Chouhan SS (2019) A robust, ultra low-power, data-dependent-power-supplied 11T SRAM cell with expanded read/write stabilities for internet-of-things applications. Analog Integr Circ Sig Process 98(2):331–346

Islam A, Hasan M (2012) A technique to mitigate impact of process, voltage and temperature variations on design metrics of SRAM cell. Microelectron Rel 52(2):405–411

Lin Sheng, Kim Yong-Bin, Lombardi Fabrizio (2010) Design and analysis of a 32 nm PVT tolerant CMOS SRAM cell for low leakage and high stability. Integration 43:176–187

Singh P, Vishvakarma SK (2017) Ultra-low power high stability 8T SRAM for application in object tracking system. IEEE Access 6(11):2279–2290

Do AT et al (2011) An 8T differential SRAM with improved noise margin for bit interleaving in 65 nm CMOS. IEEE Trans Circ Syst I Reg Pap 58(6):1252–1263

Gierczynski N, Borot B, Planes N, Brut H (2007) A new combined methodology for write margin extraction of advanced SRAM. In: Proceedings of the IEEE international conference on microelectronic test structures (ICMTS), pp 97–100

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2021 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Manoj Kumar, R., Sridevi, P.V. (2021). Design of Low Standby Power 10T SRAM Cell with Improved Write Margin. In: Chowdary, P., Chakravarthy, V., Anguera, J., Satapathy, S., Bhateja, V. (eds) Microelectronics, Electromagnetics and Telecommunications. Lecture Notes in Electrical Engineering, vol 655. Springer, Singapore. https://doi.org/10.1007/978-981-15-3828-5_53

Download citation

DOI: https://doi.org/10.1007/978-981-15-3828-5_53

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-15-3827-8

Online ISBN: 978-981-15-3828-5

eBook Packages: EngineeringEngineering (R0)