Abstract

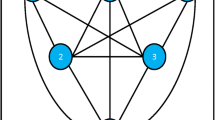

The increasing of the signaling technology motivated the research community to find alternative solutions to replace the sequential computing systems. These systems reached their limits, and it became an infeasible choice to manage the computational grand challenges. Thereby, many types of research have been conducted to improve a system with special characteristics able to cope with the new technology. Massively parallel computer (MPC) systems have been emerged to solve the complex computing challenges in parallel and concurrently. The performance of these systems is affected by the structure of the underlying interconnection network. Therefore, many designs of interconnection networks topologies have been presented looking for an optimal one. In this paper, we present the architecture of MMN which is a hierarchical interconnection network. The static and dynamic performance parameters of MMN have been evaluated in previous studies, and it provided good results compared to the conventional interconnection network topologies. This paper will focus on evaluating and determining the static cost-effective parameter of MMN which is the product of the relation between the node degree, network diameter, wiring complexity, and the total number of nodes in each network.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Cheng, S.Y., Chuang, J.H.: Varietal hypercube-a new interconnection network topology for large-scale multicomputer. In: Proceeding of the International Conference on Parallel and Distributed Systems, pp. 703–708. IEEE (1994)

Al Faisal, F., Rahman, M.M., Inoguchi, Y.: Topological analysis of the low-powered 3D-TESH network. IEICE Tech. Rep. 115(399), 143–148 (2016)

Awal, M.R., Rahman, M.M.H., Akhand, M.A.H.: A new hierarchical interconnection network for future generation parallel computer. In: Proceeding of the 16th International Conference on Computer and Information Technology (ICCIT), pp. 314–319. IEEE (2013)

Anagnostopoulos, I., Bartzas, A., Vourkas, I., Soudris, D.: Node resource management for DSP applications on 3D network-on-chip architecture. In: Proceeding of the 16th International Conference on Digital Signal Processing, pp. 1–6. IEEE (2009)

Ali, M., Welzl, M., Zwicknagl, M.: Networks on chips: scalable interconnects for future systems on chips. In: Proceeding of the 4th European Conference on Circuits and Systems for Communications, ECCSC. pp. 240–245. IEEE (2008)

Goossens, K., Dielissen, J., Radulescu, A.: Æthereal network on chip: concepts, architectures, and implementations. IEEE Des. Test Comput. 22(5), 414–421 (2005)

Dally, W.J., Towles, B.: Route packets, not wires: on-chip interconnection networks. In: Proceedings of Design Automation Conference, pp. 684–689. IEEE (2001)

Bjerregaard, T., Mahadevan, S.A.: survey of research and practices of network-on-chip. ACM Comput. Surv. (CSUR) 38(1), 1

Miura, Y., Kaneko, M., Rahman M.M.H., Watanabe, S.: Adaptive Routing Algorithms and Implementation for TESH Network (2013)

Rahman, M.M.H., Ali, M.N.M., Nor, R.M., Sembok, T.M.T., Akhand, M.A.H.: Time-cost effective factor of a midimew connected mesh network. In: Proceeding of the 6th International Conference on Information and Communication Technology for the Muslim World (ICT4 M), pp. 264–268. IEEE (2016)

Kim, J., Dally, W.J., Scott, S., Abts, D.: Technology-driven, highly-scalable dragonfly topology. In: ACM SIGARCH Computer Architecture News, vol. 36, no. 3, pp. 77–88. IEEE Computer Society (2008)

Rahman, M.H., Inoguchi, Y., Yukinori, S.A.T.O., Horiguchi, S.: TTN: a high performance hierarchical interconnection network for massively parallel computers. IEICE Trans. Inf. Syst. 92(5), 1062–1078 (2009)

Rahman, M.H., Horiguchi, S.: HTN: a new hierarchical interconnection network for massively parallel computers. IEICE Trans. Inf. Syst. 86(9), 1479–1486 (2003)

Ali, M.N.M., Rahman, M.M.H., Nor, R.M., Sembok, T.M.B.T.: A high radix hierarchical interconnection network for network-on-chip. In: Recent Advances in Information and Communication Technology, pp. 245–254. Springer International Publishing (2016)

Mohanty, S.P., Ray, B.B., Patro, S.N., Tripathy, A.R.: Topological properties of a new fault tolerant interconnection network for parallel computer. In: Proceeding of the International Conference on Information Technology (ICIT’08). pp. 36–40. IEEE (2008)

Xiao, L., Wang, K.: Reliable opto-electronic hybrid interconnection network. In: Proceeding of the International Symposium on Parallel Architectures, Algorithms, and Networks (I-SPAN08). pp. 239–244. IEEE (2008)

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2019 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Hafizur Rahman, M.M., Ali, M.N.M., Ibrahim, A.A., Behera, D.K., Miura, Y., Inoguchi, Y. (2019). A New Static Cost-Effective Parameter for Interconnection Networks of Massively Parallel Computer Systems. In: Nayak, J., Abraham, A., Krishna, B., Chandra Sekhar, G., Das, A. (eds) Soft Computing in Data Analytics . Advances in Intelligent Systems and Computing, vol 758. Springer, Singapore. https://doi.org/10.1007/978-981-13-0514-6_15

Download citation

DOI: https://doi.org/10.1007/978-981-13-0514-6_15

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-13-0513-9

Online ISBN: 978-981-13-0514-6

eBook Packages: Intelligent Technologies and RoboticsIntelligent Technologies and Robotics (R0)