Abstract

A radiation-tolerant phase-locked loop (PLL) is designed in 65 nm CMOS technology. A double feedback loop self-sampling structure is proposed to improve the anti-radiation capability. A High matched current-based charge pump is hardened by using sensitive nodes compression and transformation technology. The simulation results show that the proposed PLL has no significant variations under heavy-ion and it could output good jitter signals with high frequency.

Access provided by CONRICYT-eBooks. Download conference paper PDF

Similar content being viewed by others

Keywords

1 Introduction

The performance of aerospace chip is improving rapidly. To meet the demand of high data rates transmission, SerDes (SERializer-DESerializer) is widely used. Increasing the communication data rates lead a more stringent specification the PLL clock jitter in terms of both random Gaussian jitter and deterministic jitter [1].

Previous studies have demonstrated that PLLs are vulnerable to single-event transients (SETs), resulting in missing pulses and phase displacement [2]. Due to single-event effects (SEEs), high energy particle will pass through semiconductor materials and deposit charge in sensitive devices. It is challenging to design high-performance phase-locked loops (PLLs) for space applications.

The traditional harden technology is unsuitable for PLL in SerDes. Because the existing technology in radiation-hardened PLL is based on the trade-off between anti-radiation ability and performance(jitter and frequency). The charge pump (CP) was identified as the most sensitive module. A voltage-based charge pump was proposed to significantly improve the single-event tolerance with considerable noise degradation [3]. Besides, the voltage-controlled oscillator (VCO) was studied to present increased susceptibility to single-event upsets (SEUs) in advanced technology nodes [4]. Triple modular redundancy (TMR) technique has been commonly utilized in the VCO circuit and frequency divider [5] to eliminate soft errors, but with great area and frequency penalties

In this paper, a radiation-immune PLL is proposed to improve the anti-radiation ability without degradation of jitter and frequency performance. In Sect. 2, PLL radiation hardening by process in 65 nm process is discussed. In Sect. 3, the novel double loop feedback self-sampling structure is proposed to remove the SET effect of divider and PFD. Current-based charge pump with sensitivity node transformation technology is proposed to improve the jitter performance of PLL. In Sect. 4, layout design and simulation analysis are discussed. In Sect. 5, conclusion is given.

2 Radiation Hardening by Process

The 65 nm process provides deep Nwell technology to achieve low noise. From the aspect of radiation-hardening, the deep Nwell can also absorb the SET current of heavy-ion strike.

The heavy-ion simulations have been performed using TCAD software. The simulation result is shown in Fig. 1. LET is 37.6 meV·cm2/mg, and the ion strike is irradiated normal to the chip surface.

As shown in Fig. 2(a), the SET current is all absorbed by the deep Nwell and the dummy transistor. The Fig. 2(b) shows that the voltage has no significant variations under heavy-ion when switch gate and the dummy transistors are built in deep Nwell.

3 Radiation Hardening by Design

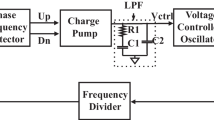

Traditional PLL is single loop negative feedback system consists of PFD, CP, LPF, DIV and VCO. When SET happen at one of the five components, it may lead the PLL out of lock state and the error bit rate of SerDes will increase.

The PFD and Divider are digital circuits and are very sensitive to SET, because they use the minimum gate length. To improve the anti-SET capability, we adapt the double loop to feedback the divided signals from VCO to PFD in Fig. 3. The advantage of this structure is that, it will largely reduce the sensitivity of feedback loops. As shown in Fig. 4, if the iron strikes the PFD1 and FBDIV2, it will only induce one loop to produce error signal in UP1 or UP2. The other loop operation remains good and will produce right UP and DN signals at the same time. The sampling circuit in Fig. 4 will let correct up and down signals(SUP, SUPB, SDN, SDNB) pass through. This double loop structure will compress the sensitive nodes of all the FBDIV and PFD into AND gates in sampler.

Previous study of voltage-based CP (V-CP) [4] employs large reference spurs and phase noise, which is not suitable for SerDes application. The proposed CP is especially suitable for low jitter application because its mismatch is quite low, as shown in Fig. 5. The differential structure of CP we used in this paper has alleviated the charge sharing of traditional charge pump by using two pairs of charge pump. It is similar to the structure of [6].

To improve the anti-radiation ability of CP, M8 is added. It is called sensitive nodes transformation technology, as shown in Fig. 6, the sensitive nodes of replica charge pump in the left is compressed to M8. As the sensitive nodes of CP are compressed into M8, the switch gate should be hardened at circuit level and layout level. As shown in Fig. 6, the original switch gate is one NMOS transistor, to absorb the large SET current, the dummy transistors are located round the switch gate. The gates of dummy transistors are all connected to ground and the drains of dummy transistors are all connected to power rail. The dummy transistors will not affect the operation of CP, but it will absorb the SET current when the ion strikes the sensitive nodes of CP.

4 Layout Design and Simulation Analysis

The test chip layout of PLL is shown in Fig. 7. We simulate the PLL with 65 nm process model to testify the low jitter and high frequency performance of this PLL. The RMS jitter and stability are calculated by Matlab program. The result is shown in Fig. 8. The Rj will not exceed 2.17 ps and the Dj is 6.5 ps, when the PLL is locked at 3.125 GHz.

The SET current model is added when the PLL is locked at 3.125 GHz, the unit interval of SerDes is 320 ps. To sample the correct RX data, the clock skew can not exceed 0.5UI. As shown in Fig. 9, the maximum skew that the VCO would produce is 41.64 ps, and the recovery time is 67 ns. Theoretically, the SET would not happen again in the 67 ns. The SerDes system will not have error data when SET happened in PLL.

We compare the proposed PLL with some recently published papers in Table 1. The deterministic jitter is 6.5 ps@65 nm. The integrated RMS jitter is 2.17 ps@65 nm. The jitter performance is good among all the references means that the charge pump can achieve better jitter performance than other PLLs. The proposed PLL will not decrease the error data rate when the PLL has SEE effects. Although Ref. [7] is more advanced in jitter and power consumption, but it is not suitable for radiation hardening because of interpolative phase-coupled oscillator DCO structure, the SET effect will lead the PLL out of lock state.

5 Conclusion

A radiation-tolerant PLL was designed and fabricated in 65 nm process. The PLL hardened by process was discussed. Various radiation hardening by design techniques were employed in order to have comprehensive radiation tolerance. A novel double loop feedback self-sampling structure was proposed to mitigate radiation effects of divider and PFD. Radiation hardened current based CP with sensitive nodes transformation technology was proposed to make the CP have smaller sensitive nodes. The simulation results demonstrate the good jitter performance of PLL when SET happens.

References

Wadekar, J., et al.: A 0.5–4 GHz programmable-bandwidth fractional-N PLL for multi-protocol SERDES in 28 nm CMOS. In: 2016 29th International Conference on VLSI Design, vol. 41, pp. 236–239 (2016)

Kauppila, A.V., et al.: Analysis of the single event effects for a 90 nm CMOS phase-locked loop. In: Proceedings of the Radiation Effects Components and Systems (RADECS), pp. 201–206, September 2009

Loveless, T.D., et al.: A hardened-by-design technique for RF digital phase-locked loops. IEEE Trans. Nucl. Sci. 53(6), 3432–3438 (2006)

Loveless, T.D., et al.: A single-event-hardened phase-locked loop fabricated in 130 nm CMOS. IEEE Trans. Nucl. Sci. 54(6), 2012–2020 (2007)

She, X., et al.: Single event transient tolerant frequency divider. IET Comput. Digit. Tech. 8(3), 140–147 (2014)

Yuan, H., et al.: A low-jitter self-biased phase-locked loop for SerDes. In: ISOCC 2016, pp. 550–554 (2016)

Deng, W., et al.: A 0.0066 mm 2780 μW fully synthesizable PLL with a current-output DAC and an interpolative phase-coupled oscillator using edge-injection technique. In: ISSCC Digest of Technical Papers, pp. 266–267, February 2014

Fischette, D., et al.: A 45 nm SOI-CMOS dual-PLL processor clock system for multi-protocol I/O. In: ISSCC Digest of Technical Papers, pp. 246–247, February 2010

Brownlee, M., et al.: Single-event transient characterization of a radiation-tolerant charge-pump phase-locked loop fabricated in 130 nm PD-SOI technology. IEEE Trans. Nucl. Sci. 63(4), 2402–2408 (2016)

Acknowledgments

This research was supported by National Natural Science Foundation of China Program (No. 61504169).

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2018 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Yuan, H., Chen, J., Liang, B., Guo, Y. (2018). A Radiation-Immune Low-Jitter High-Frequency PLL for SerDes. In: Xu, W., Xiao, L., Li, J., Zhang, C., Zhu, Z. (eds) Computer Engineering and Technology. NCCET 2017. Communications in Computer and Information Science, vol 600. Springer, Singapore. https://doi.org/10.1007/978-981-10-7844-6_5

Download citation

DOI: https://doi.org/10.1007/978-981-10-7844-6_5

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-10-7843-9

Online ISBN: 978-981-10-7844-6

eBook Packages: Computer ScienceComputer Science (R0)