Abstract

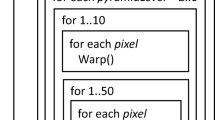

This paper presents the SONIC reconfigurable computing architecture and the first implementation, SONIC-1. SONIC is designed to support the software plug-in methodology to accelerate video image processing applications. SONIC differs from other architectures through the use of plug-in Processing Elements (PIPEs) and the Application Programmer’s Interface (API). Each PIPE contains a reconfigurable processor, a scaleable router that also formats video data, and a frame-buffer memory. The SONIC architecture integrates multiple PIPEs together using a specialised bus structure that enables flexible and optimal pipelined processing. SONIC-1 communicates with the host PC through the PCI bus and has 8 PIPEs. We have developed an easy to use API that allows SONIC-1 to be used by multiple applications simultaneously. Preliminary results show that a 19 tap separable 2-D FIR filter implemented on a single PIPE achieves processing rates of more than 15 frames per second operating on 512 x 512 video transferred over the PCI bus. We estimate that using all 8 PIPEs, we could obtain real-time processing rates for complex operations such as image warping.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Preview

Unable to display preview. Download preview PDF.

Similar content being viewed by others

References

Athanas, P.M., Abbott, A.L.: Real-Time Image Processing on a Custom Computing Platform. IEEE Computer 28(2), 16–24 (1995)

Mackinlay, P.I., Cheung, P.Y.K., Luk, W., Sandiford, R.D.: Riley-2: A flexible platform for codesign and dynamic reconfigurable computing research. In: Luk, W., Cheung, P.Y.K., Glesner, M. (eds.) Field-Programmable Logic and Applications. LNCS, vol. 1304, pp. 91–100. Springer, Heidelberg (1997)

Singh, S., Slous, R.: Accelerating Adobe Photoshop with Reconfigurable Logic. In: IEEE Symposium on FPGAs for Custom Computing Machines, April 15th - 17th, pp. 236–244 (1998)

Colaïtis, M.J., Jumpertz, J.L., Guérin, B., Chéron, B., Battini, F., Lescure, B., Gautier, E., Geffroy, J-P.: The Implementation of P3I, a Parallel Architecture for Video Real-Time Processing: A Case Study. Proceedings of the IEEE 84(7), 1019–1037 (1996)

Kung, H.T.: Computational Models For Parallel Computers. In: Elliot, R.J., Hoare, C.A.R. (eds.) Scientific applications of Microprocessors, pp. 1–15. Prentice Hall, Englewood Cliffs (1989)

Hudson, R.D., Lehn, D.I., Athanas, P.M.: A Run-Time Reconfigurable Engine for Image Interpolation. In: IEEE Symposium on FPGAs for Custom Computing Machines, April 15th - 17th, pp. 88–95 (1998)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 1999 Springer-Verlag Berlin Heidelberg

About this paper

Cite this paper

Haynes, S.D., Cheung, P.Y.K., Luk, W., Stone, J. (1999). SONIC – A Plug-In Architecture for Video Processing. In: Lysaght, P., Irvine, J., Hartenstein, R. (eds) Field Programmable Logic and Applications. FPL 1999. Lecture Notes in Computer Science, vol 1673. Springer, Berlin, Heidelberg. https://doi.org/10.1007/978-3-540-48302-1_3

Download citation

DOI: https://doi.org/10.1007/978-3-540-48302-1_3

Publisher Name: Springer, Berlin, Heidelberg

Print ISBN: 978-3-540-66457-4

Online ISBN: 978-3-540-48302-1

eBook Packages: Springer Book Archive