Abstract

A critical challenge in multifunctional heterogeneous systems-on-chip is efficiently delivering and intelligently managing high quality dynamically controlled secure power to support power efficient and portable systems. To achieve efficient real-time multi-voltage power delivery and management, a systematic, scalable, and secure system is required. A fine grain power management framework comprising a variety of circuits, algorithms, and architectures is described in this chapter to control power routing and switching, while optimally allocating power among a variety of different power domains at run time. Stability, security, and design complexity are included within this framework.

Access provided by CONRICYT-eBooks. Download chapter PDF

Similar content being viewed by others

Keywords

- Power Routing

- Power Domain

- Power Delivery System

- Dynamic Voltage And Frequency Scaling (DVFS)

- Dark Silicon

These keywords were added by machine and not by the authors. This process is experimental and the keywords may be updated as the learning algorithm improves.

Technology scaling has been driving the exponential growth of the semiconductor market over the last four decades, increasing integration density, speed, compactness, and functionality while decreasing power consumption and cost per function. Recently, the future of the More Moore (MM) virtuous circle has been challenged by a decrease in revenue growth and increase in the cost of research, development, and engineering (RD&E) of the worldwide semiconductor market [1, 2]. In addition, novel market segments such as intelligent transportation, innovative health care, sophisticated security systems, internet of things (IoT), and smart energy applications have emerged, requiring increasingly diverse functionality such as RF, power control, passive components, sensors/actuators, biochips, optical communication, and MEMs. These non-digital heterogeneous functionalities do not naturally scale (as shown in Fig. 7.1), yet provide significant value to the end customer. To support future societal needs, functional diversification (More-than-Moore (MtM)) has been recognized as a primary objective of semiconductor RD&E [2]. Integration of non-digital functionalities from the system board-level into system platforms such as systems-in-package (SiP) [3], systems-on-chip (SoC) [4], and TSV-based 3-D systems [5, 6] is a primary near and long term challenge of our semiconductor-based society.

Communication, synchronization, and power delivery are three essential components of synchronous integrated circuits. To facilitate the integration of these diverse functions, architectural, circuit, device, and material level solutions are required for each of these components. The evolution of signaling, clock distribution, and power delivery is illustrated in Fig. 7.1, exhibiting a roadmap for architectural solutions that scale while providing functional diversification. The primary foci of this chapter are to provide secure, power efficient, scalable power delivery systems, and a systematic methodology for intelligent on-chip power management .

With existing techniques for leakage current analysis, the security of the on-chip information has become a growing concern. The secure delivery of high quality power to the on-chip circuitry with minimum energy loss is a fundamental requirement of modern integrated circuits (ICs). The system-wide quality of the power supply can be efficiently addressed with distributed point-of-load (POL) power delivery [7,8,9], and includes the on-chip integration of multiple power supplies. Distributed power delivery requires the co-design of 100s of ultra-small power converters with many thousands of decoupling capacitors and billions of nonlinear current loads within multiple power domains, significantly increasing the design complexity of existing power delivery systems. Systems with 100s of on-chip power domains and 10s of different power supply voltages have recently been reported, and thousand core ICs are being considered [10,11,12,13,14,15]. The number of transistors purposely being under utilized (“dark silicon”) in future multicore ICs is expected to increase rapidly; 21% dark silicon at the 22 nm technology node, and more than 50% dark silicon at the 8 nm technology node have recently been reported [16], requiring methodologies to manage power on-chip [17,18,19,20]. Per core dynamic voltage scaling (DVS) and dynamic voltage and frequency scaling (DVFS) are primary design techniques to efficiently manage the power budget within 100s of power domains and thousands of cores [21,22,23]. These systems require the on-chip integration of compact controllers, further increasing the design complexity of these power management and delivery systems.

Centralized dynamic power management has recently been used to increase power efficiency in modern heterogeneous systems [24, 25]. Centralized power delivery systems are often characterized by a long feedback path from the individual power domains to a single power management controller, dissipating additional power due to unnecessary data transport, and limiting real-time control over the energy budget due to the slow feedback response. In addition, leakage current in centralized power delivery systems can be efficiently used to evaluate the actual current flowing to the load and extract encrypted information from the system. Security attacks on power delivery systems therefore pose a significant threat on encrypted information. It has recently been demonstrated that power attacks are effective and computationally feasible for a limited number of instances under attack (for example, up to 8 bits under attack [26]). A centralized approach that places the power management functions in one or a few locations not only affects system scalability, but potentially makes the system more prone to power attacks. While distributed power delivery may be preferable for preventing power attacks, communicating energy information in a distributed power management scheme increases the vulnerability of a system to power attacks. To protect on-chip information, specialized circuits and design techniques need to be developed that are resilient to security attacks, possibly trading off performance and power consumption for system security. Alternatively, to efficiently secure on-chip information, the detection of system intrusion followed by a protective action should also be considered. To efficiently and securely manage power while delivering high quality current to complex next generation systems, enhanced methodologies, architectures, and management policies for designing scalable, intelligent power management and delivery systems with fine granularity of dynamically controlled voltage levels are required.

A general platform for delivering power is described here, which is called a power network on-chip (or PNoC), to provide systematic, scalable, and secure management of the power delivery process in heterogeneous integrated circuits. PNoC-based power delivery and management simultaneously enhances the quality of power, performance, scalability, and cost. Since power delivery and management are fundamental to all nanoelectronic systems, specialized algorithms, architectures, and approaches will greatly accelerate the development of next generation heterogeneous systems.

The rest of the chapter is organized as follows. The principles of the PNoC design methodology, architecture, and challenges are described in Sect. 7.1. Routing, stability, security, and design complexity and system scalability are discussed, respectively, in Sects. 7.2, 7.3, 7.4, and 7.5. Some concluding remarks are offered in Sect. 7.6.

7.1 Power Network on-Chip for Distributed Power Delivery and Management

Power is traditionally managed off-chip with energy efficient power converters, delivering high quality DC voltage and current to the on-chip electrical grid which reliably distributes the on-chip power [7]. The supply voltage, current density, and parasitic impedances, however, scale aggressively with each technology generation, degrading the quality of the power delivered from the off-chip power supplies to the on-chip load circuitry. To mitigate the parasitic impedances of the board, the power supply-in-package (PSiP) approach with partially off-chip yet in package power supplies has recently been considered as an intermediate power supply technology with respect to cost, complexity, and performance [27]. To lower the parasitic impedance of both the board and package, the power is regulated on-chip. To fully integrate a power converter on-chip, advanced passive components, packaging technologies, and circuit topologies are essential. Recently, several power converters suitable for on-chip integration have been fabricated [8, 9, 28,29,30,31,32,33,34,35,36,37,38,39,40,41,42]. Based on these power converters, a power supply system with multiple on-chip power converters is now possible.

The integration of on-chip power regulators is an important cornerstone to the power delivery process. A single on-chip power converter is however not capable of supplying sufficient, high quality regulated current to the billions of current loads within the 10s of on-chip power domains. To maintain a high quality power supply despite increasing the on-chip parasitic impedances, 100s of ultra-small power regulators should ultimately be integrated on-chip, close to the loads within the individual multiple power domains [8, 9, 18]. Integrated power converters however suffer from low power efficiency. Thus, area and power efficiency are primary concerns with a POL approach. To increase the power efficiency of a POL power delivery system, a system-wide methodology is necessary. The power is primarily converted with several efficient power converters, delivered to 10–100s of ultra-small on-chip LDOs, and regulated by those LDOs close to the points-of-load. To support DVS and DVFS, scalable power delivery systems are required that are capable of dynamically redistributing high quality regulated power to billions of loads in multiple, functionally diverse power domains. To satisfy power limits at each technology node, the increasing amount of “dark silicon” should be exploited [16]. To switch transistors with greater granularity in real-time, a distributed architecture and a systematic dynamically controllable power delivery and management methodology are required.

The key concept in systemizing the design of power delivery is to convert the power off-chip, in-package, and/or on-chip with multiple power efficient but large switching power supplies, deliver the power to on-chip voltage clusters, and regulate the power with 100s of linear low dropout (LDO) regulators at the point-of-load [43]. The principles of the PNoC design methodology are described in Sect. 7.1.1. In Sect. 7.1.2, the performance of the PNoC architecture is compared with existing approaches based on the evaluation of several test cases. Challenges of distributed power delivery and management are discussed in Sect. 7.1.3.

7.1.1 Concept of Power Network-on-Chip

The concept of a power network on-chip is introduced here as a vehicle for distributed on-chip power management . The analogy between a NoC and PNoC is illustrated in Fig. 7.2 with simplified NoC and PNoC models. An NoC separates computation from communication, enhancing the performance, scalability, and control of quality of service (QoS), while increasing engineering productivity in the development of heterogeneous integrated systems. Similar to a network-on-chip, the PNoC approach provides a scalable platform for efficient power delivery and management. In addition, enhanced control over the quality of power (QoP), real-time voltage scaling, and integration of emerging technologies while mitigating invasive and non-invasive power attacks within the proposed framework are possible with PNoC.

7.1.2 Power Network-on-Chip Architecture

SoC platforms will consist of 100s of heterogeneous hardware agents (application processors, DSP cores, fixed function accelerators, sensors, and actuators), each with unique power, performance, and QoS requirements [4, 44, 45]. While the quality of the power supply can be efficiently addressed with a point-of-load power delivery system [9], distributed power delivery is impractical with existing ad hoc approaches. Maintaining a secure and stable power delivery system is an additional concern. To cope with the design complexity of distributed on-chip power delivery, a novel and scalable power delivery platform is required that relies on the reuse of components, secure architectures, secure methodologies, and applications. A power network on-chip utilizes a specific architecture and design methodology to achieve intelligent power management and scalable, secure power delivery in heterogeneous ICs.

Centralized dynamic power management is commonly used to increase power efficiency in modern heterogeneous systems. A typical power delivery scheme is illustrated in Fig. 7.3 for an SoC with multiple power domains within each of n individual modules. In this configuration, the power is managed by a centralized power management system. These centralized power delivery systems are often characterized by a long feedback path from the individual power domains to a single power management controller, dissipating extra power due to unnecessary data transport, and limiting real-time control over the energy budget due to the slow feedback response. In addition, a centralized approach places all of the power management functions in one or a few locations, affecting system scalability.

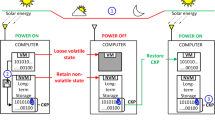

A distributed power delivery system based on the PNoC approach is shown in Fig. 7.4. In this scheme, the energy budget is managed locally with intelligent distributed power routers, considering essential information such as timing slacks, voltages, currents, and temperatures that are sensed within the individual power domains. Real-time fine grain power management is possible by shortening the power domain-to-router feedback path (as compared to the centralized approach). Power management adjustments therefore redistribute the overall energy budget in a near real-time manner by communicating local power management decisions among the individual power routers within a PNoC. A centralized power management mechanism can also be integrated to support predetermined DVS and DVFS operations. The management functions in this configuration are coordinated with specialized algorithms and controllers among the intelligent, distributed, and centralized power management mechanisms.

A PNoC composed of power routers connected to global power grids and locally powered loads is shown in Fig. 7.5. The global power from the converters is managed by the power routers, delivered to power domains, and regulated within locally powered loads. A locally powered load combines all of the current loads and decoupling capacitors physically located within a specific on-chip region within a power domain. This system senses the voltages and currents throughout the system, and manages the POL regulators with power switches. Based on these sensed voltages and currents, a programmable controller makes real-time decisions to apply a new set of configurations to the routers per time slot, dynamically managing the on-chip power delivery process. The power delivery policies are dynamically customized with specialized algorithms through a microcontroller that routes the power. These algorithms satisfy real-time power and performance requirements. Functionally diverse heterogeneous systems require additional degrees of power control and management of resources. In these complex heterogeneous systems, each power router is connected to a router-to-router communication channel to dynamically manage the shared energy budget of all of the power domains within a voltage cluster, exploiting the built-in modularity and local intelligence of PNoC to support scalable power delivery systems.

7.1.3 Challenges in Distributed Power Delivery

The power in PNoC based SoCs is virtually managed through specialized power routers, switches, and programmable control logic, while supporting scalable power delivery in heterogeneous ICs. A PNoC is comprised of physical links and routers that provide both virtual and physical power routing. This system senses the voltages and currents throughout the system, and manages the POL regulators through power switches. Based on the sensed voltages and currents, a programmable unit makes real-time decisions to apply a new set of configurations to the routers per time slot, dynamically managing the on-chip power delivery process. The challenge of efficiently routing the power in real-time is discussed in Sect. 7.2, and a power routing approach is evaluated.

A distributed system with multiple parallel connected LDO regulators delivering power to a single grid exhibits degraded stability due to complex interactions among the LDO regulators, power distribution network, and current loads. Thus, the stability of these parallel connected voltage regulators is an additional concern and requires accurate evaluation. To design a stable closed loop regulator, sufficient phase margin in the open loop transfer function is required. Phase margin is a necessary and sufficient parameter for determining the stability of a single LDO. Evaluating the open loop characteristics is however not practical with parallel LDO regulators due to the multiple regulation loops. Evaluating the stability of a distributed power delivery system is therefore not possible with the traditional phase margin criterion. An alternative stability criterion is proposed in Sect. 7.3 for evaluating the stability of parallel voltage regulators driving a single power grid .

Securing information in modern ICs is another significant challenge that needs to be addressed. Non-invasive and invasive power attack methods [26, 46,47,48] are widely used today to decode encrypted information or reduce the performance and/or lifetime of computing devices. A common countermeasure for power analysis is masking the effective power consumption of an IC by injecting additional power or modifying power profiles with DVS techniques [49]. These approaches however degrade the overall power efficiency of the system. Alternatively, securing information and performance with traditional algorithmic encryption techniques lack scalability and often do not exhibit sufficient security [50]. To efficiently mitigate power analysis attacks, specialized design flows and circuits that disrupt the correlation between the internal leakage power and overall power consumption are necessary. Accurate evaluation of power efficiency and security levels is required. Secure on-chip power networks are currently under development to efficiently manage power in modern ICs. The sensitivity of PNoC to power attacks is discussed in Sect. 7.4.

The complexity and scalability of a distributed nonlinear dynamically controllable POL power supply system is a significant design issue. Automated modeling, optimization, and synthesis techniques for complex analog circuits have recently been considered [51], and automated tools for analog circuits with 100s of components have become commercially available [51]. To automate the design of a power delivery system, accurate methods to evaluate performance metrics (e.g., quality of transient response, stability, and power) are required. Automating the design of power delivery system is discussed in Sect. 7.5.

7.2 Power Routing in SoCs

The PNoC architecture is a mesh of power routers and locally powered loads, as depicted in Fig. 7.2. The power routers are connected through power switches, distributing current via power grids to those local loads with similar voltage requirements. A PNoC is illustrated in Fig. 7.6 for a single voltage cluster with nine locally powered loads and three different supply voltages, \(V_{DD,1}\), \(V_{DD,2}\), and \(V_{DD,3}\). The power network configuration is shown at two different times, \(t_1\) and \(t_2\).

The power routers, local current loads, and power grids are described, respectively, in Sects. 7.2.1, 7.2.2, and 7.2.3. Different PNoC topologies and specific design objectives are also considered. A PNoC with four power routers is evaluated in Sect. 7.2.4.

7.2.1 Power Routers

The efficient management of the energy budget is dynamically maintained by the power routers. Each power domain is controlled by a single power router. A router topology ranges from a simple linear voltage regulator, shown in Fig. 7.7a, to a complex power delivery system, as depicted in Fig. 7.7b, with sensors, dynamically adaptable power supplies, switches, and a microcontroller. This structure features real-time voltage/frequency scaling, adaptable energy allocation, and precise control over the on-chip QoP. With PNoC routers, the power is managed locally based on specific local current and voltage demands, decreasing the dependence on the remotely located loads and power supplies. Thus, the scalability of the power delivery process is greatly enhanced with the PNoC approach.

7.2.2 Locally Powered Loads

Locally powered loads with different current demands and power budgets can be efficiently managed with PNoC. The local power grids provide a specific voltage to the nearby load circuits. The highly complex interactions among the multiple power supplies, decoupling capacitors, and load circuits are important, where the interactions among the nearby components are typically more significant. The effective region for a point-of-load power supply is the overlap of the effective regions of the surrounding decoupling capacitors [9, 52]. Loads within the same effective region are combined into a single equivalent locally powered load regulated by a dedicated LDO. All of the LDO regulators within a power domain are controlled by a single power router.

7.2.3 Power Grid

A shared power grid with multiple LDO sources and dedicated power grids each driven by a separate LDO is considered here. These topologies are illustrated in Fig. 7.8 with two power routers, and shared and dedicated local power grids. The dedicated power grids require fine grain distribution of the local power current. Alternatively, a shared power grid with multiple LDO sources is prone to stability issues due to current sharing, and process, voltage, and temperature variations. Specialized adaptive mechanisms are included within the power routers to stabilize a power delivery system within a multi-source shared power grid.

7.2.4 Case Study

To evaluate the performance of a power router, a PNoC with four power routers is considered, supplying power to four power domains. IBM power grid benchmarks [53] model the behavior of the individual power domains. To simulate a dynamic power supply in PNoC, the original IBM voltage profiles are scaled to generate target power supplies between 0.5 and 0.8 V. Target voltage profiles with four voltage levels (0.8, 0.75, 0.7, and 0.65 V) within a PNoC are illustrated in Fig. 7.9. The number of power domains with each of the four power supply voltages changes dynamically based on the transient power requirements of the power domains.

A schematic of a PNoC with four power domains (I, II, III, and IV) and four power routers (\(\text {PR}_\text {I}\), \(\text {PR}_\text {II}\), \(\text {PR}_\text {III}\), and \(\text {PR}_\text {IV}\)) is presented in Fig. 7.10. Each of the power routers is composed of an LDO with four switch controlled reference voltages to support dynamic voltage scaling. In addition, the power routers feature adaptive RC compensation and current boost networks controlled by load sensors to provide quality of power control and optimization, as shown in Fig. 7.11. The adaptive RC compensation network is comprised of a capacitive block connected in series with two resistive blocks, all digitally controlled. These RC impedances are digitally configured to stabilize the LDO within the power routers under a wide range of process variations. The current boost circuit is composed of a sensor block that follows the output voltage at the drain of transistor \(\text {M}_\text {P}\) (see Fig. 7.11), and a current boost block that controls the current through the differential pair within the LDO. When a high slew rate transition at the output of the LDO occurs, the boost mode is activated, raising the tail current of the differential pair within the LDO regulator. Alternatively, during regular operation, no additional current flows into the differential pair, enhancing the power efficiency of the LDO. A description of some configurations of the load sensor and adaptive networks can be found in [18].

The power routers are connected with controlled switches to mitigate load transitions in domains with similar supply voltages. To model the RLC parasitic impedances of the package and power network, non-ideal LDO input and output impedances (\(\text {PN}_\text {I}\), \(\text {PN}_\text {II}\), \(\text {PN}_\text {III}\), and \(\text {PN}_\text {IV}\)) are considered, as shown in Fig. 7.10. The load current characteristics are listed in Table 7.1 for each of the four domains. The PNoC is simulated in SPICE. The simulation results are presented in Fig. 7.12, exhibiting a maximum error of 0.35%, 2.0%, and 2.7% for, respectively, the steady state dropout voltage, load regulation due to the output current switching, and load regulation due to the dynamic PNoC reconfigurations. Good correlation with the required power supply in Fig. 7.9 is demonstrated. The power savings in each of the power domains range between 21.0 and 31.6% as compared to a system without dynamic voltage scaling. These average power savings demonstrate that the PNoC architecture can control power supplies in real-time, optimizing the power efficiency of the overall power delivery system [54,55,56].

7.3 Stable Distributed Power Delivery Systems

Understanding the effects of the frequency domain parameters on the time domain characteristics provides significant insight into the transient behavior of complex systems [57, 58]. Traditionally, the phase margin of the output response determines the stability of a single LDO regulator. Similarly, a criterion is required for determining the stability of a distributed power delivery system.

A distributed power delivery system with two or more power supplies driving a single power grid is depicted in Fig. 7.13a. In this distributed system, the power supplies can be combined into a single power delivery system, yielding an equivalent single port network, as shown in Fig. 7.13b. Note that the output impedance of the equivalent single port network, \(Z_{TOT}\) in Fig. 7.13b, is the parallel combination of all of the output impedances \(Z_i, i = 1, \ldots , N\) of the individual power supplies shown in Fig. 7.13a. The output impedance of a distributed power delivery system is based on the individual output impedance of the parallel connected elements. Alternatively, a method is needed to identify those loops that cause instability in a system with multiple interacting feedback paths. The open loop transfer function, traditionally used to determine the stability of a lumped power delivery system, cannot be applied to a distributed power delivery system with multiple control loops [59]. A criterion for evaluating the stability of a multi-feedback path system composed of distributed power regulators is therefore needed.

Necessary and sufficient conditions for a stable distributed power delivery system are described in this section. These conditions are based on the observation, proven in [60], that a linear, time-invariant (LTI) system is stable when coupled to an arbitrary passive environment if and only if the driving point impedance is a passive system. A distributed power delivery system is therefore stable if and only if the equivalent output impedance \(Z_{TOT}\) satisfies passivity requirements. The passivity of an LTI system is described here in terms of frequency domain parameters.

An LTI system is passive if the system can only absorb energy, yielding, in mathematical terms [61],

where v(t) and i(t) are, respectively, the voltage across the system and the current flowing through the system. The total energy delivered to a passive system is determined from (7.1) based on the Parseval Theorem, exhibiting, for all positive currents,

where \(Z(s) = V(s)/I(s)\) is the system impedance, and V(s) and I(s) are, respectively, the phasor voltage and current of the system. The passivity condition based on (7.2), {\(Re[Z(\sigma + j\omega )] \ge 0, \forall \sigma > 0\)}, can be simplified based on [62], yielding the following sufficient conditions for passivity of an LTI system:

A distributed system is, therefore, exponentially stable (converges within an exponential envelope) if and only if the impedance of the system satisfies these passivity requirements, marginally stable (oscillates with constant amplitude) if and only if the voltage and current phasors are shifted by precisely \(90^\circ \), and unstable otherwise. The phase of the output impedance is an efficient alternative to determine the stability of these distributed systems, since the traditional phase margin approach is not practical due to the multiple control loops.

7.3.1 Experimental Evaluation of Stability Criterion

To demonstrate the concept of a stable distributed power delivery system based on the passivity-based stability criterion , a distributed power delivery system with six LDO regulators is evaluated. A model of the power delivery system with the six LDO regulators and a distributed power delivery network is shown in Fig. 7.14. Each power supply in the power delivery system is an LDO regulator [63] composed of an error amplifier (EA), output device (M\(_\text {P}\)), and compensation network \(R_C C_C\), as depicted in Fig. 7.15. A three current mirror operational transconductance amplfier (OTA) topology [59] is used within each error amplifier.

LDO topology [59]

The output impedance of the parallel connected voltage regulators is a primary factor in determining the stability of a distributed power delivery system, and can be characterized by the poles and zeros of the individual LDO regulators. To maintain stability in a distributed power delivery system with n LDO regulators, the poles of the output impedance \(Z_{OUT}^{TOT}(s)\) must all be left plane poles and the phase of \(Z_{OUT}^{TOT}(s)\) must be within the \((-90^\circ , 90^\circ )\) range \(\forall ~ s\).

The stability of the proposed power delivery system is demonstrated on an example system assuming a total current load of 300 mA. Load sharing among the LDO regulators in the system exhibits a wide range of LDO currents (between 20 and 100 mA for an individual LDO regulator). The LDO in closest proximity with the current load supplies the largest portion (100 mA) of the total current requirements, which is higher by a factor of two than the average current load (52 mA) supplied by a single LDO. Alternatively, remote LDOs supply significantly less current (down to 20 mA), only half of the average LDO load current. The output impedance of the system under this load sharing scenario is evaluated for each of the LDO regulators and the overall distributed power delivery system. The poles and zeros within the range of interest are shown in Fig. 7.16. Note that the poles of the system output impedance are limited by the frequency range of the individual LDO poles. Thus, a distributed power delivery system with individually stable LDO regulators under all feasible load currents exhibits no right half plane poles (RHP). The stability of a multi-feedback system with individually stable power supplies is therefore limited by the phase of the system output impedance. To demonstrate the effect of the phase of the output impedance on the stability of a distributed system, the transient response and output impedance phase \(\angle Z_{OUT}\) of the distributed system with six LDO regulators is shown in Fig. 7.17. In agreement with the passivity-based stability criterion , the output response diverges (oscillates with increasing amplitude), and converges within an exponential envelope for, respectively, \(| \angle Z_{OUT} | > {90^\circ }\) and \(| \angle Z_{OUT} | < {90^\circ }\). Note that the system with \(C_C = \) 0.5 pF and \(\max _{\forall f}\{\angle Z_{OUT}\} = {89^\circ }\) slowly converges to the steady-state solution, exhibiting an inappropriate underdamped response to effectively regulate the voltage in a power delivery system. Alternatively, a system with \(C_C =\) 5 pF and \(\max _{\forall f}\{\angle Z_{OUT}\} = {70^\circ }\) exhibits an overdamped response with a significant margin of stability. A strong correlation therefore exists between the phase shift of the output voltage and load current, and the effective stability margin of the system. Based on this observation, the phase margin of the output impedance for a distributed power delivery system is

A distributed power delivery system is therefore unstable, stable, or marginally stable if the phase margin of the output impedance is, respectively, negative, positive, or zero. A safe phase margin of the output impedance should satisfy specific design criteria while avoiding excessively underdamped and overdamped voltage regulated systems.

7.4 Secure Power Delivery and Management

Non-invasive methods, such as side channel power attacks [26, 46, 47], are widely used to decode encrypted information based on the co-analysis of stored data and leakage current profiles. Alternatively, invasive power attacks (e.g., battery draining by sleep deprivation) [48] can be initiated to reduce the performance and/or lifetime of computing devices. Sensing leakage current in power delivery systems can be exploited to evaluate a specific current at the loads during cyber attacks. Several methods to mitigate power analysis attacks have recently been proposed at the architectural, algorithmic, and circuit levels [49, 50, 64]. These approaches usually mask the effective power consumption of an IC, degrading the overall power efficiency of the system. Circuits and design approaches to efficiently prevent, detect, and mitigate cyber attacks are therefore required.

The nature of power delivery circuits significantly affects the security of the system-wide power delivery system. For example, the LDO output current is proportional to the current dissipated within a linear regulator. This sensed excess current can be exploited to determine the actual current delivered by a regulator to a load. These power supplies with correlated leakage and effective currents are more susceptible to power security attacks. Alternatively, the distributed nature of the PNoC-based power delivery scheme increases the granularity of the power sources while decreasing the ability to observe system-wide power profiles based on the leakage current of an individual power supply. To efficiently mitigate power analysis attacks, existing voltage converters and regulators should be evaluated in terms of security requirements, and power supply circuits with strongly correlated internal leakage current and overall power dissipation should be avoided.

7.5 Automated Design of Stable Power Delivery Systems

To address the issues of power delivery complexity, a power delivery system should provide a scalable modular architecture that supports the integration of additional functional blocks and power features (e.g., DVS, DVFS, QoS and stability control, security mechanisms, and adaptive mechanisms to cope with PVT and enhance system efficiency) without requiring the re-design of the power delivery system. The architecture should also support heterogeneous circuits and technologies. An important aspect of systemizing the power delivery design process is to automate the design of certain complex analog circuits, further reducing the design complexity of power delivery systems. A process for automating the design of stable power delivery systems is described in this section.

Existing automated techniques for designing analog circuits are based on numerical optimization and evaluation engines [51]. Parametric models characterize the performance of an analog circuit (e.g., gain, bandwidth (BW), slew rate (SR), or phase margin (PM)) based on circuit design variables (e.g., transconductance and voltage bias) [51]. The performance of an individual power supply is typically characterized by a set of parameters, such as the DC gain, phase margin, DC offset, slew rate, and power dissipation. Alternatively, a distributed power delivery system is evaluated based on both the performance of the individual power regulators and additional performance metrics of the overall system such as the phase margin of the output impedance. The design complexity and stability of distributed on-chip power delivery systems can both be addressed by integrating the passivity-based stability criterion within existing automated design methodologies. An automated flow for designing a stable distributed power delivery system is shown in Fig. 7.18. The first stage of the flow is based on a standard parametric performance modeling technique [51]. During this stage, an LDO regulator is synthesized based on the specific LDO topology and design objectives. The output of the first stage is applied during the second stage to determine the number and location of the parallel connected power supplies in the distributed power delivery system. During this second stage, a distributed power delivery system with a different number and location of voltage regulators is iteratively evaluated based on the passivity-based stability criterion and distributed power supply placement algorithms [9, 65]. During each iteration, the worst case load sharing scenario is determined for a specific power delivery system. The passivity-based stability of the distributed system is evaluated based on the individual current loads. If required, the number and location of the power supplies are updated. The number and location of the parallel connected power supplies that satisfies the quality of power and stability requirements of the distributed power delivery system are determined.

Floorplan of ISPD’11 circuits [66] a superblue5, b superblue10, c superblue12, and d superblue18

The operation of the second stage of the automated PBSC-based design flow is demonstrated here based on the ISPD’11 placement benchmark suite circuits [66]. The floorplan of the superblue5, superblue10, superblue12, and superblue18 circuits is illustrated in Fig. 7.19. Each of the circuits is composed of 1000s of fine grain rectangular shapes. To reduce the complexity of the circuit evaluation process, the fine grain shapes are combined into larger rectangular blocks. Of the combined blocks, only the largest blocks are considered, producing a reduced floorplan. The magnitude of the distributed current loads is proportional to the size of these blocks with, for this example, a total load current of 1 A. The location of each of the current loads is at the center of the corresponding rectangular block. The number of fine grain shapes, large blocks, coverage of reduced floorplan, and power grid characteristics are listed in Table 7.2. Note that the blocks in the reduced floorplan occupy more than 85% of the total active circuit area.

A constant voltage is ideally distributed to all of the current loads within a circuit. Practically, the quality of power is degraded due to on-chip parasitic interconnect impedances. A map of the voltage drops of the superblue5 circuit without on-chip power supplies is shown in Fig. 7.20, yielding a maximum voltage drop of 23.4% assuming an off-chip voltage supply of 1 V. To address the quality of the on-chip power, power delivery systems with a single on-chip power supply (case 1), three on-chip power supplies (case 2), and twelve on-chip power supplies (case 3) are considered. For each of the three cases, the IR drop of a distributed power delivery system is evaluated based on the IR drop algorithm for a power grid with multiple power supplies and current loads [67]. The location of the power supplies in cases 1 and 2 is modeled as a mixed integer nonlinear programming problem [9], and optimized based on a general algebraic modeling system (GAMS) [68]. In case 3, the power supplies are uniformly distributed on-chip. The stability is evaluated for each of the three cases based on the passivity-based criterion. A map of the voltage drops and phase of the output impedance within superblue5 for a different number of on-chip power supplies is shown in Fig. 7.21. The maximum voltage drop decreases with an increasing number of power supplies, exhibiting a reduction in the maximum voltage drop of 14.2%, 20.3%, and 22.3% with, respectively, a single, three, and twelve on-chip power supplies. Alternatively, the output current of the individual regulators is dependent on the number of power supplies, affecting both the phase of the output impedance and the stability characteristics of the distributed system. Based on the stability criterion , the superblue5 circuit with the power delivery system is stable with a single power supply and three power supplies (the phase of the output impedance is within the \((-90^\circ , 90^\circ )\) range), and unstable with twelve power supplies (the minimum phase of the output impedance is \({-95.1^\circ < -90^\circ }\)). While the distributed power delivery system with twelve power supplies exhibits higher quality of power than the systems with fewer power supplies, this system is shown to be unstable under a step load. Thus, a system with fewer power supplies is preferable to deliver power within the superblue5 circuit when considering both quality of power and system stability.

The second stage of the automated PBSC-based design flow, shown in Fig. 7.18, is implemented in Matlab. Pseudo-code of the Matlab algorithm is summarized in Algorithm 1. An LDO model [59] describes the small signal response of the on-chip power supplies, and is used to evaluate the output impedance of the power supplies and overall power delivery system. The power delivery systems for the ISPD’11 benchmark circuits, superblue5, superblue10, superblue12, and superblue18, are evaluated based on this algorithm. The maximum IR drop and stability characteristics are listed in Table 7.3. For these benchmark circuits, the maximum voltage drop is significantly less with increasing number of on-chip power supplies. Alternatively, the stability of the distributed power delivery system is a function of the specific load distribution and affected by the output impedance of the POL power delivery system. The automated PBSC-based design flow generates a distributed power delivery system that addresses both the quality of power and stability requirements.

7.6 Summary

Delivering high quality, dynamically controlled power to support power efficient and portable systems is a critical challenge in heterogeneous systems-on-chip. Efficiently providing multiple point-of-load on-chip regulated voltages requires fundamental changes to the power delivery and management process. To cope with the increasing design complexity of heterogeneous, distributed, and dynamically controllable power delivery systems while enhancing the scalability of both static and dynamic power delivery systems, a systematization of the power delivery and management process is required.

The concept of intelligent on-chip networks for delivering power is introduced here as a means to address the objectives of scalable, systematic power delivery and management in high performance heterogeneous integrated systems. Primary design and performance challenges, such as physical and virtual power routing, stability, security, complexity, and scalability of PNoC based systems are reviewed. The PNoC architecture is evaluated, exhibiting significant power savings as compared to traditional power delivery systems.

A passivity-based stability criterion is described. Based on this criterion, a distributed power delivery system is stable if the total output impedance of the parallel connected LDOs exhibits no right half plane poles and a phase between \(-90 ^\circ \) and \(+90 ^\circ \). Similar to a single voltage regulator, the phase margin of the output impedance (the difference between the maximum phase and \(90^\circ \)) determines the stability of a distributed power delivery system. The integration of emerging techniques for mitigating power attacks within the proposed PNoC platform is discussed. To efficiently mitigate power analysis attacks, power supply circuits with strongly correlated internal leakage power and overall power dissipation should be avoided. Distributed power management functions are preferable to make the system less prone to power attacks.

Reducing the design complexity while increasing the scalability of the power delivery design process with on-chip power networks is described. To further reduce the design complexity, a process for automating the design of power delivery systems is proposed. The automated design flow is evaluated with ISPD benchmarks, exhibiting a distributed power delivery system that addresses both the quality of power and stability requirements. Distributed intelligence should be added to on-chip power networks to provide a secure and systematic power delivery and management process while reducing design complexity and increasing scalability.

References

Semiconductor Industry Association, The International Technology Roadmap for Semiconductors (2012), http://www.itrs.net

W. Arden, M. Brillout, P. Cogez, M. Graef, B. Huizing, R. Mahnkopf, More-than-Moore (2010), http://www.itrs.net

P. Cauvet, S. Bernard, M. Renovell, System-in-package, a combination of challenges and solutions, in Proceedings of the IEEE VLSI Test Symposium, pp. 193–199, May 2007

W. Wolf, A.A. Jerraya, G. Martin, Multiprocessor system-on-chip (MPSoC) technology. IEEE Trans. Comput. Aided Design Integr. Circuits Syst. 27(10), 1701–1713 (2008)

V.F. Pavlidis, E.G. Friedman, Interconnect-based design methodologies for three-dimensional integrated circuits. Proc. IEEE 97, 123–140 (2009)

V.F. Pavlidis, E.G. Friedman, Three-Dimensional Integrated Circuit Design, Morgan Kaufmann (2009)

R. Jakushokas, M. Popovich, A.V. Mezhiba, S. Kose, E.G. Friedman, Power Distribution Networks with On-Chip Decoupling Capacitors, 2nd edn. (Springer, 2011)

S. Kose, S. Tam, S. Pinzon, B. McDermott, E.G. Friedman, Active filter based hybrid on-chip DC-DC converters for point-of-load voltage regulation. IEEE Trans. Very Large Scale Integr. (VLSI) Circuits, 21(4), 680–691 (2013)

S. Kose, E.G. Friedman, Distributed on-chip power delivery. IEEE J. Emerg. Sel. Topics Circuits Syst. 2(4), 704–713 (2012)

Y. Kanno et al., Hierarchical power distribution with 20 power domains in 90-nm low-power multi-CPU processor, in Proceedings of the IEEE International Solid-State Circuits Conference, pp. 540–541, February (2006)

T. Hattori et al., A power management scheme controlling 20 power domains for a single-chip mobile processor, in Proceedings of the IEEE International Solid-State Circuits Conference, pp. 542–543, February (2006)

Y. Kikuchi et al., A 40 nm 222 mW H.264 full-HD decoding, 25 power domains, 14-core application processor with x512b stacked DRAM. IEEE J. Solid-State Circuits 46(1), 32–41 (2011)

D.N. Truong, W.H. Cheng, T. Mohsenin, Z. Yu, A.T. Jacobson, G. Landge, M.J. Meeuwsen, C. Watnik, A.T. Tran, Z. Xiao, E.W. Work, J.W. Webb, P.V. Mejia, B.M. Baas, A 167-processor computational platform in 65 nm CMOS. IEEE J. Solid-State Circuits 44(4), 1130–1144 (2009)

S.Y. Borkar, Thousand core chips—a technology perspective, in Proceedings of the IEEE/ACM Design Automation Conference, pp. 746–749, June 2007

D. Yeh, L.-S. Peh, S. Borkar, J. Darringer, A. Agarwal, W.-M. Hwu, Thousand-core chips [Roundtable]. IEEE Design Test Comput. 25(3), 272–278 (2008)

H. Esmaeilzadeh, E. Blem, R. St. Amant, K. Sankaralingam, D. Burger, Dark silicon and the end of multicore scaling, in Proceedings of the ACM International Symposium on Computer Architecture, pp. 365–376, June 2011

I.P.-Vaisband, Power Delivery and Management in Nanoscale ICs, in Ph.D. Thesis (University of Rochester, May 2015)

I. Vaisband, B. Price, S. Kose, Y. Kolla, E.G. Friedman, J. Fischer, Distributed LDO regulators in a 28 nm power delivery system. Analog Integr. Circuits Signal Proces. 83(3), 295–309 (2015)

S. Gangopadhyay, S.B. Nasir, A. Raychowdhury, Integrated power management in IoT devices under wide dynamic ranges of operation, in Proceedings of the IEEE/ACM Design Automation Conference, May 2015

I. Vaisband, M. Azhar, E.G. Friedman, S. Kose, Digitally controlled pulse width modulator for on-chip power management. IEEE Trans. Very Large Scale Integr. (VLSI) Circuits 22(12), 2527–2534 (2014)

P. Macken, M. Degrauwe, M.V. Paemel, H. Oguey, A voltage reduction technique for digital systems, inProceedings of the IEEE International Solid-State Circuits Conference, pp. 238–239, February 1990

Q. Wu, P. Juang, M. Martonosi, D.W. Clark, Voltage and frequency control with adaptive reaction time in multiple-clock domain processors, in Proceedings of the IEEE International Symposium on High Performance Computer Architecture, pp. 178–189, February 2005

C. Isci, A. Buyuktosunoglu, C.-Y. Cher, P. Bose, M. Martonosi, An analysis of efficient multi-core global power management policies: maximizing performance for a given power budget, in Proceedings of the Annual IEEE/ACM International Symposium on Microarchitecture, pp. 347–358, December 2006

M. Ware, K. Rajamani, M. Floyd, B. Brock, J.C. Rubio, F. Rawson, and J.B. Carter, architecting for power management: the IBM POWER7\(^\text{TM}\) approach, in Proceedings of the IEEE International Symposium on High Performance Computer Architecture, pp. 1–11, January 2010

J. Friedrich et al., The Power8\(^\text{ TM }\) processor: designed for big data, analytics, and cloud environments, in Proceedings of the IEEE International IC Design & Technology Conference, pp. 1–4, May 2014

M. Alioto, L. Giancane, G. Scotti, A. Trifiletti, Leakage power analysis attacks: a novel class of attacks to nanometer cryptographic circuits. IEEE Trans. Circuits Syst. I Regul. Pap. 57(2), 355–367 (2010)

F. Waldron, J. Slowey, A. Alderman, B. Narveson, and S.C. O’Mathuna, Technology roadmapping for power supply in package (PSiP) and power supply on chip (PwrSoC), in Proceedings of the IEEE International Applied Power Electronics Conference and Exposition, pp. 525–532, February 2010

H.-P. Le, S.R. Sanders, E. Alon, Design techniques for fully integrated switched-capacitor DC-DC converters. IEEE J. Solid-State Circuits 46(9), 2120–2131 (2011)

Y. Ramadass, A. Fayed, A. Chandrakasan, A fully-integrated switched-capacitor step-down DC-DC converter with digital capacitance modulation in 45 nm CMOS. IEEE J. Solid-State Circuits 45(12), 2557–2565 (2010)

M. Bathily, B. Allard, F. Hasbani, A 200-MHz integrated buck converter with resonant gate drivers for an RF power amplifier. IEEE Trans. Pow. Electron. 27(2), 610–613 (2012)

Y. Ahn, H. Nam, J. Roh, A 50-MHz fully integrated low-swing buck converter using packaging inductors. IEEE Trans. Pow. Electron. 27(10), 4347–4356 (2012)

Y.-H. Lee, S.-C. Huang, S.-W. Wang, W.-C. Wu, P.-C. Huang, H.-H. Ho, Y.-T. Lai, K.-H. Chen, Power-tracking embedded buckboost converter with fast dynamic voltage scaling for the SoC system. IEEE Trans. Pow. Electron. 27(3), 1271–1282 (2012)

H. Jia, J. Lu, X. Wang, K. Padmanabhan, Z.J. Shen, Integration of a monolithic buck converter power IC and bondwire inductors with ferrite epoxy glob cores. IEEE Trans. Pow. Electron. 26(6), 1627–1630 (2011)

W. Yan, W. Li, R. Liu, A noise-shaped buck DCDC converter with improved light-load efficiency and fast transient response. IEEE Trans. Pow. Electron. 26(12), 3908–3924 (2011)

L. Wang, Y. Pei, X. Yang, Y. Qin, Z. Wang, Improving Light and intermediate load efficiencies of buck converters with planar nonlinear inductors and variable on time control. IEEE Trans. Pow. Electron. 27(1), 342–353 (2012)

H. Nam, Y. Ahn, J. Roh, 5-V buck converter using 3.3-V standard CMOS process with adaptive power transistor driver increasing efficiency and maximum load capacity. IEEE Trans. Pow. Electron. 27(1), 463–471 (2012)

M. Wens, M.S.J. Steyaert, A fully integrated CMOS 800-mW fourphase semiconstant ON/OFF-Time step-down converter. IEEE Trans. Pow. Electron. 26(2), 326–333 (2011)

J. Guo, K.N. Leung, A 6-\(\rm {\mu }\)W chip-area-efficient output-capacitorless LDO in 90-nm CMOS technology. IEEE J. Solid-State Circuits 45(9), 1896–1905 (2010)

P. Hazucha et al., Area-efficient linear regulator with ultra-fast load regulation. IEEE J. Solid-State Circuits 40(4), 933–940 (2005)

T.Y. Man, K.N. Leung, C.Y. Leung, P.K.T. Mok, M. Chan, Development of single-transistor-control LDO based on flipped voltage follower for SoC. IEEE Trans. Circuits Syst. I Regul. Pap. 55(5), 1392–1401 (2008)

M. Al-Shyoukh, H. Lee, R. Perez, A Transient-enhanced low-quiescent current low-dropout regulator with buffer impedance attenuation. IEEE J. Solid-State Circuits 42(8), 1732–1742 (2007)

V. Kursun, S.G. Narendra, V.K. De, E.G. Friedman, Analysis of buck converters for on-chip integration with a dual supply voltage microprocessor. IEEE Trans. Very Large Scale Integr. (VLSI) Circuits 11(3), 514–522 (2003)

I. Vaisband, E.G. Friedman, Heterogeneous methodology for energy efficient distribution of on-chip power supplies. IEEE Trans. Pow. Electron. 28(9), 4267–4280 (2013)

D.E. Lackey, P.S. Zuchowski, T.R. Bednar, D.W. Stout, S.W. Gould, J.M. Cohn, Managing power and performance for system-on-chip designs using voltage islands, in Proceedings of the IEEE/ACM International Conference on Computer-Aided Design, pp. 195–202, November 2002

P. Magarshack, P.G. Paulin, System-on-chip beyond the nanometer Wall, in Proceedings of the IEEE/ACM Design Automation Conference, pp. 419–424, June 2003

P. Kocher, J. Jaffe, B. Jun, Differential Power Analysis, in Proceedings of the International Conference on Advances in Cryptology, pp. 388–397, August 1999

L. Lin, W. Burleson, Leakage-based differential power analysis (LDPA) on sub-90 nm CMOS cryptosystems, in Proceedings of the IEEE International Symposium on Circuits and Systems, pp. 252–255, May 2008

T. Martin, M. Hsiao, D.S. Ha, J. Krishnaswami, Denial-of-service attacks on battery-powered mobile computers, in Proceedings of the IEEE Annual Conference on Pervasive Computing and Communications, pp. 309–318, March 2004

H. Vahedi, R. Muresan, S. Gregori, On-chip current flattening circuit with dynamic voltage scaling, in Proceedings of the IEEE International Symposium on Circuits and Systems, pp. 4277–4280, May 2006

K. Tiri, I. Verbauwhede, A digital design flow for secure integrated circuits. IEEE Trans. Comput. Aided Design Integr. Circuits Syst. 25(7), 1197–1208 (2006)

R.A. Rutenbar, G.G.E. Gielen, J. Roychowdhury, Hierarchical modeling, optimization, and synthesis for system-level analog and RF designs. Proc. IEEE 95(3), 640–669 (2007)

M. Popovich, M. Sotman, A. Kolodny, E.G. Friedman, Effective radii of on-chip decoupling capacitors. IEEE Trans. Very Large Scale Integr. (VLSI) Circuits, 16(7), 894–907 (2008)

S.R. Nassif, Power grid analysis benchmarks, in Proceedings of the IEEE/ACM Asia and South Pacific Design Automation Conference, pp. 376–381, January 2008

I. Vaisband, E.G. Friedman, Power network on-chip for scalable power delivery, United States Patent (pending)

I. Vaisband, E.G. Friedman, Power network on-chip for scalable power delivery, in Proceedings of the Workshop on System Level Interconnect Prediction, pp. 1–5, June 2014

I. Vaisband, E.G. Friedman, Dynamic power management with power network-on-chip, in Proceeding of the IEEE International Conference on New Circuits and Systems, pp. 225–228, June 2014

J.H. Mulligan Jr., The effect of pole and zero locations on the transient response of linear dynamic systems. Proc. Inst. Radio Eng. 37(5), 516–529 (1949)

A. Riccobono, E. Santi, A novel passivity-based stability criterion (PBSC) for switching converter DC distribution systems, in Proceedings of the IEEE International Applied Power Electronics Conference and Exposition, pp. 2560–2567, February 2012

D.A. Johns, K. Martin, Analog Integrated Circuit Design (Wiley, 1997)

J.E. Colgate, The control of dynamically interacting systems, in Ph.D. Thesis, Massachusetts Institute of Technology, August 1988

J.L. Wyatt, L.O. Chua Jr., J. Goknar, I. Gannett, D. Green, Energy concepts in the state-space theory of nonlinear n-ports: part i-passivity. IEEE Trans. Circuits Syst. 28(1), 48–61 (1981)

O. Brune, Synthesis of a finite two-terminal network whose driving-point impedance is a prescribed function of frequency, in Ph.D. Thesis, Massachusetts Institute of Technology, August 1931

V. Kursun, E.G. Friedman, Multi-Voltage CMOS Circuit Design (Wiley, 2006)

O.A. Uzun, S. Kose, Converter-gating: a power efficient and secure on-chip power delivery system. IEEE J. Emerg. Sel. Top. Circuits Syst. 4(2), 169–179 (2014)

S. Kose, E.G. Friedman, Efficient algorithms for fast IR drop analysis exploiting locality. Integr. VLSI J. 45(2), 149–161 (2012)

N. Viswanathan et al., The ISPD-2011 routability-driven placement contest and benchmark suite, in Proceedings of the ACM International Symposium on Physical Design, pp. 141–146, March 2011

S. Kose, E.G. Friedman, Fast algorithms for IR voltage drop analysis exploiting locality, in Proceedings of the IEEE/ACM Design Automation Conference, pp. 996–1001, June 2011

A. Brooke, D. Kendrick, A. Meeraus, GAMS: A User’s Guide (The Scientific Press, 1992)

G.A. Rincon-Mora, Current efficient, low voltage, low dropout regulators, in Ph.D. Thesis, Georgia Institute of Technology, November 1996

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2017 Springer International Publishing AG

About this chapter

Cite this chapter

Partin-Vaisband, I., Friedman, E.G. (2017). Secure Power Management and Delivery Within Intelligent Power Networks on-Chip. In: Eisenstein, G., Bimberg, D. (eds) Green Photonics and Electronics. NanoScience and Technology. Springer, Cham. https://doi.org/10.1007/978-3-319-67002-7_7

Download citation

DOI: https://doi.org/10.1007/978-3-319-67002-7_7

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-319-67001-0

Online ISBN: 978-3-319-67002-7

eBook Packages: Chemistry and Materials ScienceChemistry and Material Science (R0)