Abstract

In this paper, a low-noise amplifier (LNA) having ultra-low voltage is presented, intended for active antenna SATCOM applications. The amplifier is composed of three common-source stages with inductive source degeneration and is realized in a 0.1 \(\upmu \)m GaAs process provided by United Monolithic Semiconductors (UMS). The proposed LNA can operate at a sub-Volt supply voltage (nominally 0.7 V, but even lower if some performance degradation is accepted). The LNA provides a gain of 26 dB and a noise figure below 1.6 dB across an operative band from 27 to 31 GHz, while consuming only 18.9 mW. The output third-order intercept point is 13.8 dBm at 29 GHz and the saturated output power is 3.8 dBm. The LNA survived repeated input power sweeps up to 5 dBm and a 24 h stress test at \(-7\) dBm without degradation. Chip size is \(2.3 \times 1.4\) mm2.

Supported by the European Space Agency through project “KAA - Ka-band LNA with reduced DC power consumption” (ESA ITT AO 10705).

Access provided by Autonomous University of Puebla. Download conference paper PDF

Similar content being viewed by others

Keywords

1 Introduction

Ka-band active antennas play a crucial role in satellite communication systems, providing both high-capacity data links and the possibility of multiple-beam cover-age. Due to the use of hundreds of modules, low-noise amplifiers with very low power consumption are critical for increasing energy efficiency. However, it is highly challenging to achieve satisfactory performance from Ka-band LNAs (basically, low noise figure, high gain, high linearity) at operating points featured by very low drain voltage. Many studies on GaAs LNAs with noise figures (NF) ranging from 1.5 to 2 dB in K/Ku and near-by bands have been published in the literature [1, 7, 8, 11, 14]. In this paper, an ultra-low power LNA is presented, designed, and fabricated in United Monolithic Semiconductor’s 0.1 \(\upmu \)m GaAs pHEMT process (commercial name: PH10-10). Although optimized for gain and noise figure, the LNA also exhibits interesting performance as to linearity and survivability. See Table 1 for a framing of this work in the state of the art.

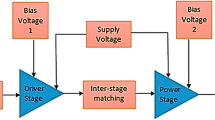

2 Design

The adopted 0.1 \(\upmu \)m GaAs pHEMT process is featured by a typical cutoff frequency (\(f_T\)) of 130 GHz and has an optimal transistor drain-source voltage (\(V_{DS}\)) of 2.5 V. Thus, the Foundry’s PDK model is not guaranteed at sub-Volt VDS. As a consequence, a multi-bias small-signal and noise transistor model was extracted in house for \(V_{DS}\) in the neighborhood of 0.7 V. The model is comprised of a small-signal equivalent circuit [3, 5] equipped with equivalent noise temperatures [12].

The designed LNA consists of three \(4 \times 30\) \(\upmu \)m active stages. The gate bias is almost zero (\(V_{GS} = -0.02\) V), corresponding to a drain current density of 75 mA/mm (9 mA per stage) at the nominal supply of \(V_{DS} = 0.7\) V. All stages are in common-source configuration, with appropriately selected, stage-dependent inductive degenerations, as explained next.

In particular, the first two stages are conceived as a simultaneously conjugate-matched pair which minimizes the noise measure [6] and therefore, virtually, also the noise figure. This is achieved in practice by following the procedure outlined in [2] and reprised in [9, 14]. The third stage is basically a simultaneously conjugate-matched one, so that he overall chain is also simultaneously conjugate-matched and low-noise [4]. Of course, the baseline design with ideal elements underwent appropriate tuning and optimization through the subsequent design steps, i.e., when introducing real elements and EM simulations.

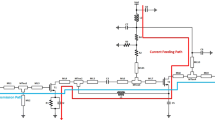

For reasons of compatibility with other cells in the reticule, the fabricated LNA occupies an area of \(2.3 \times 1.4\) mm2, but the actual length is 0.2 mm shorter. The fabricated LNA is shown in Fig. 1.

3 Characterization

After fabrication, the MMIC LNA has been extensively characterized on wafer with respect to small-signal, noise figure, power curves, intermodulation, and survivability.

Figure 2 presents the simulated and measured matching under nominal operating conditions, whereas the gain and noise figure are shown in Fig. 3. The LNA achieves a 26-dB small-signal flat gain across the whole band-width (27–31 GHz). The measured noise figure, is 1.5 dB in average across the operating bandwidth, with a lowest value of 1.4 dB at 30 GHz and a maximum of 1.6 dB at 27 GHz.

Notice that the small-signal campaign both on the LNA and on a large set of test structures has been vital in order to carry out a thorough reverse engineering of the design. In particular, two main conclusions were drawn from this activity:

-

The EM-simulated S-parameters of the passive structures were found to suffer from nonnegligible phase discrepancies from measurements when applying transmission line offsets, even if these were duly removed through calibrated ports with shifted reference planes. This issue, however, basically disappears when using calibrated ports with zero-length shifts.

-

The S-parameters of the degenerated active devices resulted much more sensitive than expected on the parameters of the degenerations themselves. Also, some differences were observed between the devices from the samples used for modeling and those in the LNA’s foundry run, especially in terms of gain. In this case, comparisons were made both on non-degenerated and degenerated transistors.

By updating the EM simulations and device models accordingly, the agreement between simulations and measurements is very satisfactory, as can be seen from Fig. 2 and Fig. 3-left.

Third-order measurements were also taken, with a tone spacing of 100 MHz. The measured frequency components versus input power are shown in Fig. 4-left for both lower and upper sides and at three nominal frequencies (lower, center and upper frequency). For better clarity, the intercept points versus nominal frequency are then shown in Fig. 4-right for the lower and upper sides separately. The measured output intercept points are quite flat versus frequency and average at \(OTOI = 13.8\) dBm at center frequency.

Finally, gain compression and stress tests were carried out with a similar test bench, namely, after removing one of the two tones and amplifying the remaining one up to a maximum nominal level, due to hardware limitations, of \(-5\) dBm. The measured output power at 1-dB gain compression point is approximately \(-2 \pm 0.5\) dBm over frequency, associated with a flat gain: see Fig. 5.

Another important aspect of LNA’s for SATCOM applications is their survivability to possible nearby interferers. When this aspect is specifically addressed, the go-to solution is the use of off-chip or (if available) on-chip limiters [15], which, however, entail a significant increase in noise figure; alternatively, GaN technology can be adopted in place of GaAs since it is inherently more robust and allows specific protection techniques [13, 16], although at the cost of higher noise figure and/or power consumption [10, 16]. Notice that the proposed design is GaAs-based and devoid of any protection mechanism in addition to the LNA.

To assess survivability, two different test conditions were devised, namely a short-term stress and a long-term stress. The former consisted in applying an input power sweep from −35 dBm to −5 dBm with 1 dB step, each level being maintained for 5 s. Notice that the final level corresponds to 16 dB gain compression for this MMIC. Also, the sweep was applied three times, obtaining a good retracing of the same curve.

The long-term stress consisted in applying an input power fixed at \(-7\) dBm for 24 h, while monitoring the output power and the total gate and drain currents. Figure 6-left reports the sequence of a short-term stress test, the long-term stress test and an additional short-term stress test performed to double check that the LNA’s behavior did not show degradations. In addition, Fig. 6-right shows the monitored values of \(I_G\) and \(I_D\) during the long-term stress. The former falls below the quantization error of the ammeter while the latter remains constant throughout the whole test.

4 Conclusion

An ultra-low voltage (0.7 V) MMIC LNA targeting active antenna SATCOM applications was presented in this contribution, designed and realized in a European, commercial 0.1 \(\upmu \)m GaAs process provided by UMS. Although the amplifier is composed of three active stages, it occupies less than \(2.3 \times 1.4\) mm2 and achieves remarkable performance in an operative band from 27 to 31 GHz while consuming as low as 18.9 mW.

Measured gain is 26 dB and a noise figure below 1.6 dB. The output third-order intercept point is around 14 dBm and the saturated output power is about 4 dBm. The LNA survived repeated input power sweeps up to 5 dBm and a 24 h stress test at \(-7\) dBm without degradation.

References

Chen, Y.M., Wang, Y., Chiong, C.C., Wang, H.: A 21.5-50 GHz low noise amplifier in 0.15-\(\upmu \)m GaAs pHEMT process for radio astronomical receiver system. In: 2021 IEEE Asia-Pacific Microwave Conference (APMC), pp. 7–9. IEEE (2021). https://doi.org/10.1109/APMC52720.2021.9661949

Colangeli, S., Ciccognani, W., Salvucci, A., Limiti, E.: Deterministic design of simultaneously matched, two-stage low-noise amplifiers. In: Asia-Pacific Microwave Conference Proceedings, APMC (2017). https://doi.org/10.1109/APMC.2017.8251506

Colangeli, S., et al.: Nondestructive, self-contained extraction method of parasitic resistances in HEMT devices. IEEE Trans. Microw. Theory Tech. 68(7), 2571–2578 (2020). https://doi.org/10.1109/TMTT.2020.2988665

Colangeli, S., Longhi, P.E., Ciccognani, W., Limiti, E.: On the optimum noise-gain locus of two-ports. IEEE Trans. Microw. Theory Tech. 67(6), 2284–2290 (2019). https://doi.org/10.1109/TMTT.2019.2910066

Dambrine, G., Cappy, A., Heliodore, F., Playez, E.: A new method for determining the FET small-signal equivalent circuit. IEEE Trans. Microw. Theory Tech. 36(7), 1151–1159 (1988). https://doi.org/10.1109/22.3650

Haus, H.A., Adler, R.: Circuit Theory Linear Noisy Networks, 2nd edn. Technology Press Research Monographs, Technology Press of Massachusetts Institute of Technology (1959)

Huang, L., Li, Z., Wang, Z., Zhou, P., Chen, J.: A 23–43 GHz LNA with 2.3-dB NF in 0.1 \(\upmu \)m GaAs pHEMT process. In: 2022 IEEE MTT-S International Wireless Symposium (IWS), pp. 1–3 (2022). https://doi.org/10.1109/IWS55252.2022.9978042, https://ieeexplore.ieee.org/document/9978042/

Lee, L.Y., Wang, Y., Wang, H.: A 25–31 GHz LNA in GaAs 0.15-\(\upmu \)m pHEMT. In: 2021 IEEE International Symposium on Radio-Frequency Integration Technology (RFIT), pp. 1–3. IEEE (2021). https://doi.org/10.1109/RFIT52905.2021.9565292

Longhi, P.E., Pace, L., Colangeli, S., Ciccognani, W., Limiti, E.: Novel design charts for optimum source degeneration tradeoff in conjugately matched multistage low-noise amplifiers. IEEE Trans. Microw. Theory Tech. 69(5), 2531–2540 (2021). https://doi.org/10.1109/TMTT.2021.3068285

Pace, L., et al.: DC power-optimized Ka-band GaN-on-Si low-noise amplifier with 1.5 dB noise figure. IEEE Microw. Wirel. Compon. Lett. 32(6), 555–558 (2022). https://doi.org/10.1109/LMWC.2021.3139769

Padmaja, T., N’Gongo, R.S., Ratna, P., Vasu, P., Babu, J.S., Kirty, V.: A 18–40 GHz monolithic GaAs pHEMT low noise amplifier. In: 2008 International Conference on Recent Advances in Microwave Theory and Applications, pp. 309–311. IEEE (2008). https://doi.org/10.1109/AMTA.2008.4763047

Pospieszalski, M.W.: Modeling of noise parameters of MESFETs and MODFETs and their frequency and temperature dependence. IEEE Trans. Microw. Theory Tech. 37(9), 1340–1350 (1989). https://doi.org/10.1109/22.32217

Rudolph, M., et al.: Analysis of the survivability of GAN low-noise amplifiers. IEEE Trans. Microw. Theory Tech. 55(1), 37–43 (2007). https://doi.org/10.1109/TMTT.2006.886907

Salvucci, A., Longhi, P., Colangeli, S., Ciccognani, W., Serino, A., Limiti, E.: A straightforward design technique for narrowband multi-stage low-noise amplifiers with I/O conjugate match. Int. J. RF Microw. Comput. Aided Eng. 29 (2019). https://doi.org/10.1002/mmce.21833

Yang, L., Yang, L.A., Rong, T., Li, Y., Jin, Z., Hao, Y.: Codesign of \({K}\) a-band integrated GAAS pin diodes limiter and low noise amplifier. IEEE Access 7, 88275–88281 (2019). https://doi.org/10.1109/ACCESS.2019.2923210

Zhang, S., et al.: Robust GAN-based LNAS with active epitaxial current limiters. IEEE Microw. Wirel. Compon. Lett. 31(12), 1287–1290 (2021). https://doi.org/10.1109/LMWC.2021.3106916

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2024 The Author(s), under exclusive license to Springer Nature Switzerland AG

About this paper

Cite this paper

Sharma, S., Colangeli, S., Longhi, P., Ciccognani, W., Serino, A., Limiti, E. (2024). A Ka-Band Ultra-Low Power GaAs MMIC LNA. In: Ciofi, C., Limiti, E. (eds) Proceedings of SIE 2023. SIE 2023. Lecture Notes in Electrical Engineering, vol 1113. Springer, Cham. https://doi.org/10.1007/978-3-031-48711-8_14

Download citation

DOI: https://doi.org/10.1007/978-3-031-48711-8_14

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-031-48710-1

Online ISBN: 978-3-031-48711-8

eBook Packages: EngineeringEngineering (R0)