Abstract

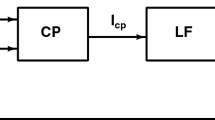

A self-balanced charge pump (CP) with fast lock circuit to achieve nearly zero phase error is proposed and analyzed. The proposed CP is designed based on the SMIC 0.25 μm 1P5M complementary metal-oxide semiconductor (CMOS) process with a 2.5 V supply voltage. HSPICE simulation shows that even if the mismatch of phase/frequency detector (PFD) was beyond 10%, the charge pump could still keep nearly zero phase error. Incorporated fast lock circuit can shorten start-up time to below 300 ns.

Article PDF

Similar content being viewed by others

Avoid common mistakes on your manuscript.

References

Parker J F, Ray D. A 1.6-GHz CMOS PLL with on-Chip Loop Filter [J].IEEE Journal of Solid-State Circuits, 1998,33:337–343.

Sheen R, Chen O. A 1.3V 1.04GHz-1.3GHz CMOS Phase-Locked Loop[J].IEEE Midwest Symp on Circuits and Systems, 1997,1:569–572.

Wu Lin, William C B. A Low Jitter 1.25GHz CMOS Analog PLL for Clock Recovert [J].IEEE Int Symp on Circuits and Systems, 1998,1:1167–1170.

Lee J S. Charge Pump with Perfect Current Matching Characteristics in Phase-Lock Loops [J].IEEE Electronics Letters, 2000,36(23):1907–1908.

Razavil B.Design of Analog CMOS Integrated Circuits [M]. Singapore: McGraw-Hill, 2001.

Gardner F M. Charge-Pump Phase-Lock Loops [J].IEEE Trans Commun, 1980,28(11):1849.

Rhee W. Design of High Performance CMOS Charge Pumps in Phase Locked Loop [J].Proc IEEE Inc Symp Circuit and Systems, 1999,1:545–548.

Howard P A, Jones A E. Improved Charge Pump Phase Detector for Digital Phase Locked Loop [J].IEEE Colloquium Analogus Signal Processing, 1994,1:1–8.

Chang R C, Kuo L C. A New Low-Voltage Charge Pump Circuit for PLL [C]//IEEE International Symposium of Circuits and Systems ISCAS, Geneva, Switzerland: EPFL, 2000: 701–703.

Waizman A. A Delay Line Loop for Frequency Synthesis of Deskewed Clock [J].ISSCC Digest of Technical Papers, 1994,37:119–121.

Johnson M, Hudson E. A Variable Delay Line PLL for CPU Coprocessor Synchronization [J].IEEE Journal of Soli-State Circuits, 1988,23:1218–1223.

Young I A, Greason J K, Wong K L. A PLL Clock Generator with 5 to 110 MHz of Lock Range for Microprocessors [J].IEEE Journal of Solid-State Circuits, 1992,27:1599–1607.

Author information

Authors and Affiliations

Corresponding author

Additional information

Foundation item: Supported by the National High Technology Research and Development Program of China (2004AA122310)

Biography: JIANG Xiang (1972-), male, Ph. D. candidate, research direction: analog and mixed integration circuit.

Rights and permissions

About this article

Cite this article

Xiang, J., Xuecheng, Z., Dingzhong, X. et al. Self-balanced charge pump with fast lock circuit. Wuhan Univ. J. Nat. Sci. 11, 621–624 (2006). https://doi.org/10.1007/BF02836677

Received:

Issue Date:

DOI: https://doi.org/10.1007/BF02836677