Abstract

A study on the bipolar-resistive switching of an Ni/SiN/Si-based resistive random-access memory (RRAM) device shows that the influences of the reset power and the resistance value of the low-resistance state (LRS) on the reset-switching transitions are strong. For a low LRS with a large conducting path, the sharp reset switching, which requires a high reset power (>7 mW), was observed, whereas for a high LRS with small multiple-conducting paths, the step-by-step reset switching with a low reset power (<7 mW) was observed. The attainment of higher nonlinear current-voltage (I-V) characteristics in terms of the step-by-step reset switching is due to the steep current-increased region of the trap-controlled space charge-limited current (SCLC) model. A multilevel cell (MLC) operation, for which the reset stop voltage (V STOP) is used in the DC sweep mode and an incremental amplitude is used in the pulse mode for the step-by-step reset switching, is demonstrated here. The results of the present study suggest that well-controlled conducting paths in a SiN-based RRAM device, which are not too strong and not too weak, offer considerable potential for the realization of low-power and high-density crossbar-array applications.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

Background

Conventional memories such as dynamic random-access memory (DRAM) and NAND flash memory that are based on charge storage have been utilized in many applications until now, and the continually increasing demand for these memories is a response to the era of big data and the Internet of Things (IoT) [1, 2]. In recent years, however, and as expected, a near-future occurrence of the physical limits of these commercial memories has been identified. As an alternative, new approaches such as three-dimensional (3D) structure technology, multilevel cell (MLC) technology, and emerging memory technology have been widely researched [3–5]. Among the emerging memories, the resistive random-access memory (RRAM) has attracted considerable interest due to numerous advantages that include a simple structure, a fast switching speed, a low-voltage operation, an extendibility to the 3D structure, and an MLC operation [6–31]. Although extensive research has been carried out on the oxide-based RRAM that is a strong candidate for nonvolatile memory applications, it is also worth investigating a nitride-based RRAM with a silicon bottom electrode (BE), as it has a complete compatibility with the standard complementary metal-oxide-semiconductor (CMOS) processing [26–31]. So far, however, only a small amount of discussion regarding the resistive-switching characteristics of the nitride-based RRAM has occurred.

In particular, MLC is an important key technology for high-density nonvolatile memories and synaptic devices, as it overcomes the limits of conventional lithography [32]. In the RRAM, the MLC can be easily achieved through a controlling of the stop voltage (V STOP) for reset switching. The main aim of this study is a clarification of the switching parameters to differentiate the three types of reset-switching transition in terms of a fabricated Ni/Si3N4/p +-Si-based RRAM device.

Methods

The sample was prepared as follows: After the standard cleaning processes, a p + Si BE was highly doped using a BF2 + ion implanting with a dose of 5 × 1015 cm−2 (converted to a peak concentration of 1020 cm−3). A SiN of 4.1 nm thickness was then deposited on the implanted silicon wafer using low-pressure chemical vapor deposition (LPCVD) at 785 °C after an annealing process was performed at 1050 °C for 10 min; subsequently, the Ni top electrode (TE) was deposited and patterned through a shadow mask that contains circular patterns with a 100-μm radii. All of the electrical properties were characterized at room temperature according to the DC voltage sweep mode and the pulse mode using the Keithley 4200-SCS semiconductor parameter analyzer (SPA) and the 4225-PMU ultra-fast I-V module, respectively. Also, the p +-Si BE was grounded and control biases were applied to the Ni TE over the measurements.

Results and Discussion

The thickness of SiN x layer was confirmed using cross-sectional transmission electron microscopy (TEM) image of Ni/SiN x /Si structure as shown in Fig. 1a. Scanning TEM (STEM) image and energy-dispersive X-ray spectroscopy (EDS) maps of distribution Ni, Si, and N is shown in Fig. 1b. Atomic percentage of each layer was confirmed by EDS line profile and spectrum of Ni/SiN x /Si structure as shown in Fig. 1c, d, respectively.

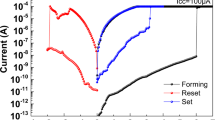

Figure 2a shows the bipolar current-voltage (I-V) characteristics of the Ni/Si3N4/p +-Si RRAM device under the DC voltage sweep mode. After the positive electroforming process (a thick black line), a current compliance (CC) of 5 mA was used to activate a pristine cell with a high initial resistance; here, the CC is used to protect the device from a permanent dielectric breakdown. A negative voltage sweep was conducted without the CC for the reset process that performs a switch from the low-resistance state (LRS) to the high-resistance state (HRS). A positive sweep switches the device back to the LRS for the reset switching. The Ni/Si3N4/p +-Si RRAM device then showed a forming-less process, indicating that the forming voltage is within the distribution range of the set voltage; notably, with the 5-mA CC, sharp current drops were observed for all of the reset switching during 100 consecutive DC voltage sweeps. Alternatively, the set switching, whereby the current is increased sharply or gradually, is more complicated; also, for some of the switching, the set process was completed after a gradual current drop due to an incomplete reset switching, suggesting that the set and the reset switching are strongly affected by the previous switching events.

Next, the reset-switching behaviors under a 100-μA CC were investigated. According to the I-V characteristics that are shown in Fig. 2b–d, reset switching can be classified into three types. Figure 2b shows a sharp reset switching that occurs even though a low CC of 100 μA was set for the device. The low LRS resistance and high reset current (I RESET) are caused by a current overshoot that is for the set process. The main reason for the occurrence of the current overshoot is an instrument-response time that is slower than the switching time of the device. Figure 2c exhibits a step-by-step reset transition that starts with a relatively high LRS resistance; here, the comparability of the I RESET to the CC of 100 μA is probably due to a reduced overshoot effect that occurs during the set process. Figure 2d shows a weak reset switching, where the current drop is within only a few microamperes and the LRS resistance is very slightly changed; here, it is likely that the weakness is due to an incomplete formation of the conducting path in terms of the set process. The current overshoot effect in the proposed fabricated device occurs randomly, and this causes a large variation of the LRS [33, 34]. If appropriate actions such as a series resistance and a transistor were prepared for the device to reduce the current overshoot, the CC could control the LRS resistance and the reset current more efficiently [35, 36]; however, the provision of a clue to gain an understanding of the reset-transition behaviors in the LRS itself is worthwhile. Figure 3 shows the cumulative frequency of the LRS and HRS resistances for the three types of reset switching. The distribution of the sharp reset switching is less dispersive compared with the distribution of the step-by-step reset switching. For the weak reset switching, only a slight difference is evident between the LRS and the HRS. According to the findings of this paper, a proper set overshoot is needed to obtain an effective resistive-switching behavior.

Through the double logarithmic plots of the I-V curve in the LRS, a preliminary estimation of the conducting mechanism of the fabricated device was made. The current transport is governed by a power law (i.e., I~V m), but with different slopes, as shown in Fig. 4. The ohmic behavior (I~V) was changed to Child’s square law (I~V 2) for the three types of switching, and a higher slope region (I~V m, m > 2) was observed for the switchings with the step-by-step and the weak reset transitions. This conduction can be explained by the trap-controlled space charge limited current (SCLC) theory [37–41]. The trap sites that are composed of the dangling bonds in the trivalent Si atoms can be used as a medium through the trapping and de-trapping of the carriers. The ohmic conduction in a low-voltage region is dominated by free electrons that are thermally dominated when they are compared to the injected electrons. The injected electrons from the electrode become especially predominant with the increasing of the voltage at the V ON that can be expressed as follows:

where θ is the free carrier density, θ t is the concentration of the traps, q is the electron charge, n 0 is the thermally produced free-electron density, L is the nitride thickness, ε r is the static-dielectric constant, and ε 0 is the permittivity of the free space. The trap-unfilled SCLC is changed to a trap-filled SCLC at the trap-filled limited voltage (V TFL), thereby resulting in a further slope increase. The sharp reset switching was finished before the V TFL was reached, while the switchings with the step-by-step reset and the weak reset were completed after the V TFL was reached.

Unlike the conventional metal-oxide-based RRAM devices such as NiO, TiO2, and CuO2, for which a metallic ohmic conduction with a slope of 1 in the log-log scale is shown, SiN x -based RRAM devices exhibited nonlinear I-V curves in the LRS. The nonlinear resistive switching in the LRS is one of the major strong points in the two-terminal-based crosspoint array application. The earlier report for which the Ni/SiN/TiN RRAM stack is used confirmed this intrinsic nonlinear characteristic, which is attributed to the different trap-assisted tunneling mechanism that applies in this case; here, the nonohmic I-V curves of the Ni/SiN/p +-Si RRAM device can also be explained by the different properties of the conducting path in the LRS. The metallic conducting paths of the metal-oxide-based RRAM that are in the LRS are formed by oxygen vacancies. In this case, the resistance is increased when the temperature is elevated; contrarily, the SiN-based RRAM employs the previously mentioned trap-related conduction mechanism that ensures the production of a nonlinear I-V curve without the use of an extra selection device. Figure 5a–c shows the plot of the ln(I) vs. the 1/T in the low-voltage region (−0.1 to −0.5 V) for the LRS of the three types of reset switching. A negative slope indicates that the underlying conduction mechanism is based on a trap-to-trap hopping that occurs through nitride vacancies, rather than the intervention of the metallic conducting filaments. Figure 6 shows the nonlinearity of the three types of reset switching in the LRS. The selectivity can be defined as the ratio of the current at the read voltage (V READ) to that at half of the V READ (1/2 V READ). The selectivity of the step-by-step reset switching is higher than that of the sharp reset switching by more than the absolute value of 0.4 V, and this is because the steep increased current in the high-voltage region after the V TFL of 0.5 V is reached leads to a higher nonlinearity for the step-by-step reset switching.

As part of the authors’ determination of the reset-transition behaviors, a further investigation of the switching parameters was conducted, whereby the relationship between the resistive-switching parameters was closely examined. Figure 7a shows the I RESET as a function of the LRS resistance in terms of the switchings with the sharp and the step-by-step resets. The sharp-reset-switching relationship between the two parameters is not clear; alternatively, for the switching with the step-by-step reset, the I RESET is decreased with an increasing of the LRS resistance. Notably, the three reset types are determined by the LRS resistance in the inset of Fig. 7a, indicating that, for the step-by-step reset switching, the conducting paths are carefully controlled for the set switching. Figure 7b shows the scatter plot of the I RESET vs. V RESET in terms of the switchings with the sharp and the step-by-step resets. The I RESET is directly proportional to the absolute V RESET value for the sharp and the step-by-step resets; meanwhile, the step-by-step reset shows the opposite trend. The inset of Fig. 7b shows the distribution of the reset power (P RESET) of the switchings with respect to both the sharp and the step-by-step resets. The two reset transitions are clearly distinguished by an I RESET of 7 mA and a P RESET of 1 mW.

To evaluate the MLC capability, the DC characteristics of the Ni/SiN/p +-Si device were investigated through a controlling of the V STOP. Figure 8a shows the multilevel I-V characteristics of the reset process for the step-by-step reset switching. The current levels of the multiple states were gradually decreased by more than three orders of magnitude, while the V STOP was increased from −1.3 to −2.5 V; moreover, the pulse characteristics were checked for the three switching types. Figure 8b shows the resistance value after the different pulse amplitudes from −2 to −5 V were applied to the devices; for the abrupt reset switching, a switching response was not registered until −4.5 V and a sharp current drop was observed at −5 V. For the step-by-step reset switching, an initially higher LRS resistance is required for the employment of the MLC operation; however, a weak resistance change was obtained for the initially very high LRS resistance that is caused by the set switching. It is therefore important to ensure a proper LRS resistance range after the set switching for the MLC operation. Figure 8c, d shows the applied voltage pulse (−3 and −5 V) and the transient current response for the sharp reset switching. A significant current change was not recorded during the peak voltage of −3 V after the occurrence of an external displacement current, which is caused by the capacitive charging effect in the test system that is shown in Fig. 8c; alternatively, a distinctive current drop was observed when the peak voltage of −5 V was applied to the device.

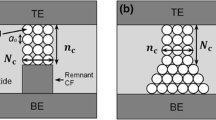

Based on the electrical measurement results, a possible reset-switching model is proposed in this paper for the three types of reset-switching behavior, as shown in Fig. 9a–c. The conducting path may be made up of abundant traps which originate from dangling bonds in the trivalent Si atoms. Here, we explain the switching and conduction mechanism for three reset switching transitions by using conduction path model. Three reset-switching transitions can be explained by the size of conducting paths, which is related to the amount of traps [42]. For the sharp reset switching, however, a singly connected large conducting path could be ruptured; that is, the sharp reset process that is caused by the electrical field with thermal assistance turns to the HRS, as shown in Fig. 9a. For the step-by-step reset switching, the weakest part among the multiple conducting paths would be ruptured first, followed by the additional rupture processes, as shown in Fig. 9b. For a weak reset switching, initially weak conducting paths would be formed, followed by the absence of an effective reset process, as shown in Fig. 9c.

Conclusions

The different bipolar reset transitions in terms of an Ni/SiN/Si RRAM device were investigated in this study depending on the reset power and the resistance value of the LRS, which is determined by the forming and set processes. The sharp reset switching was observed for the high reset power (>7 mW) and the low LRS, whereas the step-by-step reset switching was observed for the low reset power (<7 mW) and the high LRS. Higher nonlinear I-V characteristics and a gradual reset change regarding the step-by-step reset switching would be two of the most virtuous merits of the low-power and high-density crossbar array.

References

Pirovano A, Schuegraf K (2010) Memory grows up. Nature Nanotech 5:177–8

Zhu CX, Xu ZG, Huo ZL, Yang R, Zheng ZW, Cui YX, Liu J, Wang YM, Shi DX, Zhang GY, Li FH, Liu M (2011) Investigation on interface related charge trap and loss characteristics of high-k based trapping structures by electrostatic force microscopy. Appl Phys Lett 99:223504

Jo SH, Kumar T, Narayanan S, Lu WD, Nazarian H (2014) 3D-stackable crossbar resistive memory based on field assisted superlinear threshold (FAST) selector. In: Tech. Dig.-Int. Electron Devices Meet. (IEDM)., p 160

Liu T-Y, Yan TH, Scheuerlein R, Chen Y, Lee JKY, Balakrishnan G et al (2014) A 130.7 mm2 2-layer 32Gb ReRAM memory device in 24 nm technology. IEEE J Solid-State Circuits 49:140–53

Waser R, Dittmann R, Staikov G, Szot K (2009) Redox-based resistive switching memories—nanoionic mechanisms, prospects, and challenges. Adv Mater 21:2632–63

Yang JJ, Strukov DB, Stewart DR (2013) Memristive devices for computing. Nat Nanotechnol 8:13

Fujimoto M, Koyama H, Kobayashi S, Tamai Y, Awaya N, Nishi Y et al (2006) Resistivity and resistive switching properties of Pr0.7Ca0.3MnO3 thin films. Appl Phys Lett 89:243504

Lee MJ, Lee CB, Lee D, Lee SR, Chang M, Hur JH et al (2011) A fast, high endurance and scalable non-volatile memory device made from asymmetric Ta2O5−x/TaO2−x bilayer structures. Nat Mater 10:625–30

Wong HSP, Lee HY, Yu S, Chen YS, Wu Y, Chen PS et al (2012) Metal-oxide RRAM. Proc IEEE 100:1951

Prakash A, Jana D, Maikap S (2013) TaOx-based resistive switching memories: prospective and challenges. Nanoscale Res Lett 8:418

Long S, Perniola L, Cagli C, Buckley J, Lian X, Miranda E, Pan F, Liu M, Suñé J (2013) Voltage and power-controlled regimes in the progressive unipolar RESET transition of HfO2-based RRAM. Sci Rep 3:2929

Wang G, Long S, Yu Z, Zhang M, Ye T, Li Y et al (2010) Improving resistance uniformity and endurance of resistive switching memory by accurately controlling the stress time of pulse program operation. Appl Phys Lett 106(9):092103

Long S, Lian X, Cagli C, Cartoixà X, Rurali R, Miranda E et al (2013) Quantum-size effects in hafnium-oxide resistive switching. Appl Phys Lett 102:183505

Chang K-C, Tsai T-M, Chang T-C, Wu H-H, Chen J-H, Syu Y-E et al (2013) Characteristics and mechanisms of silicon-oxide-based resistance random access memory. IEEE Electron Device Lett 34:399–401

Chu T-J, Chang T-C, Tsai T-M, Wu H-H, Chen J-H, Chang K-C et al (2013) Charge quantity influence on resistance switching characteristic during forming process. IEEE Electron Device Lett 34:502–4

Maikap S, Jana D, Dutta M, Prakash A (2014) Self-compliance RRAM characteristics using a novel W/TaOx/TiN structure. Nanoscale Res Lett 9:292

Wu M-C, Lin Y-W, Jang W-Y, Lin C-H, Tseng T-Y (2011) Low-power and highly reliable multilevel operation in ZrO2 1T1R RRAM. IEEE Electron Device Lett 32:1026–8

Prakash A, Maikap S, Chiu H-C, Tien T-C, Lai C-S (2013) Enhanced resistive switching memory characteristics and mechanism using a Ti nanolayer at the W/TaOx interface. Nanoscale Res Lett 8:288

Peng CN, Wang CW, Chan TC, Chang WY, Wang YC, Tsai HW, Wu WW, Chen LJ, Chueh YL (2012) Resistive switching of Au/ZnO/Au resistive memory: an in situ observation of conductive bridge formation. Nanoscale Res Lett 7:559

Luo WC, Liu JC, Lin YC, Lo CL, Huang JJ, Lin KL, Hou TH (2013) Statistical model and rapid prediction of RRAM SET speed-disturb dilemma. IEEE Trans Electron Devices 60:3760–3766

Liu H, Lv H, Yang B, Xu X, Liu R, Liu Q, Long S, Liu M (2014) Uniformity improvement in 1T1R RRAM with gate voltage ramp programming. IEEE Electron Device Lett 35:1224–1226

Panda D, Dhar A, Ray SK (2012) Non-volatile memristive switching characteristics of TiO2 films embedded with nickel nanocrystals. IEEE Trans Nanotechnol 11:51–55

Ismail et al (2014) Forming-free bipolar resistive switching in nonstoichiometric ceria films. Nanoscale Res Lett 9:45

Kim HD, Yun MJ, Kim KH, Kim S (2016) Oxygen-doped zirconium nitride based transparent resistive random access memory devices fabricated by radio frequency sputtering method. J Alloy Compd 675:183

Kim S, Park BG (2016) Nonlinear and multilevel resistive switching memory in Ni/Si3N4/Al2O3/TiN structures. Appl Phys Lett 108:212103

Jiang X, Ma Z, Xu J, Chen K, Xu L, Li W, Huang X, Feng D (2015) a-SiNx:H-based ultra-low power resistive random access memory with tunable Si dangling bond conduction paths. Sci Rep 5:15762

Jiang X, Ma Z, Yang H, Yu J, Wang W, Zhang W, Li W, Xu J, Xu L, Chen K, Huang X, Feng D (2014) Nanocrystalline Si pathway induced unipolar resistive switching behavior from annealed Si-rich SiNx/SiNy multilayers. J Appl Phys 116:123705

Kim HD, Yun MJ, Kim S (2015) Self-rectifying resistive switching behavior observed in Si3N4-based resistive random access memory devices. J Alloy Compd 651:340

Kim S, Jung S, Kim MH, Cho S, Park BG (2015) Resistive switching characteristics of Si3N4-based resistive-switching random-access memory cell with tunnel barrier for high density integration and low-power applications. Appl Phys Lett 106:212106

Kim S, Cho S, Park BG (2016) Fully Si compatible SiN resistive switching memory with large self-rectification ratio. AIP Adv 6:015021

Kim S, Jung S, Kim MH, Cho S, Park BG (2015) Gradual bipolar resistive switching in Ni/Si3N4/n+-Si resistive-switching memory device for high-density integration and low-power applications. Solid-State Electron 114:94

Seo K, Kim I, Jung S, Jo M, Park S, Park J, Shin J, Biju KP, Kong J, Lee K, Lee B, Hwang H (2011) Analog memory and spike-timing-dependent plasticity characteristics of a nanoscale titanium oxide bilayer resistive switching device. Nanotechnology 22:254023

Wan HJ, Zhou P, Ye L, Lin YY, Tang TA, Wu HM, Chi MH (2010) In situ observation of compliance-current overshoot and its effect on resistive switching. IEEE Electron Device Lett 31:246–248

Chen YS, Lee HY, Chen PS, Liu WH, Wang SM, Gu PY, Hsu YY, Tsai CH, Chen WS, Chen F, Tsai MJ, Lien C (2011) Robust high-resistance state and improved endurance of HfOX resistive memory by suppression of current overshoot. IEEE Electron Device Lett 32:1585–1587

Wu MC, Jang WY, Lin CH, Tseng TY (2012) A study on low-power, nanosecond operation and multilevel bipolar resistance switching in Ti/ZrO2/Pt nonvolatile memory with 1T1R architecture. Semicond Sci Technol 27:065010

Fan YS, Zhang L, Crotti D, Witters T, Jurczak M, Govoreanu B (2015) Direct evidence of the overshoot suppression in Ta2O5-based resistive switching memory with an integrated access resistor. IEEE Electron Device Lett 36:1027–1029

Chen X, Wu G, Bao D (2008) Resistive switching behavior of Pt/Mg0.2Zn0.8O/Pt devices for nonvolatile memory applications. Appl Phys Lett 93:093501

Shin HY, Park JH, Chung HY, Kim KH, Kim HD, Kim TG (2015) Highly uniform resistive switching in SiN nanorod devices fabricated by nanosphere lithography. Appl Phys Express 7:024202

Sun Y, Song L, Hua L, Cai W, Chen W, Zhao X (2015) Crystal micromorphologies and forming voltage effect on resistance switching behaviors in Ti/Pr(Sr0.1Ca0.9)2Mn2O7/Pt devices. J Alloy Compd 646:477–482

Kim S, Jeong HY, Choi SY, Choi YK (2010) Comprehensive modeling of resistive switching in the Al/TiO x /TiO 2 /Al heterostructure based on space-charge-limited conduction. Appl Phys Lett 97:033508

Harada T, Ohkubo I, Tsubouchi K, Kumigashira H, Ohnishi T, Lippmaa M, Matsumoto Y, Koinuma H, Oshima M (2008) Trap-controlled space-charge-limited current mechanism in resistance switching at Al/Pr0.7Ca0.3MnO3Al/Pr0.7Ca0.3MnO3 interface. Appl Phys Lett 92:222113

Gritsenko VA, Nekrashevich SS, Vasilev VV, Shaposhnikov AV (2009) Electronic structure of memory traps in silicon nitride. Microelectron Eng 86:1866–1869

Acknowledgements

This work was supported by a grant from the National Research Foundation of Korea (NRF), funded by the Korea government (MSIP) (2015R1A2A1A01007307).

Authors’ contributions

SK prepared the samples and electrical measurements and wrote the manuscript. BGP provided technical support to the study. Both authors read and approved the final manuscript.

Competing interests

The authors declare that they have no competing interests.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

Open Access This article is distributed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits unrestricted use, distribution, and reproduction in any medium, provided you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made.

About this article

Cite this article

Kim, S., Park, BG. Power- and Low-Resistance-State-Dependent, Bipolar Reset-Switching Transitions in SiN-Based Resistive Random-Access Memory. Nanoscale Res Lett 11, 360 (2016). https://doi.org/10.1186/s11671-016-1572-9

Received:

Accepted:

Published:

DOI: https://doi.org/10.1186/s11671-016-1572-9