Abstract

The conventional topological approach to eliminate the multiple-input DC voltage requirement in multilevel inverter configurations for synthesizing high-output voltage levels is to deploy split capacitor banks at the input terminal. This method stipulates a less expensive, light weight, and reduced size inverter system. However, the excessive demand for several capacitor banks and the complex voltage balancing strategy associated with this conceptual approach poses numerous limitations in their deployment. In view of these drawbacks, this study proposes a self-balanced, single-phase, nine-level switched-capacitor-based inverter topology consisting of a single-input DC voltage, an auxiliary circuit, and an H-bridge circuit unit. A commensurate single carrier-based sinusoidal pulse-width modulation scheme is developed for the proposed power circuit control, enabling the synthesis of a nine-level output voltage waveform whose amplitude is four times the input voltage value. Detailed power circuit operations and switching functions are adequately provided in the proposed topology. A comparison between the proposed inverter and its recent counterparts in terms of component count, cost involvement, and output voltage-boosting ability is duly carried out using Python data visualization. Results reveal that the proposed inverter competes well in these three criteria. For varying R–L load values, the inverter has the capability of high active and reactive power delivery. Its dynamic response for step changes in the modulation index under these power-mode operations is presented in this paper. For high active power-mode operation, efficiencies of 98.27% and 98.92% under light- and heavy-load conditions, respectively, are obtained on a 3-kW-rated inverter prototype.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

In recent times, the use of renewable energy for electric power generation has reduced the dependence on exhaustible fossil fuels and the resultant environmental effects. Popular demand for renewable energy sources, such as wind, fuel cells, biomass, and photovoltaic (PV), is increasing owing to their zero-carbon emission, eco-friendly nature, and sustainable energy supply. Among these energy sources, PV is the most considered due to its affordability and abundant supply of solar energy, [1, 2]. The standard system that converts DC power from the PV source into an AC power is the multilevel inverter (MLI). Fundamentally, MLIs consist of an array of semiconductor power devices and low-input DC voltage source(s) skillfully configured to synthesize high-output AC voltage levels at the load terminals. The primary features of MLIs over two-level inverters are reduced THD, reduced voltage stress, low electromagnetic interference, and improved efficiency. On account of these outstanding features, MLIs have found numerous applications in interfacing renewable energy to the grid, uninterruptible power supplies, electric vehicles, and distributed generation systems, among many other uses, [3, 4].

The traditional topologies of MLIs are diode-clamped, capacitor-clamped, and cascaded H-bridge (CHB) inverters, [5,6,7,8,9,10,11,12]. In both diode- and capacitor-clamped inverters, [11, 12], the use of a single-input DC voltage with split capacitor banks for the synthesis of desired output voltage levels is an advantage. However, the structural issue of voltage imbalance among the split capacitor banks exists. Moreover, a large number of clamping devices (diodes/capacitors) are needed for the corresponding increase in output voltage levels of diode- and capacitor-clamped inverters. In CHB inverters [7,8,9,10], the advantages of modular and scalable structures and simple control algorithms are achieved, because the inverters consist of H-bridge units. Nonetheless, multiple isolated input DC voltages are required. To synthesize high-output voltage levels, the requirement of power switches and the attendant driver circuit appreciably increases. The topologies presented in [9, 10] utilize numerous independent voltage sources and the modifications of H-bridge cells to generate nine output voltage levels in their single-phase systems. However, these inverter topologies lack output voltage-boosting capabilities. They also require numerous passive and active switches and the corresponding driver’s circuits, thereby making the overall circuits bulky and expensive to implement in real time.

Considering these limitations, switched-capacitor-based MLIs (SCB-MLIs) were proposed to ameliorate the drawbacks of MLI topologies [13,14,15,16,17,18]. In particular, switched capacitor banks (SCBs) are employed to boost the output voltage levels. Thus, the multiple isolated DC sources, a large number of power switches, complex voltage balancing circuit/control, and a high number of clamping devices (capacitors/diodes) are alleviated in the variants of MLIs. In SCB-MLI configurations, the series and parallel combinations of switched capacitors are charged and discharged with the input DC voltage through the appropriate control of the power switches.

Several SCB-MLI topologies are well documented in the literature [14, 15]. In the present study, the single-phase configuration is considered because of its compactness with PV systems. Some SCB-MLIs involve the use of an H-bridge circuit for negative polarity generation, component count reduction, and high-output voltage-level synthesis. Basically, auxiliary circuits are added to the H-bridge module to produce output voltages with low harmonic content, reduced stress voltage, and improved efficiency, [10].

In [14], a modification of an H-bridge power circuit was conceived to generate a nine-level output voltage across the R–L load. Therein, an auxiliary circuit is added in the middle of the input DC source and an H-bridge circuit. The auxiliary circuit consists of six power switches and four split capacitor banks whose mid-point is clamped to the output node of an H-bridge unit. Although these capacitor banks are employed to curtail the number of input DC voltage sources, the power circuit components and the failure rate of the inverter system are also increased, because the passive devices can fail anytime.

In [13], an SCB-MLI topology was proposed that employs an independent voltage source, two switched capacitors, and 14 power switches to synthesize nine output voltage levels. This circuit configuration has four times the output voltage-boosting feature of the input voltage value. However, a high number of constituting power switches that increase the cost and reduce the efficiency led to the decline in popularity of the power circuit.

Narayanan et al. [15] conceived a single-input, nine-level SCB-MLI with a common ground-type conceptual topology used for grid-connected PV applications. The structural configuration of the inverter eliminates the leakage current owing to the concept of common grounding. This common grounding is precisely achieved by connecting the negative end of the input DC voltage and the grid neutral point. The circuit topology comprises 11 power switches, three switched capacitors, and two diodes, resulting in a lower switch count compared to the previous topology in [13]. However, the output voltage-boosting feature is lost.

The semiconductor devices in [15] were further reduced, and the output voltage-boosting ability was restored in the power circuit of [16]. Therein, 11 power switches and 2 switched capacitors are used to configure a grid-connected inverter that has an LCL filter. The generated output voltage is twice the input voltage value. However, the use of an LCL filter involves an additional component, which increases the cost of the inverter system.

The work in [17] proposed a circuit configuration that eliminates the use of an LCL filter and maintains twice the output voltage-boosting capability with 10 power switches, three switched capacitors, and three diodes. However, an inductor is utilized to minimize the high inrush current in the power circuit topology, which also involves extra components.

Another single-input, nine-level SCB-MLI was presented in [18] with a lower switch count compared to the topology conceived in [17]. Specifically, nine power switches, four capacitor banks, and three power diodes are utilized to configure the power circuit. However, the high number of capacitor banks and clamping diodes and the zero-voltage-boosting ability limit its areas of application.

In view of all these drawbacks, this paper proposes a single-phase, nine-level, switched-capacitor-based inverter topology. Herein, an auxiliary circuit (cascade charge and discharge) unit is connected between an input DC voltage source and an H-bridge unit. The H-bridge allows the synthesis of the negative voltage level, while the auxiliary circuit boosts the output voltage levels using the capacitor banks [19].

The proposed inverter configuration has the following eminent characteristics:

-

a.

Inherent self-balancing competence of the capacitors, thus simplifying the control algorithm.

-

b.

Output voltage-boosting capability (output voltage is boosted to four times the input value).

-

c.

Low voltage stress across the constituting power switches.

-

d.

Utilizes a single-input voltage, nine power switches, two switched capacitors, and a diode for the synthesis of a nine-level output voltage waveform.

-

e.

Employs an H-bridge circuit for the reduced number of semiconductor devices.

The proposed inverter has the advantages of no output filter requirement, reduced harmonics, and reduced component count compared to other recently proposed and traditional inverters. Thus, cost reduction is achieved.

To adequately moderate the charging and discharging of the switched capacitors and modulate the constituting power switches of the proposed MLI, a single carrier-based sinusoidal pulse-width modulation (SCB-SPWM) scheme is adopted from [20, 21]. This SCB-SPWM scheme involves the comparison of four rectified sinusoidal reference signals at the fundamental frequency and a triangular carrier frequency at high frequency to realize the gating signals. These gating signals are used to control the active switches of the proposed topology. The adopted control scheme utilizes fewer control signals compared to the traditional control schemes (multicarrier SPWM). Therefore, it simplifies the control, reduces the cost involvement, and ensures a reliable operation of the proposed circuit.

The remaining sections of this work are arranged as follows. Section 2 presents the detailed circuit operation and switching function of the proposed inverter. Section 3 provides a comparative analysis between the proposed inverter and other variants of single-phase, nine-level inverters. Section 4 builds and tests the simulation and experimental prototype to validate the performance of the proposed inverter topology.

2 Proposed methodology

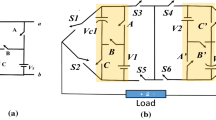

The proposed inverter circuit depicted in Fig. 1 is a single-phase, nine-level switched-capacitor-based inverter. It consists of three units: a single-input DC source, an auxiliary circuit (a cascade charge and discharge circuit), and an H-bridge circuit. The cascade charge and discharge unit comprises two SCBs, one diode, and five active switches, two of which have no antiparallel diodes. This guarantees unidirectional charging of the SCBs. Through the tactical placement of these circuit components, a single-phase switched-capacitor-based inverter topology is configured for the synthesis of nine output voltage levels.

2.1 Power circuit operation

Figure 2 shows the operational principle of the proposed circuit. The basic operation of the circuit follows Kirchhoff’s voltage law. Switches \({S}_{1}{S}_{4}\), \({S}_{3}{S}_{2}\), \({S}_{c1}{S}_{d1}\), and \({S}_{c2}{S}_{d2}\) are complementary pairs. Through the appropriate switching of the semiconductor devices, nine output voltage levels (i.e., \(\pm 0\), \({\pm V}_{{\text{s}}}\), \({\pm 2V}_{{\text{s}}}\), \({\pm 3V}_{{\text{s}}}\), and \({\pm 4 V}_{{\text{s}}}\)) are generated across the R–L load. The solid black lines indicate a current flow and charging/discharging of the SCB(s) in the circuit. The dotted black lines indicate current blockage in the circuit. For the charge/discharge of the switched capacitors, \({C}_{1}\) and \({C}_{2}\), if any of the capacitors is connected in parallel with \({V}_{s}\), the capacitor is charged; while if any of the capacitors is connected in series with \({V}_{{\text{s}}}\), the capacitor is discharged. The SCBs, \({C}_{1}\) and \({C}_{2}\), are charged to their maximum values of \(2{V}_{{\text{s}}} {\text{and}} {V}_{{\text{s}}}\), respectively.

The various output voltage levels, \(+0\), \({+V}_{{\text{s}}}\), \({+2V}_{{\text{s}}}\), \({+3V}_{{\text{s}}}\), and \({+4 V}_{{\text{s}}}\), in the positive half cycle are synthesized across the load output terminal as follows:

-

(a)

\(+OV\): When the switches (\({S}_{1}\), \({S}_{3}\), and \({S}_{c2}\)) are turned on, the positive zero voltage level (\(+OV\)) is synthesized across the R–L load, and the SCB, \({C}_{2}\), is charged to the full input voltage value of \({V}_{{\text{s}}}\). This circuit operation for the \(+OV\) synthesis is depicted in Fig. 2a.

-

(b)

\(+{V}_{{\text{s}}}\): The generation of \(+{V}_{{\text{s}}}\) across the load, as shown in Fig. 2b, requires that switches (\({S}_{1}\), \({S}_{2}\), \({S}_{5}\), and \({S}_{c2}\)) are closed and the diode, \(D\), is forward-biased. The switched capacitor, \({C}_{2}\), is charged to \({V}_{{\text{s}}}\).

-

(c)

\(+{2V}_{{\text{s}}}\): As depicted in Fig. 2c, the synthesis of \(+2{V}_{{\text{s}}}\) across the R–L load is accomplished by turning on the switches (\({S}_{1}\), \({S}_{2}\), \({S}_{d2}\), and \({S}_{5}\)). The SCB, \({C}_{2}\), is discharged to boost the output voltage across the load while \({C}_{1}\) is charged to \(+2{V}_{{\text{s}}}\).

-

(d)

\(+{3V}_{{\text{s}}}\): When the switches (\({S}_{1}\), \({S}_{2}\), \({S}_{d1}\), and \({S}_{c2}\)) are put on and the diode, \(D\), is forward-biased as demonstrated in Fig. 2d, \(+{3V}_{{\text{s}}}\) is generated across the R–L load. Hence, the switched capacitor, \({C}_{1}\), is discharged to boost the output voltage while \({C}_{2}\) is charged to a voltage level of \({V}_{{\text{s}}}\).

-

(e)

\(+4{V}_{{\text{s}}}\): The generation of \(+4{V}_{{\text{s}}}\), as depicted in Fig. 2e, is realized when the switches (\({S}_{1}\),\({S}_{2},\) \({S}_{d1}\), and \({S}_{d2}\)) are closed. The SCBs, \({C}_{1}\) and \({C}_{2}\), are discharged simultaneously to boost the output voltage to the maximum value of \(+4{V}_{{\text{s}}}\) across the load terminal.

In a similar manner, the negative output voltage levels (i.e., \(-0\), \({-V}_{{\text{s}}}\), \({-2V}_{{\text{s}}}\), \({-3V}_{{\text{s}}}\), and \({-4V}_{{\text{s}}}\)) are realized by turning on the complimentary switches of the positive circuit operations in Fig. 2a–e. Table 1 summarizes the switching states of the positive and negative half cycles of the synthesized output voltage levels. The numbers 1 and 0 in the switching table denote the ON and OFF states, respectively, of the switches, while the letters F and R represent the forward and reverse bias, respectively, of the conducting power diode.

2.2 SPWM scheme

The sinusoidal pulse-width modulation (SPWM) scheme employed to generate nine gating signals for the control of the proposed inverter is an SCB-SPWM, similar to that presented in [20, 20]. The concept of the SCB-SPWM scheme in the conceived nine-level circuit is to derive four rectified sinusoidal signals \({(R}_{1}, {R}_{2}, {R}_{3}, {R}_{4})\) at the same fundamental frequency, \({f}_{{\text{m}}}\), and amplitude, \({A}_{{\text{m}}}\), but with different offset values. These rectified signals are then compared with a triangular carrier signal of amplitude, \({A}_{{\text{c}}},\) at high frequency, \({f}_{{\text{c}}}\), to obtain the gating signals. These signals are utilized to control the semiconductor switches of the proposed power circuit.

The amplitude and frequency modulation indices for the proposed power inverter are expressed as follows:

where the parameter \(n\) is the number of output voltage levels generated in one cycle; in this case, \(n= 5\).

Figure 3 illustrates the switching scheme for the control of the proposed inverter. The logic comparator is used to compare the modulating sine wave (R) with a zero value; when R is greater than zero, the switching signal \({S}_{1}\) is synthesized. The rectified signals, \({R}_{1} {\text{to}} {R}_{4}\), are compared with the carrier signal, \(T\), using basic logic gates like AND, OR, and NOT to generate the rest of the signals.

The switching signals used to control the power-switching devices are as follows:

The gating signals \({S}_{4}\), \({S}_{3}\), \({S}_{C1}\), and \({S}_{d2}\) are realized by negating \({S}_{1}\), \({S}_{2}\), \({S}_{d1}\), and \({S}_{C2}\), respectively. \(T\) represents a triangular carrier signal; \({R}_{1}, {R}_{2}, {R}_{3}, \,{\text{and}} \,{R}_{4}\) are the rectified sinusoidal references with the same frequency and amplitude but with different offset values.

3 Comparative analysis between the proposed inverter and similar topologies

The major improvement in recent MLIs lies in the component count reduction in the traditional topologies. These new topologies are tactically configured to synthesize the same or higher output voltage levels, resulting in new MLI topologies. The components that are primarily considered in this reduction process are mainly input DC voltage sources, power switches, and passive devices (capacitors and diodes). While the least number of these components are preferred in MLI topologies, the main focus is on major components such as input voltage sources and power switches, since they are associated with significant cost involvement.

Table 2 presents a detailed comparative analysis of the multiple- and single-input DC voltages of the traditional, recently developed, and proposed single-phase, nine-level variants of MLI topologies, [7,8,9,10,11,12,13,14,15,16,17,18].

Python data visualization in the framework of Jupyter Lab is employed to showcase the superiority of the proposed nine-level SCB inverter over other nine-level variants of MLIs with regard to the component count reduction and capacitor voltage-boosting capability. Figure 4 shows the bar plots of these comparisons in the multiple- and single-input voltage sources using Python data visualization. The bar graph in Fig. 4a clearly shows that the topologies depicted in [7, 8] have the highest cost involvement, since they comprise the highest independent voltage sources. However, the topology in [8] involves a less active switch count compared to that in [7]. In [9, 10], the number of input DC voltage is lowered by half of that presented in [7, 8]. Nonetheless, the number of power switches in [10] is less than that in [9], so it has the least components among their group. Aside from the multiple-input voltage sources in the topologies conceived in [7,8,9,10], which increases the cost involvement and weight of the overall inverter, there is no output voltage-boosting capability in any of the topologies. All these have limited their areas of applications.

Considering the single-input voltage topologies depicted in Fig. 3b, the number of power switches in [18] and the proposed topology have the least value. The proposed configuration has half the number of capacitors and diodes and one-third of the topology presented in [18]. Thus, the proposed configuration has the least cost, size, weight, and improved efficiency compared to all the topologies in [7,8,9,10,11,12,13,14,15,16,17,18]. In addition, the output voltage-boosting factor in the proposed configuration is four times the input voltage value, revealing that the proposed inverter is a great candidate for PV applications compared to all the variants of the nine-level inverters reviewed in this paper.

4 Simulation and experimental results

The simulation and experimental results of the proposed single-phase, nine-level switched-capacitor-based inverter are presented in the following sections.

4.1 Simulation results

PLECS and MATLAB/SIMULINK software were utilized to carry out the simulation of the proposed single-phase, nine-level SCB inverter circuit and corresponding control scheme depicted in Figs. 1 and 3, respectively. The component specifications of the inverter circuit in Fig. 1 are shown in Table 3.

Two loading conditions are typified for the inverter operations to demonstrate its operational capability range for high reactive and active power deliveries. Figure 5 shows the simulated results of the output voltage and current waveforms, (\({v}_{{\text{o}}}\)) and (\({i}_{{\text{O}}}\)), for a modulation index of 0.95 and R–L load values of 10 Ω and 50 mH. It reveals that the power factor is about 0.5371, depicting the high reactive power delivery of the inverter to the load.

Next, the R–L load values are changed to 20 Ω and 5 mH, respectively, and the resulting inverter output waveforms are shown in Fig. 6a. Therein, the voltage and current waveforms showcase the high active power delivery capability of the inverter. The power factor is about 0.9969, indicating that almost only the active power is delivered. For this operational mode, step changes in the modulation index, ma, and the resulting dynamic responses of the inverter system are shown in Fig. 6b. The value of the modulation index changed from 0.9 to 0.45 and back to 0.9 again.

4.2 Experimental results

To validate the simulation results, an experimental prototype of the proposed inverter was set up (see Fig. 7). The prototype specifications of the components are in conformity with those utilized in the simulation, as listed in Table 3. The SCB-SPWM technique illustrated in Sect. 2.2 is carried out in the prototype setup, resulting in nine gating signals that were used to control the power switches. The experimental gating signal waveforms are shown in Fig. 8.

For the ma value of 0.95 and R–L load values of 10 Ω and 50 mH, the experimental output voltage and current waveforms, (\({v}_{{\text{o}}}\)) and (\({i}_{{\text{O}}}\)), are shown in Fig. 9. This conforms with Fig. 5 in terms of the high reactive power delivery of the inverter to the load.

The high active power delivery capability of the inverter was experimentally verified with R–L load values of 20 Ω and 5 mH, respectively. The resulting inverter output waveforms are shown in Fig. 10a. In the figure, the experimental output voltage and current waveforms tally with the simulated counterparts in Fig. 6a. Further to the operational validation in this mode, step changes in the modulation index, ma, and the resulting experimental dynamic responses of the inverter system are shown in Fig. 10b, c, respectively. These are in agreement with the simulated inverter dynamic responses in Fig. 6b.

Experimental inverter output voltage and current waveforms for high active power delivery to the load and inverter dynamic operational waveforms with step changes in the modulation index: a output voltage and current waveforms for ma value of 0.9; b ma is changed from 0.9 to 0.45; c ma is changed from 0.45 to 0.9

At the high active power delivery of this inverter to the load (R–L load values of 20 Ω and 5 mH), its input and output powers were experimentally measured as well. Both powers were simultaneously measured using the power analysis application module MDO3PWR in two MDO3034 oscilloscopes. Figure 11a shows the measured input parameters with one of the MDO3034 oscilloscope, featuring a recording true/active power of 2.318 kW and a reactive power of 448 var. Correspondingly, Fig. 11b shows the output parameters of the measured inverter, wherein the second MDO3034 oscilloscope recorded the inverter’s true/active power of 2.278 kW and a reactive power of 439.7 var. Thus, the measured active output and input powers from the inverter prototype have a ratio of 0.9827.

In addition, the inverter operational performance at partial/light load was experimentally investigated. For this, the aforementioned R–L load values were changed to 40 Ω and 5 mH, respectively. The inverter still delivers high active power but is almost half-loaded. Figure 12a shows the measured input parameters with one of the MDO3034 oscilloscope, which recorded the true/active power of 1, 114 kW, and reactive power of 201 var. Correspondingly, Fig. 11b shows the output parameters of the measured inverter, wherein the second MDO3034 oscilloscope recorded the inverter’s true/active power of 1.102 kW and reactive power of 161 var. Hence, the measured active output and input powers from the prototype at light load have a ratio of 0.9892.

5 Conclusions

A single-phase, nine-level switched capacitor-based inverter topology is presented in this paper. The proposed circuit has the ability to generate a nine-level output voltage waveform with four times the peak-to-peak amplitude of the single-input DC voltage. The switching principle and modulation strategy, as well as switching functions, are properly demonstrated. In addition, a comparative analysis between the proposed power circuit, traditional topologies, and other recently proposed inverters is carried out using Python data visualization. A commensurate single-carrier-based SPWM technique was likewise developed for the proposed inverter power circuit control. To vary the modulation index and output load values, the capability of the proposed inverter to deliver high active and reactive powers is adequately demonstrated. Both simulated and experimental inverter output voltages and currents tally with one another. The input and output active power ratios (efficiencies) of the inverter for high active power operational mode at partial and heavy load are experimentally investigated. At heavy load, the inverter has 98.27% efficiency while the delivering an active power of 2.278 kW. On the other hand, at light load, the inverter has 98.92% efficiency while delivering an active power of 1.102 kW. These experimental investigations are carried out on a 3 kW-rated proposed inverter prototype.

References

Shafiullah, M., Ahmed, S.D., Al-Sulaiman, F.A.: Grid integration challenges and solution strategies for solar PV systems: a review. IEEE Access 10, 52233–52257 (2022)

Owusu, P.A., Sarkodie, S.A.: A review of renewable energy sources, sustainability issues and climate change mitigation. Cogent Eng. 3, 1167990 (2016)

Rodríguez, J., Lai, J.-S., Peng, F.: Multilevel inverters: a survey of topologies, controls, and applications. IEEE Trans. Ind. Electron. 49(4), 724–738 (2002)

Baker, R. H.: High-Voltage Converter Circuit. US Patent 04-203-151 (1980)

Nabae, A., Takahashi, I., Akagi. H.: A new neutral-point clamped PWM inverter. In: Proc. of the Industry Application Society Conference, pp. 761–766 (1980)

Meynard, T. A., Foch, H.: Multi-level conversion: high voltage choppers and voltage-source inverters. In: IEEE Power Electronics Specialists Conf., vol. 1, pp. 397–403 (1992)

Teja, R.R., Sateesh, C., Chowdari, M.A.: Single phase 9 level symmetrical cascaded H-bridge inverter for different PWM techniques. In: International Conference on Electrical Power and Energy Systems (ICEPES), Dec., pp. 14–16 (2016)

Banaei, M.R., Oskuee, M.R.J., Khounjahan, H.: Reconfiguration of semi-cascaded multilevel inverter to improve systems performance parameters. IET Power Electron. 7, 1106–1112 (2014)

Atmanandmaya, N.J.: Single phase symmetrical nine-level cascaded multilevel inverter by single carrier PWM scheme. In: IEEE International Students’ Conference on Electrical, Electronics and Computer Science (2018)

Odeh, C.I., Nnadi, D.B.N.: Single-phase 9-level hybridised cascaded multilevel inverter. IET Power Electron. 6(3), 468–477 (2013)

Narayanan, S., Surendran, S.M., Ismayil, C.: Comparison of seven and nine-level flying capacitor-multilevel inverter using staircase and stepped modulation. In: International Conference on Systems Energy and Environment, July (2019)

Urmila, B.: Multilevel inverters: a comparative study of pulse width modulation techniques. Int. J. Sci. Eng. Res. 1(3), 1–5 (2010)

Wang, Y., Ye, J., Wang, K., Nie, F., Li, G., Liang, J.: A nine-level switched-capacitor step-up inverter with low voltage stress. J. Electr. Eng. Technol. 18, 1147–1159 (2023)

Ali, A.I.M., Mohamed, E.E.M., Sayed, M.A., Saeed, M.S.R.: Novel single-phase nine-level PWM inverter for grid connected solar PV farms. In: International Conference on Innovative Trends in Computer Engineering (ITCE), Aswan University, Egypt (2018)

Jahan, H.K., Abapour, M., Zare, K.: Switched-capacitor based single source cascaded h-bridge multilevel inverter featuring boosting ability. IEEE Trans. Power Electron. 34(2), 1113–1124 (2019)

Gopinath, N.P., Vijayakumar, K.: Common ground nine-level boost inverter for grid-connected PV applications. Front. Res. Energy (2022). https://doi.org/10.3389/fenrg.2022.922786

Aratipamula, B., Bhagwan, K.M.: Single phase nine level switched capacitor-based grid connected inverter with LCL filter. In: 3rd International Conference on Energy, Power and Environment: Towards Clean Energy Technologies, July (2020)

Almakhles, D.J., Sathik, M.J.: Single-phase transformerless nine-level inverter with voltage boosting ability for PV fed AC microgrid applications. Sci. Rep. 12, 13442 (2022). https://doi.org/10.1038/s41598-022-16057-x

Nnadi, D.B.N., Oti, S.E., Odeh, C.I.: Cascaded single phase, PWM multilevel inverter with boosted output voltage. Nigerian J. Technol. 39(2), 589–599 (2020)

Dahidah, M.S.A., Agelidis, V.G.: Single carrier sinusoidal PWM equivalent selective harmonic elimination for a five-level voltage source inverter. Electric Power Syst. Res. 78(1), 1826–1836 (2008)

Chippy, V., Shinosh, M.: A single phase nine level PWM inverter. In: Biennial International Conference on Power and Energy Systems: Towards Sustainable Energy (PESTS E) (2016)

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors have no competing interests to declare that are relevant to the content of this article.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Obe, D.O., Obe, C.T., Ugwuishiwu, C.H. et al. A single-phase, nine-level switched-capacitor-based inverter. J. Power Electron. 24, 699–710 (2024). https://doi.org/10.1007/s43236-023-00758-1

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s43236-023-00758-1