Abstract

The traditional single-stage boost LLC resonant AC/DC converter has been widely studied due to advantages such as few power stages, high power factor, and soft switching. However, it also has several disadvantages, such as a low and narrow input voltage, a DC bus voltage that is much higher than the input voltage, and high stress of the switching devices. Therefore, it is generally used in power grids under 110 V. In order to overcome the above problems, this paper proposed a buck-boost LLC resonant AC/DC converter for both 110 V and 220 V power grids. In addition to its traditional structure, the proposed converter has the advantages of a wide input voltage range and a low bus voltage. The proposed converter adopts the PFM–PWM hybrid control strategy. In this paper, the working principle of the proposed converter is analyzed in detail, the realization of the power factor correction mechanism and the soft switching are described, and the design methods of the key parameters are given. Finally, an experimental prototype with a 110 V-250 V input and a 48 V/100 W output is built. Experimental results verify the correctness of the theoretical analysis of the converter and its applicability to power grids.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

DC converters based on LLC resonance [1,2,3] have been widely used in electric vehicle charging, LED driving, solar photovoltaic panels, household appliances, consumer electronics, etc. [4,5,6,7,8]. Due to advantages such as soft switching, high efficiency, and electromagnetic isolation [9, 10], the LLC resonant circuit has been further studied in single-stage AC/DC converters.

The traditional single-stage boost LLC resonant AC/DC converter was proposed and studied in Refs. [11,12,13]. It eliminates large capacity electrolytic capacitors after the bridge rectifier. In order to realize power correction, an inductor is inserted after the bridge rectifier, and the inductor current works in the discontinuous current mode (DCM). To realize the DCM, the falling slope of the current must be greater than the rising slope. That is, the DC bus voltage is greater than 2 times the input voltage peak value, and the front part of the circuit operates in the boost mode. The disadvantage of this scheme is that the input voltage of the converter is low and narrow, usually only 80–130 V. When applied to a 220 V power grid, the DC bus voltage is close to or more than 900 V. This results in high requirements for the voltage stress of power devices, which is not conducive to device selection and system economic reliability. In Ref. [14], a comprehensive control strategy was improved based on the above topology. When the input voltage is high, the integrated control strategy of pulse frequency modulation (PFM) and asymmetric pulse width modulation (APWM) is adopted to reduce the bus voltage to a certain extent. However, when the input voltage is high, the duty cycle changes too much, the converter does not work under the best conditions, and the efficiency of the converter is reduced.

In summary, a boost topology, as a common power factor correction (PFC) scheme [15, 16], causes the bus voltage to be much higher than the input voltage, which is a disadvantage. In order to overcome this problem, buck-boost structures were proposed for other converter topologies in Refs. [17, 18]. The basic idea is that when charging the bus capacitor, only the inductor charges the capacitor. This is different from the above-mentioned boost mode topology where the input power supply and inductor in series charge the DC bus capacitor. Thus, the bus voltage does not have to be higher than the input voltage. Based on this idea, the front part of the traditional single-stage boost LLC resonant AC/DC converter is improved, and a buck-boost single-stage LLC AC/DC converter suitable for both 110 V and 220 V power grids is proposed. In the following sections, the operating principle and characteristics of the proposed converter are analyzed, and a prototype is built for experimental verification.

2 Topology and operating principle

2.1 Topology

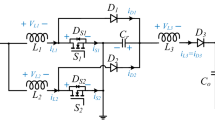

Figure 1 shows the main circuit of the proposed converter, which consists of three parts: an input filter, a buck-boost AC/DC cell and an LLC resonant DC/DC cell.

The front-end input filter is composed of Lf and Cf. Its function is to filter out the high-frequency harmonics of the input current.

The buck-boost AC/DC cell is composed of rectifier diodes (D3, D4, D7 and D8), auxiliary diodes (D1, D2, D5 and D6), a PFC inductor (Lb), a bus capacitor (CB), main switches (S1 and S2) and auxiliary switches (Q1 and Q2). The auxiliary switches are used to allow the inductor current to work in the DCM. In this way, the inductor current has a high sinusoidal degree and is synchronous with the input voltage, which can realize the PFC function and solve the problem where the DC bus voltage of the traditional boost single-stage AC/DC converter is too high. The number of components in this cell is more than that of traditional ones. However, the voltage stress of the semiconductor devices is lower. Thus, the forward voltage drop of the diode is lower, which means that conduction loss of a single diode is lower. Furthermore, the additional auxiliary switches are also soft switched and do not need a large radiator. Thus, there are no significant increases in the volume, weight or conduction losses.

The LLC resonant DC/DC cell consists of main switches, an LLC resonant tank, a high-frequency transformer and output rectifier diodes. The operating frequency of this cell is higher than the resonant frequency of the three elements (composed of a resonant inductance Lr, a resonant capacitor Cr and a magnetizing inductance Lm), and lower than the resonant frequency of the two elements (composed of Lr and Cr). Thus, ZVS or ZCS of the power switches and output rectifier diode can be guaranteed, according to the relationship between the soft switching and the operating frequency of the LLC resonant circuit [11].

When compared with the traditional two-stage PFC–LLC resonant converter, the diode voltage stress of the proposed converter is almost reduced by half. Thus, the diode has a lower forward voltage drop, reduced conduction loss and a shorter reverse recovery time. Moreover, in the case of a wide input range, the duty cycle of the PFC does not change a great deal, which is more conducive to system security.

2.2 Operating principle

The control strategy of the proposed converter is a PFM–PWM hybrid control. A control block diagram and operational waveforms are shown in Fig. 2. In Fig. 2a, vref is the reference voltage, voc is the output feedback voltage, and ve is their error signal. The “PI” block is the proportion–integration module. The “Amplitude Limiting” block is used to limit the upper and lower amplitudes of the “PI” block. The “Sawtooth Wave in PFM” block generates the sawtooth wave vsaw, whose frequency is controlled by ve. The “Frequency Identification” block is used to identify whether the frequency of the sawtooth wave reaches its highest or lowest values. When the frequency is lowest, vf is + 1; when the frequency is highest, it is − 1; and when the frequency is neither highest or lowest, it is 0. In addition, vd is the DC constant, whose value is half the amplitude of vsaw, to control the duty cycle of the driving signal. The “Comparator” block is a comparator to generate pulse signal vg. The frequency of vg is the same as that of vsaw, and its duty cycle D is determined by vc. The “Phase Inverter” block is used to generate an inverse signal, and the “Driving Circuit” block is used to amplify the driving signal. The driving signals of S1 and S2 are complementary pulses.

Figure 2b shows operational waveforms. When the input voltage is moderate, voc is close to vref. As a result, ve is small. The output voltage can track the reference only by changing the frequency of vsaw, while the duty cycle D of vg remains unchanged. The circuit only works in a simple PFM mode. At this time, vf is 0, vd is equal to vc, and the duty cycle D is 0.5, as shown in part (II) of Fig. 2b. When the input voltage is too low, the sawtooth wave reaches its lowest frequency. Then, vf becomes + 1, vc increases, which makes the duty cycle of vg increase, and the circuit enters PWM mode, as shown in part (I) of Fig. 2b. When the input voltage is too high, the sawtooth wave reaches its highest frequency. Then, vf becomes -1, vc decreases, which makes D decrease, and the circuit enters PWM mode, as shown in part (III) of Fig. 2b.

The driving signals of Q1 and Q2, which realize the buck-boost function in the front end, are always the same as that of S2. When the input AC voltage vin is in the positive half cycle, current flows through Q1 and no current flows through Q2. Meanwhile, when vin is in the negative half cycle, the opposite is true.

Due to the operating principles of the positive and negative half cycles of the input voltage vin being the same, the positive half cycle was taken as an example to analyze the proposed converter. Ignoring the conductive voltage of the diodes and MOSFETs as well as the influence of the input filter, and taking the directions indicated in Fig. 1 as the reference directions of the currents, main current waveforms of the converter can be obtained as shown in Fig. 3. Here, Fig. 3a is in the PFM mode and Fig. 3b is in the PWM mode.

Taking Fig. 3a as an example, each of the switching cycles can be divided into seven intervals, and equivalent circuits for each of the intervals are shown in Fig. 4.

Interval 1 [t0 < t < t1] At the time of t0, the current iLb has been reduced to zero, and the resonant current iLr is positive; iLr flows back to the resonant inductance Lr through the transformer T, the resonant capacitor Cr and the body diode of S2. Hence, when Q1, Q2 and S2 are simultaneously driven at t0, S2 is turned on under ZVS since its voltage is zero, and Q1 and Q2 are turned on under almost ZCS due to the existence of Lb1 and Lb2. The input voltage is applied at the ends of the two series inductors (Lb1 and Lb2) through D2, Q1, D3, S2, D8 and D5. Then, the current iLb(= iLb1 = iLb2) increases linearly, and the rising slope is vin/2Lb.

In this interval, Do2 is always on, and the circuit operates in the two-element resonant mode of Lr and Cr, with a resonant frequency of \({f}_{\mathrm{r}}=1/2\pi \sqrt{{L}_{\mathrm{r}}{C}_{\mathrm{r}}}\). The voltage of Lm is clamped by the output voltage, and iLm decreases linearly with a slope of n·vo/Lm (where n is the turn ratio of the transformer). The resonant current iLr and the magnetizing current iLm both decrease from positive to negative values. However, their decreasing rates are different. The difference is 1/n of the output current io2. The equivalent circuit of this interval is shown in Fig. 4a.

Interval 2 [t1 < t < t2] At t1, iLr and iLm are equal. Accordingly, io2 falls to zero naturally, which realizes ZCS. The converter enters the three-element resonant mode of Lr, Cr and Lm, with a frequency of \({f}_{\mathrm{m}}=1/2\pi \sqrt{({L}_{\mathrm{r}}+{L}_{\mathrm{m}}){C}_{\mathrm{r}}}\).

Since Lm is much larger than Lr, the three-element resonant frequency is much lower than that of the two elements. In other words, the change of iLr is slow and negative. This process lasts until time t2, and the equivalent circuit is shown in Fig. 4b.

Interval 3 [t2 < t < t3] At t2, Q1, Q2 and S2 are turned off at the same time. Due to the junction capacitors, the process can be considered as ZVS. Once Q1 and Q2 are turned off, D3, D4, D7 and D8 are turned on, while the inductors Lb1 and Lb2 are changed from series to parallel, and the value of iLb becomes twice that of the previous moment. The currents iLb and iLr are combined to discharge the junction capacitor of S1 and to charge the junction capacitor of S2. Since the junction capacitors are small, the charging and discharging processes are over after a very short time. Then, the body diode of S1 is on (which provides conditions for the turn-on of S1 with ZVS at t3), through which iLb and iLr charge the bus capacitor CB. In the meantime, the input voltage vin is not in the current circuit. Therefore, the bus voltage vb is not necessarily higher than the power supply voltage.

With the turnoff of S2, the voltage of the resonant tank (composed of Lr, Cr and Lm) increases rapidly. Do1 turns on, and io1 increases from zero naturally. Thus, ZCS is realized. The voltage of Lm is clamped by the output voltage. Meanwhile, iLm rises linearly, and the converter enters the two-element resonant mode again. In this interval, iLb decreases linearly under the bus voltage vb, with a slope of vb/Lb. The equivalent circuit of this interval is shown in Fig. 4c.

Interval 4 [t3 < t < t4] At t3, S1 is turned on with ZVS, and iLb and iLr charge the bus capacitor CB through S1, while iLm and iLb continue to increase and decrease linearly, respectively. The currents iLr and iLm increase from negative to positive values by the effects of iLb and vb. The equivalent circuit of this interval is shown in Fig. 4d.

Interval 5 [t4 < t < t5] At t4, iLb decreases to zero, and Do1 is still on and the converter still in the two-element resonant mode. The equivalent circuit of this interval is shown in Fig. 4e.

Interval 6 [t5 < t < t6] At t5, iLr and iLm are equal, and io1 decreases to zero naturally. As a result, ZCS is realized. Then, the converter enters the three-element resonant mode again. The equivalent circuit of this interval is shown in Fig. 4f.

Interval 7 [t6 < t < t7] At t6, S1 is turned off, and the junction capacitors of S1 and S2 are charged and discharged, respectively. A short time later, these processes end. Then, the body diode of S2 is on, which provides the condition for the ZVS of S2. The voltage of the resonant tank is changed from vb to zero. Then, Do2 is on, and io2 increases naturally from zero, which shows that ZCS is realized. At the time of t7, S2 is turned on, and the next switching cycle begins. The equivalent circuit of this interval is shown in Fig. 4g.

The operating principle of the PWM mode is similar to that of the PFM. The differences in the PWM mode are as follows. (1) The resonant current iLr is asymmetric in the positive and negative directions due to the different conduction times of S1 and S2. (2) The currents of the two output diodes Do1 and Do2 are different.

3 Parameter design of the main circuit

The proposed converter is an improvement based on the traditional single-stage LLC AC/DC converter. Thus, the parameters of the converter are designed with reference to the methods in Refs. [11,12,13, 19], and without considering the input filter. The rated input voltage, output voltage, load resistance and output power of the proposed converter are 220 V/50 Hz, 48 V/DC, 23 Ω and 100 W, respectively.

3.1 Buck-boost PFC cell

In order to realize power factor correction, the current of the PFC inductor must increase from zero to its maximum value in a switching cycle and then decrease to zero. This is fully discussed in Ref. [20]. Thus, it is not repeated here.

3.1.1 Buck-boost inductances L b1 and L b2

The inductances of Lb1 and Lb2 are equal. Both of them are Lb. A schematic waveform of the current ia in a cycle of the line frequency is shown in Fig. 5. The current ia is the same as iLb (as well as iLb1 and iLb2) when Q1 and Q2 are turned on, and it is zero when Q1 and Q2 are turned off. Therefore, ia is a discontinuous sawtooth wave, and its peak value changes sinusoidally with the input voltage vin(t) = Vm sin(2πf1t). Thus, the PFC function is realized and the power factor is high.

In a switching cycle, the equivalent average current of ia is:

where f1 is the line frequency of the input AC voltage; T1 is the cycle of the line frequency; fs is the switching frequency; Ts is the switching cycle; D is the duty ratio of the driving signals of Q1, Q2 and S2; and iap(t) is the peak value of a switching cycle of ia.

It can be seen from (1) that the equivalent average current of ia is inversely proportional to the inductance Lb and the switching frequency fs. In addition, it is directly proportional to the duty cycle D.

The input power Pin can be obtained from the equivalent current iav and the input voltage vin: circuit, in order to realize soft switching in the switches and output diodes, the switching frequency range of the converter should be between fr and fm [11, 21, 22]. Considering the size of the magnetic elements and the condition of the switches, the two-element resonant frequency is chosen to be about 100 kHz:

According to the characteristics of the LLC resonant.

Ideally, to improve the efficiency of the energy transfer, the working frequency of the LLC resonant circuit should be close to the resonant frequency fr [23]. However, in practice the maximum switching frequency should slightly lower than fr for reliable soft switching. Therefore, the maximum switching frequency fmax is set to 95 kHz. When the rated input voltage vin, the efficiency η and the duty ratio D are 220 V, 90% and 0.5, the value of Lb can be calculated from (2):

According to Refs. [11, 13, 18], the RMS value of the input current iin can be considered to be approximately the same as that of the current ia, which can be obtained from (1):

In addition, the RMS value of the input voltage vin is:

From (2) to (5), the power factor can be obtained as follows:

3.1.2 DC bus capacitor C B

In the steady state, the voltage of the bus capacitor CB is kept stable and only fluctuates with the input voltage vin. The fluctuation is related to the input power, the frequency of the input voltage, the value of the capacitor CB and its average voltage. According to Ref. [13], the product of the bus capacitance CB and its voltage vb remains constant.

Under its rated condition, assuming that the average value of the bus voltage vb is 330 V and the fluctuation Δvb is 50 V, the required capacitance CB can be calculated as:

A film capacitor of 22 μF/450 V can meet these requirements.

3.2 LLC resonant DC/DC cell

The operating principle of this part is the same as that of the traditional single-stage LLC resonant AC/DC converter, which is similar to the traditional LLC resonant DC/DC converters. The output voltage is inversely proportional to the switching frequency. The higher the switching frequency, the lower the output voltage, and vice versa. Many research results have been obtained in related analyses, which can be found in Refs. [11, 12]. Thus, they are not repeated. Only the circuit parameters are designed here.

For a wide voltage gain, the quality factor Q should be less than 0.5 [24, 25]. Q is defined as:

where RAC is the AC equivalent resistance of the load resistance RL, which is obtained by fundamental harmonic analysis (FHA). It is as follows:

where n is the turn ratio of the transformer T that is set to 4, which can ensure that the output voltage reaches 48 V when the input voltage vin is far lower than the rated value.

According to the formula of the two-element resonant frequency, the following can be obtained:

For the LLC resonant circuit, Lm is generally selected as:

According to (9)–(11) and the constraint that fr is 100 kHz, the resonant inductance Lr and the resonant capacitance Cr are selected as 120 μH and 22 nF, respectively. According to (12), and choosing a value of Lm that is five times Lr, it can be determined that Lm is 600 μH, and that three-element resonant frequency fm is about 43 kHz. Similarly, to realize soft switching reliably, the minimum switching frequency fmin is set to be slightly higher than fm, and 50 kHz is selected here.

Table 1 lists the results of a comparison between the proposed converter and the traditional one in terms of voltage stress, current stress of the semiconductors, design values of the inductance and capacitance, device counts, etc. It can be seen that the forward voltage drop of the diodes in the proposed converter is quite low, which can make up for the increasing number of devices.

Additionally, one advantage of the proposed converter is that when the input voltage is too high or too low, the duty cycle of the driving signal changes little, which is more conducive to the operation of LLC resonance and efficiency.

4 Experimental results analysis

In order to obtain and optimize the system performance, a frequency domain analysis is often needed. Since the modulation frequency is within the range of the resonant frequency, the state-space method is not suitable for LLC resonant networks. Generally, the extended description function method is used to obtain a small-signal model. Then, a frequency response diagram of the system is drawn. However, this method is very complex. In this study, MATLAB/Simulink is used to directly analyze the frequency response of the simulation model, and it is not necessary to calculate the system transfer function. Figure 6a shows the frequency response of the reduced-order open-loop system, which has poor performance. In order to achieve better system performance, the commonly used PI compensator is chosen to compensate the system [20]:

where kp and ki are the proportional and integral gains, which are 5.6 × 102 and 3.2 × 103, respectively. The system frequency response after compensation is shown in Fig. 6b. It can be seen that the system has a suitable phase margin, which meets the requirements of engineering implementations.

A 100 W experimental prototype was built in the laboratory to verify the proposed converter, as shown in Fig. 7. The experimental conditions of the converter are listed in Table 2, and the parameters of the main components of the converter are listed in Table 3.

Figure 8 shows the driving voltage of Q1 (Q2 and S2), the current of Q1, the currents ia and iLb marked in Fig. 1, when the input voltage vin is in the positive half cycle with different amplitudes. In Fig. 8b, c, the frequencies of vgsQ1 are different. However, the duty ratio of both is 0.5, which shows that when the input voltage is moderate, the output voltage vo can be stabilized by the PFM. In Fig. 8a, the input voltage vin is so low (110 V) that the voltage vo cannot be stabilized to a set value even though the switching frequency has been reduced to its lowest value of 50 kHz. Therefore, the duty cycle of vgsQ1 should be increased. In other words, D is slightly greater than 0.5. On the other hand, in Fig. 8d, when the input voltage vin is high (250 V), the voltage cannot be stabilized by increasing the frequency. Thus, the duty ratio of vgsQ1 should be reduced. In other words, D is slightly less than 0.5.

It can be seen from Fig. 8 that ia and iQ1 are zero during Q1 (Q2 and S2) switching off. In other words, when two buck-boost PFC inductors charge the bus capacitor CB in parallel, the input power supply is not in series in the circuit. This is different from the boost PFC topologies in [11,12,13], which can only realize the boost function.

When the input voltage is in the negative half cycle, ia is reverse, while iQ1 is zero. Meanwhile, the other two parameters are the same as those of the positive half cycle. Waveforms are shown in Fig. 9, which are obtained by extending the time of the waveforms in Fig. 8 to the line frequency. Figure 9a, b are waveforms of vin of 170 V and 220 V, respectively. As can be seen from Fig. 9, the shape of ia is sinusoidal.

Figure 10 shows waveforms of the driving voltage and D–S voltage of S2, and the resonant current iLr and the current io2 of the secondary diode Do2 at different input voltages. Two things can be seen from these figures. (1) Before the arrival of vgsS2, vdsS2 has been reduced to zero. Thus, ZVS is realized. (2) The current io2 increases gradually from zero. Then, it decreases to zero naturally. Thus, ZCS is realized.

Figure 11 shows waveforms of the input AC voltage vin and current iin, the DC bus voltage vb and the output voltage vo. It can be seen from these figures that when the input voltage is about 110 V, vb is about 200 V. Meanwhile, when the input voltage reaches the rated voltage and above, vb is more than 300 V and cannot reach 400 V. Thus, the switches cannot bear high voltages when turned off. Additionally, vin and iin are synchronous. Therefore, the power factor is high. Due to the input filter, iin is continuous and is kept high sinusoidal, and the harmonics are within an allowable value.

Figure 12 shows efficiency comparison curves between the proposed converter and traditional converters. It can be seen from this figure that the efficiency of the proposed converter can reach over 91% in both 110 V and 220 V power grids. In addition, the efficiency reaches 94% near the rated voltage of 220 V, which is close to that of the traditional converter with a low voltage input in [13]. Due to a lower voltage stress and forward voltage drop, as well as smaller duty cycle variations of the driving signals, the overall efficiency is higher than that in [14].

5 Conclusion

As an important aspect of medium and small power supplies, research on single-stage AC/DC converters has practical significance. In this paper, a single-stage LLC AC/DC converter with a wide input range and a low bus voltage was proposed. Theoretical analysis and formula derivation proved that the proposed converter has a high power factor and a low bus voltage and that it can realize soft switching of the power switching devices. Experiments verify that when the input voltage changes in a wide range of 110–250 V, the problem of a high bus voltage can be solved by varying the frequency and changing the duty cycle in a small range. It can also be seen that the voltage stress of the power switch devices is low. Power factor correction is realized through the buck-boost structure, and the PF value is approximately 1. The overall conversion efficiency of the converter can be maintained in the range of 91%—94%, and it can be applied to both 110 V and 220 V power grids.

References

Lazar, J., Martinelli, R.: Steady-state analysis of the LLC series resonant converter. In: Proceedings of 16th Annual IEEE Applied Power Electronics Conference and Exposition, pp. 728–735 (2001)

Yang, B., Lee, F., Zhang, A., Huang, G.: LLC resonant converter for front end DC/DC conversion. Proc. IEEE APEC 2, 1108–1112 (2002)

De Simone, S., Adragna, C., Spini, C., Gattavari, G.: Design-oriented steady-state analysis of LLC resonant converters based on FHA. In: Proceedings of International Symposium on Power Electronics, Electrical Drives, Automation and Motion, pp. 200–207 (2006)

Shen, Y., Zhao, W., Chen, Z., Cai, C.: Full-bridge LLC resonant converter with series-parallel connected transformers for electric vehicle on-board charger. IEEE Access 6, 13490–13500 (2018)

Kim, H., Kim, S., Lee, K.: A dual-output integrated LLC resonant controller and LED driver IC with PLL-based automatic duty control. J. Power Electron. 12(6), 886–894 (2012)

Hu, Z., Qiu, Y., Liu, Y., Sen, P.: A control strategy and design method for interleaved LLC converters operating at variable switching frequency. IEEE Trans. Power Electron. 29(8), 4426–4437 (2014)

Wang, H., Li, Z.: A PWM LLC type resonant converter adapted to wide output range in PEV charging applications. IEEE Trans. Power Electron. 33(5), 3791–3801 (2018)

Hu, H., Fang, X., Chen, F., Shen, Z., Batarseh, I.: A modified high-efficiency LLC converter with two transformers for wide input-voltage range applications. IEEE Trans. Power Electron. 28(4), 1946–1960 (2013)

Guo, B., Zhang, Y., Zhang, J., Gao, J.: Hybrid control strategy of phase-shifted full-bridge LLC converter based on digital direct phase-shift control. J. Power Electron. 18(3), 802–816 (2018)

Glitz, E., Ordonez, M.: MOSFET power loss estimation in LLC resonant converters-time interval analysis. IEEE Trans. Power Electron. 34(12), 11964–11980 (2019)

Lai, C., Shyu, K.: A single-stage AC/DC converter based on zero voltage switching LLC resonant topology. IET Electr. Power Appl. 1(5), 743–752 (2007)

Chen, S., Li, Z., Chen, C.: Analysis and design of single-stage AC/DC LLC resonant converter. IEEE Trans. Ind. Electron. 59(3), 1538–1544 (2012)

Ma, H., Lai, J., Zheng, C., Sun, P.: A high-efficiency quasi-single-stage bridgeless electrolytic capacitor-free high-power AC-DC driver for supplying multiple LED strings in parallel. IEEE Trans. Power Electron. 32(8), 5825–5836 (2016)

Ma, H., Li, Y., Chen, Q., Zhang, L., Xu, J.: A single-stage integrated boost-LLC AC–DC converter with quasi-constant bus voltage for multichannel LED street-lighting applications. IEEE J. Emerg. Sel. Top. Power Electron. 6(3), 1143–1153 (2018)

Fonseca, Z., Perin, A., Junior, E., Nascimento, C.: Single-stage high power factor converters requiring low DC-link capacitance to drive power LEDs. IEEE Trans. Ind. Electron. 64(5), 3557–3567 (2017)

Wu, T., Hung, J., Tseng, S., Chen, Y.: A single-stage fast regulator with PFC based on an asymmetrical half-bridge topology. IEEE Trans. Ind. Electron. 52(1), 139–150 (2005)

Yang, L., Liang, T., Chen, J.: Analysis and design of a novel three-phase AC–DC buck-boost converter. IEEE Trans. Power Electron. 23(2), 707–714 (2008)

Lee, S., Lee, D., Lee, S., Do, H.: Buck-boost AC-DC LED driver for lamp with visible light communication module. Electr. Power Compon. Syst. 47(4–5), 372–381 (2019)

Fang, X., Hu, H., Chen, F., Somani, U., Auadisian, E., Shen, J., Batarseh, I.: Efficiency-oriented optimal design of the LLC resonant converter based on peak gain placement. IEEE Trans. Power Electron. 28(5), 2285–2296 (2013)

Zhang, G., Zeng, J., Yu, S., Xiao, W.: Control design and performance analysis of a double-switched LLC resonant rectifier for unity power factor and soft-switching. IEEE Access. 8, 44511–44521 (2020)

Luo, J., Wang, J., Fang, Z., Shao, J., Li, J.: Optimal design of a high efficiency LLC resonant converter with a narrow frequency range for voltage regulation. Energies. 11(5), 1105–1124 (2018)

Kim, J., Park, M., Lee, B., Lai, J.: Analysis and design of LLC converter considering output voltage regulation under no load condition. IEEE Trans. Power Electron. 35(1), 522–534 (2020)

Zhang, Z., Xu, Z., Li, H., He, M., Tang, J., Ren, X., Chen, Q.: A 1-kV input SiC LLC converter with split resonant tanks and matrix transformers. IEEE Trans. Power Electron. 34(11), 10446–10457 (2019)

Qian, Q., Yu, J., Su, C., Sun, W., Lu, S.: A LLC resonant converter with dual resonant frequency for high light load efficiency. Int. J. Electron. 104(12), 2033–2047 (2017)

Lee, I., Moon, G.: The k–Q analysis for an LLC series resonant converter. IEEE Trans. Power Electron. 29(1), 13–16 (2014)

Acknowledgements

The authors wish to thank the reviewers for their careful, unbiased and constructive suggestions, which led to this revised manuscript.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Gao, J., Zhang, J., Zhu, Z. et al. Single-stage LLC AC/DC converter with wide input range and low bus voltage. J. Power Electron. 21, 1–12 (2021). https://doi.org/10.1007/s43236-020-00150-3

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s43236-020-00150-3