Abstract

Boost converters have wide applications in contemporary power industry, with few disadvantages like complicated design and nonlinear relationships. Amalgamation of renewable energy sources and modern applications like Electric vehicles increases the importance further, recent research studies aim simplification of design and control circuit to achieve maximum gain with lesser passive elements. Modified DC-DC converters are required for contemporary medium and high voltage applications. This work presents a transformer-less, non-isolated, modified DC converter that combines the voltage multiplier concept with a traditional boost converter structure for high-voltage conversion ratios. This manuscript incorporates a multi-stage output section to enhance the voltage amplification of the system. The paper introduces a two-stage converter and provides an analysis of its working principle in both continuous conduction mode and discontinuous conduction mode, including the corresponding equations. This topology is also evaluated in comparison to previous topologies reported in the literature, and the analysis is provided. The suggested configuration is confirmed by simulation and the outcomes are authenticated using a physical prototype.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The utilization of renewable energy sources, namely solar energy, for distributed power generation has garnered significant interest due to the depletion of fossil fuels and the escalating levels of greenhouse gas emissions. Solar panels require series–parallel configurations, requiring appropriate power converters to generate high voltages [1]. Technological advancements, particularly in the applications require portability and photovoltaic arrays, require wide DC conversion ratios. Due to conductor losses, step-up transformers, and turn-on and turn-off times, conventional converters have a limited range of conversion ratios [2]. Fuel cells present potential substitutes but may result in a low DC voltage, complicating the controller design. Isolated dc-dc converters are undesirable for high-voltage gain applications, such as solar-powered systems, due to concerns like saturation, low efficiency, and large size [3]. Non-isolated topologies such as cascaded technology can resolve these issues. However, cascaded boost converters face issues of reverse recovery, instability, and high-voltage stress on the switches and diodes used in higher stages. Current-mode control is commonly employed to regulate switch-mode DC-DC converters; however, complex topologies such as quadratic converters may exhibit ambiguous behavior because of inner coupling and right-half side zeros [4]. Power converters frequently incorporate impedance networks to improve performance. To provide higher conversion rates and change the placement of additional capacitors and inductors for voltage gains, capacitors or inductors can be swapped. However, because impedance network synthesis is based on designer inspiration and experience, it introduces randomness and hinders the creation of new power converters. The computational complexity and lack of rationalization prevents the new converters to perform under various operating conditions for various applications [5].

Recent research articles proposed various transformer less and other converters in the context of improved voltage gain, reduced number of switches, multiple inputs, multiple outputs, reduced number of passive components, etc. Multistage DC converters were introduced for higher voltage gain, with higher number of switches [6] and multiple inputs [7]. They offered many advantages in contrast to their single-level counterparts, including higher efficiency, lower cost, and smaller size. Single switch multistage converters were introduced for high voltage conversion of low voltage sources, with large number of capacitors in the output stage [8]. Voltage multipliers, switched inductors, quadratic converters are the recent methodologies used in the DC converters for higher voltage gain and lesser switching stress [9, 10]. Raising of Electric Vehicles made several developments in the field of choppers. Introduction of bidirectional converters is one of the significant changes in choppers, used for battery charging not only in the normal conditions also in the fault conditions [11]. These topologies normally used to interface low voltage source to high voltage motor or any other load with bidirectional current flow capability [12]. However, they also had few drawbacks, such as the risk of imbalance between the different voltage levels and high switching stress [13]. Despite these challenges, multilevel DC-DC converters are becoming increasingly popular in a variety of applications, such as renewable energy generation, and power supplies for electronic devices [14]. Recent advancement in the DC-DC converters use voltage lift technique with reduced number of components. The converter achieved an increased voltage gain through a simple structure and provides free current ripple for the input source [15]. The output of the converter is enhanced using the voltage multiplier cell along with reducing switch count, voltage stress, and harmonic distortion [16]. SEPIC topology was used to settle quicker than other recent converters presented in recent literature at steady state voltage and current, reducing ripple values and ensuring stable output voltage and current [17]. The utilization of a solitary-driven semiconductor switch and inductor resulted in a substantial increase in voltage amplification, while maintaining a continuous input current and achieving a greater step-up conversion ratio. [10]. Modified Switched Inductor were used to reduce voltage stress across active switches. It provided higher efficiency with lesser cost [18]. Usage of Additional voltage boost capacitor provides more voltage gain with less stress across switch [19, 20]. Higher gain values also achieved using quadratic boost converter, double switched inductor and multiplier cells. These components also help reduce voltage stress on diodes and capacitors, as well as the size of the inductors [21, 22]. These topologies provide benefits such as reduced voltage stress on semiconductor devices, a lower number of devices required, increased power conversion efficiency, and a higher switch usage factor [23, 24].

This work presents a transformer-less non-isolated chopper that achieves a large voltage gain using only a single switch. The subsequent chapter provides a comprehensive explanation of the converter’s circuitry and a rigorous mathematical analysis. Chapter 3 outlines the criteria for selecting components and conducts a thorough assessment of the converter, comparing it to alternative topologies discussed in recent scholarly works. The final sections of the script contain the simulation and hardware findings, which serve to confirm the accuracy of the mathematical analysis of the converter Table 1.

2 Circuit Diagram for Multistage Boost Converter

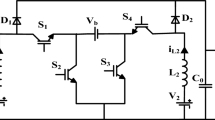

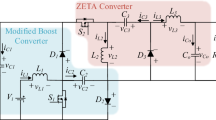

Figure 1 displays the comprehensive circuit schematic of the converter that has been proposed. The system consists of two distinct stages: the voltage multiplier stage and the voltage lifting stage. Initially, a diode and an inductor are linked in a sequential manner across the capacitor. This circuit has the capability to amplify the input voltage by a factor of two, depending on the values of the inductors. The second stage includes a switch SA, which regulates the output voltage based on the duty cycle. The voltage boosting stage comprises a sequence of self-compensating capacitors that are linked in parallel with the load to elevate the input voltage. The overall output voltage of the circuits is determined by the number of self-balancing capacitors (M) connected in the voltage lifting step.

Circuit diagram of the two-stage converter shown in Fig. 2. It is derived from the generalized circuit, also having two stages. In the first stage, when VS is more than VA, diodes DS1 and DS2 are forward biased and capacitor CS1 charges, equal to VS1. When VA is more than the input voltage VS, diodes DS1 and DS2 are reverse biased and the capacitor CS1 discharges. Booster capacitor produces a voltage of 2VS, also responsible for the higher voltage gain provided by the topology.

The output stage contains three diodes D0, D1 and DA to carry the capacitor current during charging and discharging. This stage also contains two output capacitors C1 and C2 and a voltage balancing capacitor CA. This setup balances the capacitor voltage during switch on and off conditions and provides a multi stage output across the load. Voltage across C1 is Vo,1 which is same as the output voltage of the multiplier stage (VA).

2.1 Modes of operation

Mode 1 (t0—t1): The passive components are selected for Continuous Conduction Mode (CCM) in such a way that the current value not falls to zero at any time. During this mode, Switch SA is tuned On and forms a closed loop for the current at the input side as shown in Fig. 3. Capacitor C1 discharges diode D1 to maintain the voltage balance at C1. Inductors LS1 and LS2 charge from the source, up to the voltage level VS.

where, VLS1, VLS2 are the voltage across inductors LS1 and LS2 respectively. Capacitor CS also charges from the supply, so the voltage of the capacitor also equal to VS. Current ripples because of inductors LS1 and LS2 are described as,

Mode 2 (t1—t2): During this mode of operation given in Fig. 4, switch SA in reverse bias condition and turned off. Inductors LS1 and LS2 discharges through diodes D0 and DA. Since the switches are blocked during this mode, the stress at the switches is equal to the capacitor voltage (V0,1) as shown in Fig. 5. Performance parameters of the components in this mode are given in (5)-(7)

where VS is the source voltage. By applying V-s balance principle in (1) and (5),

The potential stress at output capacitor C1 can be derived as,

Similarly, the overall output voltage across the load, VO,M can be written as based on Fig. 1,

where, M is the number of output capacitors.

2.2 Discontinuous Conduction Mode

Similar to CCM, Discontinuous Conduction Mode (DCM) has first two modes of operation during the interval t0-td. During first mode of operation from 0 < t < D1T, under steady state conditions, average output current through the capacitor will be,

So, from the operation of the converter during CCM given in (1)-(11), current flowing through the inductors LS1 and LS2 during mode-1 of DCM can be obtained as,

where, f is the switching frequency and LS1 = LS2 = L. During mode-2 operation of DCM, diodes DS1, DS2, D0 and DA are reverse biased as shown on Figs. 6 and 7. So, the current flowing through the inductors is forced to become zero at time td. Peak values of inductor currents are given in (12) when the switches are turned OFF.

Load is supplied by the capacitors C1 and C2, then the output voltage becomes,

From (11)-(14), duty cycle of the DCM can be calculated as,

By considering the average current in the capacitor and DC,

gain value of this mode is,

where, fs = 1/T and LS1 = LS2 = L. By solving the equation, the time constant \(\tau = \frac{{Lf_{S} }}{{R_{O} }}\) will be

Based on the value of \(\tau\), the boundary between DCM and CCM with respect to various duty cycles is shown in Fig. 8.

3 Selection of Components

3.1 Voltage Stress Across Devices

Higher voltage stress leads to more complexity in the design and increases the cost of the device. Voltage stress across the device is the essential parameter to select a device. Voltage stress across the device is the function of current flowing through the device. Average value of inductor currents ILS1 and ILS2 are given in (24) and (25),

Based on the operating modes discussed in Fig. 5, Voltage stress across switch is given by (26)

where, VSA is the potential stress across the switch SA. Referring to Fig. 6, when diode DS1 and DS2 is blocked the potential stress is equal to VC1-VS. The Voltage across the diode DS1 and VS2 is,

Similarly, voltage stress across D0 (VD0) equals to output voltage and given in (21).

3.2 Selection of Inductors

Critical values of inductances are calculated using the minimum inductance calculation method from CCM operations. Referring to Fig. 4, change in inductor current ILS1 is obtained as

From (34), (35) and (25), minimum value of inductor LS1 can be calculated as,

Concerning Figs. (3) and (4), current flowing through the inductors in both modes is same. So, the value of inductor LS2 is equal to LS1.

3.3 Selection of Capacitors

Selection of capacitors is also an important factor in the DC-DC converter design that provides a better voltage gain and stability. From Figs. (3) and (4), change in charge and voltage ripple across the capacitor is,

(25) and (26) provide the relationship between the capacitance value, voltage ripple and the switching frequency f. Minimum value of CS is given by

Which is the function of voltage ripple across CS given in (40) and switching frequency f.

3.4 Comparison with other Topologies

The multistage DC boost converter presented in this manuscript is compared with other topologies presented in the recent literature. Some of the key parameters like Overall Gain, Number of passive and active devices, voltage stress across the switch and Gain value with respect to Total Component Count (TCC). The gain value of the converter is greater than the topologies described in [10, 15, 19] and [21]. The voltage across the switch is better than all topologies even gain value is lesser than some of the topologies presented. [17,18,19] have posted exponential voltage gain with higher number of components and poor gain to TCC ratio. The pictorial representation of the voltage gain is presented in Fig. 9, in which the gain of all the topologies are plotted with respect to duty cycle. The proposed topology posted higher gain value. The corresponding gain to TCC ratio with respect to duty cycle is plotted in Fig. 10. Figure 11 shows the overall efficiency comparison of the topology for various load condition. All the topologies compared in this scenario provide higher efficiency in which the proposed topology registered better efficiency over most of the recent topologies. The proposed topology produces a maximum efficiency of around 93% at 200W, only [22] has better efficiency than other topologies at this load. It is observed that the presented topology has better parameters in overall, which could be a good alternative for the existing power converter for modern applications.

4 Results and Discussion

4.1 Simulation Result

The modes of operation and mathematical representation discussed in previous chapters are verified with Matlab/Simulink tool. The simulation results are presented in this section to prove the mathematical analysis of the system. The system is simulated with active and passive components values analysed in previous chapters.

An input voltage of 20 V (VS) is considered, and the resulting voltage across the load in the converter is displayed in Fig. 12. The frequency at which the switching occurs is 20 kHz, and a load with a resistance of 100Ω is being taken into account. In terms of the design specifications, the circuit incorporates passive elements such as LS = 50mH, CS = 200μF, and output capacitors with a capacitance of 400μF. The converter's overall output voltage V0,2 is measured at 150 V, which deviates from the theoretical output voltage of 160V. The output voltage stabilizes at a time of 0.04 s with a maximum value of 220 V, falling inside the allowed range.

The corresponding output current of the presented circuit is shown in Fig. 13. The output current is found to exhibit a direct correlation with the overall output voltage and stabilizes at a value of 1.6A, which makes the overall power of the system around 240W. This is slightly lesser than the described power of 250W.

The inductor values have chosen for the CCM operations were explained in chapter 3. Figure 14 shows the inductor current at CCM, which also describes the current oscillates between a minimum value of 1.8 A and a maximum value of 11A. The value of inductor current oscillates around 6A, satisfies the design parameters for CCM operation. It is also observed that, since the inductor values are equal the inductor currents are equal. The capacitor voltage is shown in Fig. 15. The voltage across the input capacitor is 18 V, lesser than the input voltage by minimum value.

The presented circuit is being analyzed using inductors of different values as well. While the voltage and current levels at the load remain comparable to the previous mode of operation, the current flowing through the inductors varies depending on the specific inductor values, as seen in Fig. 16. This condition arises when the value of LS1 exceeds that of LS2, but both currents have identical minimum and maximum values and similar durations for charging and discharging.

The proposed multistage DC converter analysed with DC mode to verify the mathematical analysis. Figure 17 shows the output voltage of the circuit at DCM. Though the settling time is similar to CCM, amplitude increases to 165V. The corresponding load current value shown in Fig. 18, settles at 1.6A. This makes the overall power of the circuit as 260W, higher than the designed value.

Figure 19 shows the inductor current at DCM, which also describes the current oscillates between zero and a maximum value of 16A. The value of inductor current oscillates around 8A, satisfies the design parameters for DCM operation. The voltage across capacitor CS during DC mode shown in Fig. 20. As per the design of the circuit the voltage across the capacitor equal to the input voltage of around 18V.

Theoretical and simulated values are compared, and the findings are presented in Fig. 21. The overall gain value of the proposed two stage DC converter exhibits exponential growth as the duty cycle increases. The output voltage increases correspondingly, as it is directly reliant on the input voltage.

Overall efficiency of the circuit for various duty cycles is presented in Fig. 22. It shows the efficiency increases at the first half of the duty cycle and reduces during the second half of the duty cycle range. The maximum efficiency of the converter is achieved over D = 0.4. It is also observed that the overall losses occurred at the converter is minimum at this point, with a gain of 6.67, as described in chapter 3.

4.2 Hardware Results

The hardware prototype of the presented topology shown in Fig. 23, was developed to verify the simulation results presented in previous section. The prototype has a IRF840mosfet for switching, the FPGA Spartan kit was utilized to generate a gating pulse. The passive components are utilized as do in the simulation. Figure 24 displays the input and output voltages of the system when a gate pulse is applied. The converter yields a total output voltage of 140 V when provided with an input of 20 V. The prototype's overall gain value is 7, which is lower than the theoretical value. The voltage across capacitor C1 is 70 V, which exhibits an equivalent gain value for the initial stage.

The potential stress across across the switch SA is presented in Fig. 25. Switching stress is reduced to zero when turned on and increases when turned off. It is observed that the switching stress value is around 80V which is almost equal to the capacitor voltage V0,1. The capacitor voltage is also presented in the figure for comparison. The overall switching stress of the converter is less when compared to output voltage. This is always constant even though the number of output stages increases.

Figure 26 shows the current values flowing through the inductors LS1 and LS2. It is observed that the inductor charges when the switch is ON and discharges during switch OFF condition. The minimum and maximum value of inductor current ILS1 is 4A and 10A respectively, shows the experimental results follows the simulation results as the current oscillates at 7A. The current through inductor LS2 oscillates between 4 and 9A, describes the inductor values are equal and the circuit operates at Continuous Conduction Mode.

Voltage across inductors LS1 and LS2 depicted in Fig. 27. As mentioned in the previous sections, voltage across the inductors are equal to the input voltage. The hardware output satisfies that the voltage across the inductors are around 20V, equal to the input voltage. It is observed that the hardware results prove the effectiveness of the circuit as do in the simulation. This topology could be an effective alternate for the existing DC-DC multistage converter topologies and the results proved it.

5 Conclusion

A transformer-less multistage boost DC-DC converter with modified voltage doubler circuit was discussed in this manuscript. This topology has two stages as the first stage gave a significant boost to the input voltage and the second stage lifted the voltage based on the number of stages. This topology has various advantages like high voltage gain, fewer passive components, and less voltage stress. The model was analysed in both continuous conduction mode and discontinuous conduction mode with equal and unequal inductance values. Despite the difference in values between the two inductors, the proposed converter exhibits good performance and easy control. The performance parameters were also presented along with the current and voltage waveforms. Performance of the presented model was verified in continuous conduction mode with a hardware prototype and the results were presented. This converter can provide a voltage gain of around 8 for two output stages, with lesser potential stress at the switch. It is suitable for low power applications with no additional switches and isolated gate-driving circuits.

References

Kolli A, Gaillard A, De Bernardinis A, Bethoux O, Hissel D, Khatir Z (2015) A review on DC/DC converter architectures for power fuel cell applications. Energy Convers Manage 105:716–730

Hossain MZ, Rahim NA (2018) Recent progress and development on power DC-DC converter topology, control, design and applications: a review. Renew Sustain Energy Rev 81:205–230

Wang H, Gaillard A, Hissel D (2019) A review of DC/DC converter-based electrochemical impedance spectroscopy for fuel cell electric vehicles. Renew Energy 141:124–138

Raghavendra KVG, Zeb K, Muthusamy A, Krishna TNV, Kumar SVP, Kim DH, Kim HJ (2019) A comprehensive review of DC–DC converter topologies and modulation strategies with recent advances in solar photovoltaic systems. Electronics 9(1):31

Sivakumar S, Sathik MJ, Manoj PS, Sundararajan G (2016) An assessment on performance of DC–DC converters for renewable energy applications. Renew Sustain Energy Rev 58:1475–1485

Shen M, Peng FZ, Tolbert LM (2008) Multilevel DC–DC power conversion system with multiple DC sources. IEEE Trans Power Electron 23(1):420–426

Babaei E, Abbasi O (2016) Structure for multi-input multi-output dc–dc boost converter. IET Power Electron 9(1):9–19

Rosas-Caro JC, Ramirez JM, Peng FZ, Valderrabano A (2010) A DC–DC multilevel boost converter. IET Power Electron 3(1):129–137

Zhu X, Jiang L, Zhang B, Jin K (2022) The resonant modular multilevel dc–dc converter adopting switched-inductor cells for high step-up ratio. IEEE J Emerg Sel Top Power Electron 10(6):6634–6647

Sadaf S, Bhaskar MS, Meraj M, Iqbal A, Al-Emadi N (2020) A novel modified switched inductor boost converter with reduced switch voltage stress. IEEE Trans Industr Electron 68(2):1275–1289

Monteiro V, Oliveira CF, Afonso JL (2023) Experimental validation of a bidirectional multilevel dc–dc power converter for electric vehicle battery charging operating under normal and fault conditions. Electronics 12(4):851

Rathore V, Rajashekara K, Nayak P, Ray A (2022) A high-gain multilevel dc–dc converter for interfacing electric vehicle battery and inverter. IEEE Trans Ind Appl 58(5):6506–6518

Sutikno T, Purnama HS, Widodo NS, Padmanaban S, Sahid MR (2022) A review on non-isolated low-power DC–DC converter topologies with high output gain for solar photovoltaic system applications. Clean Energy 6(4):557–572

Alkhaldi A, Elkhateb A, Laverty D (2023) Voltage lifting techniques for non-isolated DC/DC converters. Electronics 12(3):718

Shahir FM, Babaei E, Farsadi M (2018) Analysis and design of voltage-lift techniquebased non-isolated boost dc-dc converter. IET Power Electron 11(6):1083–1091

Subramanian V, Marikannu M, Senthilkumar B, Reka J, Rathi Devi P, Ramadoss V (2023) A novel multilevel DC-DC flyback converter fed H bridge inverter. J Circuits Syst Comput 32:2350209

Ravindran, V., Ponraj, R., Zameerbasha, S.S., Kanna, N.S., SamuelRaj, S. and Sabarish, B., (2021), May. Dynamic performance enhancement of modified sepic converter. In: 2021 2nd International Conference for Emerging Technology (INCET) (pp. 1–5). IEEE.

Ghabeli Sani S, Mohammadi F, Banaei MR, Farhadi-Kangarlu M (2019) Design and implementation of a new high step-up DC-DC converter for renewable applications. Int J Circuit Theory Appl 47(3):464–482

Rezaie M, Abbasi V (2020) Effective combination of quadratic boost converter with voltage multiplier cell to increase voltage gain. IET Power Electron 13(11):2322–2333

Marimuthu M, Vijayalakshmi S, Shenbagalakshmi R (2020) A novel non-isolated single switch multilevel cascaded DC–DC boost converter for multilevel inverter application. J Electr Eng Technol 15:2157–2166

Tewari N, Sreedevi VT (2018) A novel single switch dc-dc converter with high voltage gain capability for solar PV based power generation systems. Sol Energy 171:466–477

Bhaskar MS, Padmanaban S, Almakhles DJ, Gupta N, Subramaniam U (2022) Double-switch switched-inductor converter with minimal switch voltage stress for renewable energy conversion. Comput Electr Eng 98:107682

Divya Navamani J, Vijayakumar K, Jegatheesan R, Lavanya A (2017) High step-up DC-DC converter by switched inductor and voltage multiplier cell for automotive applications. J Electr Eng Technol 12(1):189–197

Ponraj RP, Sigamani T, Ravindran V (2023) Analysis of multi-input multilevel boost inverter circuit with optimal firing angles using dSPACE. J Electr Eng Technol 18(2):1135–1145

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of Interest

On behalf of all authors, the corresponding author states that there is no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Saravanan, R., Jaya, N. Multistage Boost Converter with Modified Voltage Multiplier for Contemporary Applications. J. Electr. Eng. Technol. 19, 4323–4333 (2024). https://doi.org/10.1007/s42835-024-01857-0

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s42835-024-01857-0