Abstract

This paper presents a low-power, wide tuning range CMOS voltage-controlled oscillator with MCML (MOS current mode logic) differential delay cell. Voltage controlled oscillator (VCO) circuit is designed in TSMC 0.25 μm CMOS process. To achieve the broad frequency range concept of variable capacitance is employed in the proposed VCO circuit. Source/drain tuning voltage (Vtune) and body bias voltage (Vb) of I-MOS varactor are used to achieve variable capacitance at different I-MOS varactor widths (W). The dual control voltage of I-MOS varactor results in a tuning range from 0.528 GHz to 2.014 GHz. VCO's figure of merit (FoM) is 152.13 dBc/Hz with phase noise of −93.77 dBc/Hz at 1 MHz offset from the oscillation frequency. The proposed VCO dissipates maximum power of 3.127 mW.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

With the rapid growth in the high-speed wireless communication system, the demand for integrating high-performance CMOS circuit’s on-chip is raising [1, 2]. Conventional CMOS circuit suffers from large power consumption at high speed due to dynamic power consumption directly related to the operation frequency. The different logic style has been proposed in the literature for low power consumption among them MOS current mode logic (MCML) is extensively used as an option to CMOS logic style for high-speed circuits. MCML dissipates less power at high frequency and provides high noise immunity [3,4,5]. Static power consumption due to the use of constant current sources is also a concern in MCML logic.

In comparison to the CMOS logic approach, MCML shows better power delay products at high frequency. In this paper, a power-efficient VCO is designed using the MCML technique for low-power applications. VCO circuits are designed by inductor-capacitor (LC) based or ring-based approach. A ring topology-based VCO is preferred over LC topology since its starting time is significantly less, and it avoids the use of passive inductors. Also, integration is straightforward and compatible with the digital CMOS fabrication process. Ring oscillator structures are usually constructed by several delay elements such as a logic gate and an operational amplifier. In the logic gate, the control current is modified to change the transition time of each delay stage. In the operation amplifier, the current is adjusted to vary the bias current so that the operation amplifier gains are modified to vary the oscillation frequency of VCO. Ring oscillators are widely used in applications like clock generators, frequency synthesizers, and analog to digital converters circuits [6, 7]. Ring oscillator provides a wide tuning range, quadrature or multiphase output, small die area compared to LC oscillator [8].

Further, various design structures of VCOs can be grouped into two major design categories as VCOs with single-ended and differential-ended delay cells [9, 10]. In a single-ended configuration, the maximum frequency is mainly depends on the delay time of delay cell. Various methods have been proposed to tune the ring oscillator frequency [11, 12]. On the other hand, differential-ended topologies are more preferable for high-speed applications because they provide better common-mode and supply voltage rejection performance. Differential-ended delay cells have many advantages over the single-ended cell-like single-ended VCO. They can be designed only by the odd number of delay stages compared with differential ended delay cell, and it has no common-mode rejection of supply voltage and body noise [13]. Multiphase output can also be obtained in differential-ended VCO [14]. Each delay stage in single-ended VCO is designed by an inverter that consist an NMOS and PMOS transistor. Alternatively, a differential-ended delay cell is designed by a load element (active and passive) and a differential pair. In both types of configuration, frequency variation is achieved by varying the delay cell's delay time. In this paper, MOS based varactor is used to vary the delay time of the proposed delay stage. In comparison to reverse-biased diode varactor, MOS varactors are more preferably used in CMOS circuits. This kind of varactors shows large capacitance and easiness of implementation in CMOS technology. Different configurations of MOS transistors are reported to work as MOS varactors. Different VCO designs based on the MOS varactors have been reported in [15,16,17]. In conventional structure drain, source, and substrate of a MOS transistor are tied together to form one end of the varactor. Variable capacitance is obtained with a change in the voltage across the varactor. In this paper, the MOS varactor working in inversion mode is used to obtain frequency tuning. In inversion mode, the bulk of the NMOS/PMOS transistor is connected with the lowest/highest voltage in the circuit. MOS varactor is placed at the output of each stage as a variable load element. With the change in load element, a tunable range of frequency is obtained in the proposed VCO.

Further, the paper is organized as follows: Sect. 2 describes the architecture of the proposed VCO. Section 3 discusses the result and performance analysis of the proposed VCO. Finally, Sect. 4 provides the conclusion.

2 VCO architecture

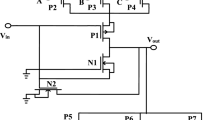

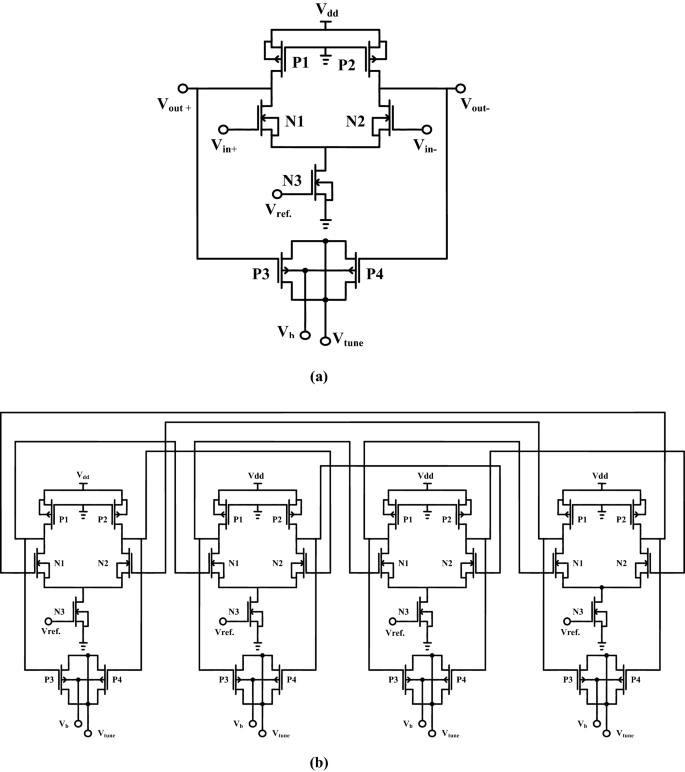

The circuit diagram of the proposed delay stage, along with a four-stage ring VCO with I-MOS varactor, is shown in Fig. 1. Figure 1a shows a differential-ended delay stage designed with MCML logic. MCML based delay cell include a pull-down network (PDN), a constant current source, and a pull-up load circuit. Pull down the network is designed with two NMOS transistors (N1, N2) as an input that performs the logic function. Two PMOS transistors (P1, P2) are used as a load element responsible for the voltage swing, and transistors (N3) function as a constant current source. PMOS transistors (P3, P4) of the I-MOS varactor are included to change the oscillation frequency of the proposed VCO. The function of the MCML delay cell is based on the principle of current steering. As the input voltage across the input transistor is high (low), the source coupled NMOS transistor pair steers the bias current (Iref) to drain of N1 and N2, thus generates a low (high) output voltage. In the MCML delay cell, the PMOS transistor operates in the triode region, and the reference current generated by the transistor N3 is divided into two NMOS drain currents. The differential input voltage is applied at the input of NMOS transistors that is (Vin+) – (Vin−), the reference current is flowing through the transistor N3. A tunable frequency range is obtained by changing the control voltage Vtune and Vb of the I-MOS varactor. Figure 1b shows the four-stage ring VCO designed using four identical differential stages connected in a closed-loop. By varying the control voltage, the equivalent capacitance at the delay stage's output terminal varies, and subsequently output frequency of VCO changes.

The delay stage's working can be explained by considering the half part of the differential pair circuit. Input voltage is applied at transistor (N1), and the output voltage is obtained at the drain terminal of the N1 transistor. For a fixed value of reference voltage (Vref.), transistor N3 works as a constant current source Iref. MOS transistor (P1) is acting as a load element. A frequency variation in VCO is achieved by connecting an I-MOS varactor at the delay cell's output node. A dual control voltage is applied to the I-MOS varactor. Due to a change in the capacitance, a wide range of frequency is achieved. The I-MOS varactor’s capacitance is estimated with the model as shown in Fig. 2.

Due to variation in load capacitance, frequency tuning is achieved in the proposed VCO while keeping power consumption remains constant. Equivalent capacitance of I-MOS varactor is given by the Eq. (1).

where: Cpara., Cox and Cdep are the parasitic capacitance, oxide capacitance and depletion capacitance under the gate, per unit area, respectively. Depletion capacitance under the gate oxide is given by the Eq. (2).

In Eq. (2), Ɛsi and Xd denotes the permittivity of silicon material and depletion width under the gate oxide. Variation in Cequi depends on the applied voltage across I-MOS varactor. As the control voltage increases, depletion width (Xd) under the gate oxide increases that result to decrease in the equivalent capacitance.

3 Results and discussions

The proposed VCO has been implemented in 0.25 μm CMOS technology. Frequency tuning range has been obtained with a change in control voltage i.e., Vtune and Vb of I-MOS varactor. Effect of change in supply voltage (Vdd) also has been observed. Output frequency tuning range of proposed VCO with Vtune variation from 1.5 V to 2.5 V at Vdd = 2.5 V and Vb = 2.5 V has been shown in Table 1. Proposed VCO achieved a variable frequency from 0.528 GHz to 1.472 GHz. Figure 3 shows the effect of Vtune on the output frequency. With rise in the tuning voltage, the equivalent capacitance at the output node of the delay stage increases, affecting the delay time of the delay stage. As a consequence, the output frequency of VCO decreases.

Table 2 provides the output frequency variation with change in Vdd at fixed Vtune = 1.5 V, and Vb = 2.5 V. VCO shows a tuning range from 0.710 GHz to 2.198 GHz with variation in Vdd from 2 to 3 V with power dissipation variation from 1.744 mW to 3.127 mW. With the rise in the Vdd, the current is flowing in the delay stage increases, increasing the output oscillation frequency. Further, power consumption directly related to the Vdd also shows the rising trends, as shown in Table 2. Figure 4 illustrates the frequency variation with I-MOS varactor width (W).

Table 3 shows the effect of variation in the Vb of the I-MOS varactor. Output frequency Variation with Vb is obtained at fixed Vdd = 2.5 V and Vtune = 1.5 V. From Table 3, it is evident that ring VCO oscillates in a range of 0.852 GHz to 2.014 GHz at a different value of MOS varactor widths (W). Figure 5 shows the trends for the frequency variation with Vb. With the increase in the Vb, equivalent capacitance across the gate and substrate terminal decreases, increasing the proposed VCO output frequency. Output waveforms for the VCO are shown in Fig. 6 with variation in Vdd and MOS varactor width (W).

Frequency tuning characteristic of the proposed VCO for different temperatures is presented in Table 4 at Vdd=1.8 V. Dual control voltages (Vtune and Vb) are fixed at 1.5 V and 2.5 V, respectively. The output frequency of proposed VCO decreases as temperature rises. With the change of temperature, parasitic effects in the circuit vary along with the carriers’ mobility effects. Overall current in the circuit is affected by these variations, and output frequency decreases. The temperature dependence of generated frequency is plotted, as shown in Fig. 7.

Performance characteristics of the proposed VCO at various Vdd are presented in Table 5. At low Vdd phase, noise and merit figures are improved due to the power consumption reduction. The circuit, however, shows a reasonably good phase noise performance over the wide range of supply voltage. Phase noise and jitter are continuous random variations in VCO. Phase noise is generally represented in the frequency domain, and jitter is usually characterized in the time domain. Figure 8 shows the phase noise waveform of the proposed VCO at 1 MHz offset.

Table 6 shows the major performance parameters for the proposed VCO design and comparison with the previous reported work using the Figure of merit (FoM) is given by the Eq. (3). [17] Which evaluate three performance parameters of VCOs; phase noise, frequency and power consumption.

where: fosc is the resonating frequency of proposed VCO, foff. is offset frequency, Pdiss represents the power consumption and PN define the phase noise in dBc/Hz of proposed VCO.

4 Conclusions

In this work, a low-power MCML based ring-based VCO in 0.25 μm standard CMOS technology is presented. MOS varactor tuning technique is utilized to obtain a wide range of frequencies. The proposed technique's results showed that improvements in power consumption, tuning range, and phase noise are obtained. The range of frequency from 0.528 GHz to 2.014 GHz is achieved for the proposed VCO by altering the I-MOS varactor's dual control voltage. Proposed VCO achieves -93.77 dBc/Hz phase noise at an offset of 1 MHz from 1.272 GHz oscillation frequency. Proposed VCO has a figure of merit (FoM) of 152.13 dBc/Hz with a power dissipation of 2.359 mW. More design improvements in the proposed delay cell can be explored for nano scale VCO design with wider frequency range and low power. Additional tuning techniques in addition to MOS varactors with improved delay cell can results in better VCO design.

References

An TJ, Son KS, Kim YJ, Kong IS, Kang JK (2014) A 8.7 mW 5-Gb/s clock and data recovery circuit with 0.18-µm CMOS. IEEE Int Symp Circuits Syst (ISCAS) 2014:2329–2332

Shylu DS, Paul PS, Moni DJ, Monica Helan JA (2020) A power efficient delta-sigma ADC with series-bilinear switch capacitor voltage-controlled oscillator. Telkomnika 18(5).

Pradeep KS, Kumar SS (2018) Design and development of high performance MOS current mode logic (MCML) processor for fast and power efficient computing. Clust Comput, 1–9. https://doi.org/10.1007/s10586-018-1917-5

Yamashina M, Yamashina H (1992) An MOS current mode logic (MCML) circuit for low-power sub-GHz processors. IEICE Trans. Electron. E75-C (10), pp 1181–1187.

Jamshidi V, Fazeli M (2018) Design of ultra-low power current mode logic gates using magnetic cells. AEU-Int J Electr Commun 83:270–279

Abiri E, Salehi MR, Salem S (2014) A low phase noise and low power 3–5 GHz frequency synthesizer in 0.18 µm CMOS technology. Microelectronics J 45(6):740–750.

Sai A, Kobayashi Y, Saigusa S, Watanabe O, Itakura T (2012) A digitally stabilized type-III PLL using ring VCO with 1.01 psrms integrated jitter in 65nm CMOS. In: IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), pp 248–250.

Van der Tang JD, Kasperkovitz D, Van Roermund A (2002) A 9.8–11.5-GHz quadrature ring oscillator for optical receivers. IEEE J Solid-state Circuits 37(3):438–442.

Danfeng C, Junyan R, Jingjing D, Wei L, Ning L (2009) A multiple-pass ring oscillator based dual-loop phase-locked loop. J Semiconductors 30(10):105014

Chen ZZ, Lee TC (2011) The design and analysis of dual-delay-path ring oscillators. IEEE Trans Circuits Syst I Regul Pap 58(3):470–478

Jangra V, Kumar M (2020) New low power differential VCO circuit designs with active load and IMOS varactor. AEU-International Journal of Electronics and Communications, 153191.

Kumar M (2018) Design of Linear Low-Power Voltage-Controlled Oscillator with I-MOS Varactor and Back-Gate Tuning. Circuits, Systems, and Signal Processing, pp 1–17. https://doi.org/10.1007/s00034-018-0748-1

Lee TH, Hajimiri A (2000) Oscillator phase noise: a tutorial. IEEE J Solid-State Circuits 35(3):326–336

Toh Y, McNeill JA (2003) Single-ended to differential converter for multiple-stage single-ended ring oscillators. IEEE J Solid-State Circuits 38(1):141–145

Kumar M, Dwivedi D (2018) A low power CMOS-based VCO design with I-MOS varactor tuning control. J Circuits Syst Comput 27(10):1850160

Karimi A, Ebrahimi E (2019) A new modified I-MOS varactor for linear range enhancement. Microelectron J 90:181–186

Andreani P, Mattisson S (2000). A 2.4-GHz CMOS monolithic VCO with an MOS varactor. Analog Integrated Circuits Signal Process 22(1):17–24.

Yang WR, Jiang WY (2007) A dual-path three-stage VCO with wide tuning range. In: 2007 7th International Conference on ASIC, pp 542–544.

Do MA, Zhao RY, Yeo KS, Ma JG (2003) New wideband/dualband CMOS LC voltage-controlled oscillator. IEE Proc Circuits Devices Syst 150(5):453–459

Eken YA, Uyemura JP (2004) A 5.9-GHz voltage-controlled ring oscillator in 0.18μm CMOS. IEEE J Solid-State Circuits 39(1):230–233.

Yan WST, Luong HC (2001) A 900-MHz CMOS low-phase-noise voltage-controlled ring scillator. IEEE Trans Circuits Systems II Analog Digital Signal Process 48(2):216–221

Fahs B, Ali-Ahmad WY, Gamand P (2009) A two-stage ring oscillator in 0.13 μm CMOS for UWB impulse radio. IEEE Trans Microw Theory Tech 57(5):1074–1082.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

On behalf of all authors, the corresponding author states that there is no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Dwivedi, D., Kumar, M. & Niranjan, V. Design of power-efficient CMOS based oscillator circuit with varactor tuning control. SN Appl. Sci. 3, 487 (2021). https://doi.org/10.1007/s42452-021-04501-y

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s42452-021-04501-y