Abstract

Introduction

In this study, a high-time-resolution electronic module with a high channel density and low power consumption was designed for the measurement of the multi-detector array positron annihilation lifetimes. This electronic module consisted of 32 input channels, and each channel provided a high sampling rate up to 5.12 GSPS based on a Domino Ring Sampler 4 (DRS4) chip. Compared to the high-speed flash analog-digital converter (FADC), DRS4 chip has a higher channel density with an affordable lower price and power consumption.

Methods

The developed electronic module was also capable of real-time data analysis for directly extracting the time information of input signals at the data acquisition site, thereby significantly decreasing the data rate. The digital constant fraction discriminator (DCFD) algorithm was implemented in the field programmable gate array (FPGA) for performing the time pick-up.

Results

The coincidence time resolution of the electronic module was measured, and the test results revealed a value of 26 ps. A prototypical 16-pixel detector module of the multi-detector system was evaluated using this electronic module, and the coincidence time resolution of the prototypical module was 411.84 ps.

Conclusions

The electronic module was confirmed to satisfy the severe requirements of the multi-array-detector positron annihilation lifetime measurement system. It was also suitable for other high-time-resolution, high-channel-density, cost-effective, and low-power-consumption applications.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

Introduction

The positron lifetime in a material is inversely proportional to its local electron density [1]. This is the elementary principle for the positron annihilation to investigate material microstructures. A slow positron beam can be used for measuring the positron annihilation lifetime spectrum (PALS), which can be used to investigate the material surface and interface structures [2]. Particularly, as a new probe, the slow positron beam is suitable for examining the irradiation damage of metals, ion-implantation damage defects, irradiation defects in semiconductors, and semiconductor interface defects [3,4,5]. In addition, this technique can be applied for the fundamental research of positron and positronium, including positron scattering, Bose–Einstein condensation, and positron microscopy [6,7,8,9].

In the traditional slow-positron-beam technique, a large number of gamma rays are produced after the positron burst annihilation. However, owing to the pile-up effect of the traditional nuclear detection technology, it cannot discriminate several gamma rays within an extremely short period. The collection of sufficient annihilation events is time-consuming for the purpose of obtaining comprehensive characteristic information on the positron annihilation in materials [10,11,12]. A successful measurement with sufficient statistic counts can be carried out in dozens of minutes or even several hours. To address this issue, an innovative multi-detector structure for PALS measurements was proposed [13], permitting the observation of dynamically changing processes of micro-defects in materials [13]. The multi-detector system exhibits broad applications in positron microscopy and high-density positron physics. In addition, it can serve as an extremely powerful research platform for the nondestructive testing of semiconductor thin-film materials.

However, the multi-detector array structure poses higher demands in terms of the data acquisition and processing electronics, i.e., high channel density, considerable data, rapid sampling rate, high time resolution, low cost, and low power consumption. Conventionally, time is measured by using discrimination circuits and time-to-digital conversion (TDC). TDC can provide a high channel density and good time resolution, but the discrimination circuits are slightly more complicated. In this study, because of the narrow space of the detector array (i.e., a hemisphere with a radius of 20 cm) and a high channel density (2048), sufficient available space is not available for the discrimination circuits in the front-end electronic site. To remedy these issues, a high-time-resolution multichannel electronic module was developed for the multi-detector array system in this study. This electronic module consisted of 32 channels in one printed circuit board (PCB), where each channel provided a sampling rate of up to 5.12 giga samples per second (GSPS) based on a DRS4 chip. The DCFD algorithm was implemented in the FPGA, and the time information of all of the 32 input pulses was obtained in real time at the data acquisition site in this module. In this study, the time resolution of this fast sampling electronic module was investigated, and a coincidence time resolution of 26 ps was obtained.

System structure and electronic module design

Multi-detector array structure and electronic requirements

In the slow-positron-beam technique, broad-energy-distribution positrons are first adjusted to monoenergetic positrons by moderation. After moderation, the positrons’ energies can be reduced to a few electron volts. Next, the moderated positrons are accelerated into the required monochromatic, low-energy positron beam [2]. The higher the positron beam energy, the deeper the penetration of the positrons into the samples [2]. Each slow positron beam comprises a large number of positrons (108−9 e+/s); these positrons exhibit the same energy; they are annihilated with electrons at a certain depth in the material. Thus, microstructures at different depths below the material’s surface are investigated by this technique. When the annihilation lifetimes of the positrons in a burst can be obtained, the slow-positron-beam technique can be employed to investigate the dynamically changing processes on a time scale of nanoseconds [13].

Emission angles of annihilation gamma photons are completely random, i.e., the annihilation gamma photons are uniformly distributed in a 4π stereo space [14]. Hence, in the multi-detector structure, a large number of detector cells are distributed on a sufficiently large spherical surface for gamma-ray detection [13]. In the preliminary plan, by considering the cost and detection efficiency, 2048 detector cells are used. Each detector cell is considered as an individual pixel, and the pulse from each pixel is transmitted to back-end electronic modules for sampling and processing (Fig. 1). The generation time of the positron burst and the time at which the annihilation photons are detected by the #i detector are set as the start time (T0) and stop time (Ti), respectively. Hence, (Ti − T0) corresponds to the positron annihilation lifetime [13]. The PALS of one positron burst can be obtained after the statistical analysis of all values. In theory, the measurement time of the PALS can be reduced from several hours to hundreds of nanoseconds [13]. In this manner, it is apt for the measurement of dynamically changing processes in a sample’s microstructure.

The time resolution of the entire multi-detector system is defined by Eq. (1), where τB is the time width of the positron burst, τS and τSi are the intrinsic time resolution of the scintillator and SiPM, respectively, τE is the time resolution of the electronic module, τP is the propagation time difference of the gamma photon, and τA is the time resolution of the detection array (the variability in time as different detector cells detect the same signal). From the analysis carried out in Ref. [13], the time resolution τ mainly depends on τB as well as τS and τSi. In this study, the detector cell comprises an LYSO scintillator and SiPM. Typically, the time resolution of the detector is a few hundred picoseconds. For not affecting the accuracy of timing measurements, the time resolution of the electronics was required to be greater than 30 ps. Hence, the sampling rate should be sufficiently high for acquiring sufficient information about the waveforms for better time resolution. Multichannel time measurement with a high time resolution is the key issue in this study. Considering the high time resolution, a large number of channels, a large amount of data, and power consumption, the main requirements for the electronic module are summarized below:

-

a.

A high channel density, where pulses from all 2048 pixels should be individually sampled;

-

b.

A high sampling rate that should be provided at an affordable cost and power consumption;

-

c.

Real-time data that can be analyzed to extract the time information at the data acquisition site to reduce the data rate;

-

d.

An optimum time resolution of < 30 ps for the electronic module due to the time resolution of LYSO scintillators, which is typically several hundreds of picoseconds.

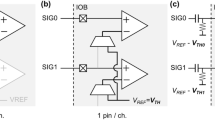

Design of the electronic module

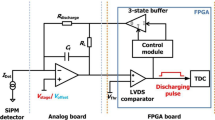

According to the system demands, a multichannel electronic module was developed (Fig. 2), comprising three parts, i.e., differential circuits, waveform sampling circuits (DRS4 and ADC), and the data process and control unit (FPGA), respectively. As shown in the functional block diagram (Fig. 3), the electronic module comprised two groups. Each group consisted of 16 input channels, and each channel exhibited one-to-one correspondence to the front-end detector cell. In addition, the module comprised eight reserved ex-trigger ports for the external reference trigger input. Each signal input port was AC coupled to an input range of 1 V peak-to-peak. Typically, rapid pulse sampling can provide the maximum time information of the particle that interacted with the detector. Hence, in this module, every signal is sampled at 5.12 GSPS, which is provided by DRS4. However, before sampling, every single-end signal had to be converted into differential signals to satisfy the requirement of the DRS4 input. The used amplifiers were completely differential amplifiers, with a bandwidth of 2 GHz, a gain of 2 V/V (6 dB), and an input voltage noise of ~ 2.3 \({\text{nV}}/\sqrt {\text{Hz}}\) (f > 10 MHz).

In conventional nuclear detection technology, the FADC is mainly used as the signal sampler. However, the conventional commercial high-speed FADC is not only expensive, but also exhibits a low channel density and extremely high power consumption (a few watts per channel). In some applications, DRS4 is an effective alternative to the high-speed FADC because it exhibits a rapid sampling frequency (0.7–5.12 GSPS), high channel density (8 + 1 channels per chip), and low power consumption (17.5 mW per channel @2GSPS) at an affordable cost [15]. Considering these factors, the DRS4 chips were finally selected as the signal sampler herein.

When a global trigger was met in FPGA, the DRS4 chip ceased sampling, and the content of the frozen sample cells was read out by read shift registers and digitized by using an external ADC at a low frequency (33 MHz). Two 16-channel ADCs were selected as the digitizer between DRS4 and FPGA. Multichannel ADC decreased the PCB area and power consumption. Each of the 16-channel ADCs corresponded to two DRS4 chips. For the further reduction of the power consumption, four single-channel ADCs with a smaller size and lower power consumption were used to connect to the multiplexed output of each DRS4, albeit at the expense of increasing the dead time. The dead time of DRS4 in the multiplex readout mode was eight times greater than that in the parallel readout mode [15]. The digitized waveforms were then sent into the FPGA via high-speed low-voltage differential signaling (LVDS) channels. The FPGA in this electronic module was responsible for analyzing real-time data, controlling the DRS4 sampling and readout process, configuring ADC, DAC, and DRS4, storing and transmitting data, and calibrating the DRS4 offset.

DRS4 offset calibration with FPGA

The DRS4 chip comprised a ring buffer, which was constructed as a chain of capacitors, with 1024 sample cells for each channel. The input signal was continuously fed into the capacitors. There were different offsets of 1024 sample cells to a certain DC input, which was related to the IC manufacturing process variations [15,16,17,18]. It exhibited a noise of ~ 10.5 mV (RMS) without calibration [Fig. 4 (left)]. For achieving high time resolution, the offset variations must be calibrated before data analysis in the FPGA. An online DC offset calibration method using the FPGA was implemented herein. In the offset calibration process, a high-precision (16-bit) DC voltage of 0 V generated by the onboard DAC was connected to all DRS4 inputs and sampled. The offset and gain voltage of each sample cell were examined in the FPGA and then stored in random-access memory (RAM) inside the FPGA. The entire process was completed in only several milliseconds. A RAM with a 12-bit width and 1024-bit data depth was deployed for each channel. The RAM address corresponded to the serial number of a sample cell from 0 to 1023. The offset was removed while simultaneously streaming the digitized waveform into the FPGA. After the offset calibration, the offset noise was decreased to ~ 0.4 mV (RMS); this value is slightly greater than 0.35 mV described in the DRS4 data sheet, but it is acceptable [Fig. 4 (right)] [15]. After offset calibration, the data were sent to the DCFD unit in the FPGA.

Real-time digital constant fraction discriminator

The DCFD algorithm was implemented in the FPGA. The constant fraction discriminator (CFD) is widely used in time-of-flight measurements. CFD was reported to exhibit high time resolution [19,20,21]. CFD exhibits an advantage of almost eliminating the effect of signal amplitude variation. It is triggered at a constant fraction of the signal height independent of the signal amplitude. In the DCFD algorithm, the input signal was passed through two parallel routes—attenuated and delayed (Fig. 5)—to determine the timing point. In the attenuated route, the input signal was attenuated by a coefficient K (using shift registers). In the delayed route, the input signal was added by the time delay D (using FIFOs), but without any amplitude change. The crossing point of the attenuated and delayed signals corresponded to the arrival time of the original input signal (Figs. 5, 6).

It had a maximal probability that the zero-crossing points were located at the intervals between two adjacent sampling cells as shown in Fig. 6. The two equations, Eqs. (2) and (3), were introduced to estimate the exact location of zero-crossing point.

where \(\Delta T_{n}\) is the time interval between the sample cell[n] and [n + 1], which equals to the sum of t1 and t2. Based on the similar triangle theory, the ratio of t1 to t2 equals to that of h1 to h2 (Fig. 6). h1 and h2 correspond to the amplitude differences between the delayed and attenuated signals at the sampling cell[n] and [n + 1], respectively. The zero-crossing point location was converted to be determined by the ratio between h1 and h2. Notably, the ratio between h1 and h2 can be easily calculated by using FPGA. By using this method, a time resolution of sub-30 ps for DCFD using FPGA was attained, which was quite acceptable for the multi-detector system.

Experimental results

In this study, the real-time DCFD algorithm was first validated. The time resolution of this electronic module was measured. In the measurement process, a 50-ns-long pulse, which was generated by a high-precision signal generator, was used as the standard reference signal. Before transmission to the electronic module, this pulse was split into two pulses by a standard T-junction. Then, these two pulses can be regarded as the same signals. These two pulses were sampled at 5.12 GSPS. After sampling, digitization, and calibration, these two pulses were sent into the DCFD unit in the FPGA. The arrival time of each pulse was extracted and then transmitted to the back-end computer for statistical analysis. The time difference distribution plotted in Fig. 7 was fitted with a Gaussian function. The full-width at half-maximum (FWHM) of the fit was used as the time resolution. A coincidence time resolution of 26 ps was attained. In some polymer organic materials that exhibit a low electron density, the positron lifetimes extended to several nanoseconds or tens of nanoseconds. Hence, in such circumstances, the time resolution contribution from the electronic module can be neglected. During the experiments, the two factors K and D can considerably affect the time resolution. Hence, an interface for the parameter adjustment is developed in the FPGA; for this purpose, experimenters can use a software to adjust the parameters for obtaining a better time resolution in real time.

Then, the prototypical detector module was investigated by this electronic module. The prototypical detector comprised 4 × 4 pixels, and each pixel was based on a silicon photomultiplier tube (SiPM), which was coupled to the LYSO scintillator. All pixels were separately read out and then transmitted into the electronic module for sampling and processing. A 22Na source was used to evaluate the coincidence time resolution of the prototypical detector. Figure 8 shows the entire experiment design. Figure 9 shows the waveform output from the SiPM, and the leading and falling edges of the waveform were ~ 2 ns and ~ 20 ns, respectively. The signal output from a standard detector, comprising a BaF2 crystal and a photomultiplier tube (PMT), was set as the start time. An FWHM of 411.84 ps (selected gamma photons of 511 keV) was obtained (Fig. 10). Experimental results revealed that the electronic module is capable of multichannel time measurements, and it is suitable for the multi-detector positron lifetime system.

Discussion and conclusions

A high-time-resolution multichannel electronic module was designed for the measurement of the positron lifetime by using a multi-detector. This electronic module was based on a DRS4 chip, which provided a sampling rate of up to 5.12 GSPS with affordable cost and power consumption. In this study, an online DRS4 calibration method and a real-time DCFD algorithm were implemented in the FPGA. The arrival time of each signal was directly extracted in the data acquisition site, thereby considerably decreasing the data rate. The test results revealed a time resolution of 26 ps for the electronic module. A prototypical detector with 4 × 4 pixels was developed and tested with this electronic module. The electronic module was confirmed to satisfy the severe requirements of the multi-detector system, e.g., high time resolution, high channel density, low cost and power consumption, and high data rate.

However, few drawbacks exist in the electronic module. Differential circuits occupied a large area in the PCB board, which also exhibited high power consumption (Fig. 2). To further improve the channel density and decrease the power consumption of this electronic module, the differential circuits should be transferred to the front-end electronics site in the detectors. Second, in the experiments, the whole system permitted a long dead time. The minimum time interval between the two consecutive positron bursts was 30 ms; however, in the multiplex readout mode, the entire signal process only took ~ 300 µs; this time is considerably less than the permissible dead time; hence, the one-channel ADC can be retained only as the digitizer. Moreover, the cost and power consumption of the one-channel ADC were less than those of the 16-channel ADC.

References

P.A.M. Dirac, On the annihilation of electrons and protons. Math. Proc. Camb. Philos. Soc. 26(3), 15 (1930)

A. Vehanen, K. Saarinen, P. Hautojärvi, H. Huomo, Profiling multilayer structures with monoenergetic positrons. Phys. Rev. B Condens. Matter 35(10), 4606–4610 (1987)

S.J. Smith, G.M.A. Hyder, W.E. Kauppila, C.K. Kwan, T.S. Stein, Evidence for absorption effects in positron elastic scattering by argon. Phys. Rev. Lett. 64(11), 1227–1230 (1990)

R.G. Greaves, M.D. Tinkle, C.M. Surko, Creation and uses of positron plasmas. Phys. Plasmas 1(5), 1439–1446 (1994)

B.L. Brown, M. Leventhal, A.P.J. Mills, D.W. Gidley, Positron annihilation in a simulated low-density galactic environment. Phys. Rev. Lett. 53(24), 2347–2350 (1984)

S.Y. Tong, H. Huang,. Guo, Low-energy electron and low-energy positron holography. Phys. Rev. Lett. 69(25), 3654–3657 (1992)

A. Weiss, R. Mayer, M. Jibaly, C. Lei, D. Mehl, K.G. Lynn, Auger-electron emission resulting from the annihilation of core electrons with low-energy positrons. Phys. Rev. Lett. 61(19), 2245–2248 (1988)

H.K.M. Tanaka, T. Kurihara, A.P.J. Mills, Positronium time of flight measurements of an open-pored spin-on low-k mesoporous film. J. Phys. Condens. Matter 18(37), 8581 (2006)

A. Zecca, R.S. Brusa, M.P. Duartenaia, G.P. Karwasz, J. Paridaens, A. Piazza, A pulsed positron microbeam. Europhys. Lett. 29(8), 617 (1995)

J. Liu, D. Li, Z. Zhang, B. Wang, T. Zhang, J. Hao, Using a LaBr 3: Ce scintillator for positron annihilation lifetime spectroscopy. Chin. Phys. C 36(4), 380–383 (2012)

L. Daowu, L. Junhui, Z. Zhiming, W. Baoyi, Z. Tianbao, W. Long, A compact positron annihilation lifetime spectrometer. Chin. Phys. C 35(1), 100–103 (2011)

L. Wei, Z.M. Zhang, C.X. Ma, C.L. Zhou, B.Y. Wang, T.B. Chang, A high-resolution BaF2 positron lifetime spectrometer with high counting rate. Mater. Sci. Forum 445–446(1), 516–518 (2004)

B.Y. Wang, P. Kuang, F.Y. Liu, Z.J. Han, X.Z. Cao, P. Zhang, Measurement of positron annihilation lifetimes for positron burst by multi-detector array. Nucl. Instrum. Methods Phys. Res. Sect. A 885, 119–123 (2018)

O. Klemperer, On the annihilation radiation of the positron. Math. Proc. Camb. Philos. Soc. 30(3), 347–354 (1934)

DRS4 datasheet rev. 0.9. https://www.psi.ch/drs/DocumentationEN/DRS4_rev09.pdf

M. Bitossi, R. Paoletti, D. Tescaro, Ultra-fast sampling and data acquisition using the DRS4 waveform digitizer. IEEE Trans. Nucl. Sci. 63, 2309–2316 (2016)

J. Wang, L. Zhao, C. Feng, S. Liu, Q. An, Evaluation of a fast pulse sampling module with switched-capacitor arrays. IEEE Trans. Nucl. Sci. 59(5), 2435–2443 (2012)

DRS4 Evaluation Board Rev. 5.1 manual. https://www.psi.ch/drs/DocumentationEN/manual_rev51.pdf

D.A. Gedcke, W.J. Mcdonald, A constant fraction of pulse height trigger for optimum time resolution. Nucl. Instrum. Methods 55(2), 377–380 (1967)

D.A. Gedcke, W.J. Mcdonald, Design of the constant fraction of pulse height trigger for optimum time resolution. Nucl. Instrum. Methods 58(2), 253–260 (1968)

A. Fallu-Labruyere, H. Tan, W. Hennig, W.K. Warburton, Time resolution studies using digital constant fraction discrimination. Nucl. Instrum. Methods Phys. Res. A 579(1), 247–251 (2007)

Acknowledgements

This work was supported in part by the National Natural Science Foundation of China (Grant Nos. 11475206, 11675191 and 11475197).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Cai, J., Li, D., Wang, Y. et al. Design of a high-sampling-rate electronic module for array-detector positron annihilation lifetime measurements. Radiat Detect Technol Methods 3, 33 (2019). https://doi.org/10.1007/s41605-019-0108-0

Received:

Revised:

Accepted:

Published:

DOI: https://doi.org/10.1007/s41605-019-0108-0