Abstract

Copper Zinc Tin Sulfide (CZTS) is a well-known kesterite material having a variety of optoelectronic applications. The constituent elements are earth abundant and non-toxic in nature. This investigation presents the bipolar switching characteristics of FTO/CZTS/Ag devices for resistive memory-switching applications. The material is deposited by spray pyrolysis method at a substrate temperature of 375 °C. The structural analysis shows the crystalline nature of the films. FESEM image reveals coral-like morphology. A resistive memory-switching device is fabricated with a structure of < FTO/CZTS/Ag>. The observed HRS/LRS resistance ratio of ~ 33 suggests that the device possesses good memory-switching properties. The formation and rupture of the conductive filaments of the FTO/CZTS/Ag memory device were observed. This confirms that CZTS material can be used as the switching layer to fabricate a simple, cost-effective, and non-toxic bipolar device, which can deliver the perfect switching characteristics.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Cu2ZnSnS4 (CZTS) quaternary semiconducting material is turning out to be a promising compound in the field of renewable energy production and many other energy-related applications. CZTS thin films are used extensively in photovoltaic devices [1], water splitting applications [2], and photodetectors [3]. This material is also found in applications such as memory-switching devices, which is still an unexplored area of research. Resistance random access memory (RRAM) has been considered a potential candidate for future memory technology due to the larger time interval taken to switch between a high-resistance state (HRS) and a low-resistance state (LRS) when subjected to proper bias voltages with various directions of scan [4]. Presently, a different category of compounds is explored for RRAM applications, which includes binary metal oxides, like CuxO, ZnO, NiO, and MoO3 [5,6,7]. These binary oxide compounds produce good switching and endurance characteristics due to their structural properties. In metal oxides, the oxygen (O2) vacancies play a vital role in the formation and rupture of conductive filaments. The role of p-type semiconductor materials in optoelectronic applications such as photodiodes, detectors, and memory devices are also a major area of study [8, 9]. p-type chalcogenide compounds are relatively new category of materials that has potential memory-switching applications [10]. Among chalcogenide compounds, there are ternary as well as quaternary compounds, which possess memory-switching properties [11, 12]. CZS, CFTS, CuInS2, and CZTS are well-known chalcogenide materials used for memory-switching applications [13,14,15]. Among these materials, CZTS has good electrical and optical properties, which gains much attention in the field of memory-switching and RRAM devices.

The actual challenge here is the implementation of higher storage capacity and density, quicker writing and reading speed, and minimal energy utilization. The resistive switching (RS) can be explained using one or more mechanisms, namely the evolution of the conduction mechanism (CM), formation of conductive filament (CF), and dynamic variation of temperature [5, 11, 16]. In CF evolution, the mechanism involves ion migration, electrical, and thermal properties [17]. The mechanism of conduction contains different modes, such as Schottky emission [18], space-charge-limited conduction mechanism (SCLC), trap-assisted tunneling [12, 19], and hopping conduction [20]. The electrical bi-stability phenomenon is a remarkable step to understand the underlying phenomenon of photovoltaic materials [15]. There are only a few reports on the resistive switching properties of CZTS [5, 16, 21].

In the present work, we investigate the electrical bi-stability of earth-abundant and non-toxic CZTS thin-film memory-switching devices without using usual metal oxide materials for the active layer. The deposition is done by spray pyrolysis technique. The advantage of this technique is the high-level uniformity, on par with the film deposition by physical methods. This article reports the fabrication of a memory-switching device with the structure of < FTO/ Cu2ZnSnS4/Ag > with CZTS as the active layer and FTO as the base contact layer. A systematic investigation of the preparation of Cu2ZnSnS4 films, device fabrication, and characterization are reported in this article.

2 Experimental

2.1 Preparation of CZTS thin films

Copper Zinc Tin Sulfide (CZTS) thin films were prepared by chemical spray pyrolysis technique. The precursor solution was prepared by mixing 0.04 molar (M) cupric chloride (CuCl2·2H2O > 98.5%, Merck), 0.02 M of zinc chloride (ZnCl2·2H2O > 95%, Merck), 0.02-M stannic chloride (SnCl4·5H2O, 98%, Merck), and 0.2-M thiourea (SC(NH2)2, 99%, Merck) in 100-ml double distilled water. The solution was sprayed onto the cleaned substrate mounted inside the spray chamber on a PID-controlled heater. Airflow for spray has been precisely monitored at an optimal value of 2.5 bar to obtain a steady solution spray rate. The flow rate of the precursor is fixed at 6 mL per minute. In order to find out the optimum deposition temperature, the initial depositions were carried on soda lime glass substrates. After the initial trials, the device fabrication was carried out on FTO glass substrates at optimum temperature of 375 °C.

2.2 Fabrication of FTO/CZTS/Ag memory device

CZTS films were deposited by spray pyrolysis technique on cleaned FTO glass slides. Some portion of the substrate was masked for taking the bottom contact. The deposition temperature was optimized at 375 °C by multiple trials. The silver top contact of the devices was prepared using conductive silver paste. The silver conductive adhesive paste (Alfa Aesar) was prepared by diluting it with iso amyl acetate (96%, Qualigens) in a petri dish. The prepared silver paste was then applied onto the top surface of the deposited FTO/CZTS device. The coated silver (Ag) contact area is approximately 1 mm2. The whole device was dried for 1 h at 80 °C in a hot air oven.

2.3 Characterization

Structural studies of CZTS thin films were carried out using GIXRD (RIGAKU Ultima Smart Lab with CuKα radiation of λ = 1.5406 Å). Raman measurements were done using Horiba Lab-RAM Spectrometer with Nd-YAG laser of wavelength 532 nm as the primary source. The scan was performed in the range of 50–800 cm−1 with a 3-mW diode laser. The surface morphology of the deposited films was obtained using HR-FESEM, ZEISS Ultra 55. The elemental composition of CZTS thin films was obtained from EDS measurements. I–V measurements and electrical bi-stability studies were carried out with the help of Keysight-B2901A Source Measure Unit (SMU).

3 Results and discussion

3.1 Structural properties

Figure 1 illustrates the XRD spectra of the spray-deposited CZTS thin films at a substrate temperature of 375 °C. The presence of the dominant peak corresponding to the (112) plane along with (220) and (312) peaks corresponds to the tetragonal kesterite phase of CZTS (JCPDS card No: 26–0575) [22]. The XRD pattern shows good crystallinity for the as-deposited samples.

3.2 Raman analysis

Figure 2 shows the Raman spectra of the as-deposited CZTS thin films. From the intensity versus Raman shift pattern, a single high-intensity peak observed at 331 cm−1 corresponds to the kesterite phase of CZTS thin films [23]. The absence of any other Raman peaks indicates that there is no Cu migration and Cu–S formation due to volatile Sulfur evaporation during the spray pyrolysis process [24]. Thus, the XRD and Raman analysis have confirmed the formation of single-phase kesterite CZTS thin films by the spray pyrolysis technique.

3.3 Morphological analysis

FESEM morphology shows (Fig. 3a) uniform distribution of grains on the surface of CZTS thin films without any visible cracks or pores. The formation of the compound on the film surface described as nano-coral-like morphology with tiny bulges and troughs. The average thickness of the as-deposited CZTS layer is in the range of 1 μm, which is obtained from the cross-sectional FESEM measurement (Fig. 3b). The atomic percentage of the constituent elements is obtained from the EDAX spectrum and shown in the inset of Fig. 3c. The EDAX data corroborate the formation of stoichiometric Cu2ZnSnS4 compound by the spray pyrolysis technique.

3.4 Resistive switching characteristics of FTO/CZTS/Ag memory devices

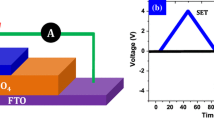

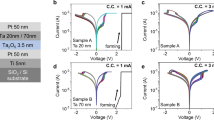

CZTS-based memory devices were characterized using I–V measurements. Figure 4a and c describes the schematic diagram of the fabricated memory device and the log(|I|)−V characteristics of the device in positive and negative bias regions. A photograph of the device is shown in Fig. 4b. Figure 4d depicts the pinched hysteresis current–voltage (I–V) loops of the FTO/CZTS/Ag resistive switching device. The device exhibits resistive switching properties by sweeping − 3 V to + 3 V with additional supply of forming voltage. The hysteresis loop of the fabricated device is a characteristic property of memristors [13].

CZTS-based memory devices with FTO substrates show a non-uniform switching loop area in both the positive bias as well as negative bias regions. The perceived variations in positive and negative loop areas arise because of the appearance of different defects, such as ionic and interstitial in the active layers of CZTS [5]. The current compliance set at an optimum value of 30 mA to avoid high current flow through the device, which can permanently rupture the films. This ensures the safety of the device. From Fig. 4c, it can be seen that the direction of forward and reverse characteristics is not following the same path. This shows the bi-stability of the device under the bias voltage. Initially, the device is in a low conducting state. The positive and negative peak voltages are referred to as SET and RESET, respectively. When the external bias voltage was supplied to the fabricated device ranging from − 3 V to + 3 V, the current traces nearly the same path. When the voltage reaches a point of about ~ 1.1 V, a sudden increase in current value occurs and reaches a point of about 100 mA at 3 V. From this high conducting state (or SET state), the current traverses a different path, where the current decreases proportional to the reverse voltage up to − 2 V. At − 2 V, there is an abrupt increase in the current value showing the writing process (or RESET). Voltage applied from + 3 V to − 3 V, an abrupt flow of high current happens in the device with a positive peak voltage. In this situation, the device considered to be in a low-resistance state (LRS) or ON state. This LRS state happens throughout the region and passing along origin. After the voltage changes from − 3 V to + 3 V, a sudden small current passes into the device at a negative peak voltage. This particular state is termed as high-resistance state (HRS) or the device is said to be in OFF state [15].

Figure 5 shows the endurance characteristics, which depicts the resistance versus number of cycles of FTO/CZTS/Ag resistive switching device. Both the cycles (SET to RESET and RESET to SET) have been repeated 100 times for the fabricated device. The device does not show much variation in their LRS and HRS even after several number of cycles. As a result, the reported resistive switching properties for the fabricated CZTS-based memory devices show excellent repeatability and reliability.

The ION/IOFF ratio obtained for the FTO/CZTS/Ag memory device was found to have a higher value with ROFF/RON ratio about 33 times, which is much higher than the reported value [11]. To understand the conduction mechanism of resistive switching devices, the I–V curves were plotted in double logarithmic coordinates to evaluate by linear fitting. Figure 6a and b shows the double logarithmic characteristics of the FTO/CZTS/Ag device for positive bias as well as negative bias.

Electrical conduction mechanism plays a very important role in the functioning of resistive memory-switching devices. The conduction mechanisms in memory devices are categorized mainly into three types. Type I conduction mechanism is defined as ohmic conduction (OC) where the slope value of the fitted curve is approximately equal to unity. At this region, the current is linearly proportional to the applied voltage (I ∝ V) [25]. The major cause of ohmic conduction is thermally generated carriers. Type II is the space-charge-limited conduction (SCLC) where the slope value of the fitted curve is approximately 2. The current in this region is proportional to the square of the voltage (I ∝ V2) which is recognized as Child’s law [26]. When the electric field is increased, the injected carrier concentration exceeds the concentration of thermally generated carriers and the injected carriers fill the traps, which cause excess charges to accumulate in the active layer. Type III is the trapped charge-limited current (TCLC) mechanism [27]. In this case, the slope value becomes greater than 2 (I ∝ Vn, n > 2). When the applied electric field increases, the current increases abruptly. The traps are occupied with injected carriers immediately and the Fermi level reaches the conduction band [28]. Figure 6a shows the double logarithmic graph of the positive bias region. There are three slopes observed in the HRS stage and a single slope observed in the LRS stage of the region. The slopes in the HRS region corresponding to positive bias have values of 10.77, 2.81, and 1.49, which relates to TCLC conduction mechanism for the first two and SCLC for the last one. In LRS state, the slope value is 1.59, which indicates the child’s law mechanism. In the negative bias region shown in Fig. 6b, the HRS and LRS values are approximately equal to one, which indicates the typical Ohm’s law mechanism for the regions. Figure 7 represents the fitted data of the positive and negative bias correlating the conduction mechanisms present in FTO/CZTS/Ag memory devices.

Figure 8 gives the band diagram showing the Fermi level and the band orientation of the FTO/CZTS/Ag device. The work function observed for the p-type CZTS is 4.75 eV, which is greater than Ag (4.35 eV) and FTO (4.4 eV) electrodes [29, 30]. Therefore, by evaluating the typical structure of metal–semiconductor–metal contact, a Schottky barrier observed at Ag/CZTS and CZTS/FTO boundaries and formed electric fields are along the direction from Ag and FTO through CZTS.

Figure 9 represents the various stages of the conductive filament formation and rupture in the FTO/CZTS/Ag memory devices. In general, a memory device has three layers in which there are metal contacts/electrodes on top and bottom and an active layer having high absorption coefficient and conductivity sandwiched in between them. If a bias voltage is applied across the electrodes, the electrical conductivity changes reversibly and can be carried through a long time between a high conductive (ON) state and a high resistive (OFF) state.

After applying a reverse voltage on the Ag metal contact, the narrowing of the depletion region takes place since the external electric field is in the opposite direction. This reduces the built-in electric field of the Ag/CZTS junction. This effect shows a low-resistance behavior. On the other hand, the depletion region is extended in the similar direction along with the external field direction and the built-in electric field of the FTO/CZTS junction shows high-resistance behavior. While supplying forward bias to the Ag electrode, the depletion region of the Ag/CZTS contact shows higher resistance until a certain value of the voltage is reached. In CZTS thin films, Cu2+ is having higher mobility [5, 28]. Therefore, if a positive bias voltage is applied on Ag metal contact, Cu2+ ions starts to drift toward FTO contact creating a reduction in copper concentration at CZTS/Ag contact. In the schematic, the hysteresis I–V loop is divided into 4 sections. In the first section (Fig. 8a), the depletion region of CZTS/Ag junction is in a high-resistance state. From this point, the Cu2+ ions drift toward the Ag electrode together with gradual increment in reverse voltage on Ag and steadily the Cu filaments starts forming. Here, the conversion from HRS to LRS occurs. This process is termed as the SET process. In the second section (Fig. 8b), the domination of Cu filaments over conductivity occur and device changes to LRS. In third section (Fig. 8c), after applying the forward bias voltage on Ag contact, the depletion region of the Ag/CZTS contact spreads, which allows the drifting motion of Cu2+ ions toward FTO contact. On further increasing the forward voltage, there is a breakage/rupture of the Cu filaments at particular voltage, which happens owing to Joule heating [16, 31] and device is in a RESET state. Finally, in the fourth section (Fig. 8d), the conductive filaments starts to vanish and the transfer of space charge starts to take over the conductivity. The device continues to be in HRS and the filaments totally ruptured. In quaternary films like CZTS, the electron traps come from the defects due to different types of vacancies, gaps in semiconductors, lattice mismatch, etc. These traps can capture the electrons and thus the conductivity is produced in the material [15]. In the present case the active layer material CZTS has abundance of Cu2+ ions. More number of vacancies are created, with the increase of Cu2+ ions, when the bias voltage is applied. These defects can act as traps to capture and recapture the electrons, which contribute to the formation of Cu conductive filaments. Moreover, additional defects are also generated at Ag/CZTS and CZTS/FTO interfaces due to the formation of ions (Ag+, Cu2+) under applied bias voltage. Low electronegativity and high mobility of copper ions are also a factor affecting the formation of copper conductive filaments in the device [5]. This mechanism shows that the CZTS thin films can be used as active layer in RRAM devices.

A comparison of the present work in the light of the reported memory-switching devices containing different types of active layers and back contacts is listed in Table 1. The table describes various deposition techniques for the fabrication of memory-switching devices and their endurance characteristics. The mainstream compounds for active layer of the memory-switching devices are metal oxides, like CuO, ZnO, NiO, and TiO2. There are various device architectures including single- and double-layered active layers. Liu et al. reported the fabrication of a bilayer structure containing TiO2 and ZrO2 as active layers using spin coating method [12]. They have observed a high ION/OFF ratio of 100. In the case of single metal oxide devices, a high ION/OFF ratio of ~ 103 was reported by Lee et al. [32]. The active layer is Ta2O5 prepared by radio frequency magnetron sputtering, using Ta as top electrode and Pt as bottom electrode. A relatively cheaper method has been employed by Dong et al. for the production of chalcogenide memristors [5]. The ION/OFF ratio of 27.5 was archived in the device with a structure of Al/CZTSSe/Mo fabricated by spin coating technique.

In the present work, it is able to achieve a higher ION/OFF ratio of 33 in chalcogenide-based memory-switching device fabricated by spray pyrolysis technique. This value is higher than most of the reported values, especially with metal oxide-based memristors. Adding to it, the process of deposition is relatively simpler and cost effective compare to the high vacuum deposition methods, like magnetron sputtering and DC sputtering [32, 33]. Hence, from the present investigation, it is clear that CZTS thin film-based memristor devices have the potential to compete with mainstream metal oxide-based switching devices.

4 Conclusion

CZTS thin films have been prepared by low-cost spray pyrolysis technique and the electrical bi-stability of the device FTO/CZTS/Ag was studied. The device showed good electrical bi-stability, with switching from low conducting state to a high conducting state. The highly responsive device shows good endurance characteristics with ROFF/RON ratio of 33. Double logarithmic graphs were plotted to study the conduction mechanism and the model has been developed to explain the memory-switching properties of the fabricated devices. With high rate of Cu2+ ion migration and filament formation under low bias voltage, the FTO/CZTS/Ag device has good electrical bi-stability and hence the CZTS thin films can be used as an active layer in memory-switching devices.

Data availability

All data generated or analyzed during this study are included in this manuscript.

References

S.B. Patel, J.V. Gohel, J. Mater. Sci. Mater. Electron. 29, 18151 (2018)

V. Mahalakshmi, D. Venugopal, K. Ramachandran, R. Ramesh, J. Mater. Sci. Mater. Electron. 33, 8493 (2022)

O.P. Singh, A. Sharma, K.S. Gour, S. Husale, V.N. Singh, Sol. Energy Mater. Sol. Cells 157, 28 (2016)

N.S. Sterin, T. Nivedya, S.S. Mal, P.P. Das, J. Mater. Sci. Mater. Electron. 33, 2101 (2022)

X.F. Dong, Y. Zhao, T.T. Zheng, X. Li, C.W. Wang, W.M. Li, Y. Shao, Y. Li, J. Phys. Chem. C 125, 923 (2021)

A. Rasool, R. Amiruddin, S. Kossar, M.S. Kumar, J. Mater. Sci. Mater. Electron. 33, 2090 (2022)

A. Rasool, R. Amiruddin, I.R. Mohamed, M.C.S. Kumar, Superlattices Microstruct. 147, 106682 (2020)

Y. Chen, L. Su, M. Jiang, X. Fang, J. Mater. Sci. Technol. 105, 259 (2022)

T. Yan, S. Cai, Z. Hu, Z. Li, X. Fang, J. Phys. Chem. Lett. 12, 9912 (2021)

T. Yanagida, K. Nagashima, K. Oka, M. Kanai, A. Klamchuen, B.H. Park, T. Kawai, Sci. Rep. 3, 1 (2013)

N. Ciocchini, M. Laudato, M. Boniardi, E. Varesi, P. Fantini, A.L. Lacaita, D. Ielmini, Sci. Rep. 6, 1 (2016)

H.C. Liu, X.G. Tang, Q.X. Liu, Y.P. Jiang, W.H. Li, XBin Guo, Z.H. Tang, Ceram. Int. 46, 21196 (2020)

S. Bera, A.K. Katiyar, A.K. Sinha, S.P. Mondal, S.K. Ray, Mater. Des. 101, 197 (2016)

Z. Hu, F. Cao, T. Yan, L. Su, X. Fang, J. Mater. Chem. C 11, 244 (2022)

S.P. Madhusudanan, K. Mohanta, S.K. Batabyal, J. Solid State Electrochem. 23, 1307 (2019)

G. Rajesh, N. Muthukumarasamy, S. Agilan, D. Velauthapillai, K. Mohanta, S.K. Batabyal, Mater. Lett. 220, 285 (2018)

S. Brivio, G. Tallarida, E. Cianci, S. Spiga, Nanotechnology 25, 385705 (2014)

K.H. Chen, T.M. Tsai, C.M. Cheng, S.J. Huang, K.C. Chang, S.P. Liang, T.F. Young, Materials (Basel). 11, 43 (2017)

J. Racko, J. Pecháček, M. Mikolášek, P. Benko, A. Grmanová, L. Harmatha, J. Breza, Radioengineering 22, 240 (2013)

K.H. Chen, C.M. Cheng, C.Y. Li, S.J. Huang, Microelectron. Reliab. 91, 330 (2018)

S. Yiğit Gezgin, H. Kılıç, Optik (Stuttg) 182, 356 (2019)

S.A. Khalate, R.S. Kate, J.H. Kim, S.M. Pawar, R.J. Deokate, Superlattices Microstruct. 103, 335 (2017)

K. Diwate, K. Mohite, M. Shinde, S. Rondiya, A. Pawbake, A. Date, H. Pathan, S. Jadkar, Energy Procedia 110, 180 (2017)

P. Aabel, M.C. Santhosh Kumar, Int. J. Energy Res. 44, 7778 (2020)

P.K. Sarswat, Y.R. Smith, M.L. Free, M. Misra, ECS J. Solid State Sci. Technol. 4, Q83 (2015)

A. Shariffar, H. Salman, T.A. Siddique, W. Gebril, M.O. Manasreh, Micro Nano Lett. 15, 853 (2020)

J.M. Montero, J. Bisquert, G. Garcia-Belmonte, E.M. Barea, H.J. Bolink, Org. Electron. 10, 305 (2009)

N. Bitri, S. Mahjoubi, M. Abaab, I. Ly, Mater. Lett. 219, 194 (2018)

M. Uda, A. Nakamura, T. Yamamoto, J. Electron Spectros. Relat. Phenomena 91, 643 (1998)

R. Jaramillo, S. Ramanathan, Sol. Energy Mater. Sol. Cells 95, 602 (2011)

A. Rasool, R. Amiruddin, S. Kossar, M.C. Santhosh Kumar, J. Appl. Phys. 128, 044503 (2020)

A.R. Lee, Y.C. Bae, G.H. Baek, J.B. Chung, S.H. Lee, H.S. Im, J.P. Hong, J. Mater. Chem. C 4, 823 (2015)

F. Gul, H. Efeoglu, Superlattices Microstruct. 101, 172 (2017)

X. Chen, H. Zhou, G. Wu, D. Bao, Appl. Phys. A Mater. Sci. Process. 104, 477 (2011)

S. Zou, P. Xu, M.C. Hamilton, Electron. Lett. 49, 829 (2013)

Funding

The authors declare that no funds, grants, or other supports were received during the preparation of this manuscript.

Author information

Authors and Affiliations

Contributions

PA contributed to conceptualization, methodology, investigation, formal analysis, and writing of the original draft. SSGS contributed to investigation, RA contributed to investigation, MCSK contributed to supervision, conceptualization, resources, and writing, reviewing, & editing of the manuscript. All authors read and approved the final manuscript.

Corresponding author

Ethics declarations

Conflict of interest

The authors have no relevant financial or non-financial interests to disclose.

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Aabel, P., Sai Guru Srinivasan, S., Amiruddin, R. et al. Bi-polar switching properties of FTO/CZTS/Ag device. J Mater Sci: Mater Electron 34, 601 (2023). https://doi.org/10.1007/s10854-023-10011-x

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s10854-023-10011-x