Abstract

Nanomagnetic logic is a recent technology used in electronic devices and systems. The current challenge in circuit miniaturization has prompted a move away from the traditional metal-oxide-semiconductor technology. Nanomagnetic logic-based devices have no leakage current, and they are also non-volatile. In this paper, we propose run-time reconfigurable layout designs for the logic gates, and to show the applicability of the logic gates, we implement a single-bit comparator design. For the logic gate designs, we use slant-edge nanomagnets of different shapes as inputs. The proposed layout designs are verified using the MuMax3 micro-magnetic simulation tool, and results are compared with a previous approach. The implementation of a single-bit comparator design can significantly reduce the number of nanodots required, typically by \(\sim\)50–80%, as well as the area occupancy, which can be reduced by \(\sim\)56–99%.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The miniaturization of CMOS devices is demanding, and the difficulty level for the investigation increases gradually with respect to physical size constraints, high power consumption, leakage current, expensive lithography costs, and the negative impact of short-channel effects [1]. Quantum dot cellular automata (QCA) and magnetic quantum dot cellular automata (MQCA) are two promising contenders for alternative computing paradigms to overcome these drawbacks. QCA technology requires low temperature for operation, whereas MQCA works at room temperature [2]. This new technology follows new approaches for both design and computation. In MQCA, quantum mechanical interaction is spin-based, and the nanomagnets work like tiny bar magnets. In nanomagnet-based designs, information is not transmitted from one place to another in electronic form. Instead, it is transmitted directly through magnetic attraction and repulsion, reversing the polarity of the north and south poles as they move from one magnet to another. This is almost equivalent to a NOT gate inverting the logic state slightly [3]. The nanomagnetic devices use two types of coupling, ferromagnetic and antiferromagnetic. With the help of this coupling concept, MQCA-based logic functionalities were verified after simulation studies [4,5,6]. A MQCA-based majority logic gate was first implemented by Imre et al. [7]. Subsequently, clocking structures and power analysis for nanomagnetic logic (NML) devices were shown by Niemier et al. [8]. After the demonstration of on-chip clocking, MQCA technology has become advantageous [9]. Alam et al. developed a CMOS-compatible clock and used it to evaluate all the NML constructs needed for a functionally complete logic set. They ensured that all possible input combinations to these constructs were considered during experiments. Furthermore, they designed the architecture to promote unidirectional data flow. Thus, NML is a promising contender for the latest computing paradigms as it consumes low power, and is non-volatile in nature. NML has the potential to operate at very high speed and has high integration density, making NML favorable for dense computing architectures. It is more reliable in high-radiation environments such as space exploration or certain medical applications.

To date, most of the researchers used the majority gate concept for the implementation of universal gates and basic gates. MQCA-based majority gates are investigated using driver magnets [7] and slant edge magnets [10] and they use ferromagnetic and antiferromagnetic wire architectures. Conventional majority gate designs relied on multiple nanomagnets and required significant area. In nanomagnet-based logic design, there has been a consistent emphasis on using a minimal number of nanomagnets, occupying the smallest area possible, and completing operations in the least amount of time [11]. With this in mind, we have introduced a groundbreaking area and energy-efficient comparator design using the non-majority logic gates as demonstrated in Fig. 1.

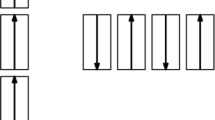

a Single-bit comparator schematic design using non-majority logic gates. Layout design of logic gates using three slant edge nanomagnets of varied lengths, b OR Layout A, c OR Layout B, d AND Layout A, e AND Layout B, f XOR Layout, g XNOR Layout, h single-bit comparator layout design with different clock zones (I, II, and III)

The number of design layouts required to implement logic using NML devices may equal the number of logic variations. In contrast, traditional CMOS devices typically require only one design layout that can be reconfigured at run-time. However, the advantage of CMOS can be harnessed by successfully realizing on-chip clocking strategies [9] and programmable input devices [12, 13] will harness this advantage of CMOS. This paper presents a simulation demonstration of one of the NML strategies, i.e., MQCA with varied amplitude clock pulses and single-layout designs for the AND/OR gate and single-bit comparator, a first-of-its-kind strategy to the best of the authors’ knowledge.

The remainder of this paper is organized as follows. Related work is explained in Sect. 2, and the proposed methodology is presented in Sect. 3. Section 4 discusses the results, and Sect. 5 provides the conclusion.

2 Related work

This section overviews the logic gates and single-bit comparator designs proposed in the literature.

2.1 Majority gates and logic gates

The majority gate is the basic building block for combinational and sequential logic circuits. Most researchers used the concept of the majority gate to implement universal or basic logic gates [14]. The majority gate comprises three input nanomagnets that surround a central computational nanomagnet, as demonstrated by Imre et al. The authors presented the basic logic gate using the majority gate concept in the MQCA design [7]. The authors arrange the two orthogonal intersecting nanomagnetic lines such that the vertical line produces ferromagnetic coupling and the horizontal line produces antiferromagnetic coupling. With one of the inputs at a constant value of 1/0, the majority gate behaves as a NAND/NOR gate.

Afterward, Varga et al. demonstrated the functioning of logic gates with the help of the programmable input majority gate concept [12]. The authors used different sizes of input driver magnets, which occupy a large area. The coercivity of the nanomagnets increases as the length in the easy axis increases, i.e., large-aspect-ratio nanomagnets need a higher value of magnetic flux density to switch as shown in Fig. 2. We demonstrate the change in magnetization direction of a small nanomagnet (15 \(\times\) 20 \(\times\) 10 nm\(^{3}\)) at different magnetic flux densities.

Siddiq et al. reported logic gate structure for nanomagnets using the concept of electrically controlled inputs and slant edge output nanomagnets [15]. The authors demonstrated the on-chip clocking. They verified the results using simulation as well as experimental analysis. The experimental validation has been done using magnetic force microscopy. The limitation of this work is that bias field-driven inputs are a major concern for large circuits.

Li et al. proposed the majority gate structure using 45\(^\circ\) misalignment-free clocking mechanism [16]. The authors used the driver magnet structure and demonstrated with the help of a reversal clocking field which decreases in amplitude progressively. Afterward, they also implemented an adder with the help of inclined driver nanomagnets of different sizes [17]. The authors require additional circuitry to ensure proper timing, which increases the complexity of the majority gate structure.

Jaiswal et al. implemented a rotating majority gate (RMG) using slant-edge nanomagnets and ferromagnetic coupling concept among the nanomagnets [18]. The authors used different layouts and a single clock technique for RMG implementation. Subsequently, they also presented a full adder design using two RMGs and antiferromagnetic coupling between sum and carry outputs.

Motivated by the above research approaches, we implement first-of-its-kind area-efficient logic gates utilizing the varied-length slant edge nanomagnets shown in Fig. 3. OR layout designs A and B, AND layout designs A and B, XOR layout design, and XNOR layout design are demonstrated in Fig. 1b, c, d, e, f, and g, respectively.

2.2 Comparator design

The comparator is the fundamental block of computing devices like ALU, CPU, etc. The function of the comparator is to compare the two logical values and give the output according to \(A<B\), \(A>B\), and \(A=B\). QCA-based comparator is demonstrated by [19,20,21] to utilize majority gate and XOR gate.

Bahar et al. demonstrated comparator design using majority gate and inverter logic only [22]. The authors demonstrated QCA architecture that works on the principle of multilayer crossing for fan-out, i.e., for accessing \(A=B\), the authors need extra crossover. They used one XOR gate, three inverter gates, and two majority gates, resulting in a large area overhead.

Majeed et al. implemented a QCA-based comparator using XNOR gates [19]. The authors need an extra cell to access the output cell. Subsequently, Khan et al. proposed the 1-bit magnitude comparator using single-layer or multilayer crossing networks [20]. The authors need 44 QCA cells, resulting in large area occupancy.

Sasamal et al. proposed big and scalable architecture for comparator design by reducing the number of crossovers [21]. They used two majority gates, two inverters, and one XOR gate. The advantage of the above design is that all input and output ports are easy to access on a single layer without using a multilayer structure.

Nanomagnetic logic-based comparator design demonstrated by Bhoi et al. They used the pNML technology and did the architectural design using the MagCAD tool [23]. They used six minority voters and one inverter in the layout design, which occupies a large bounding area of 2.4336 \(\upmu\)m\(^{2}\).

In this paper, we demonstrate a single-bit comparator design using the above-mentioned logic gates architecture in different clock zones. The schematic design of the single-bit comparator is shown in Fig. 1a. The layout design of the area-efficient single-bit comparator design is demonstrated in Fig. 4. Here we use three different clock zones and place the different logic gates, i.e., AND, OR, and XNOR gates, such as the coupling interaction between the different gates’ nanomagnets is negligible.

a Single-bit comparator layout design after \(B_H = -35 mT\) of applied magnetic flux density (B) for all clock zones (I, II and III), b \(B_L = 14 mT\) of applied B for I, \(B_M = 25 mT\) of applied B for II, III clock zones, c \(B_H\) of applied B for I and III clock zones, \(B_H\) followed by \(-B_M\) and then \(B_L\) for II clock zone, d \(-B_M\) of applied B for I clock zone, \(-B_L\) for III clock zone, \(B_H\) followed by \(-B_L\) for II clock zone

3 Proposed methodology

In this study, we propose a novel approach to implement non-majority logic gates using programmable and varied-length slant edge nanomagnets along with different amplitude clock pulses. To showcase the applicability of proposed non-majority-based logic gates we demonstrated a single-bit comparator design using different clock zones.

3.1 Logic gates

In this section, we discuss novel non-majority logic gates based on MQCA. Our approach incorporates the concept of varied-length slant edge nanomagnets and utilizes different amplitude external magnetic flux densities (\(B_H, B_M, \& B_L\)) to create run-time reconfigurable non-majority logic gate architectures. As a result of the run-time reconfigurable structure, we achieve all the outputs corresponding to all input combinations using a single layout design. Programmable input logic circuits can implement multiple applications on a single chip and switch between functionalities when necessary due to their run-time reconfigurable nature. The proposed layouts of non-majority logic gates using distinct aspect ratio nanomagnets are shown in Fig. 1b–g. Here, the output nanomagnet is ferromagnetically coupled with the input nanomagnets. In Fig. 1b–g, the output nanomagnet is shown in red, and the input nanomagnets are in brown and orange.

We propose two layout designs for OR and AND gates by interchanging the position of large and small nanomagnets. We use varied external magnetic fields high field \(B_H = 35 mT\), medium field \(B_M = 25 mT\), and low field \(B_L = 14 mT\) to attain all output states corresponding to different input combinations using a single layout, as demonstrated in Fig. 3. We demonstrate the external magnetic flux density operation of OR layout A and AND layout A in Fig. 3. Likewise, we get the output for all the input combinations for OR layout B and AND layout B using the clock pulse, as shown in Fig. 3. We also define the following axioms A1 and A2 corresponding to the hysteresis curves, as shown in Fig. 2.

-

A1:

Increasing the aspect ratio of nanomagnets increases its coercivity along the easy axis.

-

A2:

A higher magnetic field is needed for the re-magnetization of large-size nanomagnets [12, 13, 24, 25].

According to axiom A1 and A2, nanomagnets \(\hbox {IN}_{{1}}\), \(\hbox {IN}_{{2}}\), and OP lengths are distinct. The varied magnetic flux density is needed to switch the nanomagnets from stable to null state for different aspect ratio nanomagnets. The minimum height of nanomagnets is 20 nm, and the geometric anisotopic ratio, i.e., height-to-width ratio, is 1.33, 1.6, and 2.67 for small, medium, and large nanomagnets. The width and thickness of all the nanomagnets are the same: 15 nm and 10 nm, respectively. This approach is similar to the conventional CMOS design, where a single layout design is used for different input combinations. The experimental validation of our proposed design is feasible as the on-chip clocking is discussed by Siddiq et al. [15] and Alam et al. [26].

3.2 Comparator design

To date, MQCA architectural design methodology works on the principle that different input combinations need a different layout for dipole-dipole coupling. This methodology could be a promising contender for fewer input bits. However, as the number of input bits increases, the number of layout designs also increases. To overcome this drawback, programmable input logic comes into the picture. To the best of the authors’ knowledge, we propose a single-bit comparator design for dipole-dipole coupling for the very first time. The output of the comparator is defined as:

A and B are inputs, X, Y and Z are outputs for \(A<B, A>B\) and \(A=B\).

a–d Simulation result of the MQCA-based OR gate (Layout A) using MuMax3, a applied magnetic flux density (B) of −35 mT following a 0 mT, b 25 mT of applied B following a 0 mT, c 35 mT of applied B following a 0 mT, d −14 mT of applied B following a 0 mT; binary equivalent ‘1’ is represented by up arrow (green), binary equivalent ‘0’ by down arrow (blue) (Color figure online)

The nanomagnetic design of the proposed single-bit comparator uses three different gates, as depicted in Fig. 1a. The proposed architecture along with varied external magnetic flux densities is depicted in Fig. 4. Here we use two AND gate layouts and one XNOR gate layout in different clock zones. We utilize variable amplitude clock pulses for different clock zones, which makes the proposed comparator layout an area-efficient design [27, 28]. The size of input nanomagnets ‘A’ and ‘B’ is 15 \(\times\) 40 \(\times\) 10 nm\(^{3}\) and 15 \(\times\) 20 \(\times\) 10 nm\(^{3}\), respectively. We choose the output nanomagnet size to be 15 \(\times\) 24 \(\times\) 10 nm\(^{3}\). Under the influence of high magnetic flux density (\(B_H = 35 mT\)), all the nanomagnets are forced to a null state. When we apply medium magnetic flux density (\(B_M = 25 mT\)), medium and least-sized nanomagnets change their states. For the remaining input combinations, we apply low magnetic flux density (\(B_L = 14 mT\)) then there will be a change in least-sized nanomagnets only. We get the exact output for all the input combinations using this approach. All the layout architectures have been done in MuMax3, and their simulation results will be discussed in Sect. 4.

a–d Simulation result of the MQCA-based OR gate (Layout B) using MuMax3, a applied magnetic flux density (B) of −35 mT following a 0 mT, b 25 mT of applied B following a 0 mT, c 35 mT of applied B following a 0 mT, d −14 mT of applied B following a 0 mT; binary equivalent ‘1’ is represented by up arrow (green), binary equivalent ‘0’ by down arrow (blue) (Color figure online)

4 Simulation results and discussion

We have utilized GPU accelerated MuMax3 [29] to implement the proposed designs to provide proof of concept. The DyNaMat group at Ghent University developed and maintains the MuMax3 simulation platform, which gives approximately 100 times faster performance than OOMMF, a CPU-based simulation platform. The Landau-Lifshitz-Gilbert (LLG) equation is solved using the 4\(^\textrm{th}\)-order Runge-Kutta (RK45) evolver as a time step control. To achieve adaptive time step control, the Dormand-Prince method is utilized, which offers 5\(^\textrm{th}\)-order convergence and 4\(^\textrm{th}\)-order error estimation. While most micromagnetic simulations have historically been run on OOMMF, utilizing a GPU-accelerated micromagnetic simulator enables smaller tasks to be run in parallel, resulting in faster simulations. Figs. 5 and 6 show the results of the micromagnetic simulations for design layouts A and B of the proposed OR gate. The proposed AND layouts A and B are demonstrated in Figs. 7 and 8. The XOR and XNOR layout design, shown in Fig. 1f, g, and their simulation results are presented in Figs. 9 and 10. Figure 11 illustrates the micromagnetic simulation results of the proposed comparator designs depicted in Fig. 4.

The appropriate aspect ratio of nanomagnets is crucial in MQCA circuits. If the ratio is too high, the nanomagnets may become unstable and cause the circuit to malfunction. On the other hand, if the ratio is too low, it may lead to incorrect data propagation due to the high instability of the nanomagnets along their hard axis. To determine the optimal aspect ratio, multiple simulations were performed in MuMax3 as Jaiswal et al. have done [30]. In the proposed MQCA circuits, the large, medium, and small nanomagnets have differences in length only. Width and thickness are the same for the logic gates and comparator layout architectures.

a–d Simulation result of the MQCA-based AND gate (Layout A) using MuMax3, a applied magnetic flux density (B) of 35 mT following a 0 mT, b −25 mT of applied B following a 0 mT, c −35 mT of applied B following a 0 mT, d 14 mT of applied B following a 0 mT; binary equivalent ‘1’ is represented by up arrow (green), binary equivalent ‘0’ by down arrow (blue) (Color figure online)

a–d Simulation result of the MQCA-based AND gate (Layout B) using MuMax3, a applied magnetic flux density (B) of 35 mT following a 0 mT, b −25 mT of applied B following a 0 mT, c −35 mT of applied B following a 0 mT, d 14 mT of applied B following a 0 mT; binary equivalent ‘1’ is represented by up arrow (green), binary equivalent ‘0’ by down arrow (blue) (Color figure online)

a–d Simulation result of the MQCA-based XOR gate using MuMax3, a applied magnetic flux density (B) of −35 mT following a 0 mT, b 25 mT of applied B following a 0 mT, c 35 mT of applied B following a 0 mT, afterward −14mT of applied B following a 0 mT d −25 mT of applied B following a 0 mT, afterward 14 mT of applied B following a 0 mT; binary equivalent ‘1’ is represented by up arrow (green), binary equivalent ‘0’ by down arrow (blue) (Color figure online)

a–d Simulation result of the MQCA-based XNOR gate using MuMax3, a applied magnetic flux density (B) of −35 mT following a 0 mT, b 25 mT of applied B following a 0 mT, c 35 mT of applied B following a 0 mT, afterward −14mT of applied B following a 0 mT d −25 mT of applied B following a 0 mT, afterward 14 mT of applied B following a 0 mT; binary equivalent ‘1’ is represented by up arrow (green), binary equivalent ‘0’ by down arrow (blue) (Color figure online)

The simulations were conducted using a saturation magnetization of 8 \(\times\) 10\(^{5}\) A/m, an exchange stiffness constant of 1.3 \(\times\) 10\(^{-13}\) J/m, and a damping coefficient of 0.25. Permalloy was the material of choice, consisting of a poly-crystalline structure with a composition of 21.5% iron, and 78.5% nickel. It lacked a uniaxial anisotropy constant [31]. The remarkable exchange energy of permalloy makes it a preferred choice for a soft ferromagnetic material, surpassing magneto-crystalline anisotropy. The absence of a uniaxial anisotropy constant in Permalloy indicates that the magnetic anisotropy aligns easily with the long axis of the material, dependent solely on the shape of the nanomagnets.

Figures 5 and 6 demonstrates OR layouts A and B simulation results, where all the input combinations are verified using the graphical plot of applied external magnetic flux density and the magnetization direction of input and output nanomagnets w.r.t time in seconds. Likewise AND layout A and B is verified which is demonstrated in Figs. 7 and 8. XOR layout design’s simulation results are shown in Fig. 9. Here for input combinations ‘10’ and ‘11’, we get the simulation results after the application of one clock pulse only while for ‘00’ and ‘01’ we have to apply two clock pulses simultaneously. Likewise, we get MuMax3 simulation output of XNOR layout for all input combinations which is illustrated in Fig. 10.

MuMax3 simulation result of single-bit comparator design a after \(B_H = -35 mT\) of applied magnetic flux density (B) for all clock zones (I, II and III), b \(B_L = 14 mT\) of applied B for I, \(B_M = 25 mT\) of applied B for II, III clock zones, c \(B_H\) of applied B for I and III clock zones, \(B_H\) followed by \(-B_M\) and then \(B_L\) for II clock zone, d \(-B_M\) of applied B for I clock zone, \(-B_L\) for III clock zone, \(B_H\) followed by \(-B_L\) for II clock zone, binary equivalent ‘1’ is represented by up arrow (green), binary equivalent ‘0’ by down arrow (blue), e–h real-time MFM images of the simulation outputs for 10, 11, 01, and 00 input combinations, respectively

The single-bit comparator design’s simulation results in remanent magnetization form are demonstrated in Fig. 11a–d. For input combination ‘10’ output X = 0 \((A<B)\), Z = 0 \((A=B)\) and Y = 1 \((A>B)\) which is illustrated in Fig. 11a. For input combination ‘11’ and ‘00’ output X = 0 \((A<B)\), Z = 1 \((A=B)\) and Y = 0 \((A>B)\) shown in Fig. 11b, d. Input combination ‘01’ output X = 1 \((A<B)\), Z = 0 \((A=B)\) and Y = 0 \((A>B)\) is illustrated in Fig. 11c. The bit value ‘1’ can be determined by upward direction magnetization, and the nanomagnets are shown in green, while the bit value ‘0’ by downward magnetization and nanomagnets are shown in blue. Real-time magnetic force microscope (MFM) images of the simulation outputs for 10, 11, 01, and 10 are shown in Fig. 11e–h. The binary value for the nanomagnets can be determined with the help of the contrast. Solid dark black contrast shows the magnetization direction of the nanomagnets pointing towards the probe. Bright white contrast shows the magnetization pointing away from the probe. Our simulation study reported here focuses on the sub-50-nm design, motivated by the experimental confirmation of the potential fabrication of our proposed design methodology, as discussed by Gavagnin et al. [32]. This confirmation encourages further exploration and analysis of the design through simulations. By investigating the performance and characteristics of the sub-50-nm design, we aim to gain valuable insights and assess its viability for practical implementation.

The kink energy for a nanomagnet is typically defined as the difference between the energy of the meta-stable (frustrated) state and the energy of the desired ground state, as expressed in Eq. 4. This energy difference is commonly referred to as the kink energy, denoted as \(E_{Kink}\), and is given by:

Here, \(U_{MS}\) represents the energy associated with the meta-stable state of the nanomagnet, while \(U_G\) represents the energy associated with the desired ground state. By subtracting the energy of the ground state from that of the meta-stable state, we obtain the energy required to transition from the meta-stable to the ground state, which is the kink energy [33]. After applying 35 mT external magnetic flux density, the kink energy is 8.93 \(\times\) 10\(^{-21}\) J, whereas kink energy for 25 mT and 14 mT is much less, 2.25 \(\times\) 10\(^{-21}\) J and 1.63 \(\times\) 10\(^{-21}\) J, respectively.

The total energy, exchange energy, and demagnetization energy are illustrated in Table 1 for AND and OR layout A and B. When the system is in the ground state, i.e., zero external magnetic flux density after the application of varied magnetic flux densities, demagnetization and total energies are nearly equal and exchange energy is much lower than the total and demagnetization energy. By default, the MuMax3-based fourth-order Runge-Kutta (RK45) evolver performs micromagnetic simulation at 0K. We have done the simulation for 15 \(\times\) 40 \(\times\) 10 nm\(^{3}\) slant edge nanomagnets at different temperatures, i.e., 0K, 5K, 50K, 60K, 100K, 273K, and 300K, and analyzed the change in switching field and coupling energies. The total energy increases with the temperature while the exchange and demagnetization energies remain the same. The switching field, i.e., external magnetic flux density decreases as we increase the temperature as shown in Fig. 12. As we used sub-50-nm nanomagnets, magnetic polarization changes from a stable state to a meta-stable state after the application of 2 mT magnetic flux density at 60K temperature, and there is a misalignment in magnetization while increasing temperature above 70K. In this study, our focus is on implementing an area-efficient comparator design and its micromagnetic simulation analysis. In future works, we expect to remove the temperature dependency of sub-50-nm nanomagnets using the interlayer exchange coupled (IEC) approach as suggested by Mattela et al. [34].

Table 2 illustrates the performance comparison of the proposed MQCA-based run-time reconfigurable (RR) comparator design with the existing design in terms of the number of nanomagnets, area occupancy, and area usage. Our proposed design exhibits \(\sim\)56%-67% reduction in area occupancy compared to the QCA designs and \(\sim\)99% reduction compared to the existing MQCA design. The number of nanodots decreases by \(\sim\)50%-80% in comparison to the existing comparator design. The delay in the single-bit comparator for one input combination is 1 ns and the total delay is 7 ns for verification of all the input combinations.

5 Conclusion

In this research study, the authors proposed new designs for area-efficient nanomagnetic-based non-majority logic gates. To showcase the scalability of the proposed design a single-bit comparator design was introduced. It uses three logic gates and consists of only nine nanomagnets, resulting in a significant reduction in the number of nanomagnets required compared to the current state-of-the-art. Our design exhibits 99% area reduction and 50% reduction in the number of nanomagnets compared to the existing MQCA design. The authors aim to create nanomagnetic computing element libraries for computer-aided design tools to develop the proposed design further. The authors highlight the potential for future exploration of building higher-bit comparator designs. Further extensions such as an interlayer-exchange-coupled approach, placement automation using A*, and genetic algorithm could be investigated.

Data availability

Availability of data and materials—NA.

References

IRDS, systems, architectures, team: international roadmap for devices and systems: executive summary. IEEE Adv. Technol. Human. 63 (2020)

Cowburn, R.P., Welland, M.E.: Room temperature magnetic quantum cellular automata. Science 287(5457), 1466–1468 (2000). https://doi.org/10.1126/science.287.5457.1466

Porod, W., Niemer, M.: Better computing with magnets. IEEE Spectrum 172(September), 45 (2015)

Cowburn, R.P.: Probing antiferromagnetic coupling between nanomagnets. Phys. Rev. B Condens. Matter Mater. Phys. 65(9), 1–4 (2002). https://doi.org/10.1103/PhysRevB.65.092409

Csaba, G., Imre, A., Bernstein, G.H., Porod, W., Metlushko, V.: Nanocomputing by field-coupled nanomagnets. IEEE Trans. Nanotechnol. 1(4), 209–213 (2002). https://doi.org/10.1109/TNANO.2002.807380

Bernstein, G.H., Imre, A., Metlushko, V., Orlov, A., Zhou, L., Ji, L., Csaba, G., Porod, W.: Magnetic QCA systems. Microelectron. J. 36(7), 619–624 (2005). https://doi.org/10.1016/j.mejo.2004.12.002

Imre, A., Csaba, G., Ji, L., Orlov, A., Bernstein, G.H., Porod, W.: Majority logic gate for magnetic quantum-dot cellular automata. Science 311(5758), 205–208 (2006). https://doi.org/10.1126/science.1120506

Niemier, M., Alam, M., Hu, X.S., Bernstein, G., Porod, W., Putney, M., Deangelis, J.: Clocking structures and power analysis for nanomagnet-based logic devices. In: Proceedings of the International Symposium on Low Power Electronics and Design, pp. 26–31 (2007). https://doi.org/10.1145/1283780.1283787

Alam, M.T., Siddiq, M.J., Bernstein, G.H., Niemier, M., Porod, W., Hu, X.S.: On-chip clocking for nanomagnet logic devices. IEEE Trans. Nanotechnol. 9(3), 348–351 (2010). https://doi.org/10.1109/TNANO.2010.2041248

Varga, E., Niemier, M.T., Csaba, G., Bernstein, G.H., Porod, W.: Experimental realization of a nanomagnet full adder using slanted-edge magnets. IEEE Trans. Magn. 49(7), 4452–4455 (2013). https://doi.org/10.1109/TMAG.2013.2249576

Dadjouyan, A.A., Sayedsalehi, S., Faghih Mirzaee, R., Jafarali Jassbi, S.: Design and simulation of reliable and fast nanomagnetic conservative quantum-dot cellular automata (NCQCA) gate. J. Comput. Electronics 20(5), 1992–2000 (2021). https://doi.org/10.1007/s10825-021-01763-y

Varga, E., Niemier, M.T., Bernstein, G.H., Porod, W., Hu, X.S.: Programmable nanomagnet-logic majority gate. Device Res. Conf. Conf. Digest DRC 310(574), 85–86 (2010). https://doi.org/10.1109/DRC.2010.5551921

Kiermaier, J., Breitkreutz, S., Eichwald, I., Ju, X., Csaba, G., Schmitt-Landsiedel, D., Becherer, M.: Programmable input for nanomagnetic logic devices. EPJ Web Conf. 40, 2–5 (2013). https://doi.org/10.1051/epjconf/20134016007

Jaiswal, V., Sasamal, T.N.: A Novel approach to design NML-based programmable input rotating majority gate. In: 2023 IEEE Radio and Antenna Days of the Indian Ocean (RADIO), pp. 1–2 (2023). https://doi.org/10.1109/RADIO58424.2023.10146094

Siddiq, M.A.J., Butler, K., Dey, H., Shah, F.A., Li, P., Varga, E., Orlov, A., Csaba, G., Niemier, M., Porod, W., Bernstein, G.H.: Nanomagnet logic gate with programmable-electrical input. IEEE Trans. Magn. 50(11) (2014). https://doi.org/10.1109/TMAG.2014.2325853

Li, Z., Kwon, B.S., Krishnan, K.M.: Misalignment-free signal propagation in nanomagnet arrays and logic gates with 45\(^\circ\)-clocking field. J. Appl. Phys. 115(17), 1–4 (2014). https://doi.org/10.1063/1.4859996

Li, Z., Krishnan, K.M.: A 3-input all magnetic full adder with misalignment-free clocking mechanism. J. Appl. Phys. 121(2) (2017). https://doi.org/10.1063/1.4974109

Jaiswal, V., Sasamal, T.N.: Novel approach for the design of efficient full adder in MQCA. J. Supercomput. (0123456789) (2022). https://doi.org/10.1007/s11227-022-04989-0

Majeed, A.H., Zainal, M.S., Alkaldy, E., Nor, D.M.: Single-bit comparator in quantum-dot cellular automata (QCA) technology using novel QCA-XNOR gates. J. Electronic Sci. Technol. 19(3), 263–273 (2021). https://doi.org/10.1016/J.JNLEST.2020.100078

Khan, A., Arya, R.: High performance nanocomparator: a quantum dot cellular automata-based approach. J. Supercomput. 78(2), 2337–2353 (2022). https://doi.org/10.1007/S11227-021-03961-8/TABLES/4

Sasamal, T.N., Saini, G., Jaiswal, V.: High Speed Comparator and Parity generator in QCA based on optimal XOR structure. In: 2022 IEEE 7th Forum on Research and Technologies for Society and Industry Innovation (RTSI) (2022). https://doi.org/10.1109/RTSI55261.2022.9905214

Newaz Bahar, A., Roy, K., Asaduzzaman, M., Maksudur, M., Bhuiyan, R.: Design and Implementation of 1-bit Comparator in Quantum-dot Cellular Automata (QCA). Cumhuriyet Univ. Faculty Sci. Sci. J. (CSJ) 38(1) (2017). https://doi.org/10.17776/csj.72358

Kumar Bhoi, B., Kumar Misra, N., Pradhan, M.: Design of magnetic dipole based 3D integration nano-circuits for future electronics application. Int. J. Nano Dimens. 9(4), 374–385 (2018)

Zhang, B., Yang, X., Wang, Z., Zhang, M.: Innovative orderly programmable in-plane majority gates using trapezoid shape nanomagnet logic devices. Micro Nano Lett. 9(5), 359–362 (2014). https://doi.org/10.1049/MNL.2013.0695

Sivasubramani, S., Mattela, V., Rangesh, P., Pal, C., Acharyya, A.: Nanomagnetic logic based runtime Reconfigurable area efficient and high speed adder design methodology. Nanotechnology 31(18) (2020). https://doi.org/10.1088/1361-6528/ab704b

Alam, M.T., Kurtz, S.J., Siddiq, M.A.J., Niemier, M.T., Bernstein, G.H., Hu, X.S., Porod, W.: On-chip clocking of nanomagnet logic lines and gates. IEEE Trans. Nanotechnol. 11(2), 273–286 (2012). https://doi.org/10.1109/TNANO.2011.2169983

Cairo, F., Vacca, M., Graziano, M., Zamboni, M.: Domain Magnet Logic (DML): A new approach to magnetic circuits. In: Proceedings of the IEEE Conference on Nanotechnology (Dml), 956–961 (2014). https://doi.org/10.1109/NANO.2014.6968053

Vacca, M., Cairo, F., Turvani, G., Riente, F., Zamboni, M., Graziano, M.: Virtual clocking for nanomagnet logic. IEEE Trans. Nanotechnol. 15(6), 962–970 (2016). https://doi.org/10.1109/TNANO.2016.2617866

Vansteenkiste, A., Leliaert, J., Dvornik, M., Helsen, M., Garcia-Sanchez, F., Van Waeyenberge, B.: The design and verification of MuMax3. AIP Adv. 4(10), 22 (2014) https://arxiv.org/abs/1406.7635arXiv:1406.7635. https://doi.org/10.1063/1.4899186

Jaiswal, V., Sasamal, T.N.: A Novel Approach to Design Multiplexer using Magnetic Quantum-Dot Cellular Automata. IEEE Embed. Syst. Lett., 1 (2022). https://doi.org/10.1109/LES.2022.3207193

Rodrigues, D.C.M., Klautau, A.B., Edström, A., Rusz, J., Nordström, L., Pereiro, M., Hjörvarsson, B., Eriksson, O.: Magnetic anisotropy in permalloy: hidden quantum mechanical features. Phys. Rev. B 97(22), 1–6 (2018) https://arxiv.org/abs/1702.05414arXiv:1702.05414. https://doi.org/10.1103/PhysRevB.97.224402

Gavagnin, M., Wanzenboeck, H.D., Belić, D., Bertagnolli, E.: Synthesis of individually tuned nanomagnets for nanomagnet logic by direct write focused electron beam induced deposition. ACS Nano 7(1), 777–784 (2013). https://doi.org/10.1021/nn305079a

Pulecio, J.F., Pendru, P.K., Kumari, A., Bhanja, S.: Magnetic cellular automata wire architectures. IEEE Trans. Nanotechnol. 10(6), 1243–1248 (2011). https://doi.org/10.1109/TNANO.2011.2109393

Mattela, V., Debroy, S., Sivasubramani, S., Acharyya, A.: A novel and reliable interlayer exchange coupled nanomagnetic universal logic gate design. Nanotechnology 32(9) (2021). https://doi.org/10.1088/1361-6528/abcac9

Funding

The authors did not receive any support from any organization for the work presented in this submission.

Author information

Authors and Affiliations

Contributions

VJ and TNS were involved in the design of the layout, simulation studies, and analysis, and they both contributed to the writing of the manuscript. VJ initially drafted the manuscript, which was subsequently improved by both VJ and TNS. All authors have reviewed and given their approval for the final version of the manuscript.

Corresponding author

Ethics declarations

Conflict of interest

The authors of this article state that they do not have any conflicts of interest to declare.

Ethical approval

None of the authors of this article conducted any studies involving human participants or animals.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Jaiswal, V., Sasamal, T.N. Run-time reconfigurable nanomagnetic logic gates and comparator designs using very high-permeability material. J Comput Electron 22, 1748–1759 (2023). https://doi.org/10.1007/s10825-023-02105-w

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-023-02105-w