Abstract

With the shift from traditional analog circuit designs to an all-digital intensive approach, the all-digital Phase-locked loops (ADPLLs) have become more attractive in digital communication systems. Digitally controlled oscillators (DCO) are the key components of the ADPLL circuits. In this paper, a new low power DCO structure is proposed with NMOS transistor as the switching network and utilizing the NMOS varactor as shunt-capacitive loads for the delay cells. The new DCO is capable of producing much higher output frequencies and comprises of components that are fully digital. The proposed DCO structure is designed for three, five and seven stages in CMOS 0.18 µm technology. Variable capacitance is achieved by the use of control word which is applied through NMOS switches conditionally selecting combinations of capacitance and hence determining the delay of the circuit. A 3-stages digitally controlled oscillator shows output frequency variation from 1.986 to 3.526 GHz with a power consumption of 1.484 mW. In the 5-stages DCO, the output frequency varies from 1.154 to 2.210 GHz with a power consumption of 2.762 mW. For 7-stages DCO, the output oscillation frequency is in the range from 0.835 to 1.658 GHz with a power consumption of 4.04 mW. A 3-stages DCO shows a phase noise of − 100.06 dBc/Hz with the offset of 1 MHz with the corresponding figure of merit (FoM) of 165.37 dBc/Hz. Five and seven-stages DCO show phase noise of − 102.08 dBc/Hz and − 105.52 dBc/Hz at 1 MHz respectively. The figure of merit (FoM) for 5 and 7-stages is 160.92 dBc/Hz and 159.07 dBc/Hz respectively. The digital tuning range for 3, 5, and 7-stages DCO is 55.96%, 62.78%, and 66.05% respectively. Further, the results show that the designed DCO has a maximum supply voltage tuning range of 101.45% with the variation of VDD from 1 to 1.8 V. Comparison with earlier reported circuits has been made based on output frequency, power consumption, and phase noise.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Phase-Locked Loops (PLLs) are the fundamental circuit elements of the data transmission system for clock generation and frequency synthesis [1,2,3,4]. Conventional PLLs make use of voltage-controlled oscillator (VCO) for varying the oscillation frequency. However, at low-voltage operation, the frequency tuning for analog CMOS oscillator becomes more difficult to achieve. Also, conventional CMOS based oscillator shows more power consumption and are less immune to the noise. To overcome these issues, all-digital phase-locked loops (ADPLL) have come into existence [5,6,7,8,9]. ADPLL consists of three main components: a digital phase detector, a digital loop filter and a digitally controlled oscillator (DCO).

DCO which is a fully digital-intensive approach, is the key component in the fully digital PLLs for controlling the frequency of oscillation. Digital circuits are more preferable than analog circuits due to the decreasing cost of implementation in the present-day CMOS process technology. Digitally controlled delay elements (delay cells/DCDE) are the main components of DCO. The output frequency of a ring type oscillator is dictated by the delay (td) offered by single stage as well the number of delay stages (N) and is given by Eq. (1).

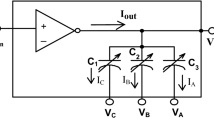

In the literature different types of DCO circuits have been reported with one or more approaches [8,9,10,11,12,13,14,15]. The most popular approach as shown in Fig. 1(a), is based on the ring-based inverter topology in which MOS capacitors are used as the switching networks which are binary weighted and are used to modify the delay of the circuit [10, 11]. However, an increase in the number of switched capacitors puts a limitation on the maximum achievable frequency by the DCO. Further, the second approach includes path selection as shown in Fig. 1(b), in which the output frequency can be controlled by selecting the number of delay stages. In path selection, multiplexers are used to select the number of delay stages in the DCO. Path selection is often used in combination with other techniques due to its limited resolution which further increases the hardware requirement [8, 12,13,14,15]. The third approach is based on current-starved inverter as given in Fig. 1(c). Binary-weighted NMOS/PMOS switching networks are connected in series with the inverters and the resistance posed by the switching networks is used to modify the delay offered by each stage which in turn dictates the output frequency of the DCO. The current starved inverter based DCO requires complex hardware and hence consumes more area [8, 9]. Delay cells are the major performance governing block of DCO and delay of these cells can be varied with different techniques like modifying the MOS driving strength: by fixed loading, shunt loading, and resistance variation [10, 16,17,18,19,20,21,22,23]. Although the above-mentioned techniques offer reasonable frequency range but by increasing the number of capacitive elements the maximum achievable frequency is limited. In the proposed DCO architecture the maximum frequency is achieved when all the control bits are 0’s, hence eliminating all the parasitic elements from the circuit.

In this paper, a three, five and seven stages DCO architectures with NMOS based varactor and switching network have been proposed. The rest of paper is organized as: Sect. 2 describes the proposed design of DCO. Section 3 describes the simulation results followed by a conclusion in Sect. 4.

2 Proposed DCO circuit design

2.1 Delay element

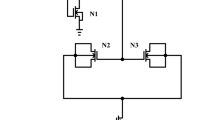

In the proposed DCO, the delay stage utilizes the MOS varactors as capacitive load cells which produce the delay. For this NMOS transistor is used to realize the MOS varactor by connecting the drain, source, and bulk (D, S, B) of the transistor together as shown in Fig. 2. Since the varactors are implemented using NMOS transistors hence no additional mask is required. Furthermore, transistor based varactors are preferred over diode based varactor since they reduce the static power consumption, area and increases the VCO phase noise performance [24]. The gate acts as one terminal and the drain, source, and bulk connected together to form another terminal of the capacitor with an oxide layer as a dielectric. The gate is connected to the voltage a and the drain, source, and bulk to the voltage b.

By applying gate voltage greater then threshold voltage i.e. VG > VT for NMOS capacitor, an inversion channel builds up due to the surplus electrons on the surface and the MOS capacitor works in strong inversion region. In strong inversion region, the variable MOS capacitance CVAR (maximum MOS capacitance) is dominated by the oxide capacitance COX given by Eq. (2).

The MOS capacitor can be varied by varying the width of the MOS.

2.2 Delay stage of the proposed DCO

In the conventional DCO, the output frequency is dictated by the delay offered by each delay cell. In the proposed design, a new delay cell with binary weighted and digitally controlled MOS varactor as capacitive loads has been developed. These binary weighted MOS capacitors are used to vary the delay of the stages accordingly thus achieving a large frequency range. Each delay stage has two identical CMOS inverters with capacitive load cells connected between their outputs as shown in Fig. 3. Each capacitive load cell is made of two identical varactors connected in series in between the output lines of the two inverters.

For a 3-bit DCO design, three binary-weighted capacitive loads are connected in between the output lines of the inverters. The NMOS switches connect the node in between the two varactors to ground depending upon the digital binary code applied to them. A control word (D0, D1, D2) is applied through NMOS switches conditionally selecting combinations of capacitance and hence determining the delay of the circuit.

In the proposed DCO, the capacitor is placed before the switch. Subsequently, the off capacitance is reduced to a very small value (< Cj), where Cj is the drain junction capacitance of the NMOS switch. As the capacitance seen by each inverter is very small (< 0.5Cj), the maximum frequency is achieved when the control word is all zeros. When the switch is ON, the common node between the two MOS varactors is connected to the ground. This makes the ON capacitance to be equal to 2C, where C is the MOS varactor capacitance. As a result of the large difference in the ON and OFF capacitance, large tuning range can be achieved.

The width of the PMOS and NMOS transistors of the switching network, MOS varactors, inverters and the 3T-NAND gate is summarized in Table 1.

2.3 DCO circuit design

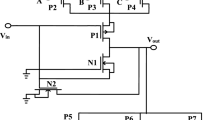

The new DCO has been designed with 3-stages, 5-stages, 7-stages variant utilizing the proposed delay stage. The proposed DCO design consists of an even number of proposed delay stages and a 3T-NAND gate [25]. The 3-T NAND gate forms the last stage of the DCO making the total delay stages to be odd in number. The 3T-NAND delay stage is made up of two PMOS transistors and one NMOS transistor. The two input terminals of the NAND gate are connected to the two feedback signals from the previous stage. In the 3-T NAND gate, the substrate of PMOS P3 as well as of PMOS P4 is connected to VDD and substrate of NMOS is connected to ground. The delay stages and the 3T-NAND gate form two digital ring oscillators that oscillate at the same frequency and phase.

The NAND gate helps in synchronization of the two oscillators and matches the output of two oscillators in terms of frequency and phase. A 3-bit three-stages DCO has been implemented which consists of two delay stages and a 3-T NAND gate as shown in Fig. 4. The digital control codes have been applied through the NMOS switches which determine the output oscillation frequency.

A 3-bit five-stages DCO has been implemented using the proposed delay stage as shown in Fig. 5. In addition, a 3-bit seven-stages DCO has also been designed using the same methodology and simulations have been carried out in 0.18 μm CMOS technology.

3 Results and discussions

The new DCO has been designed with 3-stages, 5-stages, 7-stages variant utilizing the proposed delay stage in 0.18 µm CMOS technology with 1.8 V supply. To validate the design, the design has been simulated using Mentor graphics tool. Table 2 shows the variation of output frequency and power consumption with respect to control bits applied to a 3-bit DCO for 3-stages, 5-stage and 7-stages DCOs variant. The results show that as the control word is varied from 000 to 111, the output frequency decreases as the delay offered by delay stages increases with increasing MOS capacitance of the varactors of each stage. The results also show that the power consumption does not depend on the control bits but on the number of delay stages as well as on the supply voltage VDD. Figure 6 shows the comparison of the variation of output frequency for 3-stages, 5-stages and 7-stages DCO for a 3-bit control word at supply voltage VDD = 1.8 V.

Table 3 shows the variation of the output frequency and power consumption with respect to power supply VDD for a 3-stages DCO. Figure 7 shows the variation of the output frequency along with the varying VDD for a 3-stages DCO. The results confirm that the output frequency is sensitive to the changes in the supply voltage VDD.

Supply voltage scaling has proved to be an effective method for reducing the switching power as switching power is quadratically dependent on the supply voltage as given by the following equation:

where \( \alpha \) is the activity factor, VDD is the supply voltage, \( C_{L} \) is the total load capacitance and \( f_{clk} \) is the clock frequency. The variation of power consumption with varying power supply VDD for a 3-stages DCO is shown in Fig. 8 and the results conform to the quadratic relation between them as given in the above Eq. (3).

The output frequency waveform with control word [000] has been shown for 3-stages DCO in Fig. 9 along with the frequency spectra. Figure 10 shows the output frequency and frequency spectra for 5-stages DCO with control word [101].

The phase noise and figure of merit (FoM) are two essential parameters to measure the quality performance of a ring oscillator. The phase noise of all the three variants of the proposed DCO has been measured as shown in Fig. 11 and the figure of merit (FoM) has been calculated according to the following expression [26]:

where \( L(\Delta f) \) is the phase noise of the DCO in dBc/Hz at \( f \) offset from the carrier frequency \( f_{c} \), and \( P_{DC} \) is the power consumption in mW. Table 4 shows the values of phase noise and FoM for 3,5 and 7-stages DCO along with digital tuning range.

The above results have been compared with the earlier published work as shown in Table 5. It has been observed that the proposed circuit shows a better performance in terms of output frequency and power consumption than the earlier reported circuits. Many DCOs have been implemented with standard inverter-based delay cells, and these circuits suffer from poor performance in terms of power consumption, and output frequency range. In the proposed design of DCO, the output frequency is tuned using the I-MOS based varactor at the output node. The proposed delay cell provides an additional tuning approach with a variable capacitor as compared to the standard inverter-based delay cell. Tuning of frequency without varying the power supply voltage provides the advantages of low power consumption. The last stage of the proposed circuits is designed with a 3-T NAND gate which has been implemented with the minimum number of transistors as compared to the standard approach. For a fair comparison for proposed DCO structure with those implemented using inverter-based delay cells only, a comparison based on parameters like output frequency, power consumption has been provided in Table 5.

4 Conclusions

We have proposed a delay cell with NMOS switching network with NMOS varactor acting as a shunt-capacitive loads which exhibits low power consumption and wide output frequency tuning range. The three variants of the proposed DCO were designed in CMOS 0.18 µm technology. At 1.8 V supply voltage, 3-bit three-stages DCO circuit reports a wide range of tuning from 1.986 to 3.526 GHz with a power consumption of 1.484 mW. A 3-bit five-stages DCO shows the output frequency from 1.154 to 2.210 GHz and power consumption of 2.762 mW. A 7-stages DCO exhibits an output oscillation frequency variation in the range from 0.835 to 1.658 GHz with a power consumption of 4.04 mW. Phase noise results of the proposed DCOs variants have also been obtained. Three, five and seven-stages DCO show phase noise of − 100.06 dBc/Hz, − 102.08 dBc/Hz and − 105.52 dBc/Hz at 1 MHz respectively. In addition to this, the figure of merit (FoM) for 3,5 and 7-stages was also calculated which comes out to be 165.37 dBc/Hz,160.92 dBc/Hz and 159.07 dBc/Hz respectively. The digital tuning range for 3,5, and 7-stages DCO is 55.96, 62.78, and 66.05% respectively and the DCO has a maximum supply voltage tuning range of 101.45% with the variation of VDD from 1 to 1.8 V. A comparison with earlier published work has been done. The proposed circuit provides a wide tuning range with low power consumption.

References

Hwang, I., Lee, S., Lee, S., & Kim, S. (2000). A digitally controlled phase-locked loop with fast locking scheme for clock synthesis application. In Proceedings of the 47th Annual IEEE International Solid-State Circuits Conference (ISSCC’00) (pp. 168–169), San Francisco, Calif, USA, February 2000.

Boerstler, D. W. (1999). A low-jitter PLL clock generator for microprocessors with lock range of 340–612MHz. IEEE Journal of Solid-State Circuits, 34(4), 513–519. https://doi.org/10.1109/4.753684.

Staszewski, R. B., & Balsara, P. (2005). Phase-domain all-digital phase-locked loop. IEEE Transactions on Circuits and Systems-II: Express Briefs, 52(3), 159–163.

Larsson, P. (1999). A 2–166 MHz 1.2–2.5 V CMOS clock-recovery PLL with feedback phase-selection and averaging phase interpolation for jitter reduction. In Proceedings of IEEE International Solid-State Circuits Conference (ISSCC’99) (pp. 356–357), San Francisco, Calif, USA, February 1999.

Staszewski, B., Hung, C.-M., Maggio, K., Wallberg, J., Leipold, D., & Balsara, P. (2004). All-digital phase-domain TX frequency synthesizer for Bluetooth radios in 0.13-_m CMOS. In Proceedings of the IEEE Solid-State Circuits Conference (vol. 527, sec. 15.3, pp. 272–273).

Dunning, J., Garcia, G., Lundberg, J., & Nuckolls, E. (1995). An all-digital phase-locked loop with 50-cycle lock time suitable for high-performance microprocessors. IEEE Journal of Solid-State Circuits, 30(4), 412–422. https://doi.org/10.1109/4.375961.

Olsson, T., & Nilsson, P. (2004). A digitally controlled PLL for SoC applications. IEEE Journal of Solid-State Circuits, 39(5), 751–760. https://doi.org/10.1109/JSSC.2004.826333.

Chiang, Jen-Shiun, & Chen, Kuang-Yuan. (1999). The design of an all-digital phase-locked loop with small DCO hardware and fast phase lock. IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, 46(7), 945–950. https://doi.org/10.1109/82.775392.

Zhao, J., & Kim, Y. (2010). A low-power digitally controlled oscillator for all digital phase-locked loops VLSI design. Hindawi Publishing Corporation, vol. 2010, pp. 1–11.

Raha, P., Randall, S., Jennings, R., Helmick, B., Amerasekera, A., Haroun, B. (2002). A robust digital delay line architecture in a 0.13 μm CMOS technology node for reduced design and process sensitivities. In Proceedings international symposium on quality electronic design (pp. 148–153).

Tomar, A., Pokharel, R., Nizhnik, O., Kanaya, H., & Yoshida, K. (2007). Design of 1.1 GHz highly linear digitally-controlled ring oscillator with wide tuning range. In IEEE international workshop on radio-frequency integration technology (pp. 82–85).

Wu, C.-T., Wang, W., Wey, I.-C., & Wu, A.-Y. (2005). A scalable DCO design for portable ADPLL designs. In 2005 IEEE international symposium on circuits and systems, Kobe, 2005 (Vol. 6, pp. 5449–5452). https://doi.org/10.1109/iscas.2005.1465869.

Sheng, D., Chung, C. C., & Lee, C. Y. (2006). An all-digital phase-locked loop with high-resolution for SoC applications. In Proceedings of the international symposium on VLSI design, automation and test 2006 (pp. 1–4).

Sheng, D., Chung, C., & Lee, C. (2007). An ultra-low-power and portable digitally controlled oscillator for SoC applications. IEEE Transactions on Circuits and Systems II: Express Briefs, 54(11), 954–958. https://doi.org/10.1109/TCSII.2007.903782.

Hsu, S., Yu, J., & Lee, C. (2010). A sub-10-μW digitally controlled oscillator based on hysteresis delay cell topologies for WBAN applications. IEEE Transactions on Circuits and Systems II: Express Briefs, 57(12), 951–955. https://doi.org/10.1109/TCSII.2010.2087991.

Saint-Laurent, M., & Muyshondt, G. (2001). A digitally controlled oscillator constructed using adjustable resistors. In 2001 Southwest Symposium on Mixed-Signal Design (pp. 80-82).

Staszewski, R. B., Leipold, D., Muhammad, K., & Balsara, P. T. (2003). Digitally controlled oscillator (DCO)-based architecture for RF frequency synthesis in a deep-submicrometer CMOS Process. IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, 50(11), 815–828. https://doi.org/10.1109/TCSII.2003.819128.

Staszewski, R. B., Hung, C.-M., Leipold, D., & Balsara, P. T. (2003). A first multigigahertz digitally controlled oscillator for wireless applications. IEEE Transactions on Microwave Theory and Techniques, 51(11), 2154–2164. https://doi.org/10.1109/tmtt.2003.818579.

Chen, Pao-Lung, Chung, Ching-Che, & Lee, Chen-Yi. (2005). A portable digitally controlled oscillator using novel varactors. IEEE Transactions on Circuits and Systems II: Express Briefs, 52(5), 233–237. https://doi.org/10.1109/TCSII.2005.846307.

Maymandi-Nejad, M., & Sachdev, M. (2003). A digitally programmable delay element: Design and analysis. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 11(5), 871–878. https://doi.org/10.1109/tvlsi.2003.810787.

Saint-Laurent, M., & Swaminathan, M. (2001). A digitally adjustable resistor for path delay characterization in high-frequency microprocessors. In Southwest symposium on mixed-signal design (pp. 61–64).

Elrabaa, M. E. S. (2014). A portable high-frequency digitally controlled oscillator (DCO). Integration, the VLSI Journal, 47, 339–346.

Kumar, Manoj, & Dwivedi, Dileep. (2018). A low power CMOS-based VCO design with I-MOS varactor tuning control. Journal of Circuits, Systems and Computers, 27(10), 1–14. https://doi.org/10.1142/S0218126618501608.

Gonzalez-Diaz, V. R., Sanchez-Gaspariano, L. A., Muñiz-Montero, C., & AlvaradoPulido, J. J. (2016). Improving linearity in MOS varactor based VCOs by means of the output quiescent bias point. Integration, the VLSI Journal, 55, 274–280.

Kumar, M. (2013). A low power voltage controlled oscillator design. ISRN Electronics, vol. 2013, Article ID 987179, 6 pages.

Razavi, B. (1998). RF Microelectronics. New Jesey: Prentice Hall.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Dabas, S., Kumar, M. A CMOS based low power digitally controlled oscillator design with MOS varactor. Analog Integr Circ Sig Process 100, 565–575 (2019). https://doi.org/10.1007/s10470-019-01476-0

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-019-01476-0