Abstract

As operation frequencies of the printed circuit boards (PCBs) increase in keeping with VLSI frequencies in the GHz domain, two independent serious problems occur in the PCB design. One is waveform distortion problem, or signal integrity (SI) degradation problem, in PCB traces. And the other is power-supply drop problem, or power integrity (PI) degradation problem, in PCB power planes. Those problems are barely able to be overcome on case-by-case empirical designs conventionally. In this paper we newly propose a design approach for each problem, both of which are based on the genetic algorithm. And we obtained improvement ratios of more than double compared with the both conventional designs for SI and PI degradations, respectively.

Similar content being viewed by others

Explore related subjects

Discover the latest articles, news and stories from top researchers in related subjects.Avoid common mistakes on your manuscript.

1 Introduction

In the GHz-era, printed circuit board (PCB) design is facing two difficulties; one is signal integrity (SI) degradation and the other is power integrity (PI) degradation. The two integrity degradation problems both come from high-speed switching operations of LSIs mounted on the PCB, but they can be, or have to be dealt with independently in the design. The SI degradation is related to traces, or transmission lines while the PI degradation is related to the power distribution in the PCB design as follows.

SI degradation: when the signals’ electrical lengths are approaching their transmission line lengths, they generate reflection waves, or noises at impedance mismatch points in the transmission lines. Due to this reflection principle, a serious waveform degradation problem, or SI degradation problem occurs in the GHz digital signal domain in the printed circuit board (PCB).

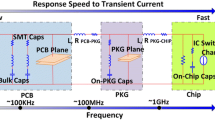

PI degradation: high frequency switching in the VLSI increases the impedances between power and ground planes in PCBs. Due to this impedance increase, serious power-supply voltage drop problem, or PI degradation problem occurs in the GHz signal domain in the PCB also.

Those problems are barely able to be overcome on a case-by-case empirical design independently at present. In this paper we newly propose a design approach for each problem, both of which are based on the genetic algorithms, and show those effectiveness, quantitatively.

2 Signal integrity improvement

The SI [1, 2] degradation is barely fixed on a case-by-case impedance matching design at present. To overcome this design problem, we propose a novel transmission line structure, which is called segmental transmission line (STL), and its design methodology using genetic algorithm.

2.1 Segmental transmission line (STL)

In STL, a transmission line is divided into multiple (N) segments, each with its own individual characteristic impedance Z i (i = 1, 2,…, N) as shown in Fig. 1, where Z i is a function of the segment’s width W i as Z i = f (W i ).

And each Z i is adjusted to achieve an ideal digital waveform at target points such as input points to the LSIs on the transmission line by superposing reflection waves generated at the interfaces between adjacent segments Z i and Z i+1 .

2.2 Design using genetic algorithm

The selection, or adjustment of all of the Z i s, however, results in a combinatorial explosion: for example, if there are 10 segments (N = 10) and 100 characteristic impedance candidates from 21 to 120 Ω at 1 Ω intervals, the resultant search space reaches 10010, and there is no deterministic search algorithm that can find the optimized or semi-optimized set of Z i s.

We have thus proposed applying genetic algorithms (GAs) as a way to manage this combinatorial explosion. The STL structure can be easily mapped onto a one-dimensional array of parameters, as shown in Fig. 2, where only characteristic impedance Z i is used for gene in the figure, in the actual design, however, we also use each segment length because of finer reflection-wave superposition.

2.3 GA operation and fitness function

We use the Minimal Generation Gap (MGG) algorithm and BXα crossover and mutation which are well-known genetic operations and were proposed to prevent the population from being occupied with the same kind of chromosomes and losing its diversity. In the MGG, a family is made by randomly selected parents in the N-th generation and their children generated by crossover operation as shown in Fig. 3. And one individual is selected from the family based on the elite or roulette selection and it is exchanged with one individual in the N-th generation to produce the N + 1 generation. Since the waveform is very sensitive to the characteristic impedance and segment length in the STL, diversity of the population in the STL decreases frequently in its evolution. We thus use the MGG to avoid diversity degradation in the evolutional STL design.

We use a fitness shown in Fig. 4. The difference area Diff between the ideal waveform I(t) and the current waveform R(t) is used for the fitness. The fitness is defined as the reciprocal of this difference area Diff.

Table 1 summarizes the GA parameters used in the design. Currently, we need about 10 h to reach 2000 generations, at which we can observe complete convergence in the evolution using a standard PC with a single 2 GHz CPU. There are more than 1000 traces in PCBs generally, but high-speed traces such as clock, data/address bus are less than 10 % of all the trace, so that it is not unrealistic for practical application even though it takes about 10 h for each STL design.

2.4 Design example

We have developed a 250 MHz scale-up prototype targeting a 1 GHz DDR memory-bus clock-distribution system (2 GHz DDR system). The scale-up prototype, in which the lengths of the transmission lines and the load capacitances are enlarged in proportion to the frequency-reduction ratio, is usually used to evaluate GHz waveforms in the MHz domain, especially if there is a possibility that the measurement equipment will affect the GHz waveforms.

Table 2 shows the resulting design of the characteristic impedance Z i , width W i ,and length L i , of each segment. We used a set of characteristic impedances from 30 to 120 Ω at intervals of 5 Ω intervals. One remarkable aspect can be seen in Table 2: the high and low characteristic impedance segments were chosen alternately in the GA.

Table 3 shows the obtained fitness, which is normalized with that of the conventional transmission line (homogeneous 50 Ω transmission line). After 2000 generations of genetic operations, the fitness defined in Fig. 4 is improved more than double successfully.

We fabricated a 250 MHz STL scale-up prototype (Fig. 5) based on the design result shown in Table 2. The lower photograph in Fig. 5 shows the STL scale-up prototype, while the upper one shows a conventional transmission line with a uniform Z of 50 Ω.

The upper waveform in Fig. 6 was observed at the target point in the conventional transmission line. The waveform is extremely distorted in both shape and amplitude. The lower waveform in Fig. 6 was observed at the same target point in the STL. The distorted waveform in the conventional transmission line (the upper waveform) is considerably improved in the STL; improvement ratio of the STL waveform amplitude to the conventional one reaches about 2.5.

3 Power integrity improvement

To decrease the power-supply voltage impedance, which is proportional to the power-supply voltage drop, decoupling capacitors are allocated in vicinity to the VLSIs at present. This design cannot work well about more than 5 GHz, and we have to solve the decoupling-capacitor allocation problem not for the vicinity of the VLSIs, but for the entire PCB area. We propose a novel design approach based on the GA also, so as to overcome this allocation problem.

3.1 Power plane model and decoupling-capacitor allocation problem

As a power plane model, we adopt the LRC-ladder circuit cell 2D-array structure as shown in Fig. 7 [3]. Assuming the number of cells in the 2D-array structure and the number of the decoupling capacitors are N × N and m, respectively, the combination of the decoupling-capacitor allocation results in the combinatorial explosion in the order of (N × N)m, which counts 1040 approximately even in the small case of N = 10 and m = 20.

Because we know some empirical allocation rules, such as “allocating decoupling capacitors as closer to LSIs as possible”, we do not have to fully search such a large search space in rather low frequency.

In the high frequency domain of 5 GHz or more, however, those empirical rules cannot work well because the wavelength of the LSI switching frequency becomes much shorter than the power plane, so that the current from the VRM (Voltage Regulation Module) to the LSI is supplied accompanying wave propagation behavior.

To map our decoupling-capacitor allocation problem onto the chromosome, we newly propose a parameter coding shown in Fig. 8: the chromosome has the same number genes, or parameters as the number of decoupling capacitors, and each gene indicates the position (i, j) in the 2D-array of power plane model. Figure 8 also shows the “crossover” operations in our application: some genes in chromosome A are randomly selected, and exchanged with the corresponding genes in chromosome B.

3.2 GA parameters and fitness function

GA parameters are summarized in Table 4, where we used simple one-point crossover and the elite selection. It takes about 30 min to reach the 100 generations using a standard PC with a single 2 GHz CPU, where the complete evolutional convergence is observed.

As a fitness function, we used the maximum power-supply voltage impedance, which is proportional to the maximum power-supply voltage drop. In the next section, the maximum power-supply voltage impedances are shown in the experimental results of power-supply voltage impedance spectra.

3.3 Experiments and results

We have carried out some experiments to show effectiveness of our design approach quantitatively. In the experiments, we use a 6 in. (15.24 cm) × 6 in. power plane that consists of two cupper metal layers with FR4 (dielectric constant ratio is 4) between them. The power plane is modeled as 50 × 50 LCR-ladder 2D-array cells as described above. Furthermore, in this experiment, to perform power-supply plane net list generation for HSPICE quickly, we used the software PGPlaneEx [4].

We simply place one VRM and VLSI onto the power plane as shown in Fig. 9 to explore and analyze the effectiveness of the GA solution for 40 decoupling capacitors of 10 μF each. The VRM and LSI are modeled as a DC 1 V constant-voltage supply and AC 1 A constant-current supply, respectively, so that the voltage measured at the LSI indicates the power impedance at the VLSI input.

Figure 10 shows the measured voltage, or power-impedance spectrum of the power plane without decoupling capacitor under the frequency range of 100 MHz to 20 GHz. A very high voltage anti-resonance, or strong peak of 37.2 Ω is measured at 4.79 GHz and some higher voltage resonances are measured at more than 10 GHz also.

Empirically, it is well known that decoupling capacitors work better as they are allocated closer to the LSI as possible. We thus chose that allocation as the initial allocation: 40 decoupling capacitors are allocated surrounding the LSI closely as shown in Fig. 9.

Figure 11 shows the measured power-impedance spectrum at initial decoupling-capacitor allocation (Fig. 9). Although some anti-resonances, or strong peaks at less than 2 GHz are suppressed well, the strongest peak of 39.0 Ω, which is stronger than in Fig. 10, is observed at 2.59 GHz. Furthermore, some stronger peaks are observed in Fig. 11 than in Fig. 10 at higher than 15 GHz. This experimental results show that the empirical allocation, or allocating decoupling capacitances as closer as possible to the LSI is not always effective in higher frequency range.

Power impedance spectrum in power plane at initial decoupling-capacitance allocation (Fig. 10)

In the decoupling capacitor allocation design using GA, we used the inverse of the strongest peak in the spectrum as the fitness. On the basis of this fitness, we evolved 100 chromosomes until 100 generations.

The obtained decoupling-capacitor allocation and its power-impedance spectrum are shown in Figs. 12 and 13, respectively. As sown in Fig. 12, the GA selects the scattered capacitors allocation, where more than 2/3 capacitors are allocated in the upper diagonal area in the power plane, which may come from the asymmetric allocations of the VLSI and the VRM on the power plane.

Power impedance spectrum in power plane at decoupling-capacitor allocation solved by GA (Fig. 11)

In Fig. 13, the strongest peak is successfully suppressed to 17.8 Ω at 13.08 GHz, and the fitness is improved more than double compared with the conventional, or initial allocation (Fig. 9) as summarized in Table 5. Furthermore, strong peaks observed in the higher frequency range more than 10 GHz are well suppressed also.

4 Conclusions

Novel design methodologies using genetic algorithms are proposed to improve the SI and the PI degradation problems on the printed circuit boards.

Those design methodologies were evaluated by a prototype and a simulation model, and improvement ratios of about 2.5 and more than 2.0 were obtained in SI and PI, respectively.

References

Li MP (2007) Jitter, noise, and signal integrity at high-speed, Prentice Hall Signal Integrity Library

Bogatin E (2010) Signal and power integrity-simplified, Prentice Hall Signal Integrity Library

Smith LD (2001) Power plane SPICE models and simulated performance for materials and geometries. IEEE Trans Adv Packag 24(3):277–287

Acknowledgments

This research was partially supported by JSPS/KAKENHI Grant Number 26289114 in Japan, and VLSI Design and Education Center (VDEC), the University of Tokyo in collaboration with Synopsys, Inc. and Keysight (Agilent) Technologies Japan, Ltd.

Author information

Authors and Affiliations

Corresponding author

About this article

Cite this article

Yasunaga, M., Yoshihara, I. An evolutionary design methodology of printed circuit boards for high-speed VLSIs. Artif Life Robotics 21, 171–176 (2016). https://doi.org/10.1007/s10015-016-0266-9

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10015-016-0266-9