Abstract

Al/AlN/p-Si diode was fabricated via thermal evaporation. The electrical properties of the structure were examined under various temperatures, illuminations, and frequencies. Temperature-dependent electrical properties were investigated using several different methods, which are the Thermionic Emission theory, Norde Function, and Cheung&Cheung Functions. The ideality factor, zero-bias barrier height, and series resistance values obtained from the Current–Voltage-Temperature plot of the diode were compared with each other. It was seen that the values obtained from three different methods were in good agreement with each other. Additionally, current–voltage measurements depending on the illumination intensity showed that the designed structure responds to light. The time-dependent photocurrent of the structure was examined with the switch on and off. The root mean square value for Aluminium nitride interfacial layer was found to be 4 nm from the Atomic Force Microscope measurements. Experimental results revealed that the fabricated structure is a candidate for sensing applications such as temperature or light sensors.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Because of properties such as carrier mobility and direct bandgap, the group III–V binary compounds are used in a variety of optoelectronic and nanoelectronic applications [1,2,3]. These compounds consist of elements listed in groups III and V of the periodic table. The III–V binary compounds are expressed as XY, where X is group III elements (Al, B, Ga, In) in the periodic table and Y is group V elements (N, P, As, Sb) in the periodic table. The III-nitride is formed by the combination of nitrite from group V elements and at least one element from group III elements. These compounds are particularly useful in optoelectronic device technology, such as light-emitting diodes (LEDs), because they have a wide bandgap that spans the visible and ultraviolet spectrums [4, 5]. For example; Wu and co-workers [4] stated that Aluminium nitride (AlN) may be a promising compound for low-cost and high-quality LEDs. These materials can be used as absorber layers to optimize efficiency in solar cells [5].

AlN, an III-nitride group member, has piezoelectric properties, extreme electrical behavior, and high thermal conductivity (Ҡ = 285 W (m K)−1) [6,7,8,9,10]. It also has a wurtzite crystal structure and a wide bandgap (6.2 eV) at room temperature, which is one of the largest bandgap semiconductor materials [11]. Devices with such a wide bandgap interface have the advantage of being chemically and thermally stable, as well as being able to operate in harsh physical environments. Due to its promising properties, AlN has an important place in technology applications. AlN has been widely used in various electronic and photonic devices with the contribution of its optical properties as well as piezoelectric properties. In the past few years, studies have been carried out to explore the potential of AlN [12,13,14,15]. For example, Esteves et al. [15] showed that AlN can be used in elevated temperature micro-scale devices. Taniyasu et al. [16] demonstrated the development of the AlN PIN (p-type/intrinsic/n-type) homojunction LED with an emission wavelength of 210 nm [16]. With the revelation of the above-mentioned features, some researchers were fabricated Al/AlN/p-Si MIS structures [17,18,19,20]. Kong et al. [18] shown a good charge holding effect with long-term charge keeping at ± 3 V, in their study of the charge storage properties of Al/AlN/p-Si metal–insulator-semiconductor (MIS). Also, they [18] stated that with this charge storage behavior, the MIS structure can be promising in improving performance in optoelectronics and memories applications. Altuntaş et al. [20] studied the electric-field-dependent current transport mechanisms of Al/AlN/p-Si MIS, and showed that the MIS structure has five current conduction mechanisms, which are ohmic conduction, Schottky emission, Frenkel–Poole emission, trap assisted tunneling, and Fowler–Nordheim tunneling. In addition, Altuntaş et al. [20] stated that this MIS structure can be a potential for various electronic applications thanks to its different physical properties. The main subject of analyses in these studies is that Al/AlN/p-Si structures can be used in various device technologies, such as optoelectronic or electronic devices.

Studies and knowledge on the electrical properties of AlN/Si-based devices are limited to an only condition environment. That is, studies on these electrical properties suffer from knowledge and behavior in various physical conditions. In this letter, the electrical properties of the Al/AlN/p-Si diode prepared with the help of thermal evaporation were investigated under various physical conditions, which are temperature (60–320 K), illumination (0–100 mW∙cm−2), and frequency (5–5 MHz). In this way, the use of AlN in various electronic and optoelectronic applications was investigated. Additionally, the AlN interface is examined for the effect on basic diode parameters such as ideality factor (n), zero-bias barrier height (ΦB0), and series resistance (Rs) and is to be compared with the literature. Temperature-dependent electrical properties were examined separately using Thermionic Emission (TE) theory, Norde Function (NF), and Cheung&Cheung Functions (CCF) and compared with each other.

2 Experimental procedures

The thermal evaporation system gave schematic representation in Fig. 1a was used at all stages of the structure’s fabrication. First, a p-type silicon wafer with a 525 μm thickness and 1–10 Ω.cm properties purchased from Sigma-Aldrich Company was cut at 1 × 1 cm square and chemically cleaned using standard RCA1 and RCA2 processes. Then, cleaned p-Si was transferred to the thermal evaporation system. Here, 1 mg of Al wire (diameter 1.0 mm, 99.999%) was evaporated on the unpolished surface of p-Si at about 1.3 × 10–3 Pa in the thermal evaporation system. Single surface coated p-Si was annealed at 450 °C for 5 min in the dry N2 atmosphere to obtain low-resistance contact. The AlN in powder form, which was used as the interface layer, was commercially purchased from Sigma Aldrich Company. AlN (1 mg) was evaporated with the thermal evaporation system at about 1.3 × 10–3 Pa. The thickness of the AlN interfacial layer is estimated to be about 106 nm from the oxide capacitance measurement in the strong accumulation region at a high frequency (= 1 MHz) [21]. Finally, to obtain a rectifier contact, commonly known as a Schottky contact, a circular mask was used. The 1 mg of Al wire (diameter 1.0 mm, 99.999%) was evaporated at about 1.3 × 10–3 Pa in thermal evaporation on the interfacial coated surface of p-Si. The thickness of the Al rectifier contact was obtained as 100 nm. Thus, the fabrication of the Al/AlN/p-Si was completed. The schematic and energy band diagram of the fabricated structure are given in Fig. 1b, c. The Current–Voltage–Temperature (I–V–T) measurements were performed using a Keithley 2400 Source Meter in the temperature range from 60 to 340 K. The illumination-dependent electrical measurements were carried out using a 150–300 W UV 16S-Series Solar Simulator, which can produce solar radiation in the 290–400 nm range. The Capacitance (C)–Voltage (V) and Conductance (G/w)–Voltage (V) measurements were performed using the HP 4192A LF Impedance Analyzer in the frequency range from 5 to 5000 kHz. Atomic Force Microscopy (AFM) measurements were carried out using a Park Systems XE-100E in non-contact mode and a 100 µm × 100 µm scanner.

3 Experimental results and discussion

3.1 Morphology properties

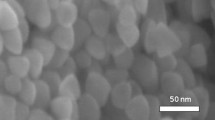

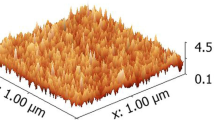

Atomic Force Microscopy (AFM) roughness measurements give information about surface roughness. AFM images of the interfacial layer at 40 × 40 μm2 square are given in Fig. 2. It was observed that the surface morphology of the AlN interfacial layer is homogeneous. Due to the interface coating method used, it is coated so homogeneously. The root mean square (RMS) value was obtained as 4 nm. This value is quite low and is suitable for thin-film studies [22]. Additionally, the obtained value shows that the material surface is of good quality and thermal evaporation is an important method for homogeneous interfacial coating [23].

3.2 The temperature-dependent electrical properties

The temperature-dependent electrical properties of the structure were performed in the temperature range of 60–340 K with an increment of 20 K. Figure 3 shows the I–V–T plot of the diode. As can be seen from this figure, the current decreases with decreasing temperature both in reverse (V < 0) and forward (V > 0) bias. Such behavior of the current can be attributed to generation-recombination and interfacial layer, which is AlN between metal (Al) and semiconductor (p-Si). Additionally, the regular increase in the current value with the increasing temperature shows that the fabricated structure is very sensitive to the temperature. As shown in Fig. 3, the structure has a relatively high leakage current for all temperatures. When metal and semiconductor are contacted, a space charge region (W) is formed near the contact of the semiconductor (see Fig. 1c) at the end of the thermal equilibrium. Since there are no free charge carriers in the region, the region is highly resistive and insulating. The presence and defects of this region limit the flow of charge carriers across the junction, which as a result causes the device's performance to degrade [21, 24, 25]. Additionally, Abdallah et al. [26] stated that the grain size should be small to contain the depletion layer, otherwise the larger leakage may be higher.

The relationship between applied voltage and current in forward bias is defined by TE as follows [27];

where A represents diode area and A* represents Richardson constant (= 32 A.cm−2 K−2 for p-Si). The curly bracket of Eq. 1 represents the saturation current (I0), ΦB0 is the barrier height, and n is the ideality factor. These values can be calculated from the intercept and slope of the linear part of the I-V-T plot for each temperature. The calculated n, I0, and ΦB0 values of the structure for each temperature value are given in the TE part of Table 1. As the temperature increases from 60 to 340 K, the ΦB0 value increases from 0.146 eV to 0.680 eV, whereas the n value decreases from 6.179 to 2.105. The reasons for the high n value are the interface layer, barrier height inhomogeneity, and interface recombination [28, 29]. There are studies on the high ideality factor in the literature [30,31,32,33]. For example, Arslan et al. [31] fabricated an (Au/Ni)/HfAlO3/n-Si metal–insulator-semiconductor junction and they found that the value of n for the junction varied from 22.93 at 80 K to 3.94 at 360 K. The series resistance (Rs) of a diode can be calculated using Ohm's Law (Ri = VF/IF) at a high forward bias. The Rs values at (+ 2 V) of the structure are given in the Ohm's Law part in Table 1. As can be seen from Table 1, the Rs value at 340 K is about 10 times smaller than its value at 60 K. Such Rs behavior can be explained by an increase in the number of free carriers gaining thermal energy and a decrease in the forbidden band gap of Si as temperature rises [27, 34,35,36].

The relative performance of the electrical properties with previously reported structures of the fabricated Al/AlN/p-Si structure in this study is listed in Table 2. For instance, in 2009, Chuah et al. [37] fabricated Ni/AIN/n-Si photodiode using a molecular beam epitaxy system and investigated the electrical characteristics of the fabricated photodiodes. They calculated n, I0, and ΦB0 to be 1.79, 6.88 × 10–6 A, and 0.71 eV, respectively. Compared to the n obtained by Chuah et al. [37], the n value obtained in this study is greater. This may be due to the high density of interface state, series resistance, and recombination generation.

Another method used to calculate the main diode parameters such as ΦB0 and Rs is a method developed by H. Norde [40, 41]. According to the method, barrier height and series resistance can be determined using F(V) function (Eq. (4)) and Eqs. (5–6).

where γ denotes the smallest integer greater than the ideality factor, F(Vmin) represents the minimum value of F(V) in the F(V)-V plot, Vmin represents the minimum value of V in the F(V)-V plot, and Imin represents the current value corresponding to Vmin. Using Eq. (5), the F(V)-V plot of the structure for each temperature was drawn and given in Fig. 4. As can be seen in the figure, the F(V)-V plot of the structure has an F(Vmin) and Vmin minimum value varying between 0.0 V and 0.3 V for each temperature. Using F(Vmin), Vmin, and Imin values and Eqs. (5–6), ΦB0, and Rs values were obtained and given in Nord’s Function part in Table 1.

Alternately, the n, ΦB0, and Rs can also be calculated using Cheung&Cheung Functions (CCF), which correspond to Eqs. (7) and (8) [42]. The n and Rs are determined using the slope and intercept values of the linear part of dV/dln(I)-I for each temperature. The ΦB0 and Rs are obtained using the slope and intercept values of the linear part of H(I)-I for each temperature. Equation (7) is known as the CCF’s 1st function, whereas Eq. (8) is known as the CCF's 2nd function.

Figure 5a, b shows dV/dln(I)-I and H(I)-I plots of the structure for each temperature, respectively. As can be seen from the figures, both plots have linear regions. Additionally, the linearity of dV/dln(I)-I and H(I)-I plots in the 60–120 K range is given in the inset of Fig. 5a, b, respectively. The n, ΦB0, and Rs values determined using the CCF’s 1st and 2nd functions for each temperature were given by the CCF part in Table 1.

The temperature-dependent ΦB0 and Rs values determined using TE, Ohm’s Law, NF, and CCF's 1st and 2nd functions are given in Fig. 6a, b, respectively. As shown in Fig. 6a, the ΦB0 determined using three different methods is almost compatible with each other. The value of ΦB0 obtained by using CCF’s 2nd function is smaller than that obtained by using TE and NF. This difference is because the used methods have different I–V regions. That is, TE and NF are applied to the full forward bias region of the I–V characteristics, whereas CCF is applied to dates where the I–V characteristics start to deviate from linearity. Additionally, the ΦB0 values determined from these methods increase as temperatures increase. Such a relationship of ΦB0 to temperature can be explained by other current conduction mechanisms other than TE, such as Thermionic Field Emission (TFE) and Field Emission (FE). TFE and TE dominate at temperatures above room temperature, whereas TFE and TE dominate at temperatures below room temperature. Therefore, the obtained ΦB0 corresponds to the apparent barrier height (BH) for different temperatures and voltages, rather than the average value of BH. As shown in Fig. 6b, the Rs was determined using four different methods. The Rs values decrease as the temperature increases. The Rs values obtained by using different methods are almost compatible with each other, except for low temperatures. This small difference is attributed to the fact that each method has different regions of I-V regions and voltage dependence of BH [43].

The width of the depletion region (WD) plays a significant role in the electric performance of structures with a thin film between metal and semiconductor. The WD (= (2εsεoVd/qNA/D)1/2) is affected by the semiconductor permittivity, diffusion potential, and acceptor or donor atom concentration (NA or ND) [44, 45]. As the temperature increases, the ionic region formed at the junction of metal and semiconductor begins to neutralize, and the mobility of the carriers, which is determined by the density of NA or ND, increases [45,46,47]. Thus, the WD decreases with increasing temperature and conductivity increases. When WD is narrow, it can cause increased recombination, which negatively affects electrical performance. However, when the width of the depletion region is long, it is an advantage to the collection of photo-generated charge carriers [48].

3.3 The illumination intensities dependent on electrical properties

The illumination intensity-dependent I–V plot of the structures is given in Fig. 7. As shown in this figure, the structure reacts to light depending on various illumination intensities. Especially in the reverse bias region, it showed much more reaction than the forward bias region, and this reaction increased with the illumination intensity. The regular increase in the current value with the increasing illumination intensity shows that the fabricated structure is very sensitive to the illumination intensity. This is proof that the structure exhibits photoconductivity properties. When the structure is exposed to various illumination intensities, the concentration of majority charge carriers and the value of the current increase. Table 3 shows n, I0, ΦB0, and Rs determined by using Eqs. (1)–(3) and Ohm’s Law for the structures under various illumination intensities. As shown in Table 3, the n and I0 increase whereas ΦB0 and Rs decrease as the illumination intensity increases. The behavior of the n and ΦB0 under various illumination intensities can be explained by the generation and separation of electron–hole pairs, barrier inhomogeneity between metal and semiconductor, and the molecular restructuring and reordering of surface states [49, 50]. Moreover, the n value has a dramatically increment due to the voltage drop across the large Rs while the ΦB0 has a slight decrease due to the bandgap narrowing as increasing illumination intensity.

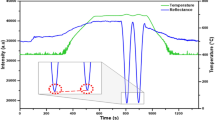

The photocurrent–time relationship of the structure was performed at various illumination intensities and − 2 V and was given in Fig. 8. When the switch is opened, the photocurrent is suddenly increased for various illumination intensities. The current has reached its maximum value of 5.77, 6.82, 7.37, 7.74, and 7.92 mA for 30, 40, 60, 80, and 100 mW cm−2, respectively, due to the increasing free charge carriers. This behavior is an indication that the device depends on the illumination intensity.

3.4 The frequency-dependent electrical properties

To investigate the effects of the AlN interfacial layer on electrical characteristics, capacitance–voltage (C–V) and conductance–voltage (G/w-V) measurements were performed over a wide frequency and bias voltage range. Figure 9 shows the low and high-frequency C–V and G/ω–V plots of the structure. As can be seen from these figures, the figures have inversion (− 1 ≤ V ≤ 1), depletion (1 ≤ V ≤ 4), and accumulation (4 ≤ V ≤ 6) regions just like in an MIS structure. Whereas the values of C and G/ω are almost independent of the frequency in the inversion region, their values decrease with the increase in frequency in the depletion and accumulation regions. The regular increase in the capacitance and conductance values with the decreasing frequency shows that the fabricated structure is very sensitive to the frequency.

According to Nicollian and Brews [21], the resistance (Ri) of a diode is given as follows;

where ω is the angular frequency (= 2πf), and Cm and Gm correspond to the measured capacitance and conductance, respectively. The series resistance (Rs), which affects the electrical properties of a diode, is obtained by using values of Cm and Gm in the strong accumulation region [21]. The Ri-V plot drawn as a function of the low and high-frequency for the structure is given in Fig. 10a, b, respectively. As can be seen from these figures, the Ri value has a peak in the inversion region for each frequency. The intensity of the peak shifts to the depletion region with increasing frequency, and the intensity of the peak decreases. The peak at high frequencies has two separate maximum points, especially in the inversion region. The intensity of the first peak can be attributed to the surface polarization, whereas the intensity of the second peak can be attributed to the presence of the interfacial layer [51]. Additionally, the Ri value is almost independent of frequency due to the relaxation mechanisms between the interfacial layer and p-Si surface in the accumulation region [52]. The frequency-dependent Rs value of the structure at + 6 V is shown in Fig. 11. As can be seen from the figure, the Rs value decreases with increasing frequency.

4 Conclusions

We fabricated an Al/AlN/p-Si diode via thermal evaporation and analyzed the electrical performance of the structure. The AFM result shows that the interfacial layer coated via thermal evaporation is quite homogeneous. The RMS value for AlN, which is the interfacial layer, was found to be 4 nm with the help of AFM. The main electronic properties such as n, ΦB0, and Rs of the structure at different temperatures were calculated using TE, NF, and CCF and compared with each other. In addition, these main electrical parameters were also examined and analyzed based on various illumination intensities. Experimental results revealed that the main electronic parameters are very sensitively dependent on both temperature and illumination intensity. When the graphs obtained for temperature, frequency, and light intensity are examined, it is seen that various electrical characteristics such as current and capacitance change with sensitivity according to the conditions of the physical condition which shows the unique characteristics of this Al/AlN/p-Si MIS device. That is, the fabricated structure responds with high sensitivity to both temperature and illumination intensity. This proves that the fabricated structure, which has been designed and whose electrical properties have been studied, may be a candidate for sensing applications such as Schottky-type temperature or light sensors.

Data availability

Authors can confirm that all relevant data are included in the article and/or its supplementary information files.

References

X. Lü, S. He, H. Lian, S. Lv, Y. Shen, W. Dong, Q. Duan, Structural, electronic, and optical properties of pristine and bilayers of hexagonal III-V binary compounds and their hydrogenated counterparts Appl. Surf. Sci. 531, 147262 (2020)

D. Çakır, D. Kecik, H. Sahin, E. Durgun, F.M. Peeters, Realization of a p–n junction in a single layer boron-phosphide Phys. Chem. Chem. Phys. 17, 13013–13020 (2015)

T. Akiyama, T. Kawamura, T. Ito, Computational discovery of stable phases of graphene and h-BN van der Waals heterostructures composed of group III–V binary compounds Appl. Phys. Lett. 118, 023101 (2021)

H. Wu, R. Zheng, Y. Guo, Z. Yan, Fabrication and characterisation of non-polar M-plane AlN crystals and LEDs Mater. Res Innov (2015). https://doi.org/10.1179/1432891714Z.0000000001268

A.R. Acharya, Group III–nitride semiconductors: preeminent materials for modern electronic and optoelectronic applications. Himal. Phys. 5, 22–26 (2015)

J. Li, K.B. Nam, M.L. Nakarmi, J.Y. Lin, H.X. Jiang, P. Carrier, S.-H. Wei, Band structure and fundamental optical transitions in wurtzite AlN. Appl. Phys. Lett. 83, 5163–5165 (2003)

G.A. Slack, R.A. Tanzilli, R.O. Pohl, J.W. Vandersande, The intrinsic thermal conductivity of AIN. J. Phys. Chem. Solids 48, 641–647 (1987)

R. Beiranvand, S. Valedbagi, Electronic and optical properties of advance semiconductor materials: BN. AlN and GaN Nanos. First Principles Optik (Stuttg). 127, 1553–1560 (2016)

N. Sanders, D. Bayerl, G. Shi, K.A. Mengle, E. Kioupakis, Electronic and optical properties of two-dimensional GaN from first-principles. Nano. Lett. 17, 7345–7349 (2017)

C. Xiong, W.H.P. Pernice, X. Sun, C. Schuck, K.Y. Fong, H.X. Tang, Aluminum nitride as a new material for chip-scale optomechanics and nonlinear optics New. J. Phys. 14, 095014 (2012)

H. Yamashita, K. Fukui, S. Misawa, S. Yoshida, Optical properties of AlN epitaxial thin films in the vacuum ultraviolet region. J. Appl. Phys. 50, 896–898 (1979)

I. Karami, S.A. Ketabi, Tuning of the electronic and optical properties of AlN monolayer by fluorination: Study of many-body effects. Comput. Condens. Matter 28, e00564 (2021)

N. Ben Hassine, D. Mercier, P. Renaux, G. Parat, S. Basrour, P. Waltz, C. Chappaz, P. Ancey, S. Blonkowski, Dielectrical properties of metal-insulator-metal aluminum nitride structures: Measurement and modeling. J. Appl. Phys. 105, 044111 (2009)

D. Kecik, C. Bacaksiz, R.T. Senger, E. Durgun, Layer- and strain-dependent optoelectronic properties of hexagonal AlN. Phys. Rev. B 92, 165408 (2015)

G. Esteves, S.D. Habermehl, P.J. Clews, C. Fritch, B.A. Griffin, AlN/SiC MEMS for high-temperature applications. J. Microelectromech. Syst. 28, 859–864 (2019)

Y. Taniyasu, M. Kasu, T. Makimoto, An aluminium nitride light-emitting diode with a wavelength of 210 nanometres. Nature 441, 325–328 (2006)

Z. Azman, N. Nayan, M.M.I.M. Hasnan, A.S.A. Bakar, M.H. Mamat, M.Z.M. Yusop, Impedance spectroscopy analysis of Al/100-plane AlN/p-Si MIS prepared by HiPIMS method for tailoring dielectric properties. Int. J. Nanotechnol. 19, 404–417 (2022)

Y.C. Kong, L.Q. Hu, Y.D. Zheng, C.H. Zhou, C. Chen, S.L. Gu, R. Zhang, P. Han, R.L. Jiang, Y. Shi, Charge storage characteristics in Al/AlN/Si metal–insulator–semiconductor structure based on deep traps in AlN layer. Appl. Phys. A 90, 545–548 (2008)

H. Altuntas, T. Bayrak, S. Kizir, A. Haider, N. Biyikli, Electrical conduction and dielectric relaxation properties of AlN thin films grown by hollow-cathode plasma-assisted atomic layer deposition. Semicond. Sci. Technol. 31, 75003 (2016)

H. Altuntas, C. Ozgit-Akgun, I. Donmez, N. Biyikli, Current transport mechanisms in plasma-enhanced atomic layer deposited AlN thin films. J. Appl. Phys. 117, 155101 (2015)

E.H. Nicollian, J.R. Brews, Metal oxide semiconductor (MOS) Physics and Technology (John Wiley & Sons, New York, 1982)

İ Orak, A. Karabulut, E. Yiğit, Ö. Sevgili, A. Ruşen, F. Ozel, The diode and photodiode performances of BaZrO3 perovskite-based device under the influence of thermal and light external stimuli. Sensors Act. A Phys. 337, 113413 (2022)

Ö. Sevgili, F. Özel, A. Ruşen, E. Yiğit, İ Orak, The surface and electrical properties of the Al/Ba2P2O7/p-Si heterojunctions in wide range of temperature and frequency. Surfaces and Interfaces 28, 101637 (2022)

A.Q. Alosabi, A.A. Al-Muntaser, M.M. El-Nahass, A.H. Oraby, Characterization and photovoltaic performance analysis of Na2Pc/p-Si heterojunction solar cell. J. Mater. Sci. Mater. Electron. 33, 25329–25341 (2022)

M.M. Makhlouf, H.M. Zeyada, Effect of annealing temperature and X-ray irradiation on the performance of tetraphenylporphyrin/p-type silicon hybrid solar cell Solid. State. Electron. 105, 51–57 (2015)

B. Abdallah, S. Al-Khawaja, A. Alkhawwam, I.M. Ismail, Deposition and current conduction of mixed hexagonal and cubic phases of AlN/p-Si films prepared by vacuum arc discharge: effect of deposition temperature. Thin Solid Films 562, 152–158 (2014)

S.M. Sze, Physics of semiconductor devices (Willey, New York, 1981)

H.C. Card, E.H. Rhoderick, Studies of tunnel MOS diodes I. Interface effects in silicon Schottky diodes. J. Phys. D. Appl. Phys. 4, 1589 (1971)

J.P. Sullivan, R.T. Tung, M.R. Pinto, W.R. Graham, Electron transport of inhomogeneous Schottky barriers: A numerical study. J. Appl. Phys. 70, 7403–7424 (1991)

Ş Altindal, Ö. Sevgili, Y. Azizian-Kalandaragh, The structural and electrical properties of the Au/n-Si (MS) diodes with nanocomposites interlayer (Ag-Doped ZnO/PVP) by using the simple ultrasound-assisted method IEEE Trans. Electron Devices 66, 3103–3109 (2019)

E. Arslan, Y. Badali, M. Aalizadeh, Ş Altındal, E. Özbay, Current transport properties of (Au/Ni)/HfAlO3/n-Si metal–insulator–semiconductor junction. J. Phys. Chem. Solids 148, 109758 (2021)

A. Kaymaz, E. Evcin Baydilli, H. Uslu Tecimer, Ş Altındal, Y. Azizian-Kalandaragh, Evaluation of gamma-irradiation effects on the electrical properties of Al/(ZnO-PVA)/p-Si type Schottky diodes using current-voltage measurements. Radiat Phys. Chem. 183, 109430 (2021)

S. Demirezen, H.G. Çetinkaya, M. Kara, F. Yakuphanoğlu, Ş Altındal, Synthesis, electrical and photo-sensing characteristics of the Al/(PCBM/NiO: ZnO)/p-Si nanocomposite structures. Sensors Actuators A Phys. 317, 112449 (2021)

H. Durmuş, M. Yıldırım, Ş Altındal, On the possible conduction mechanisms in Rhenium/n-GaAs Schottky barrier diodes fabricated by pulsed laser deposition in temperature range of 60–400 K. J. Mater. Sci. Mater. Electron. 30, 9029–9037 (2019)

S. Chand, J. Kumar, Current transport in Pd2Si/n-Si(100) Schottky barrier diodes at low temperatures. Appl. Phys. A Mater. Sci. Process. 63, 171–178 (1996)

Ö. Sevgili, On the examination of temperature-dependent possible current-conduction mechanisms of Au/(nanocarbon-PVP)/n-Si Schottky barrier diodes in wide range of voltage. J. Mater. Sci. Mater. Electron. 32, 10112–10122 (2021)

L.S. Chuah, Z. Hassan, H. Abu Hassan, C.W. Chin, S.M. Thahab, S.C. Teoh, Silicon schottky barrier photodiodes with a thin AlN nucleation layer. Microelectron Int. 26, 41–44 (2009)

Z. Azman, N. Nayan, M.M.I. Megat Hasnan, N. Othman, A.S. Bakri, A.S. Abu Bakar, M.H. Mamat, M.Z. Mohd Yusop, Improvement of c-axis (002) AlN crystal plane by temperature assisted HiPIMS technique Microelectron. Int. 38, 86–92 (2021)

M.Z.M. Yusoff, A. Mahyuddin, Z. Hassan, Fabrication of AlN/GaN MSM photodetector with platinum as schottky contacts. Mater Res. Express 6, 115913 (2019)

H. Norde, A modified forward I-V plot for Schottky diodes with high series resistance. J. Appl. Phys. 50, 5052–5053 (1979)

K.E. Bohlin, Generalized Norde plot including determination of the ideality factor. J. Appl. Phys. 60, 1223–1224 (1986)

S.K. Cheung, N.W. Cheung, Extraction of Schottky diode parameters from forward current-voltage characteristics. Appl. Phys. Lett. 49, 85–87 (1986)

O. Çiçek, Ş Altındal, Y. Azizian-Kalandaragh, A highly sensitive temperature sensor based on Au/Graphene-PVP/n-Si type schottky diodes and the possible conduction mechanisms in the wide range temperatures. IEEE Sens. J. 20, 14081–14089 (2020)

O. Sevgili, The investigation of the electrical characteristics and photo-response properties of the Al/(CMAT)/p-Si structures. Solid State Sci. 117, 106635 (2021)

S.A. Dinca, E.A. Schiff, B. Egaas, R. Noufi, D.L. Young, W.N. Shafarman, Hole drift mobility measurements in polycrystalline CuIn 1-xGaxSe2. Phys. Rev. B Condens. Matter Mater. Phys. 80, 235201 (2009)

M.M. Makhlouf, H. Khallaf, M.M. Shehata, Impedance spectroscopy and transport mechanism of molybdenum oxide thin films for silicon heterojunction solar cell application. Appl. Phys. A Mater. Sci. Process. 128, 1–13 (2022)

A. Bengi, H. Uslu, T. Asar, Ş Altındal, S.Ş Çetin, T.S. Mammadov, S. Özçelik, Temperature dependent admittance spectroscopy of GaAs/AlGaAs single-quantum-well laser diodes (SQWLDs). J. Alloys Compd. 509, 2897–2902 (2011)

J. Li, H. Wang, M. Luo, J. Tang, C. Chen, W. Liu, F. Liu, Y. Sun, J. Han, Y. Zhang, 10% Efficiency Cu2ZnSn(S, Se)4 thin film solar cells fabricated by magnetron sputtering with enlarged depletion region width Sol. Energy Mater. Sol. Cells 149, 242–249 (2016)

H.G. Çetinkaya, H. Tecimer, H. Uslu, Ş Altindal, Photovoltaic characteristics of Au/PVA (Bi-doped)/n-Si Schottky barrier diodes (SBDs) at various temperatures Curr. Appl. Phys. 13, 1150–1156 (2013)

E. Yükseltürk, O. Surucu, M. Terlemezoglu, M. Parlak, Ş Altındal, Illumination and voltage effects on the forward and reverse bias current–voltage (I-V) characteristics in In/In2S3/p-Si photodiodes. J. Mater. Sci. Mater. Electron. 32, 21825–21836 (2021)

Ç. Bilkan, Y. Azizian-Kalandaragh, Ş Altındal, R. Shokrani-Havigh, Frequency and voltage dependence dielectric properties, ac electrical conductivity and electric modulus profiles in Al/Co3O4-PVA/p-Si structures. Phys B Condens. Matter 500, 154–160 (2016)

M. Ulusoy, Ş Altındal, P. Durmuş, S. Özçelik, Y. Azizian-Kalandaragh, Frequency and voltage-dependent electrical parameters, interface traps, and series resistance profile of Au/(NiS:PVP)/n-Si structures. J. Mater. Sci. Mater. Electron. 32, 13693–13707 (2021)

Acknowledgements

This work was produced from project (Number: BAP-SHMYO.2021.002) supported by The Scientific Research Projects Coordination Unit of Bingol University.

Funding

Bingöl Üniversitesi, BAP-SHMYO.2021.002, İkram Orak.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that there is no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Yiğit, E., Sevgili, Ö. & Orak, İ. Electrical properties of Al/p-Si diode with AlN interface layer under temperature and illumination stimuli for sensing applications. Appl. Phys. A 129, 194 (2023). https://doi.org/10.1007/s00339-023-06432-4

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s00339-023-06432-4