Abstract

Malfunctioning of islanding detection algorithms leads to system instability, failure of reclosing, and damage to load-side equipment. It also threatens security personnel. Therefore, islanding detection is an essential task for the proper functioning of the distribution system. In this paper, an islanding detection technique is presented for a grid-connected distributed power generation system. The proposed islanding detection technique is based on the change in superimposed positive sequence apparent power (CSPSAP). The CSPSAP-based islanding detection technique discriminates islanding and non-islanding events. The accessibility of positive sequence components makes the technique suitable for islanding detection for a wide range of active and reactive power mismatches. It works effectively in zero power mismatch conditions. The effectiveness of the proposed technique is verified for islanding events in cases of distributed generation disconnection with the inclusion of noise, various irradiances, and unbalanced load. Even the proposed technique proves its efficacy under various non-islanding events such as capacitor switching, different fault cases, and load switching. The impact of the proposed technique is also validated in cases of islanding and non-islanding under weak grid systems. The proposed islanding detection technique is fast due to the utilization of local measured parameters at the point of common coupling and does not have power quality degradation issues. Effects of the false detection zone and non-detection zone are also discussed with regard to the proposed technique. The proposed technique is also validated on the real-time platform of the OPAL-RT. MATLAB 2018a software is considered to model and simulate a microgrid.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

The microgrid has emerged as a new trend in the existing power system, which involves renewable energy sources as generating units. The number of renewable energy sources connected to the grid has been increasing which results in an increased number of challenges regarding safety as well as security. The distributed generation (DG) acts as a local generator as the grid is connected or disconnected to the distribution system [1]. In such a system, when the main grid is disconnected due to any fault or any other type of interruption, the power is supplied by the local generators. A grid disconnection situation is called islanding, which is responsible for the flow of renewable energy toward the grid. The unexpected islanding is a threat to the safety of the microgrid. To ensure the safety of relevant personnel and equipment, unintentional islanding is strictly prohibited. Therefore, islanding detection is one of the main problems of the normal operation of the microgrid. As described in IEEE STD 1547-2018 [2], islanding should be detected within 2 s and the permissible limit of operating voltage at the point of common coupling (PCC) should be between 88 and 110% of nominal voltage. The aforementioned situations compel to detect the islanding condition and make an islanding detection algorithm suitable for differentiation between non-islanding situations to islanding situations.

2 Literature review

Remote and local techniques are general classifications of the islanding detection schemes. Local islanding detection techniques (IDTs) are further classified into active, passive, and hybrid techniques. A dedicated communication system between DGs, grids, and substations is utilized to implement the remote IDTs. Communication-based techniques comprise technologies such as SCADA [3], direct transfer trip [4], and power line signaling [5] for protection and power quality monitoring purposes. Synchronized data are utilized in the calculation of the difference between the weighted principal component analyses of parameters [6]. In this method, multi-resolution TEO with Q statistics is exploited to identify islanding. In [7], the utilization of PMU is discussed for communication in microgrids. In this, the phasor data concentrator collects and processes the data and is used for system monitoring, control, protection, and action required in contingencies. Communication-assisted IDTs do not have any impact on power quality. However, they are not reliable as communication system failure, require high computational facilities, and are expensive for implementing on a small level.

The feeder of the power distribution system sends a signal obtained from the wavelet transform through the power line signaling to the DG terminal [5]. If the DG terminal does not detect any signal, it is an indication of a non-islanding event. These schemes have a very less non-detection zone (NDZ), but these techniques require high computational speed to achieve the highest possible accuracy and are very expensive to implement. In [8], an injected reactive power is obtained through the product of adaptive gain, slip frequency, and square of PCC per unit voltage. Islanding is detected by monitoring the change in slip frequency due to the injection of this reactive power. In this case, the islanding detection time is 0.24 s. In [9], a continuous high-frequency voltage is injected into the master inverter to detect the islanding as this scheme is used for parallel connected DGs. This scheme works well and decides the new master inverter if the existing master inverter fails. However, the availability of high-frequency signals and the transition of the slave inverter to the master inverter is also required to improve THD and resolve the issue of computational complexity. In [10], to resolve the mutual influence of THD on inverters, high-frequency transients are injected as a perturbation for multi-DG systems using high-frequency impedance to identify islanding. However, such schemes do not provide good results for variable impedance situations. Low NDZ is the main advantage of active IDTs. General challenges such as instability, false tripping, and reduction of power quality should be discussed and resolved for active techniques.

In local techniques, passive techniques use the local measurements of parameters/indices such as voltage, current, impedance, frequency, and THD to identify the islanding event. These parameters/indices are compared to a set threshold so that algorithms based on these parameters can detect the islanding. The numerous methods of islanding event detection [11,12,13] discussed in the literature are the rate of change of frequency (ROCOF) [14, 15], over/under voltage [16], over/under frequency, empirical mode decomposition [17], wavelet transform [18], rate of change of reactive power [19], voltage phase angle [20], estimated power frequency ratio [21], and monitoring of reverse power [22]. These IDTs are easy to implement, faster, and do not issue power quality. However, large NDZ is the measure issue with such schemes.

In passive methods, NDZ can be reduced with the extraction of some features of parameters and also a combination of the aforementioned techniques. The passive IDT is designed for one-cycle control of a single-phase inverter based on the feedback mechanism system, which drives the PCC voltage beyond its permissible limit for a larger period. It activates the UVP/OPV and helps to disconnect the inverter [23]. However, it is tested only for single-phase inverter cases. In [24], the difference between frequency-dependent impedance and measured impedance on PCC provides information of islanding detection. This technique is not tested for noise in the signal, and it does not work well for high-impedance variation situations. A sensitivity index based on a change in frequency with a change in reactive power indicates the islanding if it violates its upper and lower limits [25]. In [26], an index based on the model transformation of input voltage is employed to detect islanding. A time-varying filter-based empirical mode decomposition of the voltage signal is discussed in [27]. The teaser energy operator (TEO) of the decomposed signal is used to detect the islanding. However, efficacy is affected by the fixed set threshold for fault resistance beyond 3Ω.

Many aforementioned passive IDTs have challenges to set the threshold. In [12], two thresholds are decided on the basis of prior knowledge based on network size and unbalancing. In [15], the threshold is set at 1.92 times of rated voltage for voltage-based IDT. The information on the proper setting of threshold selection is missing. In [27, 28], a large number of simulations of islanding and non-islanding conditions are required to set the threshold. In [29], a proper formula based on rated voltage and rated power is provided. The proper threshold selection process is a very crucial part in passive islanding detection techniques. If the threshold is set at low values, misdetection takes place, and if it is set at high value, a delay in detection time may arise. The threshold selection process should be easy.

Passive techniques are preferred to detect islanding due to their simplicity, low-cost implementation, and fast action. For fast and accurate operation, a passive IDT based on the change in CSPSAP is presented in this paper. Apparent power is calculated using voltage and current measurements on PCC. An index CSPSAP is compared with a set threshold to identify the islanding event (IE) and discrimination between IE and NIE conditions. A threshold selection process is also provided.

The main objective of this paper is to design the passive islanding event detection technique for improved and fast response in zero APM and RPM conditions. Table 1 shows a comparison of the proposed IDT with several existing techniques.

The innovation and significance of the proposed IDT are as follows:

-

The proposed IDT is designed based on local measurements of voltage and current. Therefore, it is fast, easy to implement, and cost-effective.

-

Although the technique is passive, its NDZ is very low.

-

Detailed FDZ analysis is also provided which provides the limits of the proposed IDT.

-

Under ZPM conditions, many conventional techniques fail to detect the islanding. However, the proposed IDT provides accurate and reliable results under such conditions.

-

The proposed IDT provides satisfactory results for a wide range of active power mismatch (APM) and reactive power mismatch (RPM) including ZPM.

-

The procedure to calculate the threshold is not complex and it is discussed briefly.

-

The proposed IDT provides accurate results in the case of various irradiances.

-

The proposed IDT is immune to noise with signal-to-noise ratio of up to 40 dB in case of DG disconnection.

-

Its performance is found good for IE and fault as NIE detection under a weak grid system.

-

Its comparison with conventional schemes proves the effectiveness of the proposed IDT.

-

The proposed technique is verified by experimental hardware validation and found accurate and satisfactory.

In this paper, the system description of a modified IEEE-13 bus and the methodology of the proposed technique are focused in Sect. 3. Test results and discussions are explained in Sect. 4. The experimental implementation and validation are explicated in Sect. 5. The comparative assessment of the proposed IDT with conventional schemes is provided in Sect. 6. At last, the conclusion is described in Sect. 7.

3 System description and description of proposed technique

3.1 System description

A modified IEEE-13 bus test system [32] (4160 V, 50 Hz), as provided in Fig. 1, is simulated in the MATLAB environment. Test system data are given as rated voltage of PCC (VPCC) = 4160 V, rated frequency (f) = 50 Hz, and total output power of DGs are P = 4 MW and Q = 300 kVAR. Solar-based DG1 and DG2 with a generation capacity of 2 MW each are connected at node points 646 and 675, respectively. These DGs are coupled to a 4160 V distribution system through 480 V/4160 V transformers. In Fig. 1, the DG1 is connected through a circuit breaker CB2 and DG2 is connected through CB3. Breaker CB1 is used for connection or disconnection of PCC through the main grid. Disconnection through CB1 creates an islanding situation, where the main grid is disconnected from the DGs and the power supply to the loads is done only by DGs. Three-phase voltage and current data with a sampling period of 1 ms are measured and stored at PCC for implementation of the proposed algorithm. The three-phase voltage and current data have been collected on 1 kHz sampling frequency and 50 Hz system frequency (20 samples per cycle). During such situations, three-phase voltage and current data are obtained at PCC (PCC at 632). In this paper, the efficacy of the proposed IDT is tested for various islanding and non-islanding events.

3.2 DG description and converter control

An inverter based on photovoltaic (PV) DG is connected to the main utility grid. Irradiance and temperature are kept at 1000 W/m2 and 25 °C for normal day conditions, respectively. PV array connected in 460 parallel strings and series connected modules (1Soltech 1STH-215-P) of each string is kept 23. With this combination, each DG has 2 MW generation capacities. Specification of solar panels is provided in Table 2.

Figure 2 depicts the control structure for solar-based DG. This DG provides active power to the system and typically runs at a power factor of approximate unity. The voltage generated by sustainable sources varies with natural conditions. PS and Qs are the real and reactive powers obtained at PCC and must be managed by using a control system as shown in Fig. 2a. The voltage signals Vsa, Vsb, and Vsc are collected from PCC and transformed into a dq-frame. To obtain the transformation signal Ψ, the output of the dq-frame is given to a phase-locked loop (PLL), which then feeds its output to the voltage-controlled oscillator (VCO) through a multiplexer. Using a multiplexer, initial frequency (ω0) is compared with frequency (ω) which is generated by using PLL. Its comprehensive analysis is provided in [33]. VCO should reset to zero if Ψ reaches to zero.

The controller’s main objective is to regulate the source bus voltage VDC so that Ps and Qs can be independently controlled as shown in Fig. 2a. To generate an error signal ev, the squared values of VDC and VDCref are compared, which is processed by the compensator (Kv) to receive signal Psref as shown in Fig. 2b. Qsref is set to zero in the simulation to ensure that VSC operates at unity power factor (pf). Here, Pext is the disturbance signal discussed in [33]. The input signals of the power-based controller are Psref and Qsref, which provide idref and iqref.. The inputs Vsdref and Vsqref to the voltage controller are set to 391.91 and 0, which generate idref and iqref, respectively.

These signals determine whether the control system is grid-connected or autonomous. idref and iqref are provided to the current controller in order to obtain md and mq, which are transformed to abc frames (ma, mb, and mc) via the dq to abc converter. ma, mb, and mc are three phase-modulating signals. Its output is sent to a 3rd harmonic injection circuit, which generates PWM pulses that drive the inverter.

The suggested IDT is designed using negative sequence voltage and current signals from the PCC point. The command is sent to the multiplexer and circuit breaker (CB) through the logic block, which provides the IE and NIE information. Specifications of solar-based inverters are given in Table 3.

3.3 The proposed technique for islanding detection and its implementation

The positive sequence components of voltage and current are essential to execute the proposed technique, and these components are measured at PCC to identify the islanding event. The superimposed positive sequence voltage and current exhibit significant results to identify the islanding condition. PS voltage and PS current are obtained as follows.

V1 and I1 are positive voltage and current. Va, Vb, Vc, and Ia, Ib, Ic are phase voltages and currents, respectively, and the value of k is ej2π/3.

The changes in superimposed positive sequence apparent power (CSPSAP) is calculated using PS voltage (V1) and PS current (I1) measured at PCC and provided in (3), which helps to discriminate the IEs and NIEs.

where

V1(post) and I1post are the delayed voltage and current phasor values and V1(pre) and I1pre are the values of positive sequence voltage and current in grid-connected mode and stored by relay. For proper operation, these values are updated regularly. Here, ΔV1 and ΔI1 are superimposed positive sequence voltage and current, respectively, and can be expressed in (4) and (5). During the islanding period, V1(post) = V1island and I1post = I1island. In case of fault, V1(post) = Vf and I1(post) = If. Here Vf and If is the fault voltage and current. The impact of fault cases is explained in the next section. The threshold is selected as 50 for the test system as shown in Fig. 1. If the index CSPSAP < threshold value, then the system is called grid-connected mode. If CSPSAP > threshold, then islanding is identified.

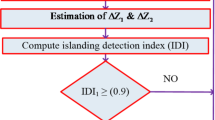

A flowchart for the execution of the proposed algorithm is shown in Fig. 3. At PCC, a positive sequence voltage and current are calculated using phasor values. After this, a superimposed positive sequence component of voltage and current is calculated. Index CSPSAP as defined in (3) is compared with the threshold. If its value crosses the threshold, then the proposed IDT detects islanding. If it is below the threshold, the system is in grid-connected mode.

3.4 Change in apparent impedance

To understand the detection of islanding using the proposed technique, a basic grid-connected system is considered as shown in Fig. 4. RDG and LDG are impedance parameters of DG. RN and LN represent impedance parameters for the distribution system. RUG and LUG are impedance parameters for the main utility grid. VUG and VDG are voltages provided by the utility grid and DG. The equivalent circuit of the basic distribution network as shown in Fig. 4 is presented in Fig. 5. Here, three cases of grid-connected mode, islanding mode, and fault mode are discussed in detail. Zth is the Thevenin equivalent impedance as provided in (6), which varies in various modes of operation [34]. Here, Z1L is a complex PQ-type load that remains connected at the PCC point as provided in Fig. 4. Z1L = RL + jωLN and Z1B = RN + RUG + jω(LN + LUG) are discussed [34]. Rf is fault resistance during fault conditions.

Scenario 1: Grid-connected condition

In close contact with CB1, the system acts as a grid-connected mode as shown in Fig. 5, and also known as a pre-islanding mode. In grid-connected mode, V1(post) = V1(pre) and I1(post) = I1(pre). Therefore, the index will be zero as calculated using (3). Figure 6 shows the equivalent circuit of Fig. 5 in grid-connected conditions.

Scenario 2: Islanding condition

In this condition, DG is disconnected from the main utility grid by the opening of CB1, and power is supplied to the load by DG only. The equivalent circuit for this case is presented in Fig. 7. Such a case is an islanding condition, where the current during pre-islanding (I1(pre)) is high as compared to that of the islanding condition (I1(island)). However, there is very less change found in the voltages of both situations. In (8), term I1(pre)/I1(island) consists of high values as I1(post) = I1(island), but (Z1L||ZUG)/Z1L is less than one. In another term, (1 − I1(pre)/I1(island)) has a significant impact on the index due to the high values of term I1(pre)/I1(island). Hence, the index calculated in (8) provides significant change during the islanding mode.

Scenario 3: Fault condition

During a fault condition, I1(pre) is less as compared to fault current (If). In index as defined in (10), I1(pre)/If should be less than 1 and (Z1L||ZUG)/(Z1L||ZUG||Rf) is greater than one as (Z1L||ZUG||Rf) < (Z1L||ZUG). Therefore, the first term of the index as defined in (10) has negligible impact. In the second term also, there is a negligible impact because of I1(pre)/If < 1. Hence, the index is not affected in fault conditions. An equivalent circuit of fault cases is provided in Fig. 8.

Hence, the proposed IDT detects the islanding properly and does not operate in a fault condition. However, the selection of a threshold is essential for the proper operation of the proposed IDT.

3.5 Selection of threshold

To distinguish between islanding and non-islanding conditions, a predetermined threshold is compared to the index CSPSAP. It is tested that the values of index CSPSAP under ZPM decide the upper limit of the threshold. Under the ZPM case, it is observed that the index waveform never comes below 200. The lower limit of the threshold is decided using LLLG fault analysis. Under this fault case, the value of index CSPSAP does not go beyond 15 for lower values of fault resistances. For proper discrimination of IE and NIE cases in this particular system, a safety margin is included. The threshold is decided at 50 including the safety margin. This value covers all types of high transients and other islanding situations within the system.

4 Result and discussion

For the execution of the proposed IDT, a 4160 V, 50 Hz IEEE 13-bus system as provided in Fig. 1 is simulated. The islanding conditions are generated through the opening of the circuit breaker (CB1) at 0.7 s under various APM and RPM conditions. The threshold value is set at 50 for all test conditions in islanding or non-islanding events. Index CSPSAP indicates the IE detection in the MATLAB environment. Various islanding and non-islanding conditions have been tested in this section to verify the efficacy of the proposed IDT.

4.1 Detection of islanding event under UL 1741 test conditions with perfect zero power mismatch (ZPM)

The proposed technique is verified under islanding and non-islanding conditions based on UL 1741 std [35]. DGs generate the active and reactive powers of 4 MW and 300 kVAR. The total load capacity is adjusted approximately the same as active and reactive powers supplied by the DGs supply to match the ZPM condition. The islanding event is created by opening CB1 at 0.7 s. V1, I1, ΔV1, ΔI1, V1* I1, and ΔV1* ΔI1 are calculated using voltage and current phasors and are shown in Fig. 9. There are very minor changes found in V1 and ΔV1 from pre-islanding to islanding situations. However, opposite to I1, ΔI1 has significant change and has a high value during islanding mode as compared to that of pre-islanding mode as shown in Fig. 9a, b. V1*I1 has a low value and ΔV1*ΔI1 has a high value, which makes the index CSPSAP competent to detect the IEs. In Fig. 9d, the index is below the threshold in pre-islanding and crosses the set threshold after 22.27 ms after islanding occurs. Hence, an alert signal (AS) is generated after detecting the islanding condition as plotted in Fig. 9e.

4.2 Verification of different load quality factors (QFs)

There are multiple standards [36] for validating the islanding state to authenticate the various load quality factors. According to IEEE standard 929, the QF value should be less than 2.5. In IEEE 1547 and UL 1741 test conditions, QF = 1 and QF = 1.8 are recommended, respectively. In the United States, QF = 2.5, and in the United Kingdom QF = 0.5 are recommended for verifying the IDT. To verify the effect of the different quality factors (QFs) of 0.5, 1.0, 1.8, 2.0, and 2.5, CSPSAP indices as discussed in (3) and their corresponding alert signals are plotted in Fig. 10 for detection of IEs according to UL 1741 standards, respectively. IEs detection time and different values of load parameters (R, L, and C) with QFs are provided in Table 4. Figure 10 shows that all CSPSAP indices cross the threshold and detect the islanding events accurately, which shows that the proposed IDT provides satisfactory results at nearly perfect power match events. A comparison of the islanding detection time of the proposed IDT with different existing techniques is provided in Table 5, which shows that the proposed IDT detects IEs fast.

NDZ is the area where IDT fails to detect the islanding condition. So, calculating the NDZ is an important factor for any IDT. To find NDZ of the proposed IDT, the modified IEEE-13 bus system simulated in ZPM condition under UL 1741 std. The power capacity provided by DGs has a ripple of 5 KW and 2 kVAR due to the dynamics of the inverter controller. The proposed technique detects islanding under ZPM conditions and has a negligible non-detection zone (0.25% and 0.66% for ΔP and ΔQ). The comparison with other existing techniques [25, 29, 37] for NDZ is depicted in Fig. 11.

4.3 Islanding verification for different APM conditions

The proposed approach has been verified under various APM situations. The verification is carried out for a wide range of APM conditions. The ZPM condition is already discussed in the previous subsection. With reference to ZPM, the RLC load is modified to obtain different power mismatch circumstances such as − 1%, − 10%, − 20%, − 50%, + 1%, + 10%, + 20%, and + 50%. To achieve positive APM values, the load is decreased by 1%, 10%, 20%, and 50%. Similarly, to obtain the negative APM values, the load is increased by 1%, 10%, 20%, and 50%, respectively. During each APM case, the islanding event is created by tripping breaker CB1 at 0.7 s. In each event, indices CSPSAP achieve higher value after the opening of CB1. CSPSAP indices along with AS for APM situations are shown in Fig. 12. The maximum IE detection time is 24.09 ms in − APM and 21.985 ms in + APM. Table 6 provides the details of IEs detection time for each APM case discussed in this subsection.

4.4 Islanding verification for different RPM conditions

Similarly, the efficacy of the proposed IDT is verified in numerous RPM conditions. For adjusting the different RPM conditions such as − 1%, − 10%, − 20%, − 50%, + 1%, + 10%, + 20%, and + 50%, RLC load parameters are calculated accordingly. In each case, the load is decreased by 1%, 10%, 20%, and 50% for negative RPM cases and increased by 1%, 10%, 20%, and 50% for positive RPM cases, respectively. During each RPM situation, islanding is initiated through the opening of CB1 at 0.7 s. Indices CSPSAP calculated using (3) accurately identify the islanding for RPM cases which, is provided in Fig. 13. Here, the maximum detection time of IE under such cases is 22.19 ms in − RPM and 22.70 ms in + RPM cases. The islanding detection time for different RPMs is shown in Table 7. The efficacy of the proposed IDT is satisfactory for various RPM situations.

4.5 Unbalanced load condition

Generally, unbalanced loading is tolerated by the distribution system. An additional 1–ϕ inductive load of 500 KW and 100 Var has been initially connected at PCC to create unbalancing. Under such a case, circuit breaker CB1 is opened at 0.7 s to create islanding. It is observed that the proposed index (CSPSAP) crosses its threshold after islanding inception and provides correct information about islanding, and an alert signal is generated. Index CSPSAP with AS for such a case is shown in Fig. 14. Therefore, it is very essential to evaluate the accuracy and reliability of the proposed scheme under unbalanced load conditions.

4.6 Islanding verification for irradiance change in ZPM condition

Solar irradiance measurement represents the solar energy hitting a per square meter area of the solar plate. It varies due to variations in sun intensity, sun angle, shadow, temperature, climatic conditions, electrical load matching, etc. In this subsection, the inverter-based DG design is of 2 MW DG capacities. For maximum cases, the irradiance and temperature are kept constant as 1000 W/m2 and 25°. To understand the impact of variation of solar irradiations, the testing of the efficacy of the proposed IDT is essential.

For testing purposes, the solar irradiance changes in a range of 900–1000 W/m2. The CB1 is tripped at 0.7 s for various cases of irradiance of 975, 950, 925, and 900 W/m2. The simulated results for each case of solar irradiances are provided in Fig. 15. In all islanding cases of various irradiances, the indices cross the threshold as shown in Fig. 15a and corresponding alert signals are provided in Fig. 15b.

4.7 Verification of DG disconnection with noise

In the modified IEEE-13 bus system, three DGs are supplied power to the load. To investigate the effect of noise in the DG disconnected mode, DG2 is completely separated from the entire system by opening the circuit breaker connected near node 675 at 0.7 s. Then, a Gaussian white noise [24] of 40 dB signal-to-noise ratio (SNR) is introduced in instantaneous voltage and current signals. The current signal is highly deteriorated as compared to the voltage signal. It is the limitation of the proposed IDT that it does not work for SNR less than 40 dB. The index CSPSAP goes higher after islanding inception and clearly indicates the IE detection as presented in Fig. 16. In this case, the proposed IDT provides satisfactory performance in the presence of noise (SNR > 40 dB).

4.8 Different faults with different fault resistances at the PCC point

To test the efficacy of the proposed IDT, several fault cases such as LG and LLLG with different fault resistances of 1Ω, 5Ω, 10Ω, and 20Ω [28,29,30, 34] are incepted at 0.7 s at PCC under ZPM condition. Types of faults with fault resistances (Rf) are provided in Table 8. Results under all fault cases are presented in Fig. 17. Indices CSPSAP calculated using (3) in all fault cases go higher from the pre-fault condition. However, these cases do not cross the threshold and remain silent as shown in Fig. 17. Figure 17 presents the results of line-to-ground fault (LG) at PCC, triple line-to-ground fault (LLLG) at PCC, and double line-to-ground (LLG) fault near DG2 at node 675. The proposed IDT will not produce any alert signal under such cases. Hence, the proposed IDT provides accurate and reliable results during fault cases also.

The LLLG fault conditions are also observed in fault resistances as low as 0.001, 0.01, and 0.1. However, as the index crosses the defined threshold and AS are formed for very low-resistance LLLG faults cases, which provide the FDZ boundary. In these cases, the FDZ boundary lies in LLLG faults with 0.001 fault resistance. In real time, the probability of such cases is minimal. This is a limitation of the proposed IDT, which is utilized to determine the FDZ.

4.9 Verification of load switching

The protection system may disturb during load switching due to the generation of transients. Hence, to examine such load switching conditions, 12.5% of the total three-phase RLC load (500 KW) under ZPM is suddenly increased at 0.7 s on PCC. The index CSPSAP goes higher but does not cross the threshold as shown in Fig. 18a. The proposed IDT considers this situation as NIE, and no alert signal is generated as shown in Fig. 18b. The proposed IDT works well in terms of accuracy and reliability under load switching situations.

4.10 Capacitive and inductive load switching

The effectiveness of the proposed IDT is also verified in capacitive and inductive load switching cases. A capacitor bank (rating of each capacitor bank 1.5 kVAR, 15kVAR, and 150 kVAR) is connected at a time of 0.7 s at PCC under various capacitor switching cases. Due to the capacitor connection at PCC, the change in reactive power does not provide a significant contribution to voltage and current. Therefore, the switching of the capacitor does not have any impact on the performance of the proposed IDT. The indices CSPSAP under all capacitor switching cases do not cross the threshold which is shown in Fig. 19. Similarly, a 15 kVAR inductor is connected at 0.7 s under a case of inductive load switching to ensure the impact on the test result. As a result, the impact of inductive load switching is negligible. During such a case, the index is very low and not able to cross the threshold; hence, no AS is generated, which is shown in Fig. 19. In this case also, the proposed technique provides accurate and satisfactory results and remains silent.

4.11 Nonlinear load verification

Nonlinear loads in the form of electronic equipment such as computers, UPS, rectifiers, printers, and power electronics switch-based instruments offer harmonics in the system. Such situations result in spurious islanding detection. Hence, testing of the proposed IDT is mandatory for such cases. For such a purpose, a nonlinear three-phase full-wave diode rectifier with a load capacity of 4.5 KW is employed to the PCC at 0.7 s. The index does not cross the threshold as shown in Fig. 20. Hence, no islanding detection signal is released. As a result, in such NIE, the approach offers correct information regarding the test outcome.

4.12 Weak grid authentication

A system with high internal resistance and low short-circuit capacity is considered a weak grid. In a weak system, voltage variation is high as compared to that of a strong system (voltage is generally constant in strong systems). Therefore, the suggested IDT needs to be validated for a weak system in both IE and NIE situations. For this reason, the 50 MVA short-circuit capacity and 0.04291 + j0.3480 internal impedance of the main utility grid are taken into consideration. By opening CB1 at 0.7 s, the islanding is created. The islanding detection results under weak grid conditions are plotted in Fig. 21a and AS in Fig. 21b. Figure 21a shows that the index goes beyond the set threshold; hence, the AS is triggered at 0.7219 s.

Hence, it takes 21.9 ms to detect islanding in a weak grid scenario. Similarly, for non-islanding verification, an LLG fault with a fault resistance of 1Ω is incepted at 0.7 s under a weak grid situation. Figure 21c confirms that the impact of LLG fault in the weak grid is unaffected as the index does not cross the threshold. However, some changes can be seen after fault inception. The proposed IDT discriminates IE and NIE accurately under weak grid situations.

5 Hardware execution

To investigate the efficacy of the proposed technique, it is verified in OPAL-RT real-time simulator (OP4510) in RT-LAB. The simulation model is created in MATLAB/Simulink on an RT-LAB desktop (Intel core i7-8700 CPU @3.20 GHz, 3.19 GHz, RAM 12.0 GB, 64-bit operating system). Figure 22 depicts the setup of the model for real-time operation in OPAL-RT. A step-by-step procedure is required to frame the model and process it in a real environment. A solver reads the data and creates an OPAL-RT file containing all details of the network and control sequences. After that, three subsystems (master, slave, and console subsystems) are created to enable execution in parallel processing.

Later all the supporting files and test case Simulink model are imported into RT-LAB and the model is compiled, which converts all components of the model to executable C++ codes. After successful compilation, the model is loaded to the available target system. Model initialization and synchronization are done using the RT-LAB box. The console subsystem becomes active and it executes and simulates the model which generates final output signals in real time. The real-time results of the proposed technique are shown using a four-channel (i/p bandwidth 100 MHz) Tektronix MD03014 mixed-domain oscilloscope.

For testing purposes, IE is created by opening CB1 under the ZPM condition in the system shown in Fig. 1 in the MATLAB environment. This MATLAB system is executed and read by the OPAL-RT solver. In the OPAL-RT environment, three subsystems (master, slave, and console subsystems) are created and it is imported by RT-LAB. After successful compilation, the console subsystem generates the final output in real time, which can be seen using Tektronix MD03014 mixed-domain oscilloscope. Corresponding real-time results with scale-down values of V1*I1, ΔV1*ΔI1, CSPSAP, and AS are provided in Fig. 23. The islanding detection time taken by OPAL-RT software is 27 ms, which is less than the described in UL 1741 std. For similar IE cases, simulated results are presented in Fig. 24. Corresponding simulated results V1*I1, ΔV1*ΔI1, CSPSAP, and AS are provided in Fig. 24. The proposed IDT takes 21.60 ms to detect islanding. For a similar case, islanding detection time at a real-time platform is near to that of a3, simulation platform on MATLAB. The similarity in experimental and simulation results validates the performance of the proposed IDT in real time.

6 Comparative study

An assessment of the performance of the proposed IDT, a comparative study is considered with another passive islanding event detection method [28]. The mentioned existing technique [28] detects islanding events based on observing lower-frequency components of PCC voltage using time-domain spectral examination.

To measure lower-frequency components, single-phase PCC voltage is provided to the DC blocker to remove the DC voltage. After that, this signal is fed to a low-pass filter (LPF) to filter out frequencies more than 50 Hz. The mean of the LPF signal is used for calculating the upper envelope. The upper envelope waveform is compared with the preset threshold value, which gives information for islanding or non-islanding conditions. The comparative assessment of the proposed algorithm with the existing method [28] is presented in Fig. 25. In [28], there is no discussion and no simulation results are provided for the LLLG fault case. So, for comparative analysis, an LLLG fault with fault resistance 1Ω is created at 0.7 s. The simulation results for the LLLG fault case are provided in Fig. 25. Fig. 25b clearly shows that the existing technique [28] generates an AS in the LLLG fault case, which provides false information about NIE. Results regarding the proposed IDT are shown in Fig. 25c in a similar LLLG fault condition. The index of the proposed IDT has negligible impact and has not released any AS in such a case which is correct information about NIE. For such a case, the proposed IDT provides superior results as compared to the existing IDT [28]. In another comparison, the islanding detection time as provided in [28] is more than 250 ms, which is higher than that of the proposed technique (less than 21.6 ms).

In another comparison case, the proposed technique is compared with existing communication-based passive IDT [38], which is based on the angle of positive sequence superimposed impedance. ΔθDG and ΔθPCC are the phase angle of superimposed impedance measured at the DG terminal and PCC point, respectively. The difference between ΔθPCC and ΔθDG called DPSIA discriminates between the IEs or NIEs. After islanding, DPSIA should be greater than zero. If it is consistently one for one cycle, the existing scheme [39] declares islanding. This existing technique [38] is implemented by simulating LLG fault with fault resistance 1Ω under ZPM condition in a modified IEEE-13 bus system as shown in Fig. 1. DPSIA should be negative for NIE for correct information. However, it is positive and does not provide an accurate result for the LLG fault case as shown in Fig. 26a. However, the index discussed in the proposed IDT remains below the threshold as shown in Fig. 26b. In such a case, the proposed IDT provides correct information.

Comparison of the scheme [38] with proposed IDT for non-islanding condition a DPSIA index for LLG fault, b proposed index for LLG fault, c proposed AS for LLG fault

Hence, the proposed technique is superior as compared to the existing passive technique [28, 38] as tested in LLLG and LLG fault events, respectively. Comparisons of different existing techniques are provided in Table 9 with regard to power mismatch, islanding detection time, verification with noise, LLLG fault, and load quality factor. The proposed IDT provides better results in comparison with existing techniques as provided in Table 9. Table 9 shows that the islanding detection time of the proposed scheme has less as compared to existing schemes.

The contribution of the CSPSAP-based paper is provided as follows:

-

The proposed IDT works well and provides accurate results for islanding events in a wide range of APM and RPM conditions including 1% APM. Even its performance is satisfactory under ZPM conditions.

-

IE test conditions are considered under unbalanced load, irradiance change, and DG disconnection cases, where this technique is found accurate and reliable.

-

The proposed IDT is also tested for various QF according to UL 1741 standards and its performance is found satisfactory.

-

NIE test cases such as capacitor switching, load switching, nonlinear load, and different faults are performed to test the efficacy of the proposed IDT. In these cases, also, its performance is consistent and accurate.

-

The proposed IDT performs well in IE and NIE cases under weak grid conditions.

-

Existing techniques [28, 38] detect IE in fault conditions and fails to discriminate the IE and NIE as proposed IDT provides correct results which prove the superiority of proposed IDT.

-

Matching simulated and experimental results validate the effectiveness of the proposed IDT.

-

In general, active islanding methods have much less NDZ than passive techniques. However, the proposed CSPSAP technique has almost zero NDZ.

7 Conclusion

This paper presents a passive islanding detection technique based on the change in positive sequence apparent power at the specific location. It can be identified that the proposed technique works effectively in zero power mismatch, active power mismatch, reactive power mismatch, and unbalanced load conditions. The ability of the proposed CSPSAP-based islanding detection technique has been tested under different islanding events according to UL 1741 std for zero power mismatches and it is identified that the proposed algorithm is accurate and consistent. Although the proposed technique can be effectively performed under non-islanding conditions such as load switching, capacitor switching and fault cases, etc. DG disconnection with the inclusion of noise is also tested in the MATLAB environment. The proposed IDT works well for the verification of islanding and non-islanding cases under a weak grid system. It works properly in such aforementioned conditions. Results of the proposed IDT are also implemented and validated on hardware platforms using OPAL-RT real-time simulator. The proposed islanding event detection technique provides accurate and satisfactory results.

The suggested work is being extended in the future to study the implementation of the proposed scheme in the higher capacity of inverters in microgrid systems. Even proposed IDT can be verified for synchronous generator along with inverter DG system.

Data availability

The data have been utilized in this research paper can be available from the corresponding author upon reasonable request.

Abbreviations

- CSPSAP :

-

Change in superimposed negative

- APM:

-

Active power mismatch

- IE and NIE:

-

Islanding and non-islanding event

- FDZ:

-

False detection zone

- NDZ:

-

Non-detection zone

- APM:

-

Active power mismatch

- DG:

-

Distribution system

- THD:

-

Total harmonic distortion

- ROCOF:

-

Rate of change of frequency

- ROCOP:

-

Rate of change of power

- PCC:

-

Point of common coupling

- PLL:

-

Phase-locked loop

- CB:

-

Circuit breaker

- PS and NS:

-

Positive and negative sequence

- IDT:

-

Islanding detection zone

- AS:

-

Alert signal

- UOV:

-

Under/over voltage

- SNR:

-

Signal-to-noise ratio

- ROCONSV:

-

Rate of change of negative sequence voltage

- LPF:

-

Low-pass filter

- UOF:

-

Under/over frequency

- P and Q :

-

Active and reactive power

- V pcc :

-

PCC voltage

- I dg :

-

DG current

- ma:

-

Modulation index

- θ :

-

Shift angle

- V 1, I 1 :

-

Positive sequence voltage and current

- V a, V b, V c :

-

Phase voltages

- I a, I b, I c :

-

Phase currents

- Z 1L :

-

Complex PQ load

- R f :

-

Fault resistance

- Z 1B :

-

Thevenin equivalent impedance

- ∆S 1 :

-

Change in apparent power

References

Zeineldin HH, Kirtley JL (2009) A simple technique for islanding detection with negligible nondetection zone. IEEE Trans Power Deliv 24(2):779–786

Photovoltaics DG, Storage E (2018) IEEE standard for interconnection and interoperability of distributed energy resources with associated electric power systems interfaces. IEEE STD, pp 1547–2018

Aphrodis N, Ntagwirumugara E, Vianney BJM, Mulolani F (2019) Design, control and validation of a PV system based on supervisory control and data acquisition (SCADA) viewer in smartgrids. In; 2019 5th international conference on control, automation and robotics (ICCAR). IEEE, pp 23–28

Dob B, Palmer C (2018) Communications assisted islanding detection: contrasting direct transfer trip and phase comparison methods. In: 2018 71st annual conference for protective relay engineers (CPRE). IEEE, pp 1–6

Bharatee A, Mishra M, Pati BB (2019) Anti-islanding protection by power line signaling and wavelet transform. In: 2019 Global conference for advancement in technology (GCAT). IEEE, pp 1–5

Sankar A, Sunitha R (2021) Synchrophasor data driven islanding detection, localization and prediction for microgrid using energy operator. IEEE Trans Power Syst 36(5):4052–4065

Samantaray SR, Kamwa I, Joos G (2017) Phasor measurement unit based wide-area monitoring and information sharing between micro-grids. IET Gener Transm Distrib 11(5):1293–1302

Ganivada PK, Jena P (2019) Active slip frequency based islanding detection technique for grid-tied inverters. IEEE Trans Ind Inf 16(7):4615–4626

Reigosa D, Briz F, Blanco C, García P, Guerrero JM (2013) Active islanding detection for multiple parallel-connected inverter-based distributed generators using high-frequency signal injection. IEEE Trans Power Electron 29(3):1192–1199

Jia K, Wei H, Bi T, Thomas DW, Sumner M (2016) An islanding detection method for multi-DG systems based on high-frequency impedance estimation. IEEE Trans Sustain Energy 8(1):74–83

Rostami A, Rezaei N (2020) A multi-feature-based passive islanding detection scheme for synchronous-machine-based distributed generation. Int Trans Electr Energy Syst 30(11):e12586

Grebla M, Yellajosula JR, Høidalen HK (2019) Adaptive frequency estimation method for ROCOF islanding detection relay. IEEE Trans Power Deliv 35(4):1867–1875

Raipala O, Mäkinen A, Repo S, Järventausta P (2016) An anti-islanding protection method based on reactive power injection and ROCOF. IEEE Trans Power Deliv 32(1):401–410

Altaf MW, Arif MT, Saha S, Islam SN, Haque ME, Oo AM (2022) Effective ROCOF-based islanding detection technique for different types of microgrid. IEEE Trans Ind Appl 58(2):1809–1821

Tao J, Han H, Wang Z, Shu Y, Fang W, Li Y (2018) An advanced islanding detection strategy coordinating the newly proposed v detection and the rocof detection. In: 2018 IEEE innovative smart grid technologies-Asia (ISGT Asia). IEEE, pp 1204–1208

Asoh DA, Chia LN (2022) Design and implementation of an automatic over/undervoltage protection system for single-phase low voltage power lines. J Power Energy Eng 10(8):12–25

Bezawada P, Yeddula PO, Kota VR (2021) A novel time-domain passive islanding detection technique for grid-connected hybrid distributed generation system. Arab J Sci Eng 46(10):9867–9877

Pangedaiah B, Reddy PSK, Obulesu YP, Kota VR, Alghaythi ML (2022) A robust passive islanding detection technique with zero-non-detection zone for inverter-interfaced distributed generation. IEEE Access 10:96296–96306

Nikolovski S, Baghaee HR, Mlakić D (2019) Islanding detection of synchronous generator-based DGs using rate of change of reactive power. IEEE Syst J 13(4):4344–4354

Shafique N, Raza S, Munir HM, Bukhari SSH, Ro JS (2021) Islanding detection strategy for wind farm based on performance analysis of passive indices having negligible NDZ. Appl Sci 11(21):9989

Lopez JR, Ibarra L, Ponce P, Molina A (2021) A decentralized passive islanding detection method based on the variations of estimated droop characteristics. Energies 14(22):7759

Usman M, Raza S, Munir HM, Riaz M, Bukhari SSH, Ro JS (2022) Novel passive islanding detection technique by monitoring reverse power at PCC. Int Trans Electr Energy Syst 2022

Reddy VR, Sreeraj ES (2019) A feedback-based passive islanding detection technique for one-cycle-controlled single-phase inverter used in photovoltaic systems. IEEE Trans Ind Electron 67(8):6541–6549

Liu N, Diduch C, Chang L, Su J (2015) A reference impedance-based passive islanding detection method for inverter-based distributed generation system. IEEE J Emerg Sel Top Power Electron 3(4):1205–1217

Raza S, Mokhlis H, Arof H, Laghari JA, Mohamad H (2015) A sensitivity analysis of different power system parameters on islanding detection. IEEE Trans Sustain Energy 7(2):461–470

Makwana YM, Bhalja BR (2017) Experimental performance of an islanding detection scheme based on modal components. IEEE Trans Smart Grid 10(1):1025–1035

Chaitanya BK, Yadav A, Pazoki M (2020) An advanced signal decomposition technique for islanding detection in DG system. IEEE Syst J 15(3):3220–3229

Bezawada P, Yeddula PO, Kota VR (2020) A new time domain passive islanding detection algorithm for hybrid distributed generation systems. Int Trans Electr Energy Syst 30(12):e12632

Xie X, Huang C, Li D (2020) A new passive islanding detection approach considering the dynamic behavior of load in microgrid. Int J Electr Power Energy Syst 117:105619

Gupta P, Bhatia RS, Jain DK (2016) Active ROCOF relay for islanding detection. IEEE Trans Power Deliv 32(1):420–429

Ramachandradurai S, Krishnan N, Prabaharan N (2022) Unintentional passive islanding detection and prevention method with reduced non-detection zones. Energies 15(9):3038

Bashir J, Jena P, Pradhan AK (2014) Islanding detection of a distributed generation system using angle between negative sequence voltage and current. In: 2014 Eighteenth national power systems conference (NPSC). IEEE, pp 1–5

Yazdani A, Iravani R (2010) Voltage-sourced converters inpower systems: modeling, control, and applications. Wiley, New York

Gupta OH, Tripathy M, Sood VK (2019) Islanding detection scheme for converter-based DGs with nearly zero non-detectable zone. IET Gener Transm Distrib 13(23):5365–5374

Mahmud R, Hoke A, Narang D (2018) Validating the test procedures described in UL 1741 SA and IEEE P1547. 1. In: 2018 IEEE 7th world conference on photovoltaic energy conversion (WCPEC) (A joint conference of 45th IEEE PVSC, 28th PVSEC & 34th EU PVSEC). IEEE, pp 1445–1450

Xie X, Xu W, Huang C, Fan X (2021) New islanding detection method with adaptively threshold for microgrid. Electr Power Syst Res 195:107167

Marchesan G, Muraro MR, Cardoso G, Mariotto L, De Morais AP (2015) Passive method for distributed-generation island detection based on oscillation frequency. IEEE Trans Power Deliv 31(1):138–146

Nale R, Biswal M, Kishor N (2022) A passive communication based islanding detection technique for AC microgrid. Int J Electr Power Energy Syst 137:107657

Voglitsis D, Papanikolaou NP, Kyritsis AC (2018) Active cross-correlation anti-islanding scheme for PV module-integrated converters in the prospect of high penetration levels and weak grid conditions. IEEE Trans Power Electron 34(3):2258–2274

Kumar GP, Jena P (2020) Pearson’s correlation coefficient for islanding detection using micro-PMU measurements. IEEE Syst J 15(4):5078–5089

Seyedi M, Taher SA, Ganji B, Guerrero J (2021) A hybrid islanding detection method based on the rates of changes in voltage and active power for the multi-inverter systems. IEEE Trans Smart Grid 12(4):2800–2811

Chaitanya BK, Yadav A, Pazoki M (2020) Reliable islanding detection scheme for distributed generation based on pattern-recognition. IEEE Trans Ind Inf 17(8):5230–5238

Acknowledgements

This work has not been supported or funded by any organization.

Author information

Authors and Affiliations

Contributions

Munna Kumar- Study concept, design, paper writing, interpretation of results and manuscript prepration. Jitendra Kumar- Reviewed the results and manuscript for final version.

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Kumar, M., Kumar, J. Islanding event detection technique based on change in apparent power in microgrid environment. Electr Eng 105, 1447–1463 (2023). https://doi.org/10.1007/s00202-023-01750-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00202-023-01750-5