Abstract

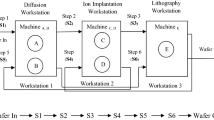

This paper is concerned with assessing the impact of 15 existing release policies in combination with three dispatching rules (together called as scheduling policy) on the performance of semiconductor fabrication facilities using a simulation model of a representative but fictitious semiconductor wafer fab. The performance criteria employed includes average cycle time, standard deviation of cycle time, work in process (WIP) level, and throughput. Arena simulation software is used to build the simulation model and conduct the experimental study. The experimental results indicate that workload regulating (WR), constant work in process (CONWIP), and constant load (CONLOAD) policies are superior among tested release policies and shortest remaining processing time (SRPT) is the best dispatching rule. This paper present a new release policy called as constant workload (CONSTWL), which is a modified version of CONWIP policy to overcome the limitations of traditional release policies. CONSTWL policy triggers the release of job into the system based on the overall workload of shop floor. Results on computational experiments indicate that CONSTWL outperforms traditional release policies in terms of the average cycle time, the standard deviation of cycle time and work in process under a prescribed throughput level. The positive impact of CONSTWL policy on system performance appears to be reliable with the increase of system congestion level. CONSTWL policy may prove useful in practical contexts of make to stock manufacturing environment whose orders are met usually from finished inventory.

Article PDF

Similar content being viewed by others

Explore related subjects

Discover the latest articles, news and stories from top researchers in related subjects.Avoid common mistakes on your manuscript.

References

Glassey CR, Resende MG (1988) Closed-loop job release control for VLSI circuit manufacturing. IEEE Trans Semicond Manuf 1:36–46

Wein LW (1988) Scheduling semiconductor wafer fabrication. IEEE Trans Semicond Manuf 1(3):115–130

Kim J, Leachman RC, Suhn B (1996) Dynamic release control policy for the semiconductor wafer fabrication lines. J Oper Res Soc 47:1516–1525

Rose O (1999) CONLOAD—a new lot release rule for semiconductor wafer fabs. Proceedings of Winter Simulation Conference, 850–855

Rose O (2001) CONWIP-like lot release for a wafer fabrication facility with dynamic load changes. Proceedings of SMOMS, Seattle

Qi C, Sivakumar AI, Gershwin SB (2009) An efficient new job release control methodology. Int J Prod Res 47(3):703–731

Li Y, Jiang Z, Jia W (2014) An integrated release and dispatch policy for semiconductor wafer fabrication. Int J Prod Res 52(8):2275–2292

Kim Y-D, Kim J-G, Choi B, Kim H-U (2001) Production scheduling in a semiconductor wafer fabrication facility producing multiple product types with distinct due dates. IEEE Trans Robot Autom 17(5):589–598

Uzsoy R, Lee CY, Martin-Vega LA (1992) A review of production planning and scheduling models in the semiconductor industry part i: system characteristics, performance evaluation and production planning. IIE Trans 24(4):47–60

Uzsoy R, Lee CY, Martin-Vega LA (1994) A review of production planning and scheduling models in the semiconductor industry part ii: shop-floor control. IIE Trans 26(5):44–55

Fowler JW, Hogg GL, Mason SJ (2002) Workload control in the semiconductor industry. Prod Plan Control 13(7):568–578

Panwalkar SS, Iskander W (1977) A survey of scheduling rules. Oper Res 25(1):45–61

Blackstone JH, Phillips DT, Hogg GL (1982) A state-of-the-art survey of dispatching rules for manufacturing job shop operations. Int J Prod Res 20:27–45

Sarin SC, Varadarajan A, Wang L (2011) A survey of dispatching rules for operational control in wafer fabrication. Prod Plan Control 22(1):4–24

Glassey CR, Resende MG (1988) A scheduling rule for job release in semiconductor fabrication. Oper Res Lett 7(5):213–217

SXC L, Kager PW (1989) A robust production control policy for VLSI wafer fabrication. IEEE Trans Semicond Manuf 2(4):159–164

Spearman ML, Woodruff DL, Hopp WJ (1990) CONWIP: a pull alternative to kanban. Int J Prod Res 28:879–894

Glassey CR, Shanthikumar JG, Seshadri S (1996) Linear control rules for production control of semiconductor fabs. IEEE Trans Semicond Manuf 9(4):536–549

Kim D, Yeong LHD, Kim UJ (1998) A simulation study on lot release control, mask scheduling and batch scheduling in semiconductor wafer fabrication facilities. J Manuf Syst 17(2):107–117

Chung SH, Lai CM (2006) Job releasing and throughput planning for wafer fabrication under demand fluctuating make-to-stock environment. Int J Adv Manuf Technol 31:316–327

Lin HY, Tsai HC, Lee EC, Liu KS (2007) A dynamic releasing scheme for wafer fabrication. International Journal of the Computer, the Internet and Management 15(1):33–42

Tabatabaei RA and Salazar CFR, (2011) Effective wip dependent lot release policies: a discrete event simulation approach. Proceedings of Winter Simulation Conference

Lawton JW, Drake A, Henderson R, Wein LM, Whitney Rand Zuanich D, (1990) Workload regulating wafer release in a GaAs fab facility. International Semiconductor Manufacturing Science Symposium

Duenyas I (1994) A simple release policy for networks of queues with controllable inputs. Oper Res 42(6):1162–1171

Yan H, Lou S, Sethi S, Gardel A, Deosthali P (1996) Testing the robustness of two-boundary control policies in semiconductor manufacturing. IEEE Trans Semicond Manuf 9(2):285–288

Wendell GG (2002) A simulation study comparing performance of conwip and bottleneck based release rules. Production Planning and Control: The Management of Operations 13(2):211–219

Ignizio PJ, (2003) The implementation of conwip in semiconductor fabrication Facilities. Future fab international issue 14

Chung SH, Pearn WL, Lee AHI, Ke WT (2003) Job order releasing and throughput planning for multi-priority orders in wafer fabs. Int J Prod Res 41(8):1765–1784

Chern CC, Haung KL (2004) A heuristic control method for a single product, high volume wafer fabrication process to minimize the number of photomask changes. J Manuf Syst 23(1):30–45

Qi C and Sivakumar AI (2005) Closed loop job release based on WIPLOAD control in semiconductor wafer fabrication. Thesis submitted to Nanyang Technological University

Qi C, Sivakumar AI and Hidayat ADK (2008) Experimental study on variations of wipload control in semiconductor wafer fabrication environment. Winter Simulation Conference

Rezaie K, Eivazy H and Shirkouhi SN (2009) A novel release policy for hybrid make to stock/make to order semiconductor manufacturing systems. International Conference on Development in E-Systems Engineering

Khouly IAE and Kilany KS (2012) A simulation study of lot flow control in wafer fabrication facilities. Proceedings of the 2012 International Conference on Ind Eng and Oper Manag, Istanbul, Turkey, July 3–6

Suri R and Sanders JL, (1993) Handbooks in OR and MS, performance evaluation of production networks. Amsterdam Elsevier Sciences, 199–286

Sivakumar AI, Chong CS (2001) A simulation based analysis of cycle time distribution, and throughput in semiconductor backend manufacturing. Comput Ind 45:59–78

Wu MC, Huang YL, Chang YC (2006) Dispatching in semiconductor fabs with machine-dedication features. Int J Adv Manuf Technol 28:978–984

Yongxian L, Xiaotian L, Jinfu Z (2008) Research on job-shop scheduling optimization method with limited resources. Int J Adv Manuf Technol 39:386–392

Eivazy H, Rabbani M, Ebadian M (2009) A developed production control and scheduling model in the semiconductor manufacturing systems with hybrid make-to-stock/make-to-order products. Int J Adv Manuf Technol 45:968–986

Zhang H, Jiang Z, Guo C (2009) Simulation-based optimization of dispatching rules for semiconductor wafer fabrication system scheduling by the response surface methodology. Int J Adv Manuf Technol 41(1–2):110–121

Chung YH, Ham WK, Park SC (2014) Production rate based dynamic dispatching rule selection in a wafer fab. International Journal of Materials, Mechanics and Manufacturing 2(3):197–201

Li L, Zhihong M (2016) An efficient adaptive dispatching method for semiconductor wafer fabrication facility. Int J Adv Manuf Technol 84(1–4):315–325

Sharma P, Jain A (2016) New setup-oriented dispatching rules for a stochastic dynamic job shop manufacturing system with sequence dependent setup times. Concurrent Engineering: Research and Applications 24:58–68

Chung YH, Lee S, Park SC (2016) Dispatching for order-driven FABs with backward pegging. Cogent Engineering 3(1)

Chung YH, Seo JC, Kim CM, Kim BH, Park SC (2017) Reservation based dispatching rule for make-to-order wafer fab with high priority lots. Concurr Eng 25(1):68–80

Monch L, Fowler JW and Mason SJ (2012) Production planning and control for semiconductor wafer fabrication facilities. Modeling, Analysis and Systems, Springer

Singh R and Mathirajan M (2016). Investigation of existing release policies and development of a few efficient release policies for wafer fabrication system—a simulation approach. Ph.D. thesis, Indian Institute of Science, Bangalore

Chen BZ, Pan XW, Li L, Chen QJ and Xu WS (2014) A release control policy (WRELM) for semiconductor wafer fabrication facilities. Proceedings of the 11th IEEE International Conference on Networking, Sensing and Control, April 7–9, IEEE xplore

Park J and Morrison JR (2015) Controlled wafer release in clustered photolithography tools: flexible flow line job release scheduling and an LMOLP heuristic. IEEE xplore, 642–655

Baker CT, Dzielinski BP (1960) Simulation of a simplified job shop. Journal of Management Science 6(3):311–323

Conway RW, Maxwell WL and Miller LW (1967) Theory of scheduling. Dallery Addison-Wesley

Dabbas RM, Chen HN, Fowler JW, Shunk D (2001) A combined dispatching criteria approach to scheduling semiconductor manufacturing systems. Comput Ind Eng 39(3–4):307–324

Vargas-Villamil FD, Rivera DE, Kempf KG (2003) A hierarchical approach to production control of re-entrant semiconductor manufacturing lines. IEEE Trans Control Syst Technol 11(4):578–587

Hernandez JAR and Fernandez E (2009) A simulation based approximate dynamic programming approach for the control of the Intel Mini Fab benchmark model. Proceedings of Winter Simulation Conference

Khouly IAE, Kilany KSE and Sayed AEE (2011) Effective scheduling of semiconductor manufacturing using simulation. World Acad Sci Eng Technol, 5(7)

Li L and Fei Q (2012) A modular simulation system for semiconductor manufacturing scheduling. PRZEGL Ą D ELEKTROTECHNICZNY (electrical review), ISSN 0033-2097, R 88 NR 1b/2012

Jang H, Jung TY, Yeh K, Lee JH (2013) A model predictive control approach for fab-wide scheduling in semiconductor manufacturing facilities. The International Federation of Automatic Control (IFAC) Proceedings, Elsevier 46(24):493–498

Jung TY, Jang H, Lee JH (2015) Move blocking strategy applied to re-entrant manufacturing line scheduling. Int J Control Autom Syst 13(2):410–418

Sarah AV, Christiano CE, Alberto PAL and Douglas AC (2015) Optimization of a semiconductor manufacturing process using a reentrant model. Exacta–EP, São Paulo, 13(2): 275–284

Spier J, Kempf K (1995) Simulating the emergent behaviour in manufacturing systems. Proceedings of IEEE/SEMI Advanced Semiconductor Conference, 90–94

Hung YF, Leachman RC (1999) Reduced simulation models of wafer fabrication facilities. Int J Prod Res 37(12):2685–2701

Rose O, (2003) Comparison of due-date oriented dispatching rules in semiconductor manufacturing. Proceedings of Industrial Engineering Research Conference

Fowler J and Robinson J (1995) Measurement and improvement of manufacturing capacity (mimac) designed experiment report. Technology transfer 95062860A-TR, SEMATECH

Urlings T and Ruiz R (2010) Genetic algorithms with different representation schemes for complex hybrid flexible flow line problems. International Journal of Meta-heuristics, 1(1)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Singh, R., Mathirajan, M. Experimental investigation for performance assessment of scheduling policies in semiconductor wafer fabrication—a simulation approach. Int J Adv Manuf Technol 99, 1503–1520 (2018). https://doi.org/10.1007/s00170-018-2414-y

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00170-018-2414-y