Abstract

For the high dynamic GPS receiver, the system key technology is to acquire the PN signal. The high dynamic characteristic of the system refers to that the radial distance and rate between the navigation satellite and the receiver result in the GPS signal phase delay and Doppler frequency shift, which makes signal acquiring more difficult. It needs a long acquiring time when using the general slippage correlation acquisition method. In order to improve the acquiring performance, a FFT based acquiring method is analyzed, the implementation based on FPGA is introduced. By using the high dynamic GPS signal generator to conduct experiments, the availability of the method is proved. Additionally, the improving measures are presented.

Access provided by Autonomous University of Puebla. Download conference paper PDF

Similar content being viewed by others

Keywords

1 Introduction

Signal acquiring is to estimate the pseudo-code phase and Doppler frequency shift of the received signal, and to initialize the track loop with such estimations. For the PN signal acquiring, slippage correlation acquisition method and matched filter method are usually adopted [1, 2]. It needs a long time to acquire signal by the slippage correlation acquisition method due to pseudo-code cycle time, resulting from the method of time domain and frequency domain serial search that related to the phase of each frequency point. To some extent, a matched filter can achieve parallel computing, not affected by pseudo-code cycle time, but it takes up a lot of hardware resources. Therefore, this system adopts the domain FFT based parallel algorithm for signal acquiring.

2 Basic Algorithm

C/A code acquiring in the slippage correlation acquisition method refers to a code related process in time domain, this process can also be carried out within the frequency domain. That is, it can be faster to adopt FFT based acquiring algorithm.

Provided that sampling interval \((\Delta \mathrm{t}={\mathrm{t}}_{\mathrm{k}+1}-{\mathrm{t}}_{\mathrm{k}})\) is a fixed constant, the GPS after inputting signal sample can be represented as [3],

whereas, n refers to serial number of code starting time \(\widehat{{t}_{s(n)}}={t}_{0}+n\Delta t\), namely the code phase; \( CA_{{k - n}} = CA\{ [1 + \eta (k - n)\Delta t]\} \) refers to signal sampling form of pseudo code.

When local carrier frequency is fixed, that is, one Doppler frame is selected [4, 5], \(z(n,\hat{\omega }D)\) can be calculated according to the code phase n, i.e. \(z\left(0,\widehat{\omega }D\right),z\left(1,\widehat{\omega }D\right),\dots ,z\left(L-1,\widehat{\omega }D\right)\). According to the convolution theorem, we can get the Formula (2):

The above formula applies the cycle characteristic of the C/A code, namely \({\mathrm{CA}}_{\mathrm{K}}={\mathrm{CA}}_{\mathrm{L}+\mathrm{K}}\) where L is the C/A code cycle [6]. The maximum value of k is the estimated value of \({t}_{s}\).

Therefore, frequency domain FFT based acquiring algorithm is to realize the parallel acquisition of PN code phase and Doppler frequency shift according to the property of inverse transform that the convolution in time domain is equal to the multiplication in frequency domain [7].

Figure 1 shows FFT based fastd code acquiring circuit diagram in frequency domain.

3 Implementation

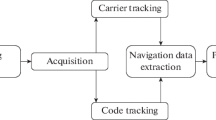

Based on the above algorithm analysis, this paper designs a more practical engineering application. See hardware function module for FFT based acquiring in Fig. 2.

3.1 Data Storage and FFT Arithmetic (FPGA)

Due to the larger scale of the system signal processing with high speed and high precision, system adopts FPGA chip (Vertex2XC2V3000), which can realize large-scale data parallel processing and meet the requirement. In addition, the FPGA has outstanding performance on flexibility and extensibility. FIFO chip is adopted for external storage, which avoids the short of the FPGA storage space and achieves the high-speed data transmission.

3.2 FFT Scheme Design

Based on the unit structure in Fig. 3, we can design a multi-point FFT or IFFT operation module. The Fig. 4. Shows the FFT module.

First of all, enter data (2N point) into the input data memory. These data can be divided into multiple sets of 1024 points, and each set carries out FFT arithmetic through a corresponding 1024-point FFT processing core. For the first time after the 1024-point combined FFT computation, the result is stored in the output data memory. However, only when adjust the data storage order in the memory can we get the correct result for the next 1024-point combined FFT arithmetic. Thus, the data in the output memory of FFT processing unit can be reorganized by means of the address generator and introduced to the input data memory for the next FFT arithmetic. At the last time the computing results directly stored in the output data memory for the final output.

4 Algorithm Validation

In order to verify the validity of the algorithm, high dynamic GPS test simulator is adopted. STR4760 GPS signal simulator, which can evaluate the high positioning precision of the dynamic user receiver, can be used for the test and validation of GPS receiver.

STR4760 technical indicators: relative speed between navigation satellite and users: 120000 m/s, accelerated speed: 360 g and 500 g/s acceleration; GPS signal source controlled by ALPHA workstation, reliable in performance. Visual satellite status diagram from the simulator is as shown in Fig. 5.

The algorithm hardware platform is used to search the entire range. See search correlation matrix for No. 5 GPS satellite (visual) in Fig. 6, a significant correlation peak can be observed.

5 Conclusion

In this paper, we discuss the hardware design of fast acquiring technology for GPS receiver and the detailed industry application of circuit for each part. Experiments show that if Doppler frequency shift is between ±50 kHz and the shift length is 500 Hz, it takes 1.92 s (0.009 6 × 200 = 1.92 s) to blind acquiring a satellite at most and takes up to 42 s to collect all the ephemeris. The new technology takes up to 1 min in positioning, which has greatly improved compared with the time consuming by original satellite-borne GPS receiver.

References

Guangshu, H.: Digital Signal Processing: Theory, Algorithms and Implementation. Tsinghua University Press, Beijing (1997)

Zhihe, Q., Wanyi, W.: The Principle and Application of GPS. Electronic Industry Press, Beijing (2002)

Qishan, L.X.Z., Qing, C.: High dynamic GPS C/A code signal acquiring scheme and implementation. Beihang Univ. J. 28(3), 358–361 (2002)

Qihua, H., Guoliang, S.: Instantaneous frequency measurement based on slippage fourier transform. Electron. Measur. Technol. 29(3), 35–40 (2006)

Dingrong, X.W.S., Shujian, L.: GPS receiver pseudo random code fast acquiring technology. Beihang Univ. J. 29(16), 489–492 (2003)

Xiaoyan, X., Jianshu, L., Dingrong, S., et al.: Fast Signal Acquiring in the High Dynamic Spread Spectrum Communication System. 26 (2), 22–27 2005

Huang Zhen, L., Jianhua, Y.S.: fast doppler frequency shift acquiring for satellite communications. J. Electron. 4, 1053–1055 (2003)

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2023 The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Xiaojiang, Y., Feifei, Z., Qian, Y., Dongbo, P. (2023). Design and Implementation of FFT Based Fast Acquiring of High Dynamic GPS Signal Based on FPGA. In: Urbach, H.P., Jiang, H. (eds) Proceedings of the 7th International Symposium of Space Optical Instruments and Applications. ISSOIA 2022. Springer Proceedings in Physics, vol 295. Springer, Singapore. https://doi.org/10.1007/978-981-99-4098-1_36

Download citation

DOI: https://doi.org/10.1007/978-981-99-4098-1_36

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-99-4097-4

Online ISBN: 978-981-99-4098-1

eBook Packages: Physics and AstronomyPhysics and Astronomy (R0)