Abstract

This paper proposes an adaptive voltage position (AVP) control method for the improved phase shift full bridge (PSFB) soft switching DC-DC converter. For the improved topology, clamping diodes and resonant inductor are added. All power Mosfets can achieve soft switching at full load conditions and since clamping di-odes are utilized, the voltage oscillation of the output rectifier diodes can be de-creased. In order to improve the output voltage response ability of the converter in the process of load conversion, An AVP control method based on output cur-rent feedback regulation is proposed. Working principle of the topology and control method are introduced. Small signal model and controller design process are analyzed. Performance of the proposed control method and topology are verified by a 500W simulation model.

Access provided by Autonomous University of Puebla. Download conference paper PDF

Similar content being viewed by others

Keywords

1 Introduction

With the development of industrial facilities, military equipment, microprocessors and industrial server more and more equipment or devices show the characteristics of load mutation [1,2,3,4]. In addition, there are a lot of pulse loads in the application of communication power supply, vehicle power supply and ship power supply system. The power required by the pulse load is constantly changing, the current change rate di/dt is very high, and the change of load current has a certain periodic characteristics. When the pulse load is running, the output voltage of power supply system should be stable enough, and the voltage overshoot caused by load current mutation should be within the allowable working voltage range of load. Thus these applications put forward higher requirements for the performance of switching power supply. It is necessary to design better DC/DC converter to meet the increasing dynamic response requirements of the output load.

In order to reduce the output voltage overshoot or drop, the traditional method of increasing the output filter capacitor will not only increase the cost, but the power density is reduced. In order to improve the dynamic response without additional output capacitance, many control methods and circuit structures are proposed. In [5, 6], hysteresis control is proposed, in [7, 8] V2 control is analysed and in [9] interleaving technology is introduced.

Among all kinds of technologies, the method of improving dynamic performance by optimizing control strategy is widely concerned, such as AVP control. AVP control strategy is often utilized to reduce the output voltage fluctuation in the process of load conversion without adding output filter capacitance [10,11,12]. Figure 1 depicts the waveforms of the output voltages of the converter which applied with and without AVP control method.

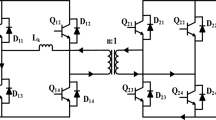

At present, the research of the AVP control method is mainly based on Buck topology [10,11,12]. Thus, the AVP control algorithm applied to other circuit topologies needs to be studied. In low voltage and high current applications, in order to achieve electrical isolation between input and output side of the converter, phase shifted full bridge circuit topology is often used, as shown in Fig. 2.

As shown in Fig. 2, through reasonable design of Lr, the power switches can achieve ZVS at rated load conditions. However, in this topology, the lagging lag has narrow soft switching range, and voltage oscillation across rectifier diodes are not reduced. In order to broaden the soft switching range, an resonance network is added in [13]. However the voltage spikes of the diodes still not be solved. To reduce voltage spikes, snubbed circuits [14, 15] have been utilized. However the circuit topology is complex.

In this paper, a phase shift full bridge soft switching DC-DC converter based on clamping diodes is introduced. The AVP control method based on output current feedback regulation which applied on DC-DC converter is proposed and studied. The working principle of the topology and the control method are analysed. The small signal model and the controller design process are presented. And the performance of the new control system is verified by 500W simulated prototype.

2 System Configuration

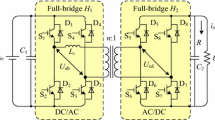

Figure 3 shows the improved topology and the AVP control method. As it shown, T is the transformer of the topology. On the primary side of topology, vin is the input voltage, vo and io is the output voltage and output current, respectively; Q1–Q4 are the power switches of the converter; D1–D4 and C1–C4 are the parasitic diode and junction capacitance of Q1–Q4, respectively; Lr is the resonant inductor and D7–D8 is the clamping diodes. On the second side of topology, D5, D6 are the rectifier diode and Cd5, Cd6 are the absorption capacitance of the diodes. Lf and Cf is the output filter inductance and capacitor; Ro is the output load.

For the control circuit, Z2 is sampling coefficient of output feedback voltage; ir is the output current adjustment feedback reference; vdr is output voltage droop adjustment signal; vref is the output voltage given signal; Zf is compensation coefficient of output voltage control loop; vc is the output signal of the control loop; PSR is phase shift regulating circuit and d1–d4 are the duty cycle adjustment signal.

3 Introduction

3.1 DC/DC Topology Operation Principle

There are 18 operating modes in each cycle. Compared with the traditional phase shifted full bridge converter, it mainly increases the conduction modes of the two clamping diodes. Since the principle of other modes is basically the same as that of traditional converter, this paper only analyses the working principle of the two clamping diodes conduction modes. The equivalent circuit of each mode are shown in the following Fig. 4.

In the analysis, assume that: rectifier diode is regarded as the ideal diode; other devices, such as inductors and capacitors, are ideal components, and the leakage inductance of transformer is ignored; \(L_{{\text{f}}} \gg L_{{\text{r}}} /N^{2}\), where N is the turn ratio of the primary and secondary sides of the transformer;

At t0, D5 turns off and D6 turns on. Lr resonates with CD5 and CD5 is charged. ip and iLr continue to increase in the opposite direction.

During the period of [t0-t1], the potential of point B is always equal to the input voltage vin. Due to the continuous accumulation of electric charge of CD5, vBC increases. Thus the potential at point C decreases continuously. At t1, the voltage across CD5 is charged to 2vin/N. At this point, the potential of point C drops to zero, D8 is clamped, and vBC is clamped to vin.

At t1, D8 turns on and provides current channel. The primary current ip of transformer is reduced to the value of which iLf converted to the primary side. After that, ip begins to increase in negative direction, while the resonant inductor current iLr remains constant. And the current difference between ip and iLr flows through the clamping diode D8 during this period. At t2, the primary current ip of the transformer increases to value of the resonant inductor current iLr, and at this moment D8 turns off.

During the period of [t3–t4], the potential of point B is equal to zero. Due to the continuous accumulation of electric charge of CD6, vCB increases. Thus the potential at point C rises continuously. At t4, the voltage across CD6 is charged to 2vin/N. At this point, the potential of point C rises to vin, D7 turns on, and vCB is clamped to vin.

At t4, D7 turns on and provides current channel. The primary current ip of transformer is reduced to the value of which iLf converted to the primary side. After that, ip begins to increase in positive direction, while the resonant inductor current iLr remains constant. And the current difference between ip and iLr flows through the clamping diode D7 during this period. At t5, the primary current ip of the transformer increases to value of the resonant inductor current iLr, and at this moment D7 turns off.

It can be seen from the above analysis that the clamping diodes D7 and D8 only conduct once in a switching cycle.

3.2 AVP Control Method Operation Principle

As shown in Fig. 5, when io > ir, it indicates that it is a heavy load. At this moment, through comparator, adjust the output voltage droop signal value to zero. When io < ir, it indicates that it is a light load. At this moment, through comparator, adjust the output voltage droop signal value vdr to negative direction. Then the output voltage droop signal value vdr is overlaid to the output voltage given value to form a new output voltage given signal vref_H. The output voltage controller makes the output voltage vo of the converter follow the given signal to realize AVP control.

4 Control Design Process

4.1 Small Signal Model

The phase shifted full bridge ZVS PWM converter is a buck type converter. So its small signal model is similar to buck circuit. The difference is that the phase-shifting full bridge ZVS PWM converter causes the loss of duty cycle when soft switch is realized.

The small signal model of buck converter is depicted as follows.

In Fig. 6, \(\hat{v}_{{{\text{in}}}}\) is the small signal disturbance value of input voltage; \(\hat{d}\) is the small signal disturbance value of duty cycle; \({ }\hat{i}_{{{\text{Lf}}}}\) is the small signal disturbance value of inductance current; \(\hat{i}_{{{\text{Cf}}}}\) is the small signal disturbance of charge/discharge current of Cf; \(\hat{i}_{{\text{o}}}\), \(\hat{v}_{{\text{o}}}\) is the small signal disturbance value of output current and voltage; Deff is equivalent duty cycle of converter.

The equivalent duty cycle of PSFB converter is as follows.

As can be seen from (1), the factors that affect Deff are as follows: Duty cycle D of original buck topology; input voltage vin and the output filter inductor average current iLf.

The above formula is disturbed,

Thus, the small signal model of phase shifted full bridge soft switching PWM converter can be obtained, as shown in Fig. 7.

4.2 Control Design Process

According to the small signal model, the circuit topology related transfer functions are calculated as follows.

Transfer function Gvd(s) of duty cycle \(\hat{d}\left( s \right)\) to output voltage \(\hat{v}_{o} \left( s \right)\) is shown as follows.

where, \(R_{{\text{s}}} = 2L_{{\text{r}}} f_{{\text{r}}} /N^{2}\), \(f_{{\text{r}}} = 2/T_{{\text{s}}}\).

Transfer function Gid(s) of duty cycle \(\hat{d}\left( s \right)\) to output current \(\hat{i}_{o} \left( s \right)\) is shown as follows.

According to the small signal model and the related transfer function, the control loop diagram of the proposed control system is shown in Fig. 8.

As shown in Fig. 8, Gc(s) is the Transfer function of compensation controller; Gm(s) is the transfer function of pulse width modulator; H(s) is the output voltage feedback sampling coefficient.

According to the control loop diagram, the open loop transfer function is deducted as follows.

where Gm = 1/Vm, Vm is the peak value of the saw tooth wave.

According to the compensation principle of the feedback controller, the cut-off frequency is 1/5–1/10 of the switching frequency, and the phase angle margin is 30°–60°. Based on the zero pole compensation principle, the PI controller is designed. The amplitude frequency and phase frequency characteristics of the system after correction are shown in Fig. 9.

5 Simulation Results

On the basis of the above design, a simulation module was built. The simulation design parameters are as follows: \(v_{{{\text{in}}}}\) = 600V. \(v_{{\text{o}}}\) = 48V. Under light load condition, the output current is 5A and under heavy load condition, the output current is 10A.

Figure 10 shows the soft switching conditions of the main power switch in AVP control mode under heavy load condition.

As shown in Fig. 10, under the condition of heavy load, zero voltage switching (ZVS) can be realized in both lead leg and lag leg.

The simulation waveform of voltage across the rectifier diodes on second side of the converter is shown in Fig. 11.

According to the above simulation waveform, the voltage spike across the rectifier diodes is reduced and clamped to input voltage.

In Fig. 12, the current of clamp diode is simulated. The simulation waveform shows that each diode only turns on once during each cycle.

Designing the load of the converter is switched from light load to heavy load in 0.1 s, and then from heavy load to light load at 0.2 s. The simulation waveforms of the output voltage and current of the converter with/without AVP control mode are shown in Fig. 13.

As shown in Fig. 13, In AVP control mode, the fluctuation of output voltage and the recovery time of dynamic response are reduced effectively in the process of heavy/light load converting.

6 Conclution

In this paper an AVP control method is applied to the improved phase shift full bridge soft switching DC-DC converter. By combining the AVP control method with the topology, not only the output voltage response ability to the load converting can be improved, but also the soft switching of the converter switches can be achieved. In the proposed converter, the AVP control method is based on output current feedback regulation. This can simplify the design complexity of the controller while improving the dynamic response capability to the output load. Meanwhile, the PSFB circuit topology with clamping diode can not only realize soft switching, but also the peak voltage oscillation across the rectifier diode is clamped. At the same time, the clamping diode only turns on once in a switching cycle, which improves the efficiency of the converter.

References

Meng, B.-K., Gao, L.-Y., Tong, X.X., Cui, J.-P., Yang, X.-M.: Application of photovoltaic uninterruptible power supply system. In: Distribution Network Communication Station. CICED Conference Proceedings, Tianjin, China, pp. 101–105 (2018)

Liu, Y., Chen, R.: Application of auto-reclosing residual current device in lightning protection for communications power supply. In: IEEE EMC-Beijing Conference Proceedings, Beijing, China (2018)

Feng, R., Wang, H., Xie, K., Xu, C., Hu, E.: The research and design of communication power supply based on the proton exchange membrane fuel cell. In: IEEE International Conference on Information Theory and Information Security, Beijing, China, pp. 919–922 (2010)

Hans, M.R., Bhagwat, N.B.: Implementation of switched mode power supply with power quality enhancement using zeta converter. In: ICOSEC Conference Proceedings, Trichy, India (2020)

Nguyen-Van, T., Abe, R.: An indirect hysteresis voltage digital control for half bridge inverters. In: IEEE Global Conference on Consumer Electronics, Kyoto, Japan, (2016)

Jun, L., Dazhi, W.: Study and simulation of a novel hysteresis current control strategy. In: International Conference on Intelligent Computation Technology and Automation, Changsha, China, pp. 306–309 (2009)

He, S., et al.: DCM low frequency oscillation in valley V2 controlled boost converter. In: IEEE ICIEA Conference Proceedings, Xi'an, China, pp. 2049–2054 (2019)

Cheng, K.Y., Yu, F., Mattavelli, P., Lee, F.C.: Characterization and performance comparison of digital V2-type constant on-time control for buck converters. In: IEEE COMPEL Conference Proceedings, Boulder, CO, USA (2010)

Chang, C.H., Chang, E.C., Cheng, C.A., Shen, C.L.: A step-up/down inverter implemented with the boost-interleaved buck-boost dc-dc converter. In: IEEE IFEEC Conference Proceedings, Taipei (2015)

Hu, K.Y., Chen, B.M., Tsai, C.H.: A digitally controlled buck converter with current sensor-less adaptive voltage positioning (AVP) mechanism. In: VLSI-DAT Conference Proceedings, Hsinchu (2017)

Yang, F., Yang, J., Yao, K., Hua, H.: Adaptive voltage position control for pulse power supply in electrical discharge machining. IEEE Trans. Industr. Electron. 66(8), 5895–5906 (2019)

Chen, C.-J., Shao-Hung, L., Hsiao, S.-F., Chen, Y.-J., Huang, J.-R.: A current-mode buck converter with reconfigurable on-chip compensation and adaptive voltage positioning. IEEE Trans. Power Electron. 34(1), 485–494 (2019)

Niu, R., Weiguo Zhang, W., Chen, L.S., Ning, G., Ma, D.: A Novel ZCS full-bridge PWM converter with simple auxiliary circuits, pp. 1–6. IEEE PEAC Conference Proceedings, Shenzhen (2018)

Lee, I.O., Moon, G.W.: Phase-shifted PWM converter with a wide ZVS range and reduced circulating current. Trans. Power Electron. 28(2), 908–919 (2013)

Ting, Y., de Haan, S., Ferreira, J.A.: The partial-resonant single active bridge DC-DC converter for conduction losses reduction in the single active bridge, pp. 987–993. IEEE ECCE conference proceedings, Melbourne (2013)

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2022 The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Zhang, Z., Sun, X., Cai, Z., Yang, S., Yao, Y., Li, F. (2022). AVP Control Method for an Improved Phase Shifted Full Bridge Soft Switching DC-DC Converter. In: Liang, J., Jia, L., Qin, Y., Liu, Z., Diao, L., An, M. (eds) Proceedings of the 5th International Conference on Electrical Engineering and Information Technologies for Rail Transportation (EITRT) 2021. EITRT 2021. Lecture Notes in Electrical Engineering, vol 867. Springer, Singapore. https://doi.org/10.1007/978-981-16-9909-2_75

Download citation

DOI: https://doi.org/10.1007/978-981-16-9909-2_75

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-16-9908-5

Online ISBN: 978-981-16-9909-2

eBook Packages: EngineeringEngineering (R0)