Abstract

In this work, new two-dimensional (2-D) analytical solution of threshold voltage (Vth) for un-doped Double Gate MOSFETs is proposed. In this research work, Green’s function based techniques are applied to solve the Poisson equations in 2-dimensional and we derived the threshold voltage (Vth) expression by using the concept of surface potential. This design is supposed uniform doping profile in Si area. The design is compared with existing experimental results and we got better solutions compared to existing works.

Access provided by Autonomous University of Puebla. Download conference paper PDF

Similar content being viewed by others

Keywords

- Minimum surface potential

- Green’s function

- Symmetric DG-MOSFET

- Threshold voltage

- 2D Poisson equations and Un-doped

1 Introduction

In last two decades, VLSI (very large-scale integration) Technology CMOS has been used as a fundamental building block for low power system designs. Double-Gate (DG) MOSFET is emerging as a latest research domain in VLSI because the scaling of these devices is possible to the minimum channel length L possible for provided process technology parameters [1]. The scaling of MOSFET at deep submicron level has shown new and serious challenges for the designing and fabrication of future integrated circuits. When the MOSFET dimensions are scaled down, both the supply voltage and the gate tox be scaled down. The short channel effects [2] are controlled by scaling down both the gate-oxide thickness and channel length. The scaling of gate-oxide thickness is limited to about 1 nm because of high gate tunneling current [3, 4]. Scaling down the device dimension in nanometer regime, leakage currents plays an important role which needs more attention from the designer. Scalability of DG-MOSFETs is limited by sub-threshold swing which is an important design parameter. Formation of two channels in the symmetric DG MOSFET [5] provides steep sub-threshold swing, high drive current, and trans-conductance. The sub-threshold swing and other short channel effects can be optimized by using appropriate gate dielectric [6]. Therefore new MOSFET structures such as Dual Gate and Tri-Gate MOS transistors [7] are proposed to replace conventional planer MOSFET. It is also important that these new structure of MOSFETs are compatible with latest designing and fabrication techniques [8] of silicon integrated circuits. Dual gate MOSFETs also referred to as inversion charge transistors have many advantages over conventional MOSFETs. First, there is a considerable reduction in the device area. Second, DG MOSFET’s miller capacitance and output conductance can be further considerably reduced which makes it useful device for the designing of analog integrated circuits. Third, the breakdown voltage of the device can be made very high by using proper design methodology. Fourth, short channel effects in scaled devices are drastically minimized. Comparable to conventional MOSFET, in case of Dual Gate MOSFET, both gates control the properties of channel. Thus more scaling of gate length can be performed in DG MOSFETs. DG MOSFETs is better alternative of conventional MOSFETs because DG MOSFETs have improved on short channel effects. Also DG MOSFET has higher current density. Therefore performance of the devices can be maintained low leakage and higher current density by employing DG MOSFETs. In DG MOSFETs better manage short channel effects and Vth is achieved ideally without altering the concentration of channel dopants. This technique diminished the statistical dopant fluctuations [9] an also reduces the phenomena of impurity scattering. Many structures and techniques were used SOI devices with less short channel effects [10, 11]. Using DG MOSFETs can minimize short channel effects. The conventional MOSFET cannot be scaled down below 10 nm process technology. Therefore DG MOSFETs are widely employed in the analog electronic circuits where reduced short-channel effects, electronic gain control capability, high breakdown voltages are required. DG MOSFETs are fabricated in below 20 nm fabrication process technology by using metal gate technology for both the gates that diminished the poly depletion effects. The effects are degradation [12] and mobility of dopant atoms are eliminated of DG MOSFETs. Due to these advantages, an analytic and simple threshold-voltage model is highly desirable for un-doped DG MOSFETs as one of the key point parameters for the design of such nano-scale devices. More advantages of Dual Gate MOSFETs are improved trans-conductance, early voltage, and carrier transport efficiency. Accurate and physics-based formulations are required for implementation of high-speed VLSI circuits comprising of compact MOSFET model. Due to these requirements for the device, the un-doped symmetric DG MOSFETs are best-suited device structure because of the thin and un-doped nature of the channel. In the situation of surface inversion near oxide-silicon interface, the energy band bends up to 2ФB at the silicon-oxide interface. The same phenomena can be utilized for the analysis of the uniformly doped carrier concentration in the substrate. For the analytical modeling of the 2-D characteristics of DG MOSFETs, the two-dimensional Poisson’s equations are analyzed by using suitable initial and final boundary conditions. Concept of Green’s function techniques are used to get the solution for the two-dimensional Poisson’s equation considering the uniform doping profile. The modeling of DG MOSFET’s reported by authors [13,14,15,16,17,18,19]. For the optimization of the performance of the devices in nanometer regime for low power applications, Vth of the DG MOSFETs should be properly modeled. The analytical expression for 2-Dimensional Vth in the substrate is derived explicitly and verified by previous existing 2-Dimensional analytical models.

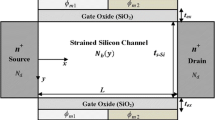

2 Structure of DG MOSFET

Figure 1 discusses the general structure of DG MOSFETs. In this structure of DG MOSFET 2 gates are used. Coupling is enhanced between gate to channel and hence short channel effects are considerably suppressed. DG MOSFETs are categorized as either symmetric DG MOSFET or asymmetric depends upon the voltages are applied to both gates. These two metal gates may or may not have same work functions. In this research work, analysis is done for symmetric DG MOSFETs. The symmetric DG MOSFETs means work function is similar for both gates. The thickness of the gate oxide is equal with same bias voltage is applied. After application of Vds, Vgs, and with constant Quasi-Fermi level is shown in Fig. 1.

3 Modeling of DG-MOSFET

3.1 he Basic Analysis

The cross-sectional view of a thin-film Dual Gate MOS device for two-Dimensional analytical model is shown in Fig. 2. The simplified domains for the analytical solution for the 2D Poisson’s equations [20,21,22,23] along with the suitable boundary conditions are shown in Eq. (1). The below equation shows the 2D Poisson’s equation with respect to rectangular coordinate system.

where \({N}_{A}\) is substrate acceptor and \(f(y)\) is doping profile in Si area. The 2-D Poisson’s equations are converted into 2-D Laplace equations in the back and front oxide regions.

The concept of Green’s function technique is utilized for solution of the 2-Dimensional Poisson’s potential distribution. Simplifying the Green’s function solution into Green’s theorem [16], this is shown below

where \(G({x, y}; {x}^{{{\prime}} },{y}^{^{\prime}})\) is the Green’s function satisfying \({ \Delta }^{2}G=-\delta (x-{x}^{^{\prime}}) \delta (y-{y}^{^{\prime}})\), \({n}^{^{\prime}}\) is the outward direction.

Equation (3) is expression for electrostatic potential distribution and \(\rho \left({x}^{{{\prime}} }, {y}^{^{\prime}}\right)=-q{N}_{A}f({y}^{^{\prime}})\) defined as the charge density of Si region. Assuming uniform doped (\(f\left({y}^{^{\prime}}\right)=1\)). 2D potential equation is shown below.

where \({D}_{sf}^{m}\) and \({D}_{sb}^{m}\) is electric displacement of front & back gate. The \({\varnothing }\left({x, y}\right)\) have to satisfy the boundary conditions,

After solving Eqs. (9) and (10) and we can obtain

where coefficients

3.2 Threshold Voltage Model

The location of \({X}_{min}\) lies on Si surface

From Eq. (9), the position of the minimum surface potential \({x}_{min}\) is

the expression for minimum surface potential \({\phi }_{sf,{\min}}\) is simplified as from above Eq. (15)

The \({V}_{\mathrm{th}}\) for the DG-MOSFET is derived from [24]. The Vth in terms of surface potential is expressed by

where

The threshold voltage roll-off \(\Delta {V}_{\mathrm{th}}\) expression is the difference between the values of threshold voltage for short channel and long-channel devices given as

4 Results and Discussion

Figures 3 and 4 shows the various levels of threshold voltage roll-off \({\Delta V}_{\mathrm{th}}\) in the substrate the length of the channel length for various values of Si film \({t}_{si}\)= (1.5, 5, 10, and 25 nm) at Gate \({t}_{ox}=1\; \mathrm{nm}\) and \({t}_{ox}=1.5\; \mathrm{nm}\) at same Vds = 0.05 V and \({N}_{a}={10}^{17} \;{\mathrm{cm}}^{-3}\) for proposed analytical model and Chen [24]. The Vth roll-off increases with increase in \({t}_{si}\). With the increase in silicon film thickness, the curves are shifted towards right side for constant Vds = 0.05 V and constant gate \({t}_{ox}=1\; \mathrm{nm}\) and \({t}_{ox}=1.5 \; \mathrm{nm}\). The proposed model shows Threshold Voltage roll-off \({\Delta V}_{\mathrm{th}}\) is 5–7% greater than Chen design.

Proposed design compared with Chen [24], \({t}_{ox}=1\; \mathrm{nm}\)

Proposed design compared with Chen [24], \({ t}_{ox}=1.5\; \mathrm{nm}\)

Figure 5 shows the parametric analysis for threshold voltage roll-off for various drain bias voltages \({V}_{ds}\)= (0.005, 1.0 V) and the parameters are \({t}_{ox}=1.5\; \mathrm{nm}\) and silicon film thickness \({t}_{si}=10\; \mathrm{nm}\). Figures 3, 4, and 5 shows the threshold voltage roll-off \({\Delta V}_{\mathrm{th}}\). The proposed model accurately predicts the device behavior compared with the existing works Liang [1] and Chen [24], with 3–5% more accurate.

Proposed design compared with Liang [1], \({t}_{si}=10\; \mathrm{nm}\) and \({t}_{ox}=1.5\; \mathrm{nm}\)

5 Conclusion

The two-dimensional Poisson’s equations have been analytically derived using the concept of Green’s function incorporating suitable initial and final boundary conditions in Silicon area. The accuracy of the proposed model in the substrate (Si-film) is analyzed and verified by existing models. This design is valid for uniform doping profile in Si area. Due to the symmetry of DG-MOSFETS, the distributions of analytic potential for both sides of the surfaces in the substrate are same. It is obvious from simulation results so as to iterative method can only be used to find the minimum surface potential. It can be easily analyzed that better results are produced between the proposed and Chen [24] design analysis for parametric analysis of device structure for various biasing. The proposed analytic voltage model can be applied as a basic concept for high-speed physical analysis of the short-channel effects. It will define the deep-sub micrometer optimized scaling rule for thin-film Silicon on Insulator based MOS transistor in ULSI Technology.

References

Jiang, C., Liang, R., Wang, J., Xu, J.: A two-dimensional analytical model for short channel junctionless double-gate MOSFETs. AIP Adv 5(5), 0571223-13 (2015)

Gupta, K.A., Anvekar, D.K., Venkateswarlu, V.: Modeling of short channel MOSFET devices and analysis of design aspects for power optimization. Int. J. Model. Optim. 3(3), 266–271 (2013)

Avci, U.E., Morris, D.H., Young, I.A.: Tunnel field-effect transistors: prospects and challenges. J. Electr. Dev. Soc. 3(3), 88–95 (2015)

Narendiran, A., Akhila, K., Bindu, B.: A physics-based model of double-gate tunnel FET for circuit simulation. IETE J. Res. 62(3) (2016)

Hosseini, R.: Analysis and simulation of a junctionless double gate MOSFET for high-speed applications. 67(9), 1615–1618 (2015)

Salmani-Jelodar, M., Ilatikhameneh, H., Kim, S., Ng, K., Klimeck, G.: Optimum high-k oxide for the best performance of ultra-scaled double-gate MOSFETs. IEEE Trans. Nanotechnol. 1–5 (2015)

Ture, E., Brückner, P., Godejohann, B.-J., Aidam, R., Alsharef, M., Granzner, R., Schwierz, F., Quay, R., Ambacher, O.: High-current submicrometer tri-gate GaN high-electron mobility transistors with binary and quaternary barriers. J. Electr. Dev. Soc. 4(1), 1–6 (2016)

Bauman, S.J., Novak, E.C., Debu, D.T., Natelson, D., Herzog, J.B.: Fabrication of sub-lithography-limited structures via nanomasking technique for plasmonic enhancement applications. IEEE Trans. Nanotechnol. 14(5), 790–793 (2015)

Saha, S.K.: Modeling statistical dopant fluctuations effect on threshold voltage of scaled JFET devices. IEEE Access J. 4, 507–513 (2016)

Xie, Q., Lee, C.-J., Xu, J., Wann, C., Sun, J.Y.-C., Taur, Y.: Comprehensive analysis of short-channel effects in ultrathin SOI MOSFETs. IEEE Trans. Electr. Dev. 60(6), 1814–1819 (2013)

Colinge, J.-P.: Multiple-gate SOI MOSFETs. Solid-State Electron. 48(6), 897–905 (2004)

Cros, A., Romanjek, K., Fleury, D., Harrison, S., Cerutti, R., Coronel, P., Dumont, B., Pouydebasque, A., Wacquez, R., Duriez, B., Gwoziecki, R., Boeuf, F., Brut, H., Ghibaudo, G., Skotnicki, T.: Unexpected mobility degradation for very short devices : a new challenge for CMOS scaling. IEEE Int. Electr. Dev. Meet. 663–666 (2006)

Rajabil, Z., Shahhoseini, A., Faez, R.: The non-equilibrium green’s function (NEGF) simulation of nanoscale lightly doped drain and source double gate MOSFETs. In: IEEE International Conference on Devices, Circuits and Systems (ICDCS), pp. 25–28 (2012)

Karatsori, T.A., Tsormpatzoglou, A., Theodorou, C.G., Ioannidis, E.G., Haendler, S., Planes, N.G.: Development of analytical compact drain current model for 28nm FDSOI MOSFETs. In: 4th International Conference on Modern Circuits and Systems Technologies, Thessaloniki Greece, pp 1–4,14–15 (May 2015)

Tripathi, S.L., Kumar, M., Mishra, R.A.: 3-D channel potential model for doped symmetrical ultra-thin quadruple gate-all-around MOSFET. J. Electr. Dev. 21, 1874–1880 (2015)

Ávila-Herrera, F., Cerdeira, A., Paz, B.C., Estrada, M., Íñiguez, B., Pavanello, M.A.: Compact model for short-channel symmetric double-gate junction-less transistors. Solid-State Electron. 111, 196–203 (2015)

Zhang, G.-M., Su, Y.-K., Hsin, H.-Y., Tsai, Y.-T.: Double gate junctionless MOSFET simulation and comparison with analytical model. In: IEEE Regional Symposium on Micro and Nanoelectronics (RSM-2013), Langkawi, Malaysia, pp. 410–413, 25–27 (2013)

Yadav, V.K.S., Baruah, R.K.: An analytic potential and threshold voltage model for short-channel symmetric double-gate MOSFET. In: International Symposium on VLSI Design and Test, Coimbatore, India, 16–18 July, 2013

Bhartia, M., Chatterjee, A.K.: Modeling the drain current and its equation parameters for lightly doped symmetrical double-gate MOSFETs. J. Semicond. 36(4), 1–7 (April 2015)

Liang, X., Taur, Y.: A 2-D analytical solution for SCEs in DG MOSFETs. IEEE Trans. Electr. Dev. 51(9), 1385–1391 (2004)

Lo, S.-C., Li, Y., Shao-Ming, Yu.: Analytical solution of nonlinear poisson equation for symmetric double-gate MOSFET. Math. Comput. Model. 46(1–2), 180–188 (2007)

Chiang, T.K.: A novel scaling-parameter-dependent sub threshold swing model for double-gate (DG) SOI MOSFETs: including effective conducting path effect (ECPE). Semicond. Sci. Technol. 19(12), 1386–1390 (2004)

Huaxin, Lu., Taur, Y.: An analytic potential model for symmetric and asymmetric DG-MOSFETs. IEEE Trans. Electr. Dev. 53(5), 1161–1168 (2006)

Chen, Q., Harrell, E.M., Meindl, J.D.: A physical short-channel threshold voltage model for undoped symmetric double-gate MOSFETs. IEEE Trans. Electron Dev. 50(7) (2003)

Maheshwari, V., Malipatil, S., Gupta, N., Kar, R.: Modified WKB approximation for Fowler-Nordheim tunneling phenomenon in nano-structure based semiconductors. In: 2020 International Conference on Emerging Trends in Information Technology and Engineering (ic-ETITE), Vellore, India, 2020, pp. 1–5. https://doi.org/10.1109/ic-ETITE47903.2020.460

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2021 The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Maheshwari, V., Malipatil, S., Garg, N.K., Kar, R. (2021). Two-Dimensional Analytical Expression of Threshold Voltage for Un-doped Double Gate MOSFET. In: Bhateja, V., Satapathy, S.C., Travieso-Gonzalez, C.M., Flores-Fuentes, W. (eds) Computer Communication, Networking and IoT. Lecture Notes in Networks and Systems, vol 197. Springer, Singapore. https://doi.org/10.1007/978-981-16-0980-0_24

Download citation

DOI: https://doi.org/10.1007/978-981-16-0980-0_24

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-16-0979-4

Online ISBN: 978-981-16-0980-0

eBook Packages: EngineeringEngineering (R0)