Abstract

At the advanced stage of technologies, when feature size is being reduced, it is compulsory to introduce other parameters for more accurate modelling of transmission line interconnects. So mutual inductance and coupling capacitance how have become more important role for analysis of high-speed on-line VLSI interconnects. This paper introduces a mathematical aware analysis result for crosstalk noise of ‘L’ type RLC interconnections using mutual inductance. Two RLC interconnect lines of ‘L’ type, are equidistant to each other and used as ‘Aggressor line’ and ‘Victim line’ respectively, whereas, a step signal voltage is employed as input to aggressor line. Other calculative results for Delay and peak noise voltage between these two RLC electrical lines with using mutual inductance, are also introduced in this paper. This paper also shows a comparative result between our derived expression values and BKM values for simulation purpose.

Access provided by Autonomous University of Puebla. Download conference paper PDF

Similar content being viewed by others

Keywords

1 Introduction

Presently, VLSI is the present level of designing and fabrication of ICs and microchips which consist of lacs of transistors on a single chip [1, 2]. In DSM region [3], now it is considered to study of inductive effect as well as capacitive-coupling effects to develop and explain the more accurate and real behaviour of on-chip VLSI interconnects. Delay and Crosstalk noise between VLSI high speed interconnected networks can have occurred due to self and mutual inductance. There are so many approaches presented [4,5,6,7,8,9,10,11,12,13,14,15,16,17,18] for the modelling of interconnect structures. This paper introduces use of closed loop of ‘L’ type RLC interconnect network. Two RLC parallel interconnects and a mutual inductance and coupling capacitance are occurred automatically. These two RLC networks are named as ‘aggressor line’ and ‘victim line’ respectively. The proposed work is much improved work of the BKM [19] model. This paper establishes a mathematical equation of crosstalk voltage of mutually inductively coupled interconnections of RLC type. This paper also introduces expressions for delay and peak noise voltage between adjacent RLC network. This paper is organized remaining follows: Sect. 2 describes Proposed models and of crosstalk voltage and delay analysis. Detailed results of simulation are discussed in portion 3 and portion 4 conclude the paper.

2 Proposed Model

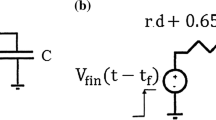

Mathematical and analytical expressions for the crosstalk voltage, delay and peak crosstalk voltage are derived in the case only when victim lines are grounded and excitation is connected to aggressor line. Figure 1 shows lumped RLC model of ‘L’ shaped interconnection system considering Mutual Inductance coupling between the parallel lines. Step input voltage is used for the analysis of the interconnection system.

A step input voltage supply is given to the input of aggressor line which is equidistant to the victim lines. Coupling capacitance is generated because those two RLC networks are proximate to each other and mutual inductance is induced due to using inductor coil.in this paper we use 90 nm technology.

As per Moore’s law, in the process of designing the ICs, the number of transistors will continue to double in every 18 months [1]. That means the same silicon area would accommodate a greater number of transistors. Transistors size is gradually getting reduced for achieving this or we can say that transistor size is shifting from one technology node to smaller technology node by using scaling process. A specific technology gets used by the industries for the period of time till the time when the next feasible smaller technology node would be ready for implantation. For example, 180 nm technology was used mostly in 1999–2000-time period whereas 90 nm technology was used in 2004–2005. The technology’s numbers represent the minimum feature size of transistor or CMOS. Minimum channel length that can be used in fabrication of CMOS or transistor is known as Feature size of transistor. These numbers are decided by dividing the previous number (technology) by square root of two (\(\sqrt{2}\)).

In the circuit shown in Fig. 1, at node C, we develop the mathematical expression for the voltage for RLC victim line.

On employing KVL in 1st loop:

On taking Laplace,

Where,

Similarly, on applying KVL in 2nd mesh,

Similarly, on applying KVL in 3rd mesh,

Where

From Eqs. (3), (5) and (6), we get a matrix:

Let,

Then required matrix is,

After solving by Cramer’s rule [20],

Now, at node ‘C’:

So,

Where,

\(P = - sABCC_{1} C_{1}^{^{\prime}} - 2s^{2} mC_{1} C_{1}^{^{\prime}} + Bs^{5} m^{2} C_{1}^{2} C_{1}^{^{\prime}2} + AC_{1} + CC_{1}\) After substituting the values of A, B and C:

Where,

Where,

Now,

After neglecting all high-power terms:

Now after substituting the value of \({V}_{s1}=\frac{1}{s}\) (for step input voltage) & P in Eq. (11),

Now, let us assume:

If, \(R={\left[\sqrt{\frac{-Z}{X}-\frac{{Y}^{2}}{4{X}^{2}}}\right]}^{2}\)

After taking Inverse Laplace transform:

Peak time value \({t}_{{p}_{c}}\) is calculated by equating first derivative of \({V}_{c}\left(t\right)\) to zero,

After simplification we get

Let’s put the value t = \({t}_{{p}_{c}}\) in Eq. (14) so that,

Now calculate the value of \({V}_{B}\):

For unit step input, \({V}_{s1}=\frac{1}{s}:\)

Now let’s put the value of P from expression (12) and have,

Where,

Putting the result of P in the equation of VB1 from Eq. (13)

after simplification, we get,

In similar way, the expressions of VB2 and VB3 after substituting the expression of P from Eq. (13),

Where,

substituting the values of \({V}_{B1},{V}_{B2},{V}_{B3}\) in Eq. (17)

After using inverse Laplace Transform in the above expression

On differentiating with respect to t

Peak time value is calculated by equating first derivative to zero,

Let us assume for simplicity,

After simplification above equation becomes,

After simplification and approximation to lower degree terms of above Eq. (19), we get

where,

After substituting the values of \({t}_{p}\) in equation, so now

The expressions for peak delay time and peak voltages at node C and B are discussed by Eqs. (15), (16), (20) and (21) respectively. The essential proposed crosstalk voltage and peak crosstalk noise voltage respectively at node C are discussed by Eqs. (14) and (16).

3 Simulation Result and Discussion

Figure-1 shows simulation set-up of two L type High speed RLC mutually coupled interconnection system having 1000 μm of length. High performance CPU system designs typically consist of such type of bus structures. Symmetrical Step signal having finite and equal rise/fall time of 10 ps is used to excite the aggressor line. It is assumed that the interconnection system is identical and symmetrically distributed by considering that the system is connected with identical size of inverters for drivers and loads. Variations in the input slew times values up to 200 ps are used for the simulation of Mutually coupled interconnection system connected with identical driver size.

For the testing and verification purpose, we have compared our proposed model values with BKM [19] model values to show the novelty of our proposed work. This comparison was done on the same set of circuit parameters. Our work is much-improved version of BKM model [19] for the same L-interconnect model with the consideration of mutual inductance for high operating frequencies. Comparison of simulated results at node C for the expression given by Eq. (16) for proposed model and BKM model are demonstrated in Table 1 for various input slew times. Table 2 discusses the comparison of aggressor line voltage described by Eq. (21) with BKM model values and our proposed model for the various input slew values. Comparative results for the peak times tpc and tpb at node C and node B of the victim line and aggressor line described by Eqs. (15) and (20) respectively is discussed in Table 3 and Table 4. Comparative results for proposed model Aggressor voltage, BKM and SPICE for different values of Ts are shown in Figs. 2, 3 and 4 respectively. Similarly, comparative results for aggressor line voltage, victim line peak time and aggressor line peak time values from proposed model and the values from SPICE simulations are shown in Figs. 5, 6, 7, 8, 9, 10, 11, 12 and 13 respectively.

.

After analysing the simulated result related Figs. 2, 3, 4, 5, 6, 7, 8, 9 and 10 and Tables 1, 2, 3 and 4, we can easily find out the novelty and importance of our proposed model in comparison to BKM [19] model. By considering mutual inductance in between two coupled interconnection models, our proposed model becomes more realistic and generic as it follows SPICE results better than BKM model. Deviation in between BKM model values with SPICE values is very large therefore; BKM model becomes appropriate in current scenario.

4 Conclusion

Proposed research work discussed about the mathematical analysis of delay and crosstalk voltage in mutually coupled RLC VLSI interconnection structures. The derived models for crosstalk voltage and delay are found precise as simulation results are very close to SPICE. The L-type RLC mutually coupled interconnection system is proposed in this research work. The correctness and validity of the research work is demonstrated by the simulation results. Simulation results shows that the proposed models are having less than 10% error comparable to the results obtained from the SPICE.

References

Wu B (2017) High bandwidth IC interconnects with silicon interposers and bridges for 3D multi-chip integration and packaging. In IEEE Semiconductor Technology International Conference (CSTIC) China, 12–13 April 2017, pp 1–3

Zhang XJ, Jiang W, Gao L, li H (2016) Impact of cross talk on signal integrity of high-speed density ceramic package for IC. In: IEEE international conference on electronic packaging technology Wuhan, 16–19 August 2016

Wu SY, Liew BK, Young KL, Yu CH, Sun SC (1999) Analysis of interconnect delay for 0.18 μm technology and beyond. In: IEEE International Conference on Interconnect Technology, San Francisco, CA, USA May 1999, pp 68–70

Agrawal Y, Chandel R (2016) Crosstalk analysis of current-mode signalling-coupled RLC interconnects using FDTD technique. IETE Tech Rev 33(2):148–159

Gupta A, Maheshwari V, Sharma S, Kar R (2015) Crosstalk noise and delay analysis for high speed on-chip global RLC VLSI interconnects with mutual inductance using 90 nm process technology. In: International Conference on computing on computing, communication and automation (ICCCA-2015), 15–16 May 2015, pp 1215–1219

Fattah G, Masoumi N (2018) Comprehensive evaluation of crosstalk and delay profiles in VLSI interconnect structure with partially coupled lines. J Iran Assoc Electric Electron Eng 14(4):41–54

Rebelli S, Nestala BR (2018) An efficient MRTD model for analysis of crosstalk in CMOS- driven coupled cu interconnects. Radio Eng 27(2):532–540

Rebelli S, Nistala BR (2020) A multiresolution time domain (MRTD) method for crosstalk noise modeling of CMOS-gate-driven coupled MWCNT interconnects. IEEE Trans Electromagn Compat 62(2):521–531

Bhattacharya S, Rahaman DDH (2017) Analysis of temperature- dependent crosstalk for graphene nanoribbon and copper interconnects. IETE J Res 10(20):187–205

Maheshwari V, Gupta S, Khare K, Yadav V, Kar R, Mandal D, Bhattacharjee AK (2012) Efficient coupled noise estimation for RLC on-chip interconnect. In: IEEE Symposium on Humanities, Science and Engineering Research (SHUSER-2012), Kuala Lumpur, Malaysia, 24–27 June 2012, pp 1125–1129

Hunagund PV, Kalpana AB (2010) Crosstalk noise modeling for RC and RLC interconnects in deep submicron VLSI circuits. J Comput 2:60–65

Kar R, Maheshwari V, Mal AK, Bhattacharjee AK (2010) Delay analysis for on-chip VLSI interconnect using gamma distribution function. Int J Comput Appl 1(3):65–68. Article 11

Peng X, Pan Z (2017) The analytical model for crosstalk noise of current-mode signaling in coupled RLC interconnects of VLSI circuits. J Semiconductors 38(9):095003

Mudavath R, Naik BR (2018) Estimation of far end crosstalk and near end crosstalk noise with mutually coupled RLC interconnect models. In: IEEE International Conference on Communication and Signal Processing India, 3–5 April 2018, pp 0198–0201

Maheshwari V, Suvra R, Kar D, Mandal AKB (2012) Analytical crosstalk modelling of on-chip RLC global interconnects with skin effect for ramp input. Procedia Technol 6:814–821

Mudavath R, Naik BR, Gugulothu B (2019) Analysis of crosstalk noise for coupled microstrip interconnect models in high-speed PCB design. In: International Conference on Electronics, Information, and Communication (ICEIC) New Zealand, 22–29 January 2019

Chhotray SK, Mohapatra DD, Dash SS, Swain S (2013) An analytical delay expression for deep sub-micron RLC interconnect. Int J Eng Res Appl 3(5):1727–1730

Chowdhury MMH (2004) Noise Analysis and Design Methodologies in Deep Sub-Micron VLSI circuits. PhD Dissertation, North-Western university

Kumar B, Maheshwari V, Dhubkariya DC, Kar R (2013) Analytical modeling of crosstalk noise and delay for high speed on-chip global RLC VLSI interconnects. J Electron Dev 17:1452–1456

Strang G (1998) Linear Algebra and its Applications, 3rd ed. Harcourt Brace Jovanich, Inc.

Author information

Authors and Affiliations

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2021 The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Gupta, A., Maheshwari, V., Malipatil, S., Kar, R. (2021). Delay and Crosstalk Aware Analysis for High Speed On-Chip Global RLC VLSI Interconnects. In: Nath, V., Mandal, J.K. (eds) Proceeding of Fifth International Conference on Microelectronics, Computing and Communication Systems. Lecture Notes in Electrical Engineering, vol 748. Springer, Singapore. https://doi.org/10.1007/978-981-16-0275-7_66

Download citation

DOI: https://doi.org/10.1007/978-981-16-0275-7_66

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-16-0274-0

Online ISBN: 978-981-16-0275-7

eBook Packages: EngineeringEngineering (R0)