Abstract

The copper pumping problem exemplifies the complex reliability issues still to be resolved for TSV structures. From a materials science perspective the reliability issues presented by TSVs are linked to manufacturing processes and the resultant microstructure formed. Routine finite-element based reliability studies that treat the TSV filler as an isotropic and homogeneous material are not capable of providing a sufficiently thorough explanation of the observed copper extrusion/intrusion behavior. Rather, the material behavior and properties at multiple scales are required as the input data for effective reliability analysis of three- dimensional TSV stacked ICs. Such 3-D ICs also push the scale of materials to a limit where the anisotropy of material properties, recovery, recrystallization and time-dependent phase morphological evolution further complicate reliability issues. This chapter reviews both experimental and modeling approaches that address the microstructural and reliability issues of TSVs. Crystal plasticity based finite element analysis (FEA) and phase field crystal method with an inherently multiscale nature are identified as promising modeling techniques to enable atomistically-informed reliability analysis of TSVs.

Access provided by Autonomous University of Puebla. Download chapter PDF

Similar content being viewed by others

4.1 Introduction

Following Chap. 3 on materials, processing and assembly, this chapter discusses the microstructural and reliability issues of TSVs. This chapter begins with microstructural characterization and stress measurement; it then discusses detailed reliability issues associated with TSVs; finally it presents promising techniques towards atomistically-informed reliability modeling of TSVs.

4.2 Microstructural Characterization and Stress Measurement

4.2.1 Microstructural Characterization

The microstructure of TSV can be characterized at four levels, i.e., crystal structure, phase structure, grain structure and defect structure. Bunge introduced a function

and mathematical methods to quantitatively describe microstructure [1, 2]. For experimental characterization, standard metallographic techniques can also be applied to TSV structures. However, preparing TSV samples for microstructural characterization to investigate precise locations through the TSV sample structures using standard metallographic polishing is tedious and unpredictable due to the small size of TSVs and presence of soft materials (e.g., Cu, Ag paste, etc.) adjacent to hard and brittle Si. Focused ion beam (FIB) milling, which allows precise machining at small length scales, is widely used for preparing TSV samples for microstructural characterization. FIB can also be used to prepare ultra-thin samples, suitable for observation under transmission electron microscope (TEM). Machining samples using FIB is both a slow and an expensive process. Emerging Xe+ plasma FIB systems, with optimized control over milling parameters, promise faster removal rates [3]. Another method for characterization of the microstructure of filler material is by via revealing: in this process, Si is wet-etched using hydroxides, which do not affect metal fillers, thus revealing the pillar [4, 5]. However, this is also a slow process and it does not allow observation of the Si-filler interface. Therefore, sample preparation, especially over the entire height of the TSV, for microstructural characterization is often very slow. The important microstructural features of TSV assemblies that are often characterized and quantified are the size and shape of filler grains, micro-texture and grain orientation, the presence of twin boundaries in Cu fillers, shapes and sizes of voids or cavities in the filler, micro-cracks, interfacial structure, etc.

Grain size, which can be measured using scanning electron microscope (SEM) and TEM, is important for the estimation of the strength of the metal filler (generally, the smaller the grain size, the greater the strength of the material). The hardness and hence strength of the TSV fillers can be measured using nano-indentation. Interestingly, as shown in Fig. 4.1, nano-indentation studies have shown that TSV fillers with smaller grain size may not always show an enhanced strength. Furthermore, as also shown in Fig. 4.1, the strength versus grain size behavior often does not follow the Hall-Petch relationship; in other words, the increase in the strength is not strictly proportional to the inverse of the square root of the grain size [6, 7]. These deviations can be attributed to the fact that TSV fillers contain relatively few grains across the via-diameter, as shown in Fig. 4.2, and hence do not display generalized polycrystalline behavior. It has been shown that electrolytes with impurities can enhance the yield strength of the fillers [15]. Therefore, attention should be paid to the methods used to estimate the mechanical behavior of TSVs [8, 9]. In addition, the conventional parameter of an average grain size may not be sufficient to characterize the grain structure of TSV fillers. In the current materials genome initiative [10], new methods that consider more parameters including phase morphology and distribution have been proposed for quantification of microstructure [11, 12].

Variation of (a) average hardness and (b) yield strength of filler material with average grain size of Cu. The broken line shows the best curve fit using Hall-Petch type of relationship between hardness in a and yield strength in b and the inverse of the square root of grain size. The data for (a) and (b) are taken from Refs. [6, 7], respectively

(a) Electron back scatter diffraction (EBSD) patterns showing inverse pole figure (IPF) maps of cross-section of Cu fillers: (i) as-deposited and (ii) after annealing at 420 °C for 20 min followed by annealing at 300 °C for additional 15 min [6]. (b) FIB micrographs showing grain structure of Cu filler: (i) as-deposited and (ii) after annealing at 400 °C for 1 h [13]

Figure 4.2 shows that the grain size of the Cu via-filler increases significantly upon annealing at elevated temperatures [6]; for example, annealing at 450 °C for 30 min leads to an increase in the grain size from 0.84 to 1.26 µm [14]. However, as shown in Fig. 4.2b, the grain growth during annealing is often inhomogeneous [13]. Furthermore, impurities in the filler material slow down the grain growth during annealing [15]. Electroplating at lower current density may lead to fillers with large grain size; for instance, plating current densities of 1 and 9 A/cm2 resulted in Cu fillers with average grain sizes of 2.57 and 0.88 µm, respectively [7]. Annealing has also been noted to induce twinning in Cu fillers [6, 16].

The micro-texture of TSV fillers is often measured by electron back-scattered diffraction (EBSD) conducted in SEM (see Fig. 4.2a). However, if the filler grains are very small, as found in the seed layer, diffraction-scanning transmission electron microscope (D-STEM) can also be used to map the micro-texture [17]. It has been noted that although annealing increases the grain size, it does not have any other noticeable effect on the texture of the filler material [6]. The micro-texture of filler materials appears to depend on the orientation of the seed layer, electroplating conditions, e.g., current density, bath chemistry, bath temperature, etc., impurity concentration, etc. [17]. However, to date, the dependence of the crystallographic texture of the via-filler on various process and geometrical parameters has not been unambiguously determined.

The general microstructural characterization techniques, such as STEM, energy dispersive X-ray spectroscopy (EDXS), electron probe microanalysis (EPMA), etc., can be used to identify the chemical species in TSVs and map their concentration profile. Time-of-flight secondary ion mass spectrometry (TOF-SIMS) may also be used to study the chemical species in TSVs [15]. X-ray diffraction (XRD) can also be used to identify the phases present in the TSV structures [18].

4.2.2 Measurement of Stress State

Substantial stresses are produced in the TSV assemblies, as a result of processing and during thermal cycling. The sources and implications are discussed in Sect. 4.3. These stresses affect the overall reliability of microelectronic packages comprising these TSV structures, and therefore various approaches have been utilized to understand the nature of these stresses. Three main techniques that been used to measure the stress state in TSVs are briefly discussed below.

4.2.2.1 Wafer Curvature Method

If a layered assembly of two or more materials having different coefficient of thermal expansion (CTE) are joined together and then heated, the assembly bends with a curvature proportional to the in-plane stresses generated in the individual components [19]. Although TSV assemblies are more complex, they also bend due to generation/relief of residual stresses during thermal excursions [15, 20,21,22], and measurement of the curvature of the wafer can be used to determine stresses in the TSVs. However, the stress state in TSV structures is more complex than simple film-substrate systems, and as such, stress analysis based on the curvature method has usually been supplemented by FEA [21]. Although this method is meant to provide only an overall or average stress (as only one curvature is measured), FEA may be used regressively to predict the 3-D state of stress. Moreover, this method can be easily adapted for in situ measurement of stress (e.g., during thermal cycling).

4.2.2.2 Micro-Raman Spectroscopy

Since Si is Raman-active, the stress in the Si wafer can be measured using micro-Raman spectroscopy (µRS) [20, 23,24,25]. The most common case involving usage of µRS in backscatter mode resolves the longitudinal vibrational mode (i.e., mode 3), which can then be used to determine the sum of the two in-plane principle stresses [23, 25]. However, if a high numerical aperture (NA) (say, ≥ 0.4 [23]) is used, then it is possible to resolve all three modes of vibration and hence tensorial nature of the stresses in TSV structures [23]. As shown in Fig. 4.3a, compressive and tensile stresses in Si lead to forward and backward shifts in the Raman signal (e.g., a shift by a wavenumber of 1 cm−1 corresponds to a stress of ∼434 MPaFootnote 1), the shift being directly proportional to the stress in Si [24]. Since a laser beam with long wavelength can penetrate deeper in Si, it can provide information from a deeper depth than a beam with a longer wavelength, and thus, depth-sensitive information can be obtained. Nevertheless, the penetration depth of µRS in the backscatter configuration is still very small and hence this method can be used to obtain stress information from near surface regions only. As shown in Fig. 4.3b, the stress in Si around a TSV strongly depends on the distance from the via-end: at very near the surface (as measured using short wavelength laser), the stress becomes less tensile away from the via end, whereas at slightly below depth (as measured using long wavelength laser), the stress transitions from being compressive to tensile as one moves away from the via end. Since the stress-state in the Si wafer is generally tri-axial, it is challenging to measure all stress-components via Raman spectroscopy. Nevertheless, by combining with FEA, µRS has been utilized to yield good estimates of the three-dimensional stress state in the wafer [23,24,25]. It should be noted that metals are not Raman-active and therefore the stress state of Cu cannot be measured using this technique and has to be derived indirectly from measurements on Si.

4.2.2.3 X-Ray Diffraction (XRD) Based Techniques

To directly measure the localized strain, and hence the stress-field in Cu TSVs, X-ray diffraction, used in conjunction with a cross-section TEM or a synchrotron radiation source, may be used to determine stress-induced changes in unit cell parameter from the equilibrium [26,27,28]. This can also be used to measure stress in Si non-destructively with very high resolution. Although XRD typically yields only average stress values, by focusing high energy X-rays in a synchrotron to a small beam size and rastering it on the sample, full strain and stress tensors from submicrometer sample volumes in the TSV structures may be obtained [26, 29,30,31]. Figure 4.4 shows an example of spatially resolved stress variation in a TSV assembly, determined using high energy X-rays.

Stress distribution on a plane as determined using synchrotron x-ray micro-diffraction: (a) the deviatoric σxx and (b) von-Mises stress [26]. The dotted vertical lines represent the effective size of the Cu TSV whereas the grey shaded region represent “non-indexable” region where the diffracted intensities from Cu are comparable with that from Si

4.2.2.4 Stress Metrology Challenges

Although the synchrotron X-ray micro-diffraction is by far the most powerful technique for stress analysis, it is the most expensive and requires access to a synchrotron radiation source [28]. None of these aforementioned techniques can directly measure stress in Si or Cu. In Raman spectroscopy phonon frequency shifts are converted into stress values [28]; in diffraction-based techniques strain tensors are mathematically converted to stress tensor using linear elastic properties of bulk single crystalline samples [28]. Although µRS can provide stress profiles in the depth direction, the penetration depth is within a submicrometer range. Therefore, the complete picture of the stress distribution in TSVs is still unavailable. How- ever, this information is critical to elucidate the root cause for the metal pumping phenomenon as discussed in Sect. 4.3.1.3. The modeling techniques discussed in Sect. 4.4 may provide a solution towards this direction.

4.3 Reliability Issues Associated with TSVs

Reliability complications in TSVs typically arise either from stress-related or electrical sources, and are often convoluted with microstructural effects. In the following, we discuss the cause and effects of each of these reliability issues, along with potential approaches to circumvent or minimize these.

4.3.1 Stresses in TSVs

4.3.1.1 Origin and Effect of Stresses

Stresses in TSVs, and therefore in the neighboring Si, arise from two sources: (i) growth stresses, that arise as a result of via-filling by electroplating, and (ii) thermo- mechanical stresses that arise due to thermal expansion mismatch between Cu in the via and the surrounding Si.

Growth stresses arise when the electrodeposited Cu grows radially inwards on the Cu-seed layer from the via side-walls, and abut itself, often resulting in a seam along the TSV axis. Such a seam may leave a thin void-line along the TSV axis (Fig. 4.5), which can grow during post-deposition annealing, and result in mechanical and electrical performance loss. Electroplated copper undergoes significant grain growth by self-annealing at room temperature, which results in volume shrinkage of the Cu TSVs by elimination of grain boundaries [32]. This may allow any existing void to grow during both self-annealing, as well as during the pre-CMP (chemical- mechanical polishing) annealing step. During annealing, hydrostatic stress gradients generated around pre-existing defects in the Cu may be relieved by diffusion of lattice vacancies towards the existing void near the axis, causing the void to grow [33].

SEM images of TSVs showing centerline void after annealing at 150 °C (a) and 300 °C (b) [33]

Thermo-mechanical stresses arise because of differential thermal expansion or contraction of Cu and Si during heating or cooling of the device as a result of their large difference in the CTE (αSi = 2.8 × 10−6/K, αCu = 17 × 10−6/K). Thermal cycling resulting from fluctuating Joule heating occurs continually during the service life of electronic devices, and 3D devices are no exception. Typically, electroplated Cu deposited on Si is under residual tension to begin with (at ambient temperature). During heating, the tension is first elastically relieved, following which a compressive stress builds up. As temperature increases, the yield strength and creep resistance of Cu decrease, resulting in stress relief by plastic yielding and creep, such that at the highest temperature, there is little stress remaining (Fig. 4.6). During subsequent cooling, a tensile stress builds up, result- ing in stresses in the neighborhood of 200–500 MPa (biaxial for thin films and hydrostatic for TSVs). Further cycling repeats the same behavior, although because of substantial plasticity during the first cycle, the yielding and stress-relaxation start at a higher temperature, and are therefore lower. This is shown for a Cu film on Si, measured by wafer curvature testing, in Fig. 4.6 [34]. The details of this behavior depend on the temperature range and rate of thermal cycling, but the overall behavior is qualitatively replicated in TSVs. In contrast to thin films, however, the TSV stress-state is triaxial, and the TSV is typically in triaxial (i.e., hydrostatic) tension at ambient temperature.

Evolution of equibiaxial stress in a blanket Cu film deposited on Si during thermal cycling [34]

As noted earlier, the stress state in Cu-TSVs may be studied either by measuring the stress in Si via Raman spectroscopy, or that in Si or Cu by X-ray microdiffraction. Depth-sensitive Raman measurements, using various excitation wavelengths of an Ar+ laser, show that Si surrounded by TSVs has a compression hydrostatic stress at ambient temperature, with the stress varying significantly along the length of the TSV [24, 25]. The hydrostatic stress in Si becomes less negative nearer the ends of the TSV. Assuming that the radial and circumferential stresses (σrr, σθθ) in the Si surrounding the TSVs are either weakly or not dependent on the axial position relative to the TSVs, one may infer that at ambient temperature, the axial stress σzz in Si is negative (i.e., σzz is positive in Cu) near the middle of the TSV, and becomes ∼0 at the surface. It was also noted that the stress-variation along the depth is larger for smaller TSV diameters (i.e., larger TSV aspect ratios). Furthermore, the stress in Si surrounded by an array of TSVs is typically larger than that outside of TSV-arrays, and these stresses change from tensile immediately after Cu electrodeposition (where the stress is due to growth and self-annealing), to increasingly compressive when annealed at increasing temperatures [35]. Raman peak-shift measurements near the surface of the chip next to TSV-ends show that the biaxial hydrostatic stress state (i.e., [σr + σθ]/3, since σz ∼ 0) is negative at the TSV-chip interface, and rises sharply and becomes positive mid-way between TSVs (Fig. 4.7). After annealing, the hydrostatic stress in Si becomes even more compressive at the interface due to Cu volume expansion, and more tensile away from the interface [20]. Conversely, in addition to increasing the grain size, annealing lowers the compressive stresses in the Cu.

Plot of the stress state in Si near the ends of TSVs. Three TSVs are shown, each as a vertical band with intervening Si [20]

Thermal cycling also leads to accumulation of hydrostatic stress in Cu TSV or filler [27]. In addition, TSVs with high impurity levels appear to lead to high residual stresses [15]. It has been reported that large tensile radial stresses exist at the Si–Cu interface [25]; this may make these sites prone to failure in TSV assemblies. The radial stress at the Cu-filler/Si interface generally increases with the length of the TSV for a given diameter [25]. The TSV diameter also seems to affect the stress state in the TSV assembly, although the dependence of the hydrostatic stress on TSV diameter is not monotonic [36].

The stresses induced near the surface of Si next to the Cu-filled TSVs have an adverse impact on the electrical performance of devices in the immediate neighbor-hood of the TSVs due to induced piezoresistivity, which results in degradation of carrier mobility [37, 38]. This necessitates a keep-out zone (KOZ) in the Si, typically a few micrometers in width, in the immediate vicinity of each TSV, where active devices cannot be placed. The KOZ, which scales with the square of the TSV diameter, is also greater for high aspect-ratio TSVs, and places a significant overhead on the area available in the chip for active devices, particularly with the increasing density of TSVs in chips. Based on FEA of the stress-state in Si next to TSVs, it has been inferred that Cu microstructures with smaller yield strengths reduce the KOZ size, which increases with increasing yield strength until the via yields plastically, and then remains stable [39].

FEA of TSVs in free-standing chips shows that after both heating and cooling, maximum von Mises stress, and hence plastic deformation of the copper occurs near the interface close to TSV-ends, which is a root cause of copper-pumping [40]. It is further observed that the maximum principal stress (tensile) is in the radial direction at the interface near the middle of the TSV, and in the circumferential dielectric layer surrounding the TSV [41]. Evidence of dielectric cracking at the circumferential Cu–SiO2–Si interface, as well as roughening (due to voiding) of the metal-line at the top of the TSV has been noted after thermal cycling, as shown in Fig. 4.8 [42]. However, FE analysis of a stacked-die package shows that each die undergoes convex curvature when the package is cooled from the stress-free temperature (150 °C), which fundamentally alters the stresses and displacements relative to the free standing die [41]. The convex curvature alters the radial interfacial stress to compressive, reducing the proclivity towards interfacial fracture as well as dielectric cracking, and shifting the critical failure location to the copper-pillar near the solder-microbump interface in 3D packages [41]. In fact, the failure probability near the silicon–Cu pillar-microbump junction (as indicated by the maximum equivalent strain), as well as the required KOZ diameter, increase with increasing diameters of both the TSV and the copper-pillar in a 3D package [43].

TSV (a) prior to cycling, and after (b) 500 and (c) 2000 cycles between 30 and 150 °C, showing development of dielectric cracks and top-line roughening [42]

In addition to producing defects (e.g. voids) in TSVs, including complications in electrical performance and potentially causing interfacial and or dielectric fracture, induced stresses also give rise to a plasticity-related phenomenon commonly referred to as copper-pumping, which can have serious reliability implications. Because of the pervasiveness of this phenomenon, it is discussed separately in Sect. 4.3.1.3.

4.3.1.2 Microstructure and Stresses

Direct measurement of stresses in Cu-TSVs with X-ray micro-diffraction reveal a significant tensile hydrostatic stress (∼ 234 MPa) at room temperature, which goes to compression (−196 MPa) during annealing at 200 °C, and becomes a smaller tensile stress when the sample is cooled to the ambient (167 MPa). The large initial tensile stress is caused by grain boundary elimination during self-annealing and device fabrication, and as noted previously, is undesirable from the reliability perspective, since this causes large stresses in Si. A subsequent annealing treatment lowers the tensile hydrostatic stress in Cu, even though the zone of initially larger grains expands during annealing, as shown in Fig. 4.9 [29], possibly because of relaxation associated with plasticity and creep at the high temperature.

Cross sections of Cu-filled TSVs in: (a) the as- received state, showing a zone of large grains in the center surrounded by smaller grains; and (b) after annealing, showing an expanded central zone with large grains [29]

EBSD studies have shown that during annealing, large grains remain stable when there is a preponderance of Σ3 twin boundaries, but grains without twins and smaller grains grow rapidly [44]. It has also been noted that the Cu-TSV has random texture both before and after annealing. However, microvoids or small cracks have been noted to form during annealing, thereby reducing stress, as shown in Fig. 4.10. This is possibly because of vacancy diffusion to pre-existing defects under hydrostatic stress gradients within the TSV during annealing, as noted in the discussion associated with Fig. 4.5.

(a) Voids and cracks form at various locations in a TSV after annealing (red circles). (b) Voids near the top of the TSV, and (c) grain boundary cracks near one of the side-walls [44]

FEA based modeling work has also reported the linkage between the microstructure of copper grains and the stress in Cu-TSVs. The results from a linear elastic mechanical model clearly demonstrate that the stress distribution is rather heterogeneous inside the TSV filler, as show in Fig. 4.11, considering the anisotropy of the elastic compliance tensor of copper. Depending on the texture, morphology and distribution of the copper grains, stress concentrations may occur at the grain boundaries [45]. Elastoplastic models have also been conducted directly on copper grain structures with the aim of explaining the formation of copper-pumping [46, 47]. However, the drawbacks of this kind of model is clear. First, although the mechanical analysis is conducted directly on copper microstructure, the microstructure is assumed to remain unchanged during the mechanical loading process. Second, the plastic deformation mechanisms at the atomic scale, e.g. the motion of dislocations, have not been considered. However, the dislocation involved processes such as recovery, recrystallization and grain growth have been reported to occur in electrodeposited copper and can significantly influence its mechanical properties [48]. Recrystallization has also been suspected to account for the copper-pumping phenomenon [15, 36, 49]. Considering the limitation of the current modeling techniques, more robust simulation methodologies that take into account the polycrystalline nature of Cu TSVs and their complex deformation and stress relaxation mechanisms are needed [36]. Section 4.4 will introduce atomistically-informed modeling techniques to address this limitation.

Distribution of the von Mises stress in a Cu-TSV structure from a linear elastic mechanical model with Cu grain microstructure [45]

4.3.1.3 Metal Pumping: Extrusion or Intrusion of TSVs

During service and consequent thermal cycling, the CTE mismatch between Cu and Si results in residual stresses in each material (σCu, σSi), as well as significant interfacial shear stresses (Ti) near the extremities of the via. The induced stresses, if high enough, may cause plastic deformation of the filler [39, 47, 50, 51] with the differential straining between Cu and Si sometimes accommodated by interfacial sliding [52,53,54]. This results in extrusion (and sometimes, intrusion) of Cu relative to the Si. Generally, the extrusion of the Cu occurs due to plastic deformation of the metal near the via-ends (typically, towards the top or mouth of the via), and can be enhanced by creep and grain boundary sliding. Two examples of this phenomenon are illustrated in Fig. 4.12.

Examples of Cu pumping. (a) Uniform pumping, showing a cross-sectional image dis- playing curvature of the top of a TSV, resulting in deformation of the RDL structure above [50]; (b) non-uniform pumping showing a few Cu grains protruding out of the Si surface [54]. The sample in (a) was annealed at 400 °C for 60 min, and the sample in (b) was annealed at 425 °C for 90 min

When heated up relatively rapidly and kept at a constant elevated temperature for a period, the protrusion observed is generally associated with plastic deformation of the copper, with no relative displacement observed at the interface between Cu and Si, as observed in Fig. 4.12. Generally, the extrusion increases with increasing temperature, and occurs during any pre or post-CMP annealing, as well as heating associated with dielectric-deposition for fabricating the back end of line (BEOL) or redistribution layer (RDL). FEA shows that following heating to a high annealing/fabrication temperature (425 °C) and cooling down, the Von Mises stress exceeds the yield strength over the entire upper part of the TSV, resulting in yielding of the top part of the via (Fig. 4.13a). As a result, inelastic (plastic and creep) strains accrue in the top part of the via, with strain concentrations adjacent to the interface near the TSV-end (Fig. 4.13b, c). This accrual of plastic and creep strain at the top of the TSV leads to copper pumping, or protrusion of the Cu from the top. This is particularly acute for blind vias, where any expansion of the Cu must necessarily occur at the open end of the via.

Von Mises stress in MPa (a), and equivalent plastic (b) and creep strains (c) in a Cu-TSV following fabrication at 425 °C and cooling to −25 °C (prior to thermal cycling). The figures show one quadrant of the TSV, with the interface at the right, the axis of the TSV at the left, and TSV mid-plane at the bottom. Although the plastic strain plot highlights only the strain concentration near the interface, most of upper part of the TSV, where Von Mises stress > ∼250 MPa, has yielded

EBSD studies show that Cu grains in a TSV typically have random grain boundary misorientations, and the via has little crystallographic texture, and no correlation between orientation and extruded grains has been noted [44]. This is evident from Fig. 4.14, which clearly shows a random texture in the TSV. It has been suggested that the protrusion observed is uniform when the grain size near the TSV ends is large, but non-uniform when there are smaller grains near the TSV ends [47]. In general, it is noted that the extent of protrusion is larger when there are high angle grain boundaries at the TSV ends that promote creep processes, but not when there are coherent twin boundaries [55].

EBSD orientation map of a TSV, showing a random grain texture [44]. This is typical of most TSV structures reported in the literature

It is useful to note that for adherent Cu–Si interfaces, when TSVs undergo uniform protrusion, the top of the Cu typically attains a convex curvature, as shown in Fig. 4.12a, with minimal or no relative displacement between the Cu and Si (or the barrier layer) at the interface. This is particularly true when the die is either cycled rapidly, or held at a constant temperature. On the other hand, when the die is cycled slowly, shear stresses are repeatedly generated and relieved at the interface near the ends of the TSV, allowing sufficient time to drive diffusionally accommodated interfacial sliding, which results in a significant, step-like interfacial displacement [52,53,54], as illustrated in Fig. 4.15.

Evidence of relative displacement between Cu and Si at the interface. (a) SEM image of Cu protrusion in an 80 µm diameter via, and (b) scanning white light interferometry image of Cu protrusion in a 10 µm diameter via. In both, the majority of protrusion occurs at the interface [54]

Diffusionally accommodated interfacial sliding at hetero-interfaces (i.e., interfaces between dissimilar materials) is akin to grain boundary sliding, and may be driven by interfacial shear stresses (Ti) that occur at the extremities of a TSV. In addition, it may be enhanced or mitigated by an electric current flowing through the TSV due to associated electromigration along the interface. The resultant displacement rate is given by [57,58,59]:

where Ω is the atomic volume, h is the roughness of the topographically periodic interface, k and T are the Boltzaman constant and temperature, respectively, Di is the interfacial diffusion coefficient, \(\delta_{i}\) is the thickness of the interfacial region, and Z* and e are the effective charge number of the diffusing ion and the charge of an electron, respectively. Thus, \(\dot{U}\) depends linearly on both Ti and the electric field E (which equals j, where ρ = resistivity of the filler and j is the current density), the relative signs of which determining whether they augment or mitigate each others contributions. In Eq. 4.2, the first term gives the effect of shear stress, while the second term gives the impact of superimposed electromigration (EM). Since Z* is negative, the second term (due to EM) acts against the first term (due to stress-driven creep) when both driving forces (Ti and E) are positive, and thus reduce the interfacial sliding rate. Conversely, if Ti and E have opposite signs, the two terms in Eq. 4.2 augment each other and increase the interfacial sliding kinetics. Figure 4.15 shows the effect of interfacial sliding due to Ti only (i.e., when E = 0), and Fig. 4.16 schematically shows the origin of Ti in through and blind vias after a thermal excursion. The impact of superimposed current on interfacial sliding is discussed separately, in conjunction with electromigration in Sect. 4.3.2.

Schematics showing shear stress distribution at the TSV-Si interface in a through-via, and b blind-via. The interfacial shear stress (dashed line) is symmetric about the length of the TSV for the through-via (a), and is non-zero only near the TSV-ends. Ti is zero at the blind-end of the via in (b), and rises monotonically towards the open end

In through-vias, the interfacial shear stress generated after cooling from the fabrication temperature is symmetric about the length of the via and is concentrated at both ends. As a result, the interfacial sliding, and hence copper-extrusion, would also be symmetric at the two ends for straight (i.e. untapered) vias. For blind-vias, the interfacial shear stress rises from the blind end towards the open end, and therefore, the resultant protrusion at the open end is greater. It should be noted that interfacial sliding, which occurs due to interfacial diffusion under the applied shear stress, is a mechanism that accommodates differential deformation of the Cu and Si at the interface and therefore a thermal excursion as well as a high enough temperature and sufficient time to make diffusional processes active are needed. This is why, under rapid cycling conditions, Cu pumping typically occurs uniformly due to inelastic deformation of Cu without significant contribution from interfacial sliding, whereas when cycled slowly over a larger temperature range, steps emerge due to sliding at the interface.

Since CTE of Cu is much larger than that of Si, when cooled from an elevated temperature, significant relative shrinkage of Cu can occur, which can also be accommodated at the interface by sliding. In this case, instead of protrusion, the ends of Cu vias may intrude into the Si with a sharp step at the interface, as illustrated in the SEM image in Fig. 4.17. Again, the shrinkage is due to deformation of the Cu, but the interfacial step is due to diffusionally accommodated interfacial sliding. It should be noted, however, that the rate of protrusion or intrusion of the via-ends during thermal cycling decreases with increasing number of cycles, as the stresses generated in the metal filler reach saturation due to progressive strain hardening. Therefore, after several cycles, protrusion/intrusion due to Cu pumping levels off [52,53,54].

Since the ends of a TSV are typically connected to a RDL or BEOL layer, protrusion or intrusion of the Cu via poses a significant risk to the integrity of these layers. Distortion of the RDL/BEOL structures, as shown in Fig. 4.12a, or delamination of a capping layer at the end of the TSV, as shown in Fig. 4.18 due to stresses associated by even a small protrusion of the via ends, can pose serious reliability challenges. Because of the potentially serious reliability complications, the role of Cu pumping has been widely studied, and the effects of various process parameters such as TSV spacing, diameter, Cu overburden after electroplating, and annealing conditions have been noted [50]. Generally, a majority of Cu-pumping is noted to be uniform or global (∼10–30 nm protrusion), with relatively few TSVs showing extrusion of individual grains after a high temperature anneal. Spacing appears to have little if any effect, but the pumping is greater on average for larger via diameters [50, 56]. However, although the average protrusion of an array of TSVs is larger for larger TSVs, the maximum copper pumping appears to be independent of the TSV diameter, which suggests that TSV diameter has little effect on BEOL reliability [56]. Copper overburden typically has no effect, but a higher pre-CMP annealing temperature (∼430 °C) reduces pumping. Finally, an additional annealing step, following pre-CMP anneal, reduces pumping significantly [50].

Recent work has demonstrated that the surface relief that is often seen on the end-surface of the TSVs after thermal cycling (e.g., Figure 4.12b), is associated with grain boundary sliding along incoherent Σ3 boundaries of the copper [60]. As noted earlier, EBSD typically reveals no strong preferred orientation (texture) in the Cu-TSV, along with the presence of numerous high angle grain boundaries. In particular, the presence of Σ3 boundaries (both coherent and incoherent) are particularly prolific in the electroplated Cu TSVs. However, the incoherent Σ3 boundaries with misorientations of ~59o (e.g., the boundaries between B and C, C and D, and D and E in Fig. 4.19) are the ones susceptible to sliding because of their high interfacial energy [60]. The coherent Σ3 boundaries, which have much lower energy, do not slide. This implies that if the electroplating process for TSVs can be controlled to yield only coherent Σ3 boundaries near the top surface, copper-pumping due to boundary sliding can be largely eliminated.

Grain orientation map of the cross-section in the vicinity of the top surface of a TSV, and the corresponding SEM image (inset), showing a distinct surface step. The EBSD image of the region of the step is also shown, with the red lines marking the incoherent Σ3 boundaries, and the green line representing a coherent Σ3 boundaries (twin plane)

4.3.1.4 Heating Rate Dependence of Copper Pumping

The extent and mechanisms of copper-pumping during thermal cycling depend on the heating/cooling rate, as well as the range of temperatures over which the package is thermally cycled. The influence of heating rate during in situ heating has been reported [60] on dies with 200 µm pitch TSV arrays, where the samples were rapidly heated at a rate of 0.1 °C/sec to 300 °C, and then heated further to 425 °C at various heating rates.

No change in the TSV surface occurs up to 300 °C, but during holding at 425 °C for 90 min, the existing surface features start protruding. As shown in Figs. 4.20 and 4.21, little change occurs during holding at 425 °C following heating at 0.02 °C/sec; but at a higher heating rate (0.05 °C/sec), grains protrude along both the edges and at the center of the TSV due to grain boundary sliding. These features continue to become exaggerated as time progresses. It is to be noted that multiple mechanisms (including grain boundary sliding, interfacial sliding, and plasticity/creep) operate at all heating rates, although the dominant mechanism(s) are different at different rates and over different temperatures ranges. The heating rate dependence is attributable to the fact that grain boundary sliding, interfacial sliding and creep are all rate dependent (i.e., diffusion dependent) processes. Because of this diffusion-dependence, as well as the dependence on the stress state of the TSV and the interface (i.e., the driving forces for these processes) at any instant, the relative kinetics of these mechanisms depend on both the temperature, as well as the heating rate.

Interposer surface single Cu-TSV SEM in situ observation during holding at 425 °C. TSV sample thermal cycling heating rate is 0.02 °C/sec [60]

Interposer surface single Cu-TSV SEM in situ observation during holding at 425 °C. TSV sample thermal cycling heating rate is 0.05 °C/sec [60]

Figure 4.22a, b show the top of two representative TSVs following five thermal cycles from room temperature to 300 °C and 425 °C, respectively, at a heating rate of 0.01 °C/sec [60]. It is clear that even at the same heating rate, the temperature range of thermal cycling has significant impact on the predominant mechanism of copper-pumping (grain boundary sliding for 300 °C, and interfacial sliding for 425 °C). At this slow heating rate, the creep mechanisms (i.e., grain boundary sliding and interfacial sliding) dominate, with the former dominant at lower temperatures, and the latter at the higher temperatures.

Based on this, Fig. 4.23 schematically shows a summary of the regions of dominance of the various mechanisms, in the heating rate vs. thermal-cycling temperature range plot. As noted in the figure, rate-independent plastic deformation of the TSV dominates when the heating rate is high and the temperature range, and in particular, the maximum temperature is low. At intermediate heating rate and intermediate temperature range, where there is sufficient thermal activation and time for diffusion, and the stresses in the TSV are high enough, grain boundary sliding is the dominant mechanism, leading to significant surface relief of the TSV-top surface. At high maximum temperature and slow heating rate, the stresses in the TSV are substantially lower (because of stress relief by dislocation or diffusional creep), and interfacial sliding dominates. This interplay between the stress state, heating rate and maximum temperature of the thermal excursion typically results in a superposition of all three of the effects shown in Fig. 4.23, although the effect of one or two of these mechanisms is predominant.

4.3.2 Electromigration Related Effects

Although electromigration (EM) is a significant reliability issue in metallic interconnects in electronics, particularly in BEOL structures, TSVs are generally less susceptible to EM induced failures. This is primarily due to their relatively large cross-sections, which reduces the current density. However, the combination of electric current and complicated stress states above and below the TSV, where it joins the BEOL or RDL structures, can cause substantial diffusional effects, and give rise to EM-related void growth. FEA of the effects of stress-gradient, potential gradient and temperature gradient on the atomic flux divergence (AFD), which correlates with diffusional flow and hence electromigration, has noted AFDs are typically high where the top and bottom metallizations meet the TSV [61]. A large proportion of the AFD is due to the stress gradient generated due to Joule heating, with relatively little due to the potential gradient. Still EM damage and void growth can occur. Generally, strategies to reduce stress gradients will reduce void growth.

EM experiments on devices with thin as well as thick metal layers at the top and bottom of TSVs generally show no void formation due to EM within the TSVs, irrespective of the current flow direction [62, 63]. However, voids form downstream of the direction of electron flow, at the intersection of TSV-end and the metal layer in the RDL. It has been hypothesized that these voids nucleate because migration of Cu atoms from the TSV to the void is prevented by the TiN barrier layer, but migration out of the void region can occur into the Cu lines at the end of the TSV. Thus, the layer of TiN, by being effective as a diffusion barrier, actually becomes the root cause behind EM void nucleation. In thin Cu lines, voids occupy the entire thickness of the line (between the TiN barrier and SiN capping layer). Current crowding at the location where the electron current exits the TSV is greater for the thicker lines, and therefore, thicker lines do not mitigate voiding. In thick lines, the voids are at the interface between TiN and the Cu-line. Experimental electromigration studies [64] have also shown voiding in backside Cu lines below the TSV downstream of the electron flow direction, but at the SiN-Cu interface, as opposed to at the TiN-Cu interface seen in Fig. 4.24. However, small voids present prior to EM experiments inside the TSV remained unaltered. Thus, even though the TSVs themselves are not susceptible to EM damage, the BEOL and RDL structures in the device can be significantly affected by EM.

(a) Chip showing a TSV with metal lines at top and bottom. Voids form due to EM at 300 °C at exits of electron flow at top and bottom for thin metal-lines (b) and (c) and thick metal lines (d) and (e) [62]

A different type of complication is posed by interfacial sliding under electro-migration conditions, as indicated in Sect. 4.3.1.3. As evident from Eq. 4.2, an applied electric current may enhance, or mitigate the kinetics of interfacial sliding due to the interfacial shear stress, depending on the direction of the applied field. Even when there is little or no shear stress at the interface, EM can drive interfacial sliding along the TSV-Si (actually, TSV-barrier layer) interface. Evidence of this is shown in Figs. 4.25 and 4.26, where the end of a TSV is seen to protrude in the direction of electron flow, and intrude opposite to electron flow for samples under EM with thermal cycling conditions, and at a constant temperature under a constant current. Under applied current, diffusional flow of Cu occurs along the interface in the direction of electron flow, and this can result in a time-dependent shift of the position of the Cu-filler relative to Si [52,53,54]. Since EM induced interfacial sliding is non-symmetric (i.e., it causes protrusion of the via downstream of the direction of electron flow and intrusion at the opposite end), and unlike under thermal cycling conditions, it accrues continuously [52,53,54], it may pose a potentially serious reliability challenge, particularly as the current density through the vias increases with decreasing TSV diameter. It is noted that while this via-migration under EM conditions is noted in experiments conducted on samples with through-vias with no RDL layer, the presence of an RDL or BEOL dielectric can constrain such migration and therefore mitigate it. However, because of the low elastic modulus of the RDL/BEOL dielectric, the effect of any imposed constraint may be limited, and therefore, the effect of this phenomenon on the stability of the RDL or BEOL layer needs further study.

(a) Schematic of experimental arrangement for electromigration cum thermal cycling (25–425 °C) experiments. (b)TSV edge showing protrusion due to 3 thermal cycles + EM due to a current density of 5.2 × 104 A/cm2, with upward electron flow through Cu. (c) The same TSV following a reverse current density of −5.2 × 104 A/cm2, showing that the Cu now intrudes into Si [52, 53]

Scanning white light interferometry (SWLI) images of the end of a TSV before and after EM experiments, showing protrusion in the direction of electron flow. A current was passed through Cu thin films deposited on the top and bottom of the chip through several TSVs simultaneously, for 62 h at 170 °C. The current density through each TSV was 5 × 105 A/cm2 [54]

Recent studies of several TSVs in a Si interposer with metal layers on top of a TSV have shown two dominant damage mechanisms due to electromigration (EM) [65]. Generally, protrusion/intrusion of the TSV was suppressed due to the presence of the back end interconnect structure (BEIS) at the top, and the redistribution layer (RDL), copper bond-pad and the solder joint at the bottom. However, when subjected to extreme EM conditions (TSV current density of 1.5 × 105 A/cm2 at 200 °C for 20 days), voids were observed in the metal-1 (M1) layer, where the electron current crowds following leaving the much larger cross-section TSV, and then leaves after fanning out again. Such a void is indicated with an arrow in Fig. 4.27a. These types of EM voids because of current crowding are consistent with routinely noted voids that form in high density interconnect structures at high current densities. A second type of damage that was noted under the extreme EM exposure was the concentration of Sn within the TSV, as shown in the Sn Ka x-ray map (from energy dispersive spectroscopy) in Fig. 4.27b. It is apparent that Sn has electromigrated in the direction of electron flow from the Sn-based solder ball, through the metallization below the TSV, along the TSV-Si interface, and into the TSV. Such alloying of Cu with elements from the solder under very high current densities can cause significant deterioration of the electrical properties of the device, as well as mechanical instability due to volume change due to alloying. As noted above, the experimental conditions in these experiments were much more severe than those TSV-containing packages are subjected to, but suggest the types of damage to which 3D packages may be subjected with rising current densities and temperatures (ambient or due to Joule heating).

(a) Focused ion beam (FIB) image of the cross-section of the region near the top of a TSV subjected to a current density of 1.5 × 105 A/cm2 at 200 °C for 20 days. The electrons flow upwards through the TSV into the metal-1 (M1) layer, and turn 90o to leave the plane of the micrograph. (b) Sn Ka x-ray map of the same TSV, showing Sn concentrations at the dark features of the ion image

4.4 Towards Atomistically-Informed Reliability Modeling of TSVs

As discussed in Sects. 4.2.2.4 and 4.3.1.2, more robust modeling techniques are needed to complement the FEA and advanced experimental characterization in order to provide a complete picture of the microstructure and stress inside the TSVs. This section introduces two methods, i.e., the crystal plasticity FEA (CPFEA) and the phase field crystal (PFC) method, and discusses their capabilities for atomistically-informed reliability modeling of TSVs.

4.4.1 The CPFE Method

The challenge of managing mechanical stress is not new, and a number of simulators do exist and have a long track record of use in the electronics industry. Most of the proven simulators are based on FEA, or derivatives of that class of modeling technique. The established FEA stress simulators have typically been used for addressing the traditional chip-package interactions, and have therefore mostly modeled physical deformations, such as cracking, delaminating, or fracturing [66]. In this class of analyses Si dies and TSV fillers are typically modeled as monolithic bricks and isotropic material models based on empirical equations are used, even though it has been known since 1934 that crystalline materials deform plastically by the slip of dislocations on discrete slip systems [67–69]. However, a physically based CPFE method is relevant in order to address the polycrystalline nature of Cu TSVs and their complex deformation and stress relaxation mechanisms.

Early CPFE models used phenomenological constitutive equations and considered dislocation slip as the only deformation mechanism [67]. In a phenomenological constitutive model, a critical resolved shear stress, \(T_{c}^{\alpha }\), is used as a state variable for each slip system α. The shear rate, \(\dot{\gamma }_{\alpha }\), is formulated as a function of the resolved shear stress and the critical resolved shear stress:

The evolution of the material state is then formulated as a function of the total shear, γ, and the shear rate, \(\dot{\gamma }^{\alpha }\):

The first CPFE simulations were performed in 1982 using a simplified setup of two symmetric slip systems to study the tensile behavior of a single crystal [70]. The technique was later extended to a polycrystalline scenario using a 2D setup with two or three slip systems [71, 72]. Simulations on a face-centered cubic (FCC) crystal with 12 slip systems was reported in 1991 [73]. Applying the aforementioned phenomenological constitutive laws to small-scale deformation, interface mechanics, and twinning and/or deformation-induced phase transformations are often found inadequate [65]. To address size effects, strain gradient theories [74] can be introduced into the CPFE framework. As strain gradients can be associated with geometrically necessary dislocations (GNDs), new internal-variable constitutive formulations were developed to incorporate dislocation densities as physically-based state variables replacing the strain variables. This latter class of constitutive models also allows the flexibility to incorporate additional metallurgical mechanisms such as grain boundary mechanics or damage initiation into the model [67]. To deal with additional deformation mechanisms such as occurring in TWIP (twinning-induced plasticity) or TRIP (transformation-induced plasticity) steels, the CPFE framework was further extended [75].

The result from a unidirectional compression on a copper single crystal using the CPFE method is shown in Fig. 4.28 [76]. The simulation was implemented in the Du¨sseldorf Advanced Material Simulation Kit (DAMASK) framework [77]. Although the mechanical boundary conditions and the material are both different from the real Cu-TSV structures, the result highlights the usefulness of the CPFE method in capturing atomistically-informed deformation and deformation induced crystallographic orientation evolution. The body centered cubic (BCC) tungsten single crystal subjected to uniaxial loading has also been recently studied using the DAMASK framework [78].

Evolution of crystallographic orientation and geometry of a Cu single crystal pillar with a diameter-to-length ratio of 0.29 under compression with a strain (an engineering thickness reduction) of (a) 0.05, (b) 0.15 and (c) 0.25. Color coding represents accumulated plastic shear ranging from blue (low) to yellow (large). Starting single crystal orientation: [1 1 12] compression axis (unstable) [76]

4.4.2 The PFC Method

The phase field (PF) methodology is an atomically diffuse interface method for modeling of complex microstructures in solidification, precipitation, and strain- induced phase transformations [79, 80]. The PF may be seen as describing the degree of crystallinity or atomic order/disorder in a phase [80]. More recently, a new class of PF models has been developed, called the PFC models, which describes the thermodynamics and dynamics of phase transformations through an atomically varying order parameter field that is loosely connected to the atomic density field [8, 81, 82]. PFC models naturally capture most of the salient physics of nucleation, polycrystalline solidification, grain boundaries [8, 83], and solidification in multicomponent and multiphase systems [84, 85]. In addition, PFC models also capture, in the context of a single order parameter, elasticity and plasticity phenomena relevant to solid-state processes such as dislocation source creation, dislocation stability [86, 87], and creep [88]. The original PFC model was predominately used for the study of 2D triangular and 3D BCC crystal symmetries [8, 81]. Later models introduced multipeaked two-point correlation kernels in the nonlocal part of the free energy that allowed for a simple yet robust approach to simulate most of the common metallic crystal structures (2D square, BCC, FCC, HCP) in phase transformations [87, 88]. These so-called structural PFC (XPFC) models were later generalized to binary and multicomponent and multiphase alloys [85, 89].

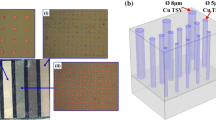

Figure 4.29 illustrates a 2D PFC simulation of grain formation in TSVs with different geometries. To study the copper pumping phenomenon, mechanical loads have to be applied on such samples with corresponding grain structures. Since the PFC method does not model a solid-vacuum interface, traction boundary conditions in the PFC model using a penalty term are introduced. In deformation simulations, dislocation creation and annihilation are emergent characters of the PFC model. Therefore, applying the PFC model to TSV filler allows the investigation of the dislocation dynamics responsible for the metal extrusion or intrusion problem. The recorded dislocation dynamics can also be used to formulate dislocation-based constitutive laws for the CPFE method. In addition, progress has been made to couple the atomic-scale PFC density field to order parameters that describe ferromagnetic and ferroelectric ordering [90]. As such, the PFC models can be used to study the role of external magnetic or electric fields on the evolution of atomic scale defect structures on diffusion time scales. This provides an opportunity to study electromigration related reliability issues of TSVs using the PFC models.

4.5 Summary

Some of the key reliability issues related to TSVs are discussed, starting with the origin and nature of stresses in TSVs, their effects on microstructure development and evolution, and their role on device performance and BEOL or RDL reliability. The main reliability complications are (i) void growth to relieve internal stress gradients during pre or post-CMP annealing, (ii) copper pumping during processing or service due to differential thermal expansion mismatch and associated inelastic deformation of the copper that may be accommodated by sliding at the interface, and associated distortion of the BEOL/RDL structure, (iii) piezoresistive effects that lead to device performance loss and require a keep-out zone adjacent to TSVs, and (iv) electromigration induced void growth downstream of the electron flow direction in the interconnect lines outside the TSV. These effects have been reviewed in the context of the associated physical mechanisms. Finally, two promising methods, i.e., the CPFEA and the PFC method, to enable atomistically-informed reliability modeling of TSVs are introduced.

Notes

- 1.

It should be noted that the exact value of the stress for a wavenumber shift may depend on the materials properties used in secular equation (i.e., set of equations in the reference axes which may be different than that of materials crystallographic reference system). It can lie in the range of 430–520 MPa [25].

References

H.J. Bunge, R.A. Schwarzer, Orientation stereology—a new branch in texture research. Adv. Eng. Mater. 3, 25–39 (2001)

H.J. Bunge, Texture Analysis in Materials Science—Mathematical Methods (Butterworth & Co, London, 1982)

T. Hrncir, J. Dluhos, L. Hladik, E. Moyal, Advances in FIB-SEM analysis of TSV and solder bumps—approaching higher precision, throughput and comprehensiveness, in IST-FA 2014: Proceedings of the 40th International Symposium for Testing and Failure Analysis (Houston, Texas, USA, November 2014)

B. Wu, A. Kumar, S. Pamarthy, High aspect ratio silicon etch: a review. J. App. Phys. 108, 051101 (2010)

L.B. Mauer, J. Taddei, R. Yousself, Wet silicon etch process for TSV reveal, in Electronic Components and Technology Conference, IEEE, p. 878 (2014)

C. Okoro, K. Vanstreels, R. Labie, O. Luhn, B. Vandevelde, B. Verlinden, D. Vandepitte, Influence of annealing condition on the mechanical and microstructural behavior of electro-plated Cu-TSV. J. Micromech. Microeng. 20, 045032 (2010)

H. Wang, P. Cheng, H. Wang, R. Liu, L. Sun, Q. Rao, Z. Wang, T. Gu, G. Ding, Effect of current density on microstructure and mechanical property of Cu micro-cylinders electrode-posited in through silicon vias. Mater. Charact. 109, 164–172 (2015)

K.E. Elder, M. Grant, Modeling elastic and plastic deformations in nonequilibrium processing using phase field crystals. Phys. Rev. E 70, 051605 (2004)

P. Stefanovic, M. Haataja, N. Provatas, Phase field crystal study of deformation and plasticity in nanocrystalline materials. Phys. Rev. E 80, 046107 (2009)

Natinoal Science and Technology Council, Materials genome initiative for global competitiveness. National Science and Technology Council, Washington, D.C. (2011). http://www.mgi.gov. Accessed 21 June 2016

S.R. Kalidindi, M. De Graef, Materials data science: current status and future outlook. Annu. Rev. Mater. Res. 45, 171–193 (2015)

H. Xiong, Z. Huang, P. Conway, A method for quantification of the effects of size and geometry on the microstructure of miniature interconnects. J. Electron. Mater. 43, 618–629 (2014)

M. Krause, et al., Characterization and failure analysis of TSV interconnects: from non-destructive defect localization to material analysis with nanometer resolution, in Electronic Components and Technology Conference, IEEE, p. 1452 (2011)

A. Heryanto, W.N. Putra, A. Trigg, S. Gao, W.S. Kwon, F.X. Che, X.F. Ang, J. Wei, R.I. Made, C.L. Gan, K.L. Pey, Effect of copper TSV annealing on via protrusion for TSV Wafer Fabrication. J. Electron. Mater. 41, 2533–2542 (2012)

C. Okoro, R. Labie, K. Vanstreels, A. Franquet, M. Gonzalez, B. Vandevelde, E. Beyne, D. Vandepitte, B. Verlinden, Impact of the electrodeposition chemistry used for TSV filling on the microstructural and thermo-mechanical response of Cu. J. Mater. Sci. 46, 3868–3882 (2011)

X. Feng, T. Huang, M. Li, The influence of annealing on characteristics of copper in TSV. ECS J. Solid State Sci. Technol. 4, P451–P455 (2015)

K.J. Ganesh, A.D. Darbal, S. Rajasekhara, G.S. Rohrer, K. Barmak, P.J. Ferreira, Effect of downscaling nano-copper interconnects on the microstructure revealed by high resolution TEM-orientation-mapping. Nanotechnology 23, 135702 (2012)

M. Faheem, R.R. Giridharan, Y. Liang, P. van Der Heide, Micro-XRD characterization of a single copper filled through-silicon via. Mater. Lett. 161, 391–394 (2015)

G.G. Stoney, The tension of metallic films deposited by electrolysis. Proc. R. Soc. Lond. A 82, 172–175 (1909)

T. Jiang, S.-K. Ryu, Q. Zhao, J. Im, R. Huang, P.S. Ho, Measurement and analysis of thermal stresses in 3D integrated structures containing through-silicon-vias. Microelectron. Reliab. 53, 53–62 (2013)

S.K. Ryu, T. Jiang, K.H. Lu, J. Im, H.-Y. Son, K.-Y. Byun, R. Huang, P.S. Ho, Characterization of thermal stresses in through-silicon vias for three-dimensional interconnects by bending beam technique. Appl. Phys. Lett. 100, 041901 (2012)

K.H. Lu, S.K. Ryu, Q. Zhao, K. Hummler, J. Im, R. Huang, P.S. Ho, Temperature-dependent thermal stress determination for through-silicon-vias (TSVs) by combining bending beam technique with finite element analysis, in Electronic Components and Technology Conference, IEEE, p. 1475 (2011)

Q. Zhao, J. Im, R. Huang, P.S. Ho, Extension of micro-Raman spectroscopy for full-component stress characterization of TSV structures, in Electronic Components and Technology Conference, IEEE, p. 397 (2013)

A.D. Trigg, L.H. Yu, C.K. Cheng, R. Kumar, D.L. Kwong, T. Ueda, T. Ishigaki, K. Kang, W.S. Yoo, Three dimensional stress mapping of silicon surrounded by copper filled through silicon vias using polychromator-based multi-wavelength micro Raman spectroscopy. Appl. Phys. Exp. 3, 086601 (2010)

I. De Wolf, V. Simons, V. Cherman, R. Labie, B. Vandevelde, E. Beyne, In-depth Raman spectroscopy analysis of various parameters affecting the mechanical stress near the surface and bulk of Cu-TSVs, in Electronic Components and Technology Conference, IEEE, p. 331 (2012)

M. Song, K.R. Mundboth, J.A. Szpunar, L. Chen, R. Feng, Characterization of local strain/stress in copper through-silicon via structures using synchrotron x-ray microdiffraction, electron backscattered diffraction and nonlinear thermomechanical model. J. Micromech. Microeng. 25, 085002 (2015)

C. Okoro, L.E. Levine, R. Xu, K. Hummler, Y. Obeng, X-ray micro-beam diffraction measurement of the effect of thermal cycling on stress in Cu TSV: a comparative study, in Electronic Components and Technology Conference, IEEE, p. 1648 (2014)

V.H. Vartanian, R.A. Allen, L. Smith, K. Hummler, S. Olson, B.C. Sapp, Metrology needs for through-silicon via fabrication. J. Micro/Nanolith MEMS MOEMS 13, 011206 (2014)

A.S. Budiman, H.-A.-S. Shin, B.-J. Kim, B.-J. Kim, S.-H. Hwang, H.-Y. Son, M.-S. Suh, Q.-H. Chung, K.-Y. Byun, N. Tamura, M. Kunz, Y.-C. Joo, Measurement of stresses in Cu and Si around through-silicon via by synchrotron X-ray microdiffraction for 3-dimensional integrated circuits. Microelectron. Reliab. 52, 530–533 (2012)

T. Tian, Shin H. Morusupalli, H.-Y. Son, K.-Y. Byun, Y.-C. Joo, R. Caramto, L. Smith, Y.-L. Shen, M. Kunz, N. Tamura, A.S. Budiman, On the mechanical stresses of Cu through-silicon via (TSV) samples fabricated by SK Hynix vs. SEMATECH Enabling robust and reliable 3-D interconnect/integrated circuit (IC) technology. Procedia Eng. 139, 101–111 (2016)

L.E. Levine, C. Okoro, R. Xu, Full elastic strain and stress tensor measurements from individual dislocation cells in copper through-Si vias. IUCrJ 2, 635–642 (2015)

J.M.E. Harper, C. Cabral Jr., P.C. Andricacos, L. Gignac, I.C. Noyan, K.P. Rodbell, C.K. Hu, Mechanisms for microstructure evolution in electroplated copper thin films near room temperature. J. Appl. Phys. 86, 2516–2525 (1999)

L.W. Kong, J.R. LIoyd, K.B. Yeap, E. Zschech, A. Rudack, M. Liehr, A. Diebold, Applying x-ray microscopy and finite element modeling to identify the mechanism of stress-assisted void growth in through-silicon vias. J. Appl. Phys. 110, 053502 (2011)

I. De Wolf, K. Croes, O. Varela Pedreira, R. Labie, A. Redolfi, M. Van De Peer, K. Vanstreels, C. Okoro, B. Vandevelde, E. Beyne, Cu pumping in TSVs: effect of pre-CMP thermal budget. Microelectron. Reliab. 51, 1856–1859 (2011)

C. McDonough, B. Backes, W. Wang, R. Caramto, R.E. Gree, Thermal and spatial dependence of TSV-induced stress in Si, in Interconnect Technology Conference and 2011 Materials for Advanced Metallization (IITC/MAM) (Dresden, May 2011)

C. Okoro, L.E. Levine, R. Xu, Y.S. Obeng, Experimentally, how does Cu TSV diameter influence its stress state? in Electronic Components and Technology Conference, IEEE, p. 54 (2015)

K. Athikulwongse, A. Chakraborty, J.S. Yang, D.Z. Pan, S.K. Lim, Stress-driven 3D-IC placement with TSV keep-out zone and regularity study, in International Conference on Computer-Aided Design (ICCAD) (San Jose, CA, November 2010), IEEE/ACM, p. 669

P.S. Ho, S.K. Ryu, K.H. Lu, Q. Zhao, J. Im, R. Huang, Reliability challenges for 3D interconnects: a material and design perspective. Presentation at the 3D Sematech Workshop (Burlingame, 17, March 2011)

T. Jiang, S.K. Ryu, J. Im, H.Y. Son, N.S. Kim, R. Huang, P.S. Ho, Impact of material and microstructure on thermal stresses and reliability of through-silicon via (TSV) structures, in IITC: IEEE International Interconnect Technology Conference (Kyoto, June 2013)

E.J. Cheng, Y.L. Shen, Thermal expansion behavior of through-silicon-via structures in three-dimensional microelectronic packaging. Microelectron. Reliab. 52, 534–540 (2012)

X. Liu, Q. Chen, V. Sundaram, M. Simmons-Matthews, K.P. Wachtler, R.R. Tummla, S.K. Sitaraman, Thermo-mechanical behavior of through silicon vias in a 3D integrated package with inter-chip microbumps, in Electronic Components and Technology Conference, IEEE, p. 1190 (2011)

C. Okoro, J.W. La, F. Golshany, K. Hummler, Y.S. Obeng, A detailed failure analysis examination of the effect of thermal cycling on Cu TSV reliability. IEEE Trans. Electron. Dev. 61, 15–22 (2014)

S.-H. Hwang, B.-J. Kim, H.-Y. Lee, Y.-C. Joo, Electrical and mechanical properties of through-silicon vias and bonding layers in stacked wafers for 3D integrated circuits. J. Electron. Mater. 41, 232–240 (2012)

H.-A.-S. Shin, B.-J. Kim, J.-H. Kim, S.-H. Hwang, A.S. Budiman, H.-Y. Son, K.-Y. Byun, N. Tamura, M. Kunz, D.-I. Kim, Y.-C. Joo, Microstructure evolution and defect formation in Cu through-silicon vias (TSVs) during thermal annealing. J. Electron. Mater. 41, 712–719 (2012)

Z. Wu, Z. Huang, Y. Ma, H. Xiong, P.P. Conway, Effects of the microstructure of copper through-silicon vias on their thermally induced linear elastic mechanical behavior. Electron. Mater. Lett. 10, 281–292 (2014)

N. Nabiollahi, N. Moelans, M. Gonzalez, J. De Messemaeker, C.J. Wilson, K. Croes, E. Beyne, I. De Wolf, Microstructure simulation of grain growth in Cu through silicon vias using phase-field modeling. Microelectron. Reliab. 55, 765–770 (2015)

T. Jiang, C. Wu, J. Im, R. Huang, P.S. Ho, Effect of microstructure on via extrusion profile and reliability implication for copper through-silicon vias (TSVs) structures, in IITC/AMC: International Interconnect Technology Conference/Advanced Metallization Conference, IEEE (San Jose, CA, May 2014), p. 377

H.D. Merchant, Thermal response of electrodeposited copper. J. Electron. Mater. 24, 919–925 (1995)

P. Bayat, D. Vogel, R.D. Rodriguez, E. Sheremet, D.R.T. Zahn, S. Rzepka, B. Michel, Thermo-mechanical characterization of copper through-silicon vias (Cu-TSVs) using micro-Raman spectroscopy and atomic force microscopy. Microelectron. Eng. 137, 101–104 (2015)

D. Smith, S. Singh, Y. Ramnath, M. Rabie, D. Zhang, L. England, TSV residual Cu step height analysis by white light interferometry for 3D integration, in Electronic Components and Technology Conference, IEEE, p. 578 (2015)

C. Okoro, C. Huyghebaert, J. Van Olmen, R. Labie, K. Lambrinou, B. Vandevelde, E. Beyne, Van- depitte D, Elimination of the axial deformation problem of Cu TSV in 3D integration. AIP Conf. Proc. 1300, 214 (2010)

I. Dutta, P. Kumar, M.S. Bakir, Interface-related reliability challenges in 3-D interconnect systems with through-silicon vias. JOM 63, 70–77 (2011)

P. Kumar, I. Dutta, M.S. Bakir, Interfacial effects during thermal cycling of Cu-filled through-silicon vias (TSV). J. Electron. Mater. 41, 322–335 (2012)

L. Meinshausen, M. Liu, T.K. Lee, I. Dutta, L. Li, Reliability implications of thermo-mechanically and electrically induced interfacial sliding of through-silicon vias in 3D packages, in ASME 2015 International Technical Conference and Exhibition on Packaging and Integration of Electronic and Photonic Microsystems (San Francisco, CA, July 2015)

J. De Messemaeker, O.V. Pereira, H. Philipsen, E. Beyne, I. De Wolf, T. Van der Donck, K. Croes, Correlation between Cu microstructure and TSV Cu pumping, in Electronic Components and Technology Conference, IEEE, p. 613 (2014)

J. De Messemaeker, O.V. Pereira, B. Vandevelde, H. Philipsen, I. De Wolf, E. Beyne, K. Croes, Impact of post-plating anneal and through-silicon via dimensions on Cu pumping, in Electronic Components and Technology Conference, IEEE, p. 586 (2013)

P. Kumar, I. Dutta, Influence of electric current on diffusionally accommodated sliding at hetero-interfaces. Acta Mater. 59, 2096–2108 (2011)

P. Kumar, I. Dutta, Effect of substrate surface on electromigration-induced sliding at hetero-interfaces. J. Phys. D 46, 155303 (2013)

K.A. Peterson, I. Dutta, M.W. Chen, Diffusionally accommodated interfacial sliding in metal-silicon systems. Acta Mater. 51, 2831–2846 (2003)

H. Yang, T.K. Lee, L. Meinshausen, I. Dutta, J. Electronic. Mater. 48, 159–169 (2019)

Y.C. Tan, C.M. Tan, X.W. Zhang, T.C. Chai, D.Q. Yu, Electromigration performance of through silicon via (TSV)—a modeling approach. Microelectron. Reliab. 50, 1336–1340 (2010)

T. Frank, S. Moreau, C. Chappaz, L. Arnaud, P. Leduc, A. Thuaire, L. Anghel, Electromigration behavior of 3D-IC TSV interconnects, in Electronic Components and Technology Conference, IEEE, p. 326 (2012)

T. Frank, S. Moreau, C. Chappaz, P. Leduc, L. Arnaud, A. Thuaire, E. Chery, F. Lorut, L. Anghel, G. Poupon, Reliability of TSV interconnects: electromigration, thermal cycling, and impact on above metal level dielectric. Microelectron. Reliab. 53, 17–29 (2013)

H.J. Choi, S.M. Choi, M.S. Yeo, S.D. Cho, D.C. Baek, J. Park, An experimental study on the TSV reliability: electromigration (EM) and time dependant dielectric breakdown (TDDB), in IITC: IEEE International Interconnect Technology Conference. San Jose, CA (June, 2012)

T.K. Lee, I. Dutta, Unpublished Research

R. Radojcic, M. Nowak, M. Nakamoto, TechTuning: stress management for 3D through-silicon-via stacking technologies. AIP Conf. Proc. 1378, 5–20 (2011)

F. Roters, Advanced material models for the crystal plasticity finite element method: development of a general CPFEM framework. Habilitation Thesis, RWTH Aachen University (2011)

G.I. Taylor, The mechanism of plastic deformation of crystals. Part I. Theor. Proc. R. Soc. Lond. A 145, 362–387 (1934)

G.I. Taylor, The mechanism of plastic deformation of crystals. Part II. Comparison with observations. Proc. R. Soc. Lond. A 145, 388–404 (1934)

D. Peirce, R.J. Asaro, A. Needleman, An analysis of nonuniform and localized deformation in ductile single crystals. Acta Metall. 30, 1087–1119 (1982)

S.V. Harren, H.E. Deve, R.J. Asaro (1988) Shear band formation in plane strain compression. Acta Metall. 36, 2435–2480 (1988)

S.V. Harren, R.J. Asaro, Nonuniform deformations in polycrystals and aspects of the validity of the Taylor model. J. Mech. Phys. Solids 37, 191–232 (1989)

R. Becker, J.F. Butler, H. Hu, L.A. Lalli, Analysis of an aluminum single crystal with unstable initial orientation (001) [110] in channel die compression. Metall. Trans. A 22, 45–48 (1991)

W.D. Nix, J.R. Greer, G. Feng, E.T. Lilleodden, Deformation at the nanometer and micrometer length scales: effects of strain gradients and dislocation starvation. Thin Solid Films 515, 3152–3157 (2007)

S.R. Kalidindi, Incorporation of deformation twinning in crystal plasticity models. J. Mech. Phys. Solids 46, 267–290 (1998)

D. Raabe, D. Ma, F. Roters, Effects of initial orientation, sample geometry and friction on anisotropy and crystallographic orientation changes in single crystal microcompression deformation: a crystal plasticity finite element study. Acta Mater. 55, 4567–4583 (2007)

F. Roters, P. Eisenlohr, C. Kords, D.D. Tjahjanto, M. Diehl, D. Raabe, DAMASK: the Du¨sseldorf advanced material simulation kit for studying crystal plasticity using an FE based or a spectral numerical solver. Procedia IUTAM 3, 3–10 (2012)

D. Cereceda, M. Diehl, F. Roters, D. Raabe, J.M. Perlado, J. Marian, Unraveling the temperature dependence of the yield strength in single-crystal tungsten using atomistically-informed crystal plasticity calculations. Int. J. Plasticity 78, 242–265 (2016)

L.Q. Chen, Phase-field models for microstructure evolution. Ann. Rev. Mater. Res. 32, 113–140 (2002)

N. Provatas, K. Elder, Phase-Field Methods in Material Science and Engineering (Wiley-VCH, Weinheim, 2010)

K.R. Elder, M. Katakowski, M. Haataja, M. Grant, Modeling elasticity in crystal growth. Phys. Rev. Lett. 88, 245701 (2002)

M. Seymour, N. Provatas, Structural phase field crystal approach for modeling graphene and other two-dimensional structures. Phys Rev B 93, 035447 (2016)

L. Granasy, F. Podmaniczky, G.I. Toth, G. Tegze, T. Pusztai, Heterogeneous nucleation of/on nanoparticles: a density functional study using the phase-field crystal model. Chem. Soc. Rev. 43, 2159–2173 (2014)

K.R. Elder, N. Provatas, J. Berry, P. Stefanovic, M. Grant, Phase-field crystal modeling and classical density functional theory of freezing. Phys. Rev. B 75, 064107 (2007)

N. Ofori-Opoku, V. Fallah, M. Greenwood, S. Esmaeili, N. Provatas, Multicomponent phase-field crystal model for structural transformations in metal alloys. Phys. Rev. B 87, 134105 (2013)

J. Berry, N. Provatas, J. Rottler, C.W. Sinclair, Defect stability in phase-field crystal models: Stacking faults and partial dislocations. Phys. Rev. B 86, 224112 (2012)

J. Berry, N. Provatas, J. Rottler, C.W. Sinclair, Phase field crystal modeling as a unified atomistic approach to defect dynamics. Phys. Rev. B 89, 214117 (2014)

J. Berry, J. Rottler, C.W. Sinclair, N. Provatas, Atomistic study of diffusion-mediated plasticity and creep using phase field crystal methods. Phys. Rev. B 92, 134103 (2015)

M. Greenwood, N. Ofori-Opoku, J. Rottler, N. Provatas, Modeling structural transformations in binary alloys with phase field crystals. Phys. Rev. B 84, 064104 (2011)

M. Seymour, F. Sanches, K. Elder, N. Provatas, Phase-field crystal approach for modeling the role of microstructure in multiferroic composite materials. Phys. Rev. B 92, 184109 (2015)

Acknowledgements

The authors (PK & ID) acknowledge financial support for some of the re- ported work by the National Science Foundation (DMR-0513874 and DMR-1309843), Cisco Research Council and the Semiconductor Research Corporation. The contributions of, and collaborations with several colleagues (Dr. Lutz Meinshausen, formerly of Washington State University, and currently at Global Foundries, Dresden, Germany; Dr. Tae-Kyu Lee, formerly of Cisco Systems, and currently at Portland State University; Dr. Ravi Mahajan of Intel Corporation; Dr. Vijay Sarihan of Freescale Semiconductor, and Professor Muhannad Bakir of Georgia Tech) are gratefully acknowledged. The assistance of current and former colleagues (Dr. Hanry Yang of Washington State University, and Dr. Zhe Huang, formerly of Washington State University, and currently at Seagate Technologies) with the literature survey is also gratefully acknowledged. The author (ZH) acknowledges financial support for his research by the Pearl River Science and Technology Nova Program of Guangzhou under grant no. 2012J2200074, the National Natural Science Foundation of China (NSFC) under grant no. 51004118, and Guangdong Natural Science Foundation under grant no. 2015A030312011. The author (ZH) also acknowledges useful discussions with Dr. F. Roters of Max Planck Institute for Iron Research on the CPFE method and Prof. N. Provatas of McGill University on phase crystal models. The editors would like to thank George Vakanas from Intel Corporation for his critical review of this Chapter.

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2021 The Editor(s) (if applicable) and The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd.

About this chapter

Cite this chapter

Kumar, P., Lee, TK., Dutta, I., Huang, Z., Conway, P. (2021). Microstructure and Mechanical Reliability Issues of TSV. In: Li, Y., Goyal, D. (eds) 3D Microelectronic Packaging. Springer Series in Advanced Microelectronics, vol 64. Springer, Singapore. https://doi.org/10.1007/978-981-15-7090-2_4

Download citation

DOI: https://doi.org/10.1007/978-981-15-7090-2_4

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-15-7089-6

Online ISBN: 978-981-15-7090-2

eBook Packages: EngineeringEngineering (R0)