Abstract

Single-electron transistors (SETs) have shown their competence to overpower MOSFETs as well as FinFETs in low power regime. However, research to exhibit room temperature operation and its demonstration for application in logic and memory circuits is still in infancy. A SET contains two ultra-thin tunnel barriers and a conductive island which work on the principle of Coulomb blockade (CB) and tunneling. Its dimensions must be planned properly to exhibit room temperature operation with CMOS compatibility. In this work, the island engineering technique is proposed for devising SET so as to observe both Coulomb blockade and quantum mechanical tunneling at room temperature. The island engineering is carried out for aluminum and copper island. The SET has been simulated in TCAD using the designed dimensions and its output as well as transfer characteristics have been plotted at room temperature. The analyses illustrate that out of all the SET devices, aluminum island SET with 4 nm tunnel barrier with 17 nm island length offers the desired CB and tunneling current in tens of nA range. To validate the results and ascertain the concept of CMOS compatible design, SET transfer and output characteristics have been simulated using Cadence Virtuoso using MIB model. The proposed technique of SET is also compared with the other SET optimization techniques.

Access provided by Autonomous University of Puebla. Download conference paper PDF

Similar content being viewed by others

Keywords

- Coulomb blockade

- Island engineering

- MIB model

- Nano-electronics

- Quantum mechanical tunneling

- Single-electron transistor

- TCAD

1 Introduction

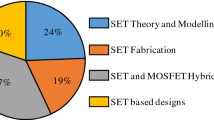

Owing to small size and low power consumption, single-electron transistors (SETs) are becoming an attractive alternative in the post-CMOS era of semiconductor technology [1,2,3,4]. They operate on the principles of Coulomb blockade and quantum mechanical tunneling (QMT), depicting the on and the off states of the device, respectively [5,6,7]. SETs have proved their potential to be a promising candidate for non-volatile memory as well as logic applications [2, 3, 8]. SET-MOS hybridization is also one huge field of interest for logic development. It is envisaged that SETs can outperform CMOS in nanometer regime with its virtues like ultra-low power consumption and scalability [2, 3, 9]. Since last two decades, many researchers have worked to overcome two fundamental issues of SETs, viz., (a) mass production and (b) room temperature operation. In recent years, with advent in time and technology, many CMOS-compatible processes are demonstrated for fabrication of SETs [2, 4, 10,11,12]. They include nanodamascene processes [4], patterning with reactive ion etching and electromigration, chemical mechanical polishing-based fabrication [10], self-assembly and self-alignment of quantum dots [11], even optical lithography of silicon nanowire [12]. Thus, prospects of integrating SETs in a CMOS process are bright. However, room temperature operation is still a matter of experimentation.

Coulomb blockade is inherently a low energy phenomenon [6, 7]. Hence, it cannot be detected at ambient temperatures easily. So, to observe the SET operation in true sense, the device needs to be engineered carefully. The material and dimensions of island play crucial role in tunneling of electron between source and drain. Hence, the effect of island on SET drain current along with CB and QMT must be observed. The structure of island should also be compatible with the CMOS fabrication processes. In this paper, we will present the rudiments of SET design followed by a detailed analytical approach. We will then simulate the device demonstrating thorough island engineering. Results show occurrence of both, the Coulomb blockade and the quantum mechanical tunneling in the optimized device. Finally, we will present validation of our device with MIB model [3].

2 SET Design Considerations

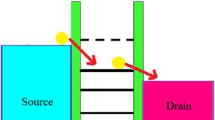

As shown in Fig. 1, a SET consists of two tunnel junctions on source and drain sides sandwiching a quantum dot. Every junction offers a barrier—popularly known as Coulomb blockade—to flow of electrons. These junctions or barriers ensure weak coupling of source and drain with the quantum island. An electron from source, after overcoming Coulomb blockade energy level, enters the island by the process of tunneling. Simultaneously, an electron leaves the island and tunnels to the drain, causing current to flow. Thus, to ensure the charge transfer, one needs to supply Coulomb energy to the island. This energy can be supplied by an external voltage source. It is given by [5,6,7],

where C∑ is the capacitance of the island given by (2CJ + CG), CJ being the tunneling junction capacitance. Correspondingly, Coulomb voltage is given by

This capacitance is primarily governed by the device geometry and material parameters. With reduction in this capacitance, EC increases, making the junction more opaque.

In addition to this capacitive coupling, the barrier offers tunnel resistance, which must be larger than the fundamental resistance \({R}_{T}\gg \boldsymbol{ }\frac{\boldsymbol{\hslash }}{{{\varvec{q}}}^{2}}\), that is, approximately 25.8 KΩ [5,6,7]. It ensures localization of electron states to the island during blockade. RT also controls the driving capability of the device. The device maximum operating frequency is 1/(RTC) [9]. Conflict of speed and power can be addressed by fine tuning these two electrical parameters. This demands appropriate materials choice and fabrication of capacitors of the order of attofarads, which is possible in today’s era.

For designing a rugged SET, Coulomb energy of the SET should be sufficiently higher than the ambient thermal energy. Table 1 illustrates capacitance and bias requirements with respect to thermal robustness. General trend dictates acceptable range as 20 KBT.

It is evident from Table 1 that for room temperature operation of SETs, appropriate tunnel junction engineering and optimization is crucial so as to obtain: (a) very low total capacitance (aF), (b) high driving current (nA) and (c) very low thermionic current (during opaque state of the junction). A low-k dielectric like SiO2 can offer a barrier less than 0.4 eV [13] aiding high level of transparency. But for junction opacity, high-k dielectric like TiO2 which offers barrier greater than 1 eV is required. To resolve this conflict, Hajjam et al. proposed multi-dielectric stack to control the off current [13]. However, it involved realizing ultra-thin layers of various dielectric increasing design and process complexity. We propose that instead of tunnel engineering, one can opt for island engineering to achieve acceptable ION and IOFF values. It is comparatively easy, simple to comprehend and process-friendly.

Figure 2a, b shows structure and MIB model of a single-gate SET [3]. Source, drain and gate are made up of n-polysilicon (phosphorus, 1e19 cm−3), whereas the substrate is p-silicon (boron, 1e15 cm−3). Tunneling junction capacitances on source as well as drain side are CTD = CTS = CJ, control gate capacitance is CG, tunnel junction resistances are RTD = RTS = RT = 1 MΩ. The total device capacitance is defined as CΣ = 2CJ + CG. SET design parameters compatible with BSIM predictive technology model (PTM) [14] and 22 nm node CMOS model operation at T = 300 K are chosen. Consequently, supply voltage is chosen to be 0.8 V. For a robust reliable design of SET logic, which can operate with the least possible error at room temperature, the charging energy EC must be as large as possible compared with the thermal energy. As such, Coulomb/charging energy = e2/CΣ = 40 KBT = 1.036 eV. This leads to a value of 0.155 aF for CΣ. So, Coulomb blockade voltage = e/2CΣ = 0.51 V. Control gate capacitance = e/2VDD = 0.045 aF. Hence, junction/tunnel capacitance = (CΣ – CG)/2 = 0.055 aF. Background charge is neglected.

a Single-gate SET structure, b equivalent MIB model where tunnel barriers are represented by parallel RC combinations (RTS || CTS and RTD || CTD), gate dielectric as gate capacitance CG, conductive island as black dot and two bias supplies, namely, VDS and VGS between drain––source and gatesource, respectively [3]

3 Island Engineering

Figure 3 shows top view of single-gate SET under consideration.

Table 2 illustrates SET electrical parameters and their possible mapping with its physical parameters. Our strategy is to play with island and junction dimensions while maintaining overall device dimension constant. The tunnel barrier engineering plays a vital role for this work to choose the tunnel barrier thickness [15]. We have experimented with aluminum and copper as island material, due to general good conductivity. In TCAD simulations, for global device, we used Philips Unified Mobility Model because it incorporates doping and temperature dependencies. For modeling tunneling near insulator for rapidly varying field, we used band-to-band and Schenk recombination models [16]. At material interfaces, we also used direct tunneling model as the barrier is trapezoidal [15, 16]. Junction width less than 3 nm did not result in satisfactory Coulomb blockade and greater than 4 nm did not show tunneling in the neighborhood of bias voltage. Under no influence of gate, devices exhibit blockade and tunneling as shown in Fig. 4a, b, for aluminum and copper island, respectively.

The devices clearly show the mechanisms of Coulomb blockade and quantum mechanical tunneling. In the limiting case of small structures, the structure resistivity becomes proportional to ρ0 * λ for any given fixed dimension [17], where ρ0 and λ are the bulk resistivity and mean free path for electron phonon scattering, respectively. Thus, the metal with the lowest product ρ0 * λ is expected to exhibit the highest conductivity. This product is 6.70e–16Ω m2 for copper and 5.01e–16Ω m2 for aluminum [17]. Hence, the current capacity of aluminum devices is higher than the copper devices. Coulomb voltage and SET capacitances extracted from above profiles for all the devices are listed in Table 3.

First observation here is that copper island devices offer better confinement than their aluminum counterparts. Small islands have higher Coulomb voltage. This is attributed to increased confinement and hence higher blockade. It is also observed that the extracted values have higher degree of matching as the device capacitance becomes smaller and smaller. Effect of island dimension and material can be seen in Fig. 5.

So, it is found that bigger island leads to higher Coulomb blockade and lower drain current.

Finally, we settled for Device A with aluminum island (CG = 0.045 aF, CJ = 0.035 aF) and simulated it for the bipolar I–V behavior. Result obtained is shown in Fig. 6.

4 Validation

Validation of our work was done by implementing SET in cadence with the help of MIB model. Parameters extracted from the TCAD simulations were used for implementing MIB model [3]. The model setup and various results are as shown in Fig. 7a–d.

Clear-cut manifestation of Coulomb blockade, tunneling and Coulomb oscillations indicate successful implementation of the designed device. Effect of gate voltage can be easily seen in both output as well as the transfer characteristics.

Comparison of our technique with other groups peer work is mentioned in Table 4.

5 Conclusion

Owing to modern technological inventions, it is possible to fabricate very small capacitive structures. Hence, SET has a potential to operate at room temperature in ultra-low power applications. Island engineering can be sought as simplest method for optimizing SET. The aluminum island device simulated here gives a stable room temperature operation with a current of the order of 10 nA and is compatible with BSIM predictive technology model (PTM) and 22 nm node CMOS model. The device can operate at a bias voltage of 0.8 V and can be used in logic as well as memory applications. The proposed technique is simple and easily realizable compared with the other techniques proposed.

References

Likharev K (1987) Single-electron transistors: electrostatic analogs of the dc squids. IEEE Trans Magn 23(2):1142. https://doi.org/10.1109/TMAG.1987.1065001

Uchida K, Matsuzawa K, Toriumi A (1999) A new design scheme for logic circuits with single electron transistors. Jpn J Appl Phys 38:4027–4032. https://doi.org/10.1143/jjap.38.4027

Mahapatra S, Vaish V, Wasshuber C, Banerjee K, Ionescu AM (2004) Analytical modeling of single electron transistor for hybrid cmos-set analog ic design. IEEE Trans Electron Devices 51(11):1772. https://doi.org/10.1109/TED.2004.837369

Dubuc C, Beauvais J, Drouin D (2008) A nanodamascene process for advanced single-electron transistor fabrication. IEEE Trans Nanotechnol 7(1):68–73. https://doi.org/10.1109/TNANO.2007.913430

Mahapatra S, Ionescu AM (2006) Hybrid CMOS single-electron-transistor device and circuit design. Artech House, Norwood, MA

Hanson GW (2008) Fundamentals of nanoelectronics. Pearson/Prentice Hall, Upper Saddle River, NJ

Hamaguchi C (2009) Basic semiconductor physics. Springer, Berlin, Heidelberg, Neckar

Durrani ZAK, Irvine AC, Ahmed H, Nakazato K (1999) A memory cell with single-electron and metal-oxide-semiconductor transistor integration. Appl Phys Lett 74:1293–1295. https://doi.org/10.1063/1.123528

Parekh R, Beaumont A, Beauvais J, Drouin D (2012) Simulation and design methodology for hybrid SET-CMOS integrated logic at 22-nm room-temperature operation. IEEE Trans Electron Devices 59(4):918–923. https://doi.org/10.1109/TED.2012.2183374

Joshi V, Orlov AO, Snider GL (2008) Silicon single-electron transistor with oxide tunnel barriers fabricated using chemical mechanical polishing. J Vac Sci Technol B Microelectron Nanometer Struct 26(6):2587–2591. https://doi.org/10.1116/1.297887

Ray V, Subramanian R, Bhadrachalam P, Ma L-C, Kim C-U, Koh SJ (2008) CMOS-compatible fabrication of room-temperature single-electron devices. Nat Nanotechnol 3(10):603–608. https://doi.org/10.1038/nnano.2008.267

Sun Y, Rusli, Singh N (2011) Room-temperature operation of silicon single-electron transistor fabricated using optical lithography. IEEE Trans Nanotechnol 10(1):96–98. https://doi.org/10.1109/TNANO.2010.2086475

Hajjam KGE, Bounouar MA, Baboux NA, Ecoffey S, Guilmain M, Puyoo E, Francis L, Souifi A, Drouin D, Calmon F (2015) Tunnel junction engineering for optimized metallic single-electron transistor. IEEE Trans Electron Devices 62(9):2998–3003. https://doi.org/10.1109/TED.2015.2452575

Predictive Technology Model (PTM). In: Predictive Technology Model (PTM). https://ptm.asu.edu/.

Shah R, Dhavse R (2018) Tunnel barrier optimization for room temperature operation of single electron transistors. In: Proceedings of the nanotech France 2018 international conference (nanotech France 2018), Sector, Paris, pp 37–40

Sentaurus Device User Guide.

Gall D (2016) Electron mean free path in elemental metals. J Appl Phys 119(8):085101. https://doi.org/10.1063/1.4942216

Beaumont A, Dubuc C, Beauvais J, Drouin D (2009) Room temperature single-electron transistor featuring gate-enhanced on-state current. IEEE Electron Device Lett 30:766–768. https://doi.org/10.1109/led.2009.2021493

Lee Y-C, Joshi V, Orlov AO, Snider GL (2010) Si single electron transistor fabricated by chemical mechanical polishing. J Vac Sci Technol B Nanotechnol Microelectron Mater Process Meas Phenom 28(6). https://doi.org/10.1116/1.3498748

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2021 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Shah, R., Parekh, R., Dhavse, R. (2021). Island Engineering of Single-Electron Transistor for Room Temperature Operation. In: Patel, Z., Gupta, S., Kumar Y. B., N. (eds) Advances in VLSI and Embedded Systems. Lecture Notes in Electrical Engineering, vol 676. Springer, Singapore. https://doi.org/10.1007/978-981-15-6229-7_23

Download citation

DOI: https://doi.org/10.1007/978-981-15-6229-7_23

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-15-6228-0

Online ISBN: 978-981-15-6229-7

eBook Packages: EngineeringEngineering (R0)