Abstract

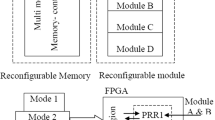

With extensive usage of Field Programmable Gate Arrays (FPGAs), a reconfigurable computing platform enhances the wide variety of Digital Signal Processing (DSP) applications using Lookup Table (LUT), Flip-Flop, and multiplexers. Reconfigurable computation using memory becomes a subject of current research. FPGAs can be reprogrammed an unlimited number of times in which various DSP algorithms can be executed on a single hardware device, just as many different software algorithms can run on a conventional processor. The general architectures for DSP consist of a reconfigurable interconnection, Computational Elements (CEs), and memory. This article discusses on the CE architectures based on Memory (CEMs) and Serial arithmetic (CESs). Reconfigurable computing based on memory is much faster, reliable, and, hence the computation using memory requires less delay and power. The CEMs perform multiplication and addition using LUT and the CESs perform computation using serial arithmetic’s. The results of the CESs, CEMs, and the computational reuse processing elements are compared. The architectures design based on CEMs significantly improves the performance of the previously reported results in terms of speed, area, and power using Xilinx Virtex-II FPGA, and Xilinx Vivado software.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Brown, S., Rose, J.: FPGA and CPLD architectures: a tutorial. IEEE Des. Test Comput. 13(2), 42–57 (1996)

Compton, K., Hauck, S.: Reconfigurable computing: a survey of systems and software. ACM Comput. Surv. (CSUR) 34(2) (2002)

Tessier, R., Burleson, W.: Reconfigurable computing for digital signal processing: a survey. J. VLSI Sig. Proc. 28, 7–27 (2001)

Mazher Iqbal, J.L., Varadarajan, S.: High performance reconfigurable balanced shared memory architecture for embedded DSP. Int. J. Comput. Sci. Inf. Secur. 8(4), 198–206 (2010)

Mazher Iqbal, J.L., Varadarajan, S.: A new algorithm for FIR digital filter synthesis for a set of fixed coefficients. Eur. J. Sci. Res. 59(1), 104–114 (2011)

Mazher Iqbal, J.L., Varadarajan, S.: Performance Comparison of Reconfigurable Low Complexity FIR Filter Architectures vol. 250, pp. 637–642. Springer-Verlag Berlin Heidelberg, Springer LNCS-CCIS, (2011). https://doi.org/10.1007/978-3-642-25734-6_151

Mazher Iqbal, J.L., Varadarajan, S.: High performance reconfigurable FIR filter architecture using optimized multipliers. Circ. Syst. Signal Proc. 32, 663–682 (2013). https://doi.org/10.1007/s00034-012-9473-3

Mazher Iqbal, J.L., Varadarajan, S.: Memory based and memory less computation for low complexity reconfigurable digital FIR filter. WSEAS Trans. Syst. 12(3), 142–153 (2014)

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2021 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Mazher Iqbal, J.L., Manikandan, T. (2021). FPGA-Based Reconfigurable Architectures for DSP Computations. In: Suresh, P., Saravanakumar, U., Hussein Al Salameh, M. (eds) Advances in Smart System Technologies. Advances in Intelligent Systems and Computing, vol 1163. Springer, Singapore. https://doi.org/10.1007/978-981-15-5029-4_48

Download citation

DOI: https://doi.org/10.1007/978-981-15-5029-4_48

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-15-5028-7

Online ISBN: 978-981-15-5029-4

eBook Packages: Intelligent Technologies and RoboticsIntelligent Technologies and Robotics (R0)