Abstract

Promising nanoelectronic memories such as PCRAM, STT-RAM, Ferroelectric FET Memory and Resistive Random Access Memory (RRAM) are capable of substituting the conventional memory technologies such as SRAMs, DRAMs and flash memory in future computers. Among all these nanoelectronic memories RRAM results in higher density, lower power consumption, higher speed and better scalability which can fulfill the requirements of massive data growth as well as storage. But it is expected to go through numerous faults that reduce the reliability of the system. These faults may arise at any element of the memory system which includes the marginal circuits, inter junction and memory cell array. Read 1 Disturbance (R1D) fault is one among the main faults in RRAM that occurs, if the read value is 0 when 1 is the actual result which is kind of low resistance defect. In RRAM SET voltage (VSET), bit line voltage, restricted thermal stability and accumulated read current pulse leads to read disturbance faults and also when maximum current is applied for a read operation that immediately induces the read disturbance fault. As the read current and write current have the same path, read disturbance faults makes a bit flip. The accumulated effect of this read ‘1’ disturbance degrades the memory reliability. This kind of fault changes the value stored in a particular memory cell which leads to consequent inaccurate read values that keep on propagates till a new logic value is written in the same cell. Read disturbance lies between the read operation and read disturbance fault which is a major concern of today’s NVM since it directly affects the performance of the system. According to march C* test algorithm HfO2 based 1T1R RRAM’s R1D faults can be sensitized by ensuring the presence of ‘1’ (read 1) after the write ‘1’ operation and detected by another read 1 operation. In this article a novel March C2RR algorithm is proposed, here read operation is repeated twice in the second, fourth memory element (R3, R4 in M3 and R5, R6 in M4) and 100% fault coverage is achieved by the proposed method that detects R1D faults and all the random faults effectively.

Access provided by Autonomous University of Puebla. Download conference paper PDF

Similar content being viewed by others

Keywords

1 Introduction

The memory chip is the fundamental unit for every electronic system to store the data. The massive growth of data and various blooming electronic technologies require huge data storage capacity. This requirement is achieved by CMOS miniaturizations, the future resolution is to integrate CMOS and non-CMOS technologies such as spintronics, magnetic tunneling junctions, carbon nanotubes and memristors in a single memory chip. This hybrid memory technology is referred as nanoelectronic memories [9,10,11,12,13,14]. Due to the fiery expansion of digital data in the latest technology of Internet of Things (IoT), quick and scalable memory technologies are being researched for data storage and data-driven computation. 1T1R RRAM is one of the most promising candidates where the transistor is used to limit the pulse current that avoids the hard breakdown (HBD) in resistor [21, 22]. It can be applied in many fields like medical healthcare devices [24] and in system-on-chip (SoC) applications such as wireless sensor networks (WSNs) [23]. Various materials are used as resisitive switching element [18, 20] since 2007 HfO2 has been selected as “standard” gate dielectric material in modern CMOS transistors [25] due to its compatibility with the current semiconductor fabrication process hence HfO2 based 1T1R RRAM is tested with various existing algorithms and march C2RR algorithm is proposed for R1D fault detection.

2 Importance of Testing

Defect is the physical abnormality materialized by manufacturing process that was not originally defined in the design circuit. Due to the contaminations, unintended particles like an additional or misplaced materials results in hard defects. Moreover, the slight progression variations lead to latent defects like source/drain dislocation, inadequate doping and via pinholes that are much crucial in nanoelectronic memories. The fault is the symptom of defects and an exterior conflict. Exterior conflicts are due to environmental sources such as cosmic rays, alpha particles and temperature fluctuations that will result in three types of faults they are hard faults, intermittent faults, and transient faults. Hard faults arise with determination, intermittent faults that occur over and over again (i.e., appears, disappears and reappears repeatedly) which is caused by hidden defects or older elements. Transient faults appear and disappear shortly that is caused by exterior instability. The error is the outcome of fault at the output of a circuit and failure is the incapability of a circuit to carry out its intentional task due to errors. The capability of the system to handle the failure can be manifested as either an incorrect result, no result or delayed results (e.g., an exact result that delays from the intended time). Quality is the term used to quantify the defective devices that escape manufacturing tests but are returned back to the manufacturer by customers. Similarly reliability is the term used to quantify the ability of a system to operate correctly for a specified period of time under certain conditions. The longer a system operates correctly corresponds to higher reliability. However, faults due to latent defects and external disturbances affect the reliability. Since the applications of RRAM are deployed in various multidimensional applications, it has to be tested well for the proficient outcome. The principle behind the memory test is to authenticate that each storage site in a memory device is functionally correct. In case, if we fetch the arithmetical value 18 at a specific address, we look forward to tracing that particular value stored in a specific address until a new value is written to that address. i.e., the memory test is an act of writing some sequence of data to each and every address in the memory device and verifying the presence of that written data by reading back. At when all the values retrieved are the one which was written previously then the memory device is fault free. The expenditure, moment in time and the worth of the test are the considerations that require being weighed for every device in each company. But no issue what methodology is taken or how decisive consistency is for a meticulous purpose. All of this needs to be done earlier than ever before. The test is moving more rapidly to design any electronic system as quality is a key metric. As it does, it is moving much further to the left of the design through industrialized flow. Various factors involved in RRAM testing are reactive ion etching [3], thermal stability [15], thermal crosstalk [16] and more importantly various internal processing faults.

3 Operational Characteristics of RRAM

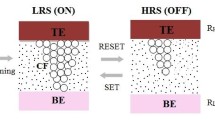

RRAM is fabricated on a p-type silicon substrate and a 3 nm Ti layer was deposited over the silicon layer as an adhesion promoting layer followed by the deposition of 100 nm of Ru depositions using RF magnetron sputtering. After the deposition process, the temperature was increased to 300 ℃, a 6 nm thick HfO2 was layered by reactive sputtering of Hf within 20% oxygen and 150 nm thickness of TiOx was deposited by the same method of Ti within 10% oxygen. RRAM is a passive device where both top and bottom layers are electrically conducting electrodes, insulating switching layer is located in-between the electrodes [1]. By applying external bias voltage the resistance can be changed. If a memristive element has a high resistance, then it is represented as HRS (High Resistance State). Similarly for low resistance state LRS. RON and ROFF are the maxima and the minimum CRS resistances respectively. Based on the bias voltage applied to RRAM write ‘0’ and write ‘1’ operations are carried, data ‘0’ low resistance state and data ‘1’ stands for by high resistance state (Fig. 1).

The connection between the top electrode layer and bottom electrode layer by means of the conductive layer results in SET operation (from HRS to LRS) which is responsible for a write operation and similarly subsequent application of voltage returns the resistance to the HRS in the RESET process. Reproducible resistive switching is achieved by repeating these processes. The disconnection between (HRS, LRS) them results in RESET operation (from LRS to HRS), which is responsible for read operation. RON = R(LRS) + R(LRS), ROFF = R(HRS) + R(LRS) (Figs. 2 and 3).

To accomplish forming and SET operation, a positive voltage is given to the bottom electrode (BE), whereas for the RESET operation top electrode (TE) was positively biased [2]. In the case of 1T1R RRAM structure which is used here, the forming/SET and RESET were programmed by the source line (SL) and bit line (BL), respectively. By applying SET voltage (VSET) to the bit line and connecting the source line to the ground, resistive device can be changed from HRS to LRS. This process is called as SET operation similarly RESET operation can be made by applying RESET voltage VRESET to the source line and connecting bit line to the ground [19]. All the conditions are summarized in Table 1.

4 RRAM: Fault Occurrence and Its Notation

The deviated behavior of particular write/read operation is called as a fault. It can be identified by basic two fault models (i) Fetching a sequence of operation to a specific memory function (ii) Observing Resultant behavior. The sequence which results in faulty behavior is called sensitizing sequence (S). Following faults can occur in 1T1R RRAM. If the fault f is observed within the memory element by applying the sensitizing sequence (S), for example when S is applied to M1 by enabling write logic 1 and stuck at 0 is noted in M1 then it is called self-fault (SF). In controversy, if the sensitizing sequence ‘S’ is applied to a particular cell M1 and a fault is observed in another cell M2 then it is called as coupling fault (CF). Here M1 is aggressor cell and M2 is victim cell. During the doping process, the effect of over doping results in stuck at 1 fault (SA1). In the functional process, if the column or memristor is connected to Vdd SA1 occurs. This fault is manifested as <0/1>, here logic ‘1’ is the output when logic ‘0’ is expected output. When there is a lack of oxygen vacancies in memristor or due to an open circuit in row/column that will create stuck at 0 fault (SA0), here logic ‘0’ is the output when logic ‘1’ is expected output and it is denoted by <1/0>. Even there is a minimum increase in impurities that will lead to slow write 1fault (SW1). Similarly, the decrease in a deficiency in oxygen vacancies results in slow write 0 (SW0). Increase in length ‘L’ and shrink in the cross-sectional area ‘A’ results in deep-0 fault and if the length decrease with the increase in cross-sectional area deep-1 fault occurs. Undefined output occurs due to excessive doping and increases in cross-sectional length which leads to unknown read (UR), it is manifested as <-/x> . Based on the resistance all faults are occurring in RRAM, that may be high resistance or low resistance applied HRS and LRS. In order to make RRAM with a fault-free state, various test algorithms are introduced. Each algorithm will focus specifically some kind of faults. Based on the reason of fault occurrence the operation of RRAM testing algorithm is designed. The effectiveness of testing algorithms assessed by parameters like test time, test complexity and fault coverage. In order to improve the overall performance of RRAM some soft computing techniques are incorporated [7] some unique bias schemes are used to improve the power utilization and read margin [17].

5 Existing Testing Methodologies

5.1 March Algorithm

March algorithms are used in most of the memory testing schemes. Its write and read actions are done through unchangeable patterns that thoroughly checks the memory with a certain number of faults in series manner i.e., at a time one memory element can be tested. So large memristor based memories take protracted test time using this march testing algorithm. The conventional march test just detects the predictable faults like stuck-at fault 1, stuck-at fault 0, transition fault 1, transition fault 0, coupling faults and address decoder faults and the sequence of march test is given below.

The notations of the march algorithm are as follows:

- ↑::

-

Address sequence changes in ascending order

- ↓::

-

Address sequence changes in descending order

- ↕::

-

Address sequence can change either way

- r0::

-

Reading 0 from the particular memory cell

- r1::

-

Reading 1 from the particular memory cell

- w0::

-

Writing 0 to a particular memory cell

- w1::

-

Writing 1 to a particular memory cell

- M::

-

Memory element

5.2 Modified March Algorithm

Chen et al. [5] has developed a modified march algorithm in order to detect dynamic write disturbance fault (DWDF) and write disturbance fault (WDF). In this method for an N-bit memristor memory (1 + 2a + 2b) N write operations and 5N read operations are required where ‘a’ is the number of consecutive Write-1 and ‘b’ is the Write-0 operations.

5.3 Fast March Algorithm

Mozaffari et al. [8] has proposed fast march algorithm to reduce the time dominance created by w0 and r0. Here two new writes and read are used rather than time intense w0 and r0 that can be applied to sneak path testing [6] also, the proposed fast march test can trace out undefined state fault (USF) with 97% of reduced test time.

Here, fw0 denotes fast w0 and rR denotes fast r0 operations. Symbol ׀׀ denotes parallel operation.

5.4 March C-Algorithm

Since RRAM architecture is comparable to the traditional RAMs, the majority of the practical fault models frequently utilized for testing RAMs including the Transition Fault (TF), Address Decoder Fault (AF), Stuck-At Fault (SAF) and inter-word Coupling Fault (CF) are found to be helpful for testing RRAM. The March C- is a testing algorithm similar to March C with reduced complexity that detects the abovementioned faults in the RRAM array. But in RRAM ‘R1D’ fault will flip the cell data before the read operation that results in corrupted read data. It can be detected by the March C-test, however, it cannot be predicted accurately whether the activator of R1D fault is read operation or an earlier write operation. Hence, it simply defines the R1D as the fault that occurs after the read operation. So a read-1 operation is introduced in front of a random read-1 operation, which can be an individual element or one more read-1 operation in M3 (r1, w0) as shown in the two algorithms below:

5.5 March C* Algorithm

Chen et al. [4] has proposed March C*-1T1R algorithm for 1T1R RRAM that detects all known modeled faults. This method accomplishes 100% fault coverage with less test time for 4 MB HfO2 based RRAM.

6 Proposed Algorithm for RRAM Testing

Enhanced March C algorithm is introduced in this paper that detects most of the random faults. Due to the bidirectional flexibility of RRAM’s I-V characteristics read 1 fault, read 0 fault occurs, read 1 disturbance fault can be detected effectively by using the proposed algorithm. During the read operation or after that, there is a probabilistic occurrence of read disturbance fault. This modifies the value in the particular cell which is going to be read that will result in faulty read data. The confusion between whether the fault is due to a previous write operation or presence of read disturbance occurs here if the read value is 0 when 1 is the actual result than it is “Read 1 Disturbance” fault (R1D) which is kind of low resistance defect. Here a couple of read 1 operation is followed to detect such R1D fault. In order to ensure the presence of ‘1’ after the write ‘1’ operation in 1st march element, two repeated read ‘1’ operation is performed in 2nd march element which is proposed in march C* algorithm [4]. At the same time there is a probability of R1D fault after the write ‘1’ operation in 3rd march element also therefore in 4th march element two repeated read ‘1’ operation is performed to ensure the presence of ‘1’, so that R1D fault is detected fully by using such repeated read ‘1’ operation after write ‘1’ operation rather than making lengthy march sequence. It is effective when repeating the main march element for a particular fault detection that improves the diagnosing resolution that is the basic idea proposed here. Since the read operation is repeated for two times, the proposed algorithm is named as March C2RR.

Steps involved in the proposed algorithm:

-

Step 1:

Initially write ‘0’ operation is performed (Write ‘0’ operation is neglected since the RRAM is fabricated and initially fetched with 0 [4])

-

Step 2:

Corresponding read operation and write ‘1’ operation is performed

-

Step 3:

Equivalent read operation is repeated twice and write ‘0’ operation is also performed

-

Step 4:

Read ‘0’ operation is followed by write 1 operation

-

Step 5:

Again Equivalent read operation is repeated twice and write ‘1’ operation is also performed.

7 Fault Detection in 1T1R RRAM

Stuck-at 0 (SA0) faults are sensitized by write 1 operation and detected by read 1 operation. Here these faults are sensitized by R2, R3 in M2 or R5, R6 in M4. Stuck-at 1 (SA1) are sensitized by ‘write 0 operations’ and detected by ‘read 0 operations’. Here these faults are sensitized by R1 in M1, R4 in M3 and detected by M2 and M4.

Deep-0 faults are initialized by two write 0 operations that are sensitized by write 1 operation and detected by read 1 operation, as the memristor of 1T1R cross-bar goes through a forming process, where all the memristors are started into LRS and all 1T1R cells are in logic 0 states (Fig. 4).

After the forming process, initial write 0 operations are carried and M1 initializes the faults in the cross-bar as the second write 0 operations. M2 sensitizes the faults then the faults are detected by R2, R3 in M2 or R5, R6 in M4. Deep-1 faults are initialized by two write 1 operation, be sensitized by write 0 operations and detected by read 0 operations. M4 initializes the faults as the first write 1 operation. M5 initializes the faults as the second w1. M5 also sensitizes the faults. Deep-1/0 faults consist the characteristics of both Deep-1 and Deep-0 faults. Hence, the test method of either Deep-1 or Deep-0 is also effective in detecting these faults. Slow Write 0 (SW0) faults are initialized by write 1 operations, sensitized by write 0 operations, and detected by read 0 operations. M2 or M5 initializes the faults. M3 sensitizes the faults and it is detected by R4 in M4. Slow Write 1 (SW1) faults are initialized by write 0 operations, be sensitized by write 1 operation and detected by read 1 operation. M1 or M3 initializes the faults. M2 or M4 sensitizes the faults. Then, the faults can be detected by R2, R3 in M2 or R5, R6 in M5. Read 1 Disturbance (R1D) fault occurs during the read operation the data stored in a particular cell will be flipped to logic 0 from logic 1. This kind of faults can be sensitized by read 1 operation and detected by another succession of read 1operation. In the proposed March C2RR algorithm R3, R6 in M3 and R5, R6 in M4 detects the R1D faults.

8 Experimental Result

An 8-Mb RRAM with eight 1-Mb macros and each macro has 1,024 rows and 1,024 columns (with 512K words and 8 bits in each word) have been designed. March C2RR test is applied to the first macro and the test follows. The test time for RRAM is formulated by the set time, Tset, reset time, Treset, and read time, Tread as well. As a result, the test time complexity of the proposed March C2RR test algorithm is 2N.Treset + 2N.Tset + 6N.Tread (N is a number of addresses). Though the complexity of March C2RR algorithm is higher than fast march algorithm it is less than march algorithm and march C-algorithm. March C2RR has linear complexity, which is scalable with respect to the memory size (Table 2).

9 Conclusion

An HfO2 based 8 MB 1T1R RRAM is tested with various existing algorithms and the proposed march C2RR algorithm is designed to trace all the random faults and main focus in this work is directed to detect all the R1D faults which lead performance degradation. In the proposed march C2RR algorithm read operation is repeated twice in the second memory element and also in the fourth memory element (R3, R4 in M3 and R5, R6 in M4) 100% fault coverage is achieved by the proposed method that detects R1D faults and all the random faults effectively. In future, such proposed method of testing can be designed for all kinds of fault in RRAM.

References

Ielmini, D.: Resistive switching memories based on metal oxides: mechanisms, reliability, and scaling. Semicond. Sci. Technol. 31(6), 063002 (2016)

Lv, H., et al.: Evolution of conductive filament and its impact on reliability issues in oxide-electrolyte based resistive random access memory. Sci. Rep. 5, 7764 (2016)

Beckmann, K., Holt, J., Olin-Ammentorp, W., Alamgir, Z., Van Nostrand, J., Cady, N.C.: The effect of reactive ion etch (RIE) process conditions on ReRAM device performance. Semicond. Sci. Technol. 32(9), 095013 (2017)

Chen, C.Y.: RRAM defect modeling and failure analysis based on march test and a novel squeeze-search scheme. IEEE Trans. Comput. 64(1), 180–190 (2015)

Chen, Y.X., Li, J.F.: Fault modeling and testing of 1T1R memristor memories. In: 33rd VLSI Test Symposium (VTS), pp. 1–6. IEEE (2015)

Kannan, S., Rajendran, J., Karri, R., Sinanoglu, O.: Sneak-path testing of crossbar-based nonvolatile random access memories. IEEE Trans. Nanotechnol. 12(3), 413–426 (2013)

Sribhuvaneshwari, H.: A novel feed forward back propagation technique for online resistive random access memory testing. Int. J. Pure Appl. Math. 118(12), 13909–13915 (2018)

Mozaffari, S.N., Tragoudas, S., Haniotakis, T.: Fast march tests for defects in resistive memory. In: 2015 IEEE/ACM International Symposium on Nanoscale Architectures (NANOARCH), pp. 88–93. IEEE (2015)

The International Technology Roadmap for Semiconductors (2011). http://www.itrs.net/Links/2011ITRS/Home2011.htm

Strukov, D.B., Likharev, K.K.: Prospects for terabit-scale nanoelectronic memories. Nanotechnology 16(1), 137–148 (2004)

Likharev, K.K.: Hybrid CMOS/nanoelectronic circuits: opportunities and challenges. J. Nanoelectron. Optoelectron. 3(3), 203–230 (2008)

Mishra, M., Goldstein, S.C.: Defect tolerance at the end of the roadmap. In: Shukla, S.K., Bahar, R.I. (eds.) Nano, Quantum and Molecular Computing, pp. 73–108. Springer, Boston (2004). https://doi.org/10.1007/1-4020-8068-9_3

Chung, A., Deen, J., Lee, J.S., Meyyappan, M.: Nanoscale memory devices. Nanotechnology 21(41), 412001 (2010)

Fujisaki, Y.: Current status of nonvolatile semiconductor memory technology. Jpn. J. Appl. Phys. 49(10R), 100001 (2010)

Lai, Y.F., Chen, F., Zeng, Z.C., Lin, P., Cheng, S.Y., Yu, J.L.: Thermal stability and data retention of resistive random access memory with HfO x/ZnO double layers. Chin. Phys. B 26(8), 087305 (2017)

Sun, P., et al.: Thermal crosstalk in 3-dimensional RRAM crossbar array. Sci. Rep. 5, 13504 (2015)

Sun, W., Choi, S., Shin, H.: A new bias scheme for a low power consumption ReRAM crossbar array. Semicond. Sci. Technol. 31(8), 085009 (2016)

Wang, X.F., Zhao, H.M., Yang, Y., Ren, T.L.: Graphene resistive random memory - the promising memory device in next generation. Chin. Phys. B 26(3), 038501 (2017)

Xie, Y.: Emerging Memory Technologies Design, Architecture, and Applications. Springer, New York (2014). https://doi.org/10.1007/978-1-4419-9551-3

Waser, R., Aono, M.: Nanoionics-based resistive switching memories. Nat. Mater. 6(11), 833–840 (2007)

Walczyk, C., et al.: Impact of temperature on the resistive switching behavior of embedded HfO2-based RRAM devices. IEEE Trans. Electron Devices 58(9), 3124–3131 (2011)

Zangeneh, M., Joshi, A.: Design and optimization of nonvolatile multibit 1T1R resistive RAM. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 22(8), 1815–1828 (2014)

Zhang, K.: Embedded Memories for Nano-Scale VLSIs, 1st edn. Springer, New York (2009). https://doi.org/10.1007/978-0-387-88497-4

Micheloni, R., Campardo, G., Olivo, P.: Memories in Wireless Systems, 1st edn. Springer, Heidelberg (2008). https://doi.org/10.1007/978-3-540-79078-5

Mistry, K., et al.: A 45nm logic technology with high-k+ metal gate transistors, strained silicon, 9 Cu interconnect layers, 193nm dry patterning, and 100% Pb-free packaging. In: Electron Devices Meeting, IEDM 2007, pp. 247–250. IEEE (2007)

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2019 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Sribhuvaneshwari, H., Suthendran, K. (2019). A Novel March C2RR Algorithm for Nanoelectronic Resistive Random Access Memory (RRAM) Testing. In: Rajaram, S., Balamurugan, N., Gracia Nirmala Rani, D., Singh, V. (eds) VLSI Design and Test. VDAT 2018. Communications in Computer and Information Science, vol 892. Springer, Singapore. https://doi.org/10.1007/978-981-13-5950-7_48

Download citation

DOI: https://doi.org/10.1007/978-981-13-5950-7_48

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-13-5949-1

Online ISBN: 978-981-13-5950-7

eBook Packages: Computer ScienceComputer Science (R0)