Abstract

A low power all CMOS based smart temperature sensor is introduced without using any bandgap reference or any current/voltage analog-to-digital converter. With the intention of low cost, power and area consumption, the proposed temperature sensor operates in sub-threshold region generating a temperature dependent frequency from the proportional to absolute temperature current. A digital output is obtained from the temperature dependent frequency by using a 12-bit asynchronous counter. A temperature insensitive ring oscillator is designed used a reference clock signal in counter. The temperature sensor is implemented using 65 nm CMOS standard process and its operation is validated through post-layout simulation results, at a power supply of (0.5–1)-V. The sensor has an uncalibrated accuracy of +2.4/–2.1 °C for (–55 to 125) °C and a resolution of 0.28 °C for the same range. The power and area consumed by the sensor is 1.55 µW and 0.024 mm2 respectively.

Access provided by CONRICYT-eBooks. Download conference paper PDF

Similar content being viewed by others

Keywords

1 Introduction

Due to the progression in pervasive computing, internet of things (IoTs) and the increase in demand of portable and miniature electronic devices, demand of low-cost, high performance temperature sensor is increased. The aggressive scaling techniques and increased transistor integration results in amplified junction temperature gradient. These junction temperature variations affect the lifetime, performance and reliability of the electronic device by increasing the leakage power, timing issues, gate delay, self-heating and the overall cost [1]. Temperature sensors have become an important element in every system on chip (SoC), especially the on-chip temperature sensors, mostly because of their compactness, low cost, high performance and low power consumption. The low power consumption helps in mitigating the self-heating issues of these sensors. The on-chip temperature sensors are mostly used for thermal compensation and power consumption control in SoCs.

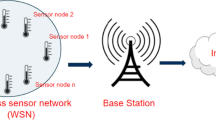

Different types of temperature sensors have been realized in CMOS technology. The conventional block diagram of sensor with its interface is shown in Fig. 1. A conventional temperature sensor is designed using bipolar junction transistors (BJTs) [2]. The BJT based temperature sensors measure the temperature by comparing the temperature independent voltage with a temperature dependent voltage. These two voltages are created using the characteristics of a vertical PNP voltage [3,4,5,6]. The ratio between the proportional to absolute temperature (PTAT) and the reference voltage is fed to an analog to digital converter (ADC) for digital output. The BJT based temperature sensors are able to achieve good resolution with high precision data converters, but result in more sensing errors. In order to mitigate the error, complex calibration techniques involving dynamic element matching (DEM) and chopping techniques are used making the output interface bulky and increasing the overall cost [2]. This resulted in tradeoff between sensing error, power consumption and sensor size. Moreover, the compatibility issue of BJT with CMOS technology increased the overall cost of the sensor. To overcome these issues, metal-oxide-semiconductor (MOS) based temperature sensors are introduced [7,8,9,10,11,12,13,14,15,16]. These sensors mostly exploit the thermal dependency of threshold voltage or leakage current of MOS devices. The output of MOS based sensors is usually temperature dependent current, voltage or frequency, with a typical accuracy of ±2 °C [2].

Conventional ADC and TDC based temperature sensor [2].

In this paper, a current-mode MOS based temperature sensor is introduced without using any BJTs. It employs a PTAT frequency generator, operating in sub-threshold region for low power operation, and a low power temperature insensitive ring oscillator (TIRO) used as a reference clock signal for counter. The output of both the temperature sensor and the TIRO is given to a 12-bit asynchronous counter for digital output. The sensor, realized in 65 nm CMOS standard process, results in high resolution, small size and power consumption and is compatible with common CMOS process. The temperature sensor results in an average temperature resolution of 0.28 °C over the military range (–55 °C to 125 °C) and has an uncalibrated inaccuracy of +2.4/–2.1 °C for the same temperature range.

The rest of the paper is organized as follows. Section 2 discusses the block diagram and working principle of the proposed temperature sensor followed by the operation of different sub-blocks. The operation of the sensor is validated through post-layout simulations in Sect. 3. Finally, Sect. 4 presents the conclusion.

2 Proposed CMOS Based Temperature Sensor

The block diagram of the proposed temperature sensor is shown in Fig. 2. The different blocks of the temperature senor are: A PTAT current generator, reference current generator, a temperature insensitive ring oscillator and a 12-bit asynchronous counter. The sensor employs the concept of current to frequency translation, where the proportional to absolute temperature current (\( I_{PTAT} \)) generates a temperature dependent frequency at the capacitor output. The frequency variation due to temperature is given to the counter and a digital output is achieved with respect to the clock frequency of ring oscillator An Enable switch is used to reduce the static power consumption.

2.1 Temperature Sensor Core

The schematic of the proposed temperature sensor is shown in Fig. 2. The reference current (\( I_{PTAT} \)) charges the capacitor (\( C_{S} \)) to voltage (\( V_{A} \)) with a slope of \( I_{PTAT} /C_{S} \), whereas the PTAT current (\( I_{PTAT} \)) discharges the \( C_{S} \) with a slope of \( I_{REF} /C_{S} \). The PTAT current generator operating in sub-threshold region is adopted from [10], where the switched capacitor circuit is replaced by a resistor and a startup-circuit is added. The rate of charging and discharging of \( C_{S} \) translates a varying waveform in time corresponding to temperature variations, as given by:

where \( V_{A,max} \) is the maximum value of \( V_{A} \) and \( V_{REF} \), \( C_{S} \), \( t_{r} \) and \( I_{REF} \) are considered as constants. Therefore, from Eq. (1):

where T is the temperature (°C). Moreover, from Eq. (1), the \( C_{S} \) has a negligible effect on the current charging and discharging as \( I_{PTAT} \, \times \,t_{r} = I_{REF} \, \times \,t_{f} \). Therefore, the accuracy of the temperature sensor is insensitive to capacitor variation. The clock signals CLKA, CLKB and RST are generated from the CLK signal. The RST is used as \( C_{S} \) reset signal. The timing diagram of all clock signals and the charging and discharging of \( C_{S} \) at different temperatures (T1, T2, T3 and T4) is shown in Fig. 3 and the operation is explained in Table 1. As the absolute temperature (T) and \( t_{f} \) have linear relationship, the output count-value of counter represents the absolute temperature.

2.2 Temperature Insensitive Ring Oscillator

The TIRO, adopted from [17], consists of five stages, where each stage composed of a bootstrap circuit and a driver stage. The schematic of TIRO is shown in Fig. 4. The transistors MP2 and MN2 are used as switches controlled by the input signal (VIN). The capacitors CBP and CBN behave as bootstrap circuit and are pre-charged by transistors MP1 and MN1, respectively. The INVN and INVP perform as drivers. To reduce the static power consumption, a NAND gate is employed at the first stage to prevent the unnecessary oscillations. The bootstrapped inverter gives an output swing of \( - \beta \,V_{DD} \) to 2 \( \beta \,V_{DD} \), where \( \beta \) is the boosting efficiency and \( V_{DD} \) is the power supply. The increase in the swing improves the driving capability of the transistors MP2 and MN2 and that of driver stage, so that a high frequency can be attained near the threshold voltage region. Besides the advantages highlighted in [17], this bootstrapped ring oscillator (BTRO) can be used as TIRO, if designed carefully. At a power supply approximately equal to the threshold voltage of MOS transistors, the BTRO operates in sub-threshold or linear region during the turned-on transient. Therefore, for one period of oscillations, the BTRO has two operating behaviors during the tuned-on transient operation. The period of BTRO remains invariant with temperature due to the opposite temperature behavior during the tuned-on transients.

5-stage TIRO [17].

The total delay (\( \tau_{total} \)) of a single stage TIRO is given as:

where \( \tau_{lin} \) and \( \tau_{sub} \) are the delay in linear and sub-threshold region, respectively. Considering, the current flowing in both the linear and sub-threshold region are equal, therefore the driving capability of both nMOS and pMOS transistors is same. Then, the \( \tau_{total} \) is given as:

where \( C_{dep} \) and \( C_{ox} \) are the depletion and oxide capacitors, \( \mu \) is the effective mobility,

\( {W \mathord{\left/ {\vphantom {W L}} \right. \kern-0pt} L} \) is the aspect ratio of the transistors and \( k_{f} \) is the fitting parameter.

2.3 Counter

The frequency signal generated from the temperature sensor converted into digital output through asynchronous counter. The TIRO is used as a reference signal for the counter. The size of the counter is chosen so that it does not overflows the countvalue, mostly at high temperatures. Although more bits can be added to the counter but it increases the static power and will also impact the dynamic power, as the most significant bit (MSB) switching activity is small. A 12-bit asynchronous counter is realized using JK flip-flops, AND gate and buffers, as shown in Fig. 5.

3 Post-layout Simulation Results

The proposed temperature sensor is realized in 65-nm CMOS process, at (0.5–1) V power supply, and its operation is validated through post-layout simulation results using Cadence IC617 environment. The total area consumed by the sensor (excluding the input/output pads) is 0.024 mm2, as shown in Fig. 6.

The variation of power consumption with respect to temperature (−55 °C to 125 °C) is shown in Fig. 7. The sensor consumes a power of 1.55 µW at room temperature. The variation of VPTAT with temperature is shown in Fig. 8. It is concluded that the slope of the VPTAT varies almost by 50% with rise in temperature.

The variation of the reference clock signal used at the counter with temperature is shown in Fig. 9. As can be seen, the TIRO has a frequency of 50 kHz at room temperature and varies within ±10% of the clock frequency over the defined temperature range.

The characteristic plot of asynchronous counter is shown in Fig. 10. The count value is taken with respect to a calibration table. As the results are based on post-layout simulation, the actual calibration issues weren’t dealt. The sensor has an uncalibrated accuracy of +2.4/–2.1 °C and a resolution of 0.28 °C. Then from the linear fitting curve for a value of R2 = 0.9978, the temperature value is translated from the count value as:

4 Conclusion

In this paper, a low power, frequency to temperature based CMOS smart temperature, operating in sub-threshold region for a temperature range of –55 °C to +125 °C, is introduced in 65-nm CMOS process. The proposed temperature sensor employs two current sources: ideal and proportional to absolute temperature. Based on the charging and discharging of capacitor due to these two current sources with temperature, a varying frequency is generated. A 12-bit asynchronous counter is used for analog-to-digital conversion. The counter uses a slow reference clock of 50 kHz, generated on chip by employing a five stage temperature insensitive ring oscillator. The overall temperature sensor consumes a power and area of 1.55 µW and 0.024 mm2, respectively. The sensor achieves a resolution of 0.28 °C and an uncalibrated accuracy of +2.4/–2.1 °C for a temperature range of –55 °C to +125 °C. To improve the resolution and accuracy of the temperature sensor, vernier time to digital converter or analog-to-digital converter and dynamic element techniques or autozeroing techniques can be employed (Table 2).

References

Bakker, A.: CMOS smart temperature sensors— an overview. In: 2002 Proceedings of the IEEE Sensors, vol. 2, pp. 1423–1427. IEEE (2002)

Pertijs, M.A.P., Huijsing, J.H.: Precision Temperature Sensors in CMOS Technology, 1st edn. Springer, Dordrecht (2006). https://doi.org/10.1007/1-4020-5258-8

Souri, K., Chae, Y., Makinwa, K.A.A.: A CMOS temperature sensor with a voltage- calibrated inaccuracy of ±0.15 °C (3σ) from −55 °C to 125 °C. IEEE J. Solid-State Circuits 48(1), 292–301 (2013)

Aita, L., Pertijs, M.A.P., Makinwa, K.A.A., Huijsing, J.H., Meijer, G.C.M.: Low-power CMOS smart temperature sensor with a batch-calibrated inaccuracy of ±0.25 °C (± 3σ) from −70 °C to 130 °C. IEEE Sens. J. 13(5), 1840–1848 (2013)

Sebastiano, F., Breems, L.J., Makinwa, K.A.A., Drago, S., Leenaerts, D.M.W., Nauta, B.: A 1.2-V 10-μW NPN-based temperature sensor in 65-nm CMOS with an inaccuracy of 0.2 °C (3σ) from −70 °C to 125 °C. IEEE J. Solid-State Circuits 45(12), 2591–2601 (2010)

Souri, K., Makinwa, K.A.A.: A 0.12 mm2 7.4 μW micropower temperature sensor with an inaccuracy of ±0.2 ℃ (3σ) from −30 ℃ to +125 ℃. IEEE J. Solid-State Circuits 46(7), 1693–1700 (2011)

Hwang, S., Koo, J., Kim, K., Lee, H., Kim, C.: A 0.008 mm2 500 μW 469 kS/s frequency- to-digital converter based CMOS temperature sensor with process variation compensation. IEEE Trans. Circuits Syst. I, Reg. Papers 60(9), 2241–2248 (2013)

Chen, P., Chen, S.C., Shen, Y.S., Peng, Y.J.: All-digital time-domain smart temperature sensor with an inter-batch inaccuracy of −0.7 °C/+ 0.6 °C after one-point calibration. IEEE Trans. Circuits Syst. I, Reg. Papers 58(5), 913–920 (2011)

Bashir, M., Sreehari Roa, P., KrishnaPrasad, K.S.R.: On-chip CMOS temperature sensor with current calibrated accuracy of −1.1 °C to +1.4 (3σ) from −20 °C to 150 °C. In: 19th International Symposium on VLSI Design and Test, pp. 1–5. IEEE, Ahmedabad (2015)

Bashir, M., Sreehari Roa, P., KrishnaPrasad, K.S.R.: An ultra-low power, 0.003mm2 area, voltage to frequency based smart temperature sensor for −55 °C to +125 °C with one-point calibration. Turkish. J. Electr. Eng. Comput. Sci. 25(4), 2995–3007 (2017)

Chen, C.C., Liu, W.J., Lin, S.H., Lin, C.C.: A CMOS oscillators-based smart temperature sensor for low-power low-cost systems. Procedia Eng. 47, 92–95 (2012). Elsevier

Chen, S.W., Chang, M.H., Hsieh W.C., Hwang, W.: Fully on-chip temperature, process, and voltage sensors. In: Proceedings of 2010 IEEE International Symposium on Circuits and Systems, pp. 897–900. IEEE, Paris (2010)

Mohamad, S., Tang, F., Amira, A., Bermak, A., Benammar, M.: A low power oscillator based temperature sensor for RFID applications. In: Proceedings of Fifth Asia Symposium on Quality Electronic Design, ASQED 2013, pp. 50–54. IEEE, Penang (2013)

Nebhen, J., Meillère, S., Masmoudi, M., Seguin, J.L., Barthelemy H., Aguir, K.: A temperature compensated CMOS ring oscillator for wireless sensing applications. In: Proceedings of 10th IEEE International NEWCAS Conference, pp. 37–40. IEEE, Montreal (2012)

Chen, C.C., Chen, H.W.: A low-cost CMOS smart temperature sensor using a thermal-sensing and pulse-shrinking delay line. IEEE Sens. J. 14(1), 278–284 (2014)

Kim, K., Lee, H., Kim, C.: 366-Ks/s 1.09-nJ 0.0013-mm2 frequency-to-digital converter based CMOS temperature sensor utilizing multiphase clock. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 20(12), 1–5 (2012)

Ho, Y., Yang, Y.S., Su, C.: A 0.2–0.6 V ring oscillator design using bootstrap technique. In: Proceedings of Asian Solid-State Circuits Conference (ASSCC) on Digital Technology Papers, pp. 333–336. IEEE, Jeju (2011)

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2017 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Bashir, M., Patri, S., Krishna Prasad, K.S.R. (2017). A Low Power, Frequency-to-Digital Converter CMOS Based Temperature Sensor in 65 nm Process. In: Kaushik, B., Dasgupta, S., Singh, V. (eds) VLSI Design and Test. VDAT 2017. Communications in Computer and Information Science, vol 711. Springer, Singapore. https://doi.org/10.1007/978-981-10-7470-7_62

Download citation

DOI: https://doi.org/10.1007/978-981-10-7470-7_62

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-10-7469-1

Online ISBN: 978-981-10-7470-7

eBook Packages: Computer ScienceComputer Science (R0)