Abstract

High noise margins and low power dissipation are the major attributes of the SRAM cells used in ultra-low power applications. This paper proposes a 10T Static Random-Access memory (SRAM) with data aware dynamic feedback control and disturb free read which enhances the noise margins in the sub-threshold region. Exploiting the dynamic threshold MOS transistors (DTMOS) technique reduces the read access time of the proposed memory cell. As this cell offers single ended write operation with the bitlines kept at logic HIGH which leads to large saving in dynamic power due to charging/discharging operation on bitlines. Therefore, proposed SRAM reduces the activity factor of discharging the bitlines for each write pattern. The simulation has been carried out in 65 nm technology node to show the comparison among the existing techniques and proposed cell. The proposed memory cell has write static noise margin (WSNM) of 1.7x and 1.48x compared to iso-area 6T and Schmitt Trigger based (ST2) SRAM cells respectively at supply voltage of 300 mV. Read operation is data controlled which improves the read margin. Dynamic threshold technique increases read current for faster read operation. Read SNM is 2x, 1.16x and 1.4x of iso-area 6T, differential data aware 9T and Schmitt trigger SRAM (ST2) respectively. These features enable the cell for ultralow power applications.

Access provided by CONRICYT-eBooks. Download conference paper PDF

Similar content being viewed by others

Keywords

1 Introduction

Memory occupies major portion of chip area. It is anticipated that the memory area will increase further in future version of mobile electronic devices, high-end processor and microcontrollers. In order to increase the battery life of mobile devices, low power memory design is essential. Operating the memory in the sub-threshold region of the transistor can lead to significant reduction of power consumption due to the reduction of dynamic power, gate leakage and standby current of the design. Hence, sub-threshold memory is one of the viable option to achieve low power dissipation. Quadratic reduction in dynamic power and linear reduction in leakage power with respect to supply voltage can be achieved in subthreshold memory cell [1]. As reported in [2], 60% of the dynamic power in memory is due to the charging and discharging of the bitlines during write operation. Reducing this dynamic power consumption will significantly improve the battery life of mobile devices.

In the subthreshold region, the data stability of memory cell is severely affected due to (1) the reduction in on-current to off-current ratio (Ion/Ioff), (2) local threshold voltage variation and (3) reduction in supply voltage [3]. The traditional 6T Static Random-Access Memory (SRAM) cannot behave properly under such stringent constraints. Several read and write assist techniques have been proposed to improve read and write stability of 6T SRAM which include virtual-ground (CVSS) bias [4, 5], differential CVSS [6], boosted [7] or reduced wordline voltage [7], dual supply scheme [8, 7], and write back schemes [4]. Even with these techniques, the Vmin (minimum operating voltage) of 6T SRAM lies in the range of 0.45 V to 0.7 V.

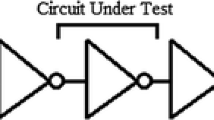

Several architectures have been proposed in recent years that aim to increase the write and read stability by increasing number of transistors used by making one or more design modifications. Breaking the feedback between the inverters during write/read stage increase write/read stability as in 7T [9] and 7T [10] cells. However, the stability depends on the transistor that controls the feedback loop. Due to the impact of process variation, feedback may fail to work which leads to marginal benefit in cell stability. 8T [11] isolates storage nodes from the bitlines by inserting buffer between bitlines and storage nodes which improves read stability. However, the write margin remains low and read access delay is increased. The half select stability failure is one of the major issues of that work.

Several techniques to save dynamic write power have been proposed that includes reducing the voltage swing of bitlines and capacitance [12, 13]. In [13], extra logic circuitry in row decoder and DC-to-DC converters are used to precharge and discharge the bitlines which leads to increase in area, reduction in speed and noise margins. Reducing the capacitance of bitlines and wordlines and datalines leads to saving in dynamic write power of the SRAM cell.

In this paper, a new 10T subthreshold SRAM cell is proposed that provides high noise margins and reduced dynamic power dissipation without extra logic circuitry. The major contributions of the paper are as follows:

-

The proposed 10T cell reduces the activity factor of SRAM cell to almost ‘0’ during write operation by keeping both the bitlines at logic high value for write operations. The data to be written is managed by WBL and WBLB control signals.

-

Read operation is disturb free by isolating storage nodes from bitlines. DTMOS (Dynamic threshold MOS) technique [14] in read operation reduces threshold voltage for faster read operation.

-

As the read and write access transistors are different. They can be sized efficiently to improve the read and write SNMs.

-

Leakage current is reduced due to stacking of pull down transistors in read and hold state. Symmetric structure offers symmetric layout and lower mismatch.

-

Half select issue arising due to BL and BLB is reduced.

2 Proposed 10T SRAM Cell Design

To achieve higher noise margins and minimum dynamic power consumption, a 10T SRAM cell is designed as shown in Fig. 1. The transistors M7, M8, M9 and M10 have been added to the conventional 6T cell. The transistor M11 is common to all the SRAM cells in a row. The transistors M1–M5–M7 and M2–M6–M8 form two cross coupled inverter pairs. The transistors M3, M4 and M9, M10 act as access transistors for the write and read operations respectively. The symmetric layout structure is drawn to reduce the impact of local process variations. The structure uses the LE and RE signals to control the transistors M7 and M8 which breaks the feedback between inverters using dynamic feedback control. It increases the write margin. RWL and WBL, WBLB signals control the read and write operations respectively. The write operation in the cell exploits write assist dynamic feedback control technique. Even there are two bit-lines, the write operation is functionally single ended. The bit-lines are kept at high value during both write ‘0’ and write ‘1’operations. M9 and M10 work as switches, only one of them is on during one write operation transferring data to adjacent node and other node value is changed due to inverting operation of another inverter attached to that node. Since bit-line values are never changed and write operation is controlled by switches according to the data to be written power consumed in switching bitlines is fully saved. Read operation is differential and controlled by data stored. Hence read is disturb free leading to higher read margin equivalent to hold margin. The status of the control signals is shown in Table 1.

2.1 Write Operation

Unlike the conventional SRAM cells, both the bit-lines BL and BLB are kept high during write operation. In contrast to general writing pattern of SRAM, where data to be written is controlled by values on BL and BLB, it is controlled by control signals WBL and WBLB in this proposed SRAM cell. The write operation in the proposed SRAM cell is single ended that is one access transistor is used to write desired value and other one is OFF.

For writing ‘1’ to the SRAM cell, RWL is made logic low which switches off M11. BL and BLB are kept logic high. WBL is kept at logic high which makes M3 ON. WBLB is kept at logic low which turns M4 off such that write operation becomes single ended. To make the feedback loop cutoff to help in write operation, Data Aware Dynamic Feedback Control write assist technique is employed. For write ‘1’, M7 is turned off and M8 is turned ON using LE = 0 V and RE = V DD . Since M7 is turned OFF, feedback loop of the cross-coupled inverter pair is cut-off. There is no pull down path connecting node Q to ground to help it maintain its value. It is now directly connected to BL through M3. Thus, BL generates a high voltage bump at node Q, which leads to change its value to ‘1’ with significant increase in write margin. With Q changing its value, the inverter (M2–M8–M6) connected directly at Q changes the value at QB to ‘0’. As M1 source is connected to V DD , pull up speed at Q is high in this case as compared to conventional CVDD write assist technique. Write ‘1’ to the cell is shown in Fig. 2(a). Similarly, the procedure of writing ‘0’ is shown in Fig. 2(b).

2.2 Read Operation

Read operation is performed by precharging BL and BLB and turning control signals RWL to logic high and WBLB, WBL to logic low. During the read operation M7 and M8 are ON by activating the RE and LE signals, leading to strong cross coupled inverter. The storage nodes Q and QB are isolated from bitlines completely which leads to disturb-free read operation. This decoupling action helps in increasing the SNM as disturbance does not reach storage nodes Q and QB as shown in Fig. 3. Body terminal of M11 is connected to RWL making threshold voltage of M11 dynamic. When RWL is activated for read operation it decreases the threshold voltage and discharges the bitline quickly, making read operation faster than all the compared cells with a greater margin. Due to differential signals, design of sense amplifier is simple. As the read and write access transistors are different, the sizing of the access transistors can be performed to improve the read and write margins separately. Read margin is equivalent to hold margin.

2.3 Hold Operation

The transistors M7 and M8 are ON during hold mode. Both WBL, WBLB and RWL are switched OFF and two cross-coupled inverters form a strong feedback loop. The hold margin of proposed cell is slightly less compared to hold margin of 6T SRAM cell due to the stacking effect of pull-down NMOS transistors. On the other hand, due to stacking of transistors in pull down, leakage current is reduced in hold state (Fig. 4).

2.4 Half- Selected Cell Issue

When a write ‘0’ (‘1’) operation is performed on a SRAM cell, the voltage at storage node QB (Q) for row half selected cells will increase because there will be charge transfer from bitline BLB (BL). In the proposed SRAM cell, the storage node Q (QB) does not have driving path to bitline BL as M3 (M4) is turned OFF. Therefore, in the proposed design there are less chances of change in the value stored in the cell as compared to conventional techniques.

3 Simulation Results and Discussion

In this section, all the post layout simulation results are presented to confirm the functionality of proposed design. The simulations are done using 65 nm industrial technology node. The operating supply voltage and temperature for the simulations are 0.3 V and 27 °C respectively. To show effectiveness of proposed design, it is compared with 6T iso-area (6T upsized to match the layout area of proposed 10T), 9T [15], 10T [17] and ST2 [16]. Iso-area 6T is 3x upsized of its minimum required W/L ratios for 65 nm technology node. Area occupied by the layout of the proposed design is 3.216 µm2 as shown in Fig. 1(b).

3.1 Write Ability

The WL voltage is used to assess write ability. In this case, the WL voltage is swept from zero to V DD to find the minimum voltage at which the bit cell is written (Q and QB flip) and is called wordline write margin(WVWL). If the value of WVWL is less, then it is easier to write on the bit cell. The write failure criteria is defined as WVWL ≥ V DD . Write failure occurs at V DD , hence margin is given by V DD -WVWL and is denoted as WVWL write margin. Write ability is also assessed using Write Static Noise Margin (WSNM) calculated using butterfly curve.

In iso-area 6T and ST2, there is fight between access and pull down transistor. But in proposed 10T, during write 1 operation, we turn off M7 that breaks the feedback loop and no direct path is now for Q node to ground. There is no fight between access and pull down transistor. There is undisturbed charging of Q node through WBL. The write margin is slightly lower than 9T and 10T as write operation is single ended. In 9T, write operation is differential. It is a small tradeoff for dynamic write power saved in write operation of proposed 10T. WSNM of proposed 10T is 1.71x and 1.44x as compared with that of iso-area 6T and ST2 and 0.93x as compared to 9T and 10T.

3.2 Read Static Noise Margin

RSNM is defined as the maximum amount of voltage noise that a cell can tolerate in read configuration without flipping of Q and QB. RSNM is calculated by finding the largest square which fits inside the VTCs (butterfly curves). Read noise margin are equivalent to hold noise margin as read is decoupled and disturb free as noise does not reach internal storage nodes. In 9T and 10T, the internal nodes are float during read operation and data retention time is a factor to be considered but in proposed 10T read path bypasses the storage nodes Q and QB isolating them from bitlines completely during read operation. RSNM of proposed 10T is 2x better than 6T as here no voltage divider is formed between access and pull-down transistor.

3.3 Write and Read Access Time

TWA (write access time) is measured as the time required for writing ‘0’ to the storage node Q. It is difference of the time when WBLB is HIGH and the time when Q falls to 10% of its initial high value (i.e., 90% change). Similarly, TWA for writing ‘1’ to Q is calculated as the difference of the time when WBL is turned ON and the time when Q rises to 90% of its initial low value. This ensures correct write operation. Being single ended, it requires more write time for storage nodes compared to all the compared cells as all other cells follow differential write operation.

TRA (read access time or read delay) is measured as the difference of the time when RWL (WL) is turned ON and the time when one of the bitlines is discharged by 50 mV from its initial high value [16]. The 50-mV difference in voltage between the bitlines is sufficient to be spotted by a sense amplifier, thereby avoiding incorrect read operation of the data stored. The read access time for different configurations is shown in Table 2. The read access time of proposed 10T cell is less than 10T cell. Its read current is high compared to 10T cell as result of reduced threshold voltage due to use of DTMOS technique. It is less than 9T cell as it uses single ended read.

4 Conclusion

A 10T SRAM cell is proposed to improve read and write stability for subthreshold operation. This 10T cell employs a data-aware-feedback-cutting scheme to enlarge the write margin and the read-disturb free scheme with DTMOS technique. This proposed design is an ultra-low voltage SRAM cell. Its WSNM is 1.7x of the write margin of iso-area 6T cell. The WVWL margin of proposed 10T is higher than 10T, 6T (iso-area) and ST2. Write operation is functionally single ended and write control signals are data aware. As BL and BLB are always high, hence activity factor of switching the bitlines during write operation is minimal which reduces dynamic power dissipation during write operation. Design of write driver is also simple as same data is sent on both lines. RSNM is highest among all the cells under consideration. Read SNM is almost equal to hold SNM. Read access time is better than compared 9T and 10T. Due to different access transistors for read and write operation, there sizing can be done efficiently for higher margins. Proposed 10T SRAM cell in hold state has smaller leakage current due to stacking of pull down transistors. Hence the proposed cell has high read and write stability and can be operated at ultra-low voltage of 200–300 mV. The advantage of reduced dynamic power consumption enables it to be used in portable battery operated System-on-Chip (SoC) designs.

References

Rabaey, J.M., Chandrakasan, A., Nikolic, B.: Digital Integrated Circuits: A Design Perspective, 2nd edn. Prentice-Hall, New Delhi (2005)

Karandikar, A., Parhi, K.K.: Low power SRAM design using hierarchical divided bit-line approach. In: Proceedings of International Conference Computer Design, pp. 82–88 (1998)

Zhai, B., Hanson, S., Blaauw, D., Sylvester, D.: A variation-tolerant sub-200 mV 6-T subthreshold SRAM. IEEE J. Solid-State Circuits of 43(10), 2338–2348 (2008)

Pilo, H., Barwin, J., Braceras, G., Browning, C., Burns, S., Gabric, J., Lamphier, S., Miller, M., Roberts, A., Towler, F.: An SRAM design in 65 nm and 45 nm technology nodes featuring read and write-assist circuits to expand operating voltage. In: Symposium on VLSI Circuits, Digest of Technical Papers, pp. 15–16, June 2006

Bhavnagarwala, A., Kosonocky, S., Radens, C., Stawiasz, K., Mann, R., Ye, Q., Chin, K.: Fluctuation limits and scaling opportunities for CMOS SRAM cells. In: International Electron Devices Meeting (IEDM) Digest, pp. 659–662, December 2005

Suzuki, T., Yamauchi, H., Yamagami, Y., Satomi, K., Akamatsu, H.: A stable 2-port SRAM cell design against simultaneously read/write-disturbed accesses. IEEE J. Solid-State Circuits 43(9), 2109–2119 (2008)

Hirabayashi, O., Kawasumi, A., Suzuki, A., Takeyama, Y., Kushida, K., Sasaki, T., Katayama, A., Fukano, G., Fujimura, Y., Nakazato, T., Shizuki, Y., Kushiyama, N., Yabe, T.: A process-variation-tolerant dual-power-supply SRAM with 0.179 m cell in 40 nm CMOS using level-programmable wordline driver. In: IEEE Int. Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, pp. 458–459, February 2009

Zhang, K., Bhattacharya, U., Chen, Z., Hamzaoglu, F., Murray, D., Vallepalli, N., Wang, Y., Zheng, B., Bohr, M.: A 3-GHz 70-Mb SRAM in 65-nm CMOS technology with integrated column-based dynamic power supply. IEEE J. Solid-State Circuits 41(1), 146–151 (2006)

Bai, N., Wu, X., Yang, J., Shi, L.: A robust high density 7T SRAM bitcell for subthreshold applications. Chin. J. Electron. 20(2), 243–246 (2011)

Singh, J., Mathew, J., Pradhan, D.K., Mohanty, S.P.: A subthreshold single ended I/O SRAM cell design for nanometer CMOS technologies. In: 2008 IEEE International SOC Conference, 17–20 September 2008

Chang, M.-F., Wu, J.-J., Chen, K.-T., Chen, Y.-C., Chen, Y.-H., Lee, R., Liao, H.-J., Yamauchi, H.: A differential data-aware power-supplied (D-AP) 8T SRAM cell with expanded write/read stabilities for lower VDDmin applications. IEEE J. Solid-State Circuits 45(6), 1234–1245 (2010)

Yoshimoto, M.: A 64 kb CMOS RAM with divided word line structure. In: Technical Digest IEEE International Solid-State Circuits Conference, pp. 58–59 (1983)

Yang, B., Kim, L.: A low-power SRAM using hierarchical bit line and local sense amplifiers. IEEE J. Solid-State Circuits 40(6), 1366–1376 (2005)

Hwang, M.-E., Roy, K.: A 135 mV 0.13-μW process tolerant 6T subthreshold DTMOS SRAM in 90 nm technology. In: Proceedings IEEE Custom Integrated Circuits Conference, September 2008, pp. 419–422 (2008)

Chang, M.F., Chang, S.W., Chou, P.W., Wu, W.C.: A 130 mV SRAM with expanded write and read margins for subthreshold applications. IEEE J. Solid-State Circuits 46(2), 520–529 (2011)

Kulkarni, J.P., Roy, K.: Ultralow-voltage process-variation-tolerant Schmitt-trigger-based SRAM design. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 20(2), 319–332 (2012)

Hassanzadeh, S., Zamani, M., Hajsadeghi, K.: A 32 kb 90 nm 10T-cell sub-threshold SRAM with improved read and write SNM. In: Proceedings of 21st Iranian Conference Electrical Engineering (ICEE), May 2013, pp. 1–5 (2013)

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2017 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Swaati, Das, B.P. (2017). A 10T Subthreshold SRAM Cell with Minimal Bitline Switching for Ultra-Low Power Applications. In: Kaushik, B., Dasgupta, S., Singh, V. (eds) VLSI Design and Test. VDAT 2017. Communications in Computer and Information Science, vol 711. Springer, Singapore. https://doi.org/10.1007/978-981-10-7470-7_48

Download citation

DOI: https://doi.org/10.1007/978-981-10-7470-7_48

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-10-7469-1

Online ISBN: 978-981-10-7470-7

eBook Packages: Computer ScienceComputer Science (R0)