Abstract

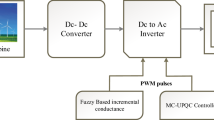

A fuzzy logic controller based multiconverter unified power quality conditioner (MC-UPQC) to enhance the power quality issues. This newly designed controller is connected to a source in order to compensate voltage and current in the two feeders. In the proposed system the power can be conveyed from one feeder to another in order to mitigate the voltage sag, swell, interruption and transient response of the system. The control strategies of MC-UPQC are designed based on the MSRF theory with Fuzzy logic controller. The transient response of the fuzzy logic controller in dc-link voltage controller will be very fast. The relevant simulation and compensation performance analysis of proposed MC-UPQC with fuzzy logic controller is performed.

Access provided by Autonomous University of Puebla. Download conference paper PDF

Similar content being viewed by others

Keywords

46.1 Introduction

An electrical power system consists of wide range of electrical and power electronic equipment in commercial and industrial applications. The quality of the power is effected by many factors like harmonic contamination, arc in arc furnace, sag and swells due to the increment of non-linear loads such as large thyristor power converters, power electronics devices, voltage and current flickering, arc in arc furnaces and switching of loads respectively which also affects the sensitive loads to be fed from the system. In lightning strikes on transmission lines, the switching of capacitor banks and various network faults can also cause PQ problems. In order to meet PQ standard limits, it is necessary to include some sort of compensation [1]. The solutions can be found in the form of active rectification or active filtering [2]. The Shunt active power filter is suitable for the suppression of negative load influence on the supply network, supply voltage imperfections, a series active power filter may be needed to provide full compensation [3–8].

In all the above mentioned techniques PI controller is used for designed UPQC. In order to regulate the dc-link capacitor voltage, a conventional PI controller is used to maintain the dc-link voltage at the reference value. The conventional UPQC is also modified; with the new control techniques based on Modified Synchronous Reference Frame theory (MSRF) to overcome the power quality problems such as voltage current unbalance, harmonics, reactive power compensation, voltage sag, swell and interruptions.

46.2 Proposed System Description

46.2.1 Circuit Configuration

The MC-UPQC line diagram of a distribution system is shown in Fig. 46.1; two feeders connected to two different substations supply the loads Linear load L1, non linear load L2. The MC-UPQC is connected to two buses BUS1 and BUS2 with voltages of u t1 and u t2 and load L1 and L2 with a current of i l1 and i l2. Sending end voltages are denoted by u s1 and u s2 while load voltages are u l1 and u l2. Finally, feeder currents are denoted by i s1 and i s2. The Bus voltages u t1 and u t2 are distorted and may be subjected to sag/swell.

46.3 Design of Shunt and Series VSCs

46.3.1 The Control Scheme of the Shunt VSC

When compared to conventional method [2], the designed system of shunt VSC gives the better compensating of harmonics, reactive components of feeder one load current as well as to regulate the common dc-link capacitor voltage.

The three phase load currents for feeder one is transformed into load synchronous reference currents using Eq. (46.1).

The fundamental direct axis component current is transferred into dc quantities using 2nd order LPF and it is added to the Fuzzy output to generate a new reference shunt feeder currents in Eqs. (46.3) and (46.4).

The direct component of the feeder current is subjected to load direct dc components and quadrature components of the feeder current is subjected to zero. The new reference shunt feeder currents in Eqs. (46.3) and (46.4) are transformed back to the abc reference currents.

The shunt currents are added to the abc reference frame currents and it is sensed by the relay to control the currents.

46.3.2 The Control Scheme of the Shunt VSC

The MSRF based control algorithm for the shunt VSC block is shown in Fig. 46.2. When compared to conventional method [2], the proposed system of series VSC’s gives the better compensation of voltage sag, swell and interruptions in feeder two alone. The series VSC block is based on the unit vector template by the new MSRF theory.

The three phase load voltages are transformed into load synchronous reference voltages using Eq. (46.6).

The expected load Synchronous reference dqo voltages is subtracted to the V l−dqo in Eq. (46.8) and its compensation reference feeder dqo voltages is transformed back to the synchronous reference feeder voltages using Eq. (46.9).

The output of the PWM generator compensation voltage is directly given to control part of series VSC.

46.4 Simulation Block Diagrams

The series VSC simulation control block diagram is shown in Fig. 46.3. In series VSC the measured load current is transformed into the synchronous dq0 reference frame by using Eq. 46.5. The reference current in (46.9) is then transformed back into the abc reference frame.

46.4.1 Design of Source Controller

The new source controller is designed using normal continuous sine wave. Changing the amplitude, angular frequency, phase sequence we can get the discrete sine wave form. The below Eqs. (46.10), (46.11), (46.12) shows the source of A, B, C for sine wave form.

Here Sw1 to Sw6 are the switches, t1 and t2 are the timer values, bias value is zero, phase degree is 120° phase shift. Using sample based sine wave type if numerical problems due to running for large time error. The simulation circuit diagram of pure sinusoidal supply voltage is shown in Fig. 46.4a and linear series transformer is shown in (b).

The load and source active and reactive powers are calculated without and with MC-UPQC is connected to system are shown in Table 46.1. The Simulation circuit diagram of Multi Converter-UPQC (MC-UPQC) is connected in a distribution system is shown in Fig. 46.5.

46.5 Simulation Results and Discussion

The simulation results of MC-UPQC are shown in below figures. In this section, calculating sag/swell, Harmonic for bus1, bus2, load side, source side in feeder1 and 2.

46.5.1 The Bus Voltage on Distortion and Sag/Swell

The BUS1 voltage contains 37.50 % sag between 0.1–0.2 s and swells 134 % between 0.2–0.3 s. The BUS2 voltage contains 34 % sag between 0.15–0.2 s and swells 130 % between 0.25–0.3 s.

The MC–UPQC is switched on at t = 0.02 s. The BUS1 voltage and harmonic spectrum are shown Fig. 46.6, the corresponding compensation voltage injected by VSC1 is shown in Fig. 46.7a and load L1 voltage are shown in Fig. 46.7b. The distorted voltages of BUS1 and BUS2 are satisfactorily compensated for across the loads L1 and L2 with very good dynamic response. Similarly, the BUS2 voltage are shown in Fig. 46.8, corresponding compensation voltage injected by VSC3 is shown in Fig. 46.9a and the load L2 voltage are shown in Fig. 46.9b. Feeder1 current are shown in Fig. 46.10a. The distorted nonlinear load current is compensated and the THD of the feeder current is reduced from 14.68 to 3.49 % is shown in Fig. 46.10b. THD values for without and with MC-UPQC are shown in Table 46.2.

46.6 Conclusion

The design of a new source controller and Multi-Converter Unified Power Quality Conditioner (MC-UPQC) connected to 3P3 W system has been presented in this paper. By using FLC with MC-UPQC dc-link voltage controller it is observed that transient response is attained very fast. The distorted Non-linear load current is compensated very well. The harmonic components and unbalance of bus1 voltage are compensated for by injecting the proper series voltage.

References

Mohammadi HR, Varjani AY, Mokhtaria H (2009) Muti converter unified power-quality conditioning system: MC-UPQC. IEEE Trans Power Deliv 24(3):1679–1686

Babu PC, Dash SS (2012) Design of unified power quality conditioner (UPQC) to improve the power quality problems by using P-Q Theory. In: Proceedings of 2012 IEEE international conference on computer communication and informatics, ICCCI 2012, vol 3, no 1, pp 1–7, Jan 2012

Mokhtatpour A, Shayanfar HA (2011) Power quality compensation as well as power flow control using of unified power quality conditioner. In: Power and energy engineering conference (APPEEC), 2011 Asia-Pacific, pp 1–4: 25–28 Mar 2011

Rajasekaran D, Dash SS, Vignesh P (2011) Mitigation of voltage sags and voltage swells by dynamic voltage restorer. IET Semin Dig 2011(2):36–40

Leela S, Dash SS (2013) Modelling and simulation of SVM based DVR system for voltage sag mitigation. Res J Appl Sci Eng Technol 6(23):4424–4431

Premalatha S, Dash SS, Babu PC Power quality improvement features for a distributed generation system using shunt active power filter. Procedia Eng 64: 265–274

Babu PC, Dash SS (2012) Design of unified power quality conditioner (UPQC) to improve the power quality problems by using P-Q theory. In: 2012 International conference on computer communication and informatics, Jan 2012, pp 1–7

Reddy UV, Babu PC, Dash SS (2013) Space vector pulse width modulation based DVR to mitigate voltage sag and swell. In: 2013 International conference on computer communication and informatics, Jan 2013, pp 1–5

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2015 Springer India

About this paper

Cite this paper

Babu, P.C., Dash, S.S., Subramani, C., Tejaswini, N., Sravan Kumar Reddy, Y. (2015). A Fuzzy Logic Controller Based Multi Converter UPQC to Enhance the Power Quality Problems. In: Kamalakannan, C., Suresh, L., Dash, S., Panigrahi, B. (eds) Power Electronics and Renewable Energy Systems. Lecture Notes in Electrical Engineering, vol 326. Springer, New Delhi. https://doi.org/10.1007/978-81-322-2119-7_46

Download citation

DOI: https://doi.org/10.1007/978-81-322-2119-7_46

Published:

Publisher Name: Springer, New Delhi

Print ISBN: 978-81-322-2118-0

Online ISBN: 978-81-322-2119-7

eBook Packages: EngineeringEngineering (R0)