Abstract

GaN-based heterojunction devices, in the form of high electron mobility transistors (HEMTs) and metal–insulator–semiconductor HEMTs (MIS-HEMTs), are capable of delivering superior performance in high-frequency power amplifiers and high-voltage power switches. Conventional Ga-face C-plane GaN-based heterostructures offer record-high 2DEG (two-dimensional electron gas) density without any intentional doping because of the strong intrinsic charge polarization. High-density 2DEG channel inevitably results in depletion-mode (D-mode) GaN transistors with negative threshold voltage (V th). However, enhancement-mode (E-mode) HEMTs are highly desirable for their inherent fail-safe operation and simple circuit configurations. The key to a feasible normally off HEMT technology is a post-epitaxy threshold voltage control technique that allows localized conversion from D-mode to E-mode or vice versa, since a high-performance E-mode HEMT requires a gate-controlled E-mode channel and D-mode regions (for low access resistance). Gate recess, p-type cap (AlGaN or GaN), and fluorine plasma ion implantation are the three commonly used approaches to fabricating normally off HEMTs. In this chapter, a comprehensive discussion on the underlying physical mechanisms of the fluorine implantation is presented, including atomistic simulation and experimental studies. Further development of the F-implant technique and its integration with other advanced techniques such as gate recess and AlN passivation is described. Finally, the robustness of the F-implant technique is further illustrated with the demonstration of various mixed-signal circuits fully integrated with GaN power devices.

Access provided by CONRICYT-eBooks. Download chapter PDF

Similar content being viewed by others

Keywords

12.1 Introduction: Fluorine in III-Nitride Heterostructures: Robust V th Control

The fluorine plasma ion implantation approach was discovered when large positive shift in V th was observed in AlGaN/GaN HEMTs as F ions were incorporated into the barrier layer by carbon tetrafluoride (CF4) plasma treatment, whose major role is identified as providing F ions with enough energy to penetrate into the subsurface layer of III-nitride epitaxial layers grown along the [0001] direction [1, 2]. The effectiveness of fluorine implantation technique in GaN and related compounds stems from the strong electronegativity of F element and the intrinsic III-nitride wurtzite crystal structure. In AlGaN/GaN heterostructures, because of the very tight lattice structure (with an in-plane lattice constant of a ~3.2 Å), the implanted F ions tend to be stabilized at the interstitial sites by the repulsive forces from the neighboring atoms (Al, Ga, or N). Since group-VII F has the strongest electronegativity among all the chemical elements, a single F ion at the interstitial site tends to capture a free electron and becomes a negative fixed charge. These negative fixed charges subsequently modulate the local potential and deplete the 2DEG in the channel, as shown in Fig. 12.1b. The amount of the V th shift can be robustly controlled by the implantation time, as shown in Fig. 12.2. The fluorine plasma implantation technique also leads to the first demonstration of E-mode GaN-on-Si HEMTs [3].

The RF plasma power is another parameter that needs to be adjusted during process optimization. While this power needs to exceed a lower bound (in the range of ~100–250 W depending on the specific plasma systems used) to introduce significant V th shift, it is preferred to keep this power as low as possible in order to minimize the plasma-induced lattice damages and the amount of F ions that can penetrate to the channel region. Annealing at 400 °C has been proven to be effective in removing majority of the plasma-induced damages. The nature of the ion implantation process, however, indicates that there is a small amount of F ions in the 2DEG channel, presenting themselves as impurities that could lead to slight mobility degradation. With process optimization, the 2DEG mobility degradation can be reduced to 10–20 %.

12.2 Physics Mechanism of Fluorine Implantation

12.2.1 Atomistic Modeling of F Plasma Ion Implantation

To provide a theoretical framework for understanding the physical mechanisms and developing a modeling tool for process design and optimization, it is necessary to develop an approach capable of predicting the ion or dopant distribution profiles and the effects of the ion–solid interactions.

Despite the high atomic densities of GaN and related compound, low-energy (0.1–1.0 keV) F ions are able to penetrate to a shallow depth in AlGaN/GaN heterostructures, partially as a result of the narrow opening channels along the [0001] GaN, as shown in Fig. 12.3. A molecular dynamics (MD) simulation framework [4] was established to study the F plasma implantation into III-nitride material system, because the MD simulation takes into account the ion–lattice interactions on an atomistic scale and includes lattice structure information that is absent in other more traditional implantation simulation tools such as Stopping and Range of Ions in Matter (SRIM) which are based on Monte Carlo method. The MD simulation also provides time and space evolution of atomic coordinates, resembling a real-time observation of the F ion implantation process.

The substrate structure under study is a standard C-plane AlGaN/GaN HEMT structure with a 20-nm AlGaN barrier layer. F− ions are implanted by CF4 plasma into the region under the gate. The regular wurtzite lattice structure is applied to model both AlGaN and GaN layers in the MD simulation. Because of its small thickness (20 nm), the AlGaN barrier is assumed to be strained without any lattice relaxation. Thus, the piezoelectric charge polarization and the slight variation in the vertical lattice constant, as a result of the strained AlGaN layer, are both considered in MD simulations. It was found that the charge polarization has negligible effect on the fluorine dopant profiles.

According to published results [5], F− and \({{{\text{CF}}_{3}}^{ + }}\) ions are the main ions existing in CF4 plasma. However, after CF4 plasma implantation, no obvious change has been observed in the carbon concentration according to SIMS (second ion mass spectroscopy) measurement and the detected carbons are already in presence in the as-grown sample. There are two possible causes for this phenomenon, (1) F− is much lighter than \({{{\text{CF}}_{3}}^{ + }}\), with a mass ratio of 9:33. With the same acceleration time determined by the RF signal applied across the two electrodes driving the plasma, majority of F− ions travel enough distance to reach the sample, which is located at the bottom electrode. On the contrary, only small fraction of \({{{\text{CF}}_{3}}^{ + }}\) can reach the sample surface before the electric field reverses its direction and pulls the ions away from the sample; (2) In the plasma system, the bottom electrode is grounded, and the top electrode is capacitively coupled to the RF source. Thus, a negative self-bias in the order of several hundreds of volts is induced at the top electrode, which attracts \({{{\text{CF}}_{3}}^{ + }}\) and pulls them away from the sample. It should be noticed that the absence of additional C atoms in the sample is preferred because C impurities present adverse effects to AlGaN/GaN HEMT [6].

With MD simulation, the 1-D profile of F ion in AlGaN/GaN heterostructure is calculated and plotted in Fig. 12.4, along with the experimental results measured by SIMS. The simulation results with a (100) Si substrate are also calculated as reference. Excellent agreement between simulation and measurement is obtained in the case of F ion in AlGaN/GaN heterostructure. It can be seen that F ion implantation in AlGaN/GaN could get a smaller full width at half maximum (FWHM) compared to Si. This can be explained by the higher density of Al0.3Ga0.7N (5.19 g/cm3) compared to Si (2.33 g/cm3).

In the region near the substrate surface, i.e., in the AlGaN layer, the F concentration exhibits a Gaussian-like profile. F ions can penetrate deeper into AlGaN/GaN heterojunction than (100) Si, despite higher atomic density in AlGaN/GaN, indicating a strong channeling effect for the F ions in III-nitride wurtzite lattice structure. From the top views of both III-nitride wurtzite lattice and (100) Si crystal structure, it can be seen that there are many channels available in GaN for incident fluorine ions to go through, while the cubic lattice of silicon does not provide these open channels in the direction of implantation.

2-D and 3-D F distribution profiles have been simulated, as shown in Fig. 12.5. The simulation tool considers F ions with all possible incident angles. It should be noted that the F ions penetrating into the AlGaN/GaN structure are capable of inducing vacancies along the implantation path. The long-term high-temperature (400 °C) annealing indicates no shift in V th [7], suggesting weak correlation between these vacancies and the threshold voltage.

12.2.2 Stability of F Ions in AlGaN/GaN Heterostructures

Unlike in Si or other compound semiconductors in which the F ions have shown rather poor thermal stability due to F’s small atomic size and large space in the interstitial regions of these materials [8, 9], much better thermal and electrical stabilities have been reported for F ions in AlGaN/GaN heterostructures [7, 10]. The F ions’ stability is revealed by the potential energy profiles of F ions in AlGaN/GaN, also calculated by MD simulation [11]. The three locally stable sites that can physically accommodate fluorine ions are (Fig. 12.6a): interstitial site I, substitutional group-III cation site S(III), and substitutional group-V anion site S(V). Since majority (>90 %) of the implanted F ions are initially located at the I sites after implantation, the potential energy profiles between an I site and these three possible nearby sites along the minimum energy path are calculated and shown in Fig. 12.6b.

a Top view of (0001) GaN with three possible sites that can accommodate fluorine ions. b The potential energy profiles from I, S(III) and S(V) sites to their nearest I site of fluorine ion in Al0.25Ga0.75N (open symbols) and GaN (solid symbols). The Al0.25Ga0.75N is strained and lattice matched to GaN

Several conclusions can be drawn from Fig. 12.6 as follows:

-

Interstitial F ions will be stabilized at the I site unless there is an S(III) site nearby.

-

An F ion exhibits higher potential energy at the S(V) site compared to an I site since the Ga atoms around an N vacancy provide strong repulsive force to F ions and also help prevent interstitial F ions from moving into N vacancies.

-

Around a Ga vacancy, the N atoms are smaller and the repulsive force to an F ion is significantly weaker. Thus, it is easier for an interstitial fluorine ion to move into a nearby Ga vacancy when available.

When there are no continuous S(III) vacancy chains, the F ions will be trapped at the S(III) sits, as depicted in Fig. 12.7. The thermal stability of F ions in GaN is highlighted in Fig. 12.8 and the F–Ga vacancy interactions are revealed by positron annihilation spectroscopy experiment, as shown in Fig. 12.9 [12].

Excellent thermal stability has been reported in F-implanted normally off GaN HEMTs as long as the ambient temperature does not exceed the limit of the gate metal (e.g., 500 °C for Ni) [7] or gate dielectric (>800 °C for SiNx). The stability of the gate metal or gate dielectric is critical since it provides the cover that prevents F ions from escaping through the surface under high-temperature thermal excitation. It is observed that F ions can be stable under high electric field stress as long as large number of defects and dislocations are not introduced, e.g., by the inverse piezoelectric effect.

12.2.3 Electron Binding Energy Around F Ions

To study the binding energy of electrons associated with F ions, photoconductivity measurements were conducted using a Xe lamp together with a monochromator. The photocurrents as a function of the excitation wavelength are plotted in Fig. 12.10. The photocurrent increases slowly as the wavelength decreases (photon energy increases) from 750 nm in both the F-implanted and unimplanted samples. As the wavelength falls below 670 nm (corresponding to a 1.85 eV photon energy), the F-implanted sample starts to exhibit a much higher increasing rate compared to the unimplanted sample, indicating activation of electrons from certain deep levels. Thus, the electron binding energy associated with the F ions in AlGaN/GaN is ~1.85 eV [13].

12.3 Fluorine-Implanted Enhancement-Mode GaN MIS-HEMTs

12.3.1 GaN MIS-HEMTs

Many of the early normally off GaN FETs are HEMT devices with Schottky gate, which has relatively small threshold voltage (<1 V) and small gate swing that is limited by the Schottky-gate forward turn-on voltage (e.g., <3 V). In power-switching applications, large positive threshold voltage (e.g., >3 V) and large gate swing (e.g., >10 V) are required to prevent the power switches from faulty turn-on by electromagnetic interference and to become compatible with the gate drive designs currently used for Si-based power transistors. MIS-HEMT (metal–insulator–semiconductor HEMT) with a gate dielectric inserted between the gate metal and group-III-nitride surface provides the capability of scaling up the threshold voltage and gate swing. Various dielectric materials (e.g., Al2O3, SiO2, and SiNx) have been employed to convert Schottky gate to MIS gate [14, 15]. A few reports have shown GaN E-mode devices with large gate swings [16]. Meanwhile, low current collapse, or low dynamic on-resistance (R on), is another indispensable requirement for achieving high-efficiency power conversion under high-voltage switching conditions, whereas effective device passivation still demands more effort [17].

Device Structure and Fabrication

The studied sample features a 21-nm barrier layer (with 2-nm GaN cap, 18 nm Al0.25Ga0.75N, and 1 nm AlN) and a 4-µm GaN buffer/transition layer, grown on a 4-inch p-type (111) Si substrate. The schematic cross section of a fabricated E-mode MIS-HEMT is shown in Fig. 12.11. An AlN/SiNx passivation stack structure was deposited with plasma-enhanced atomic layer deposition (PE-ALD) of 4 nm AlN and plasma-enhanced chemical vapor deposition (PECVD) of 50 nm SiNx in sequence [18]. Planar device electrical isolation was realized by standard fluorine ion implantation. The gate window was opened with low-power dry etching of the passivation stack. The gate region was then subjected to CF4 plasma at an RF power of 200 W for 250 s with photoresist as the plasma implantation mask. After removing photoresist and carrying out an ex situ surface cleaning process with remote NH3/Ar/N2 plasma at 300 °C in the PE-ALD system to effectively remove the detrimental Ga–O bonds at the surface [19], the second SiNx thin film of 17 nm thickness was immediately grown by PECVD and deployed as the gate insulator to reduce gate leakage. Gate electrode with 1-µm footprint and 0.5-µm overhang was formed with Ni/Au deposited upon the second SiNx.

Measurement Results and Analysis

Device characterization was carried out on devices with L GS = 1 µm, (W/L)G = 10 µm/1 µm, and L GD = 15 µm (unless otherwise specified). Figure 12.12 shows typical DC transfer and output characteristics of an MIS-HEMT. The threshold voltage Vth, determined by the linear extrapolation method (i.e., the gate bias intercept of the linear extrapolation of drain current at the point of peak transconductance), is extracted to be +3.6 and +1.2 V for the MIS-HEMTs and the Schottky-gate control HEMTs fabricated on the same wafer, respectively. The positive shift of V th in the MIS-HEMT is primarily a result of the reduced gate-to-channel capacitance by the insertion of the SiNx gate dielectric.

The trap density at SiNx/barrier interface is estimated to be ~3 × 1012 cm−2 using a pulsed I D–V GS measurement [20]. The device exhibits an ON/OFF current ratio of 4 × 109 and a drive current of 430 mA/mm. The gate leakage is effectively suppressed by the SiNx at positive gate bias, enabling a large gate swing of 14 V and a low R on of 9.8 Ω mm. The DC-specific R on is calculated to be 2.1 mΩ cm2, taking into account a 1.5 µm transfer length for each ohmic contact (i.e., source and drain) in active area calculation.

The off-state breakdown/leakage characteristics of an MIS-HEMT are shown in Fig. 12.13. Gate and source electrodes are biased at 0 V and the substrate is grounded. It can be observed that the leakage current is mainly originated from the source injection current at a drain bias V DS up to 450 V, when the off-state gate leakage has been substantially suppressed by the gate insulator SiNx. When V DS continues to increase, the gate leakage and vertical substrate leakage will both increase to be comparable to the source injection current as V DS approaches 600 V. The breakdown voltage (BV), defined as the drain bias at a drain leakage current of 1 µA/mm, is measured to be 604 V.

Current collapse evaluation is performed using AMCAD-pulsed I–V measurement system. Figure 12.14a shows the pulsed I D–V DS characteristics of a normally off device with L GS = 1 µm, (W/L)G = 2 × 50 µm/1 µm, and L GD = 10 µm. The quiescent bias point is set at (V GSQ, V DSQ) = (0 V, 60 V). The pulse width and pulse period are 500 ns and 1 ms, respectively. The DC output curves are plotted for reference. Effective suppression of current collapse by AlN/SiNx passivation is demonstrated with little difference between the DC and pulsed drain current in the linear region. The elimination of self-heating effect is believed to be the reason for the higher drain current obtained in the pulsed I–V measurement. For high-voltage switching measurement, a slow-switching on-wafer testing was conducted using Agilent B1505A power device analyzer/curve tracer. After a high drain bias stress in the off-state with V GS = 0 V, the device is turned on when the dynamic R on is measured at V GS = 12 V and V DS = 1.5 V with a transient on-state current of ~ 100 mA/mm, as shown in Fig. 12.14b. The off-to-on switching time is 0.1 s when the drain stress voltage V DS is lower than 200 V and 2.7 s when V DS is higher than 200 V. The device has slight dynamic R on degradation of only 76 % for an off-state drain bias stress of 650 V.

12.3.2 GaN MIS-HEMTs with Partially Recessed Fluorine-Implanted Barrier

For the GaN transistors with metal–insulator–semiconductor (MIS) structure, their high-temperature stability can be hindered by the challenges of V th instability originating from the thermal electron emission of trap states at the dielectric/III-N interface [21, 22]. To address this issue, a thinned barrier layer is proposed to bring the deep interface traps below the Fermi level at pinch-off so that they become inactive [22]. In this work, the normally off MIS-HEMTs featuring a partially recessed (Al)GaN barrier were realized by a fluorine plasma implantation/etch technique. The partially recessed barrier leads to improved thermal stability, while the fluorine implantation can convert the device from D-mode to E-mode without completely removing the barrier and sacrificing the high mobility heterojunction channel [1].

Device Fabrication

The schematic cross section of the normally off MIS-HEMT is shown in Fig. 12.15. Both the fluorine ion implantation and gate recess were carried out using CF4 plasma [23]. By properly adjusting the power level of the RF source driving the fluorine plasma, we are able to obtain two desirable results: (1) a well-controlled slow dry etching for gate recess; and (2) effective shallow implantation of fluorine ions into the AlGaN barrier. Fluorine plasma implantation at a higher RF power level of 200 W resulted in a well-controlled slow-etching process with an etching rate of 2 nm/min. Meanwhile, a lower RF power of 150 W only induced insignificant etching of the barrier layer [1]. After 6 min of F-implantation/etch, a recess depth of ~12 nm and a smooth etched surface were obtained. After removing another 2 nm AlGaN by a digital etching [24], 20 nm Al2O3 was deposited by ALD with an in situ nitridation process [19].

Results and Discussion

The partially recessed F-implanted E-mode MIS-HEMT exhibits a threshold voltage (V th) of +0.6 V at a drain current of 10 μA/mm, a maximum drive current of 730 mA/mm, an on-resistance of 7.07 Ω mm (Fig. 12.16), and a hysteresis of ~ 0.3 V between the up- and down-V GS-sweep with a relatively fast sweeping rate (0.7 V/s).

The temperature (T)-dependent transfer and output characteristics of an MIS-HEMT were characterized (Fig. 12.17). When temperature increases from 25 to 200 °C, an increase in 3 orders of magnitude is observed in the OFF-state drain leakage due to increased buffer leakage, while the drain current exhibits an decrease (e.g., from 240 mA/mm to 200 mA/mm at V GS = 4 V). By using a current criteria of I DS of 10 μA/mm, V th shifted by 0.5 V toward negative direction when T increased from 25 to 200 °C.

According to a recent report [22], the thermally stable V th of MIS-HEMTs with recessed gate is mainly attributed to the thin barrier thickness (Fig. 12.18a). As shown in figure inset, the V th shift with temperature increasing from 25 to 200 °C depends on the barrier layer thickness (t BR). As t BR is reduced, the thermally induced V th shift can be significantly suppressed. The recessed barrier buries the deep interface traps below the Fermi level at pinch-off (i.e., ΔE 3 < ΔE 2 < ΔE 1) so that they become inactive and do not participate in the thermally sensitive emission (Fig. 12.18b). Stable charge states of the interface traps would lead to more stable V th.

a T-dependence of threshold voltage of GaN MIS-HEMTs with various barrier thicknesses and with/without fluorine (F) implantation. b Simulated band diagram of MIS-HEMT structure in this work (red) at pinch-off situation, compared with MIS-HEMTs with thicker barrier layer. The band diagrams are simulated using a 1D Poisson/Schrödinger equation solver. A uniform fluorine concentration (yielding a sheet density of 1 × 1013/cm2) in the AlGaN barrier was used in the simulation for the purpose of simple illustration

12.3.3 GaN Smart Power ICs

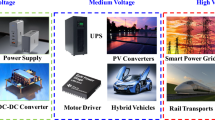

Although the current focus of GaN power device technologies is on discrete power devices, higher level integration of GaN power electronics could lead to many application-relevant benefits including reduced cost and improved reliability. In a more complete power converter module, besides the core power components (i.e., switches and rectifiers), intelligent control units are also needed to achieve precise adjustment of the output signal under different loading conditions, as shown in Fig. 12.19. Ultimately, robust sensing and protection units should be integrated to realize full-range protections against extreme operating conditions such as over-temperature, over-current, and over-voltage. It is thus desirable to develop highly integrated GaN power electronics technology with which we can implement on-chip power conditioning/protection circuits that promise to provide optimized performance, increased functionality, and enhanced reliability.

Platforms for Heterogeneous Integration

A smart power IC technology requires a platform on which both high-voltage components and low-voltage periphery devices can be integrated (Fig. 12.20) [25, 26]. The high-voltage switches prefer normally off transistors for their inherent fail-safe operation. For digital IC development, the mainstream CMOS-like architecture may have intrinsic difficulties in GaN materials due to the inferior hole mobility. The analog IC development using AlGaN/GaN has started recently.

Based on the robust fluorine plasma ion implantation technique, several key smart power components including high-voltage normally off transistors and lateral field-effect rectifiers [27, 28] have been developed. A smart power chip technology also requires low-voltage peripheral devices for the implementation of digital and analog blocks. Due to the lack of high-performance p-channel GaN devices, the simplest circuit configuration for GaN digital circuits is the direct-coupled FET logic (DCFL) that requires both the E-mode and D-mode n-channel HEMTs [29]. The Schottky diodes and L-FERs all exhibits graceful temperature dependences that can be explored for temperature sensing and compensation.

Lateral Field-Effect Rectifier (L-FER)

Analog circuits typically require diodes in additional to transistors. With the III-N heterostructures, diodes can be realized with three approaches including the lateral field-effect rectifier (L-FER) [27], the simple Schottky barrier diode (SBD) on heterostructures, or the lateral SBD with the Schottky junction to the 2DEG channel made from the sideway [30]. The forward and reverse characteristics of an L-FER with the anode–cathode drift region length L D of 10 µm are plotted in Fig. 12.21. The knee voltage V k, defined as the anode bias at a forward current of 1 mA/mm, is 0.1 V in the proposed L-FER. Figure 12.22 shows the forward I–V curves of L-FER and SBD at varied operating temperature. It is seen that the current of L-FER exhibits a negative temperature coefficient because its conduction current is dominated by phonon scattering. For the SBD directly fabricated on the heterostructure, the thermionic emission dominates the forward current at forward bias smaller than 1 V, and thus, its forward current has a positive temperature coefficient.

GaN Mixed-Signal ICs Based on Monolithic Integration of E/D-Mode HEMTs

Based on the fluorine implantation technique, monolithic integration of E/D-mode HEMTs has been demonstrated [29]. A 17-stage ring oscillator has been shown to operate properly, even at 375 °C [31]. Various mixed-signal GaN ICs have been demonstrated including a voltage reference [32], a bootstrapped comparator [33], a 2-bit quantizer and flip-flop [34], a temperature sensor [35], and a self-startup circuit [36].

The first GaN-based PWM circuit using monolithically integrated E/D-mode HEMTs and L-FERs [37] is illustrated in Fig. 12.23. The circuit is able to generate 1 MHz PWM signal with its duty cycle modulated linearly over a wide range.

a Block diagram of the GaN-based PWM IC. Three off-chip passive components are used (marked in red line) for the sawtooth generator. V c is the reference voltage sampled from the converter output. b Scanning electron microscope (SEM) picture of the adjacent dies (left sawtooth generator; right PWM comparator). The GaN-on-Si chip is wire-bonded and mounted onto a PCB which also houses three off-chip passive components

The GaN-based pulse width modulator incorporates two functional blocks, i.e., a sawtooth generator and a comparator. The sawtooth generator produces a sawtooth signal (V saw) and the comparator (referred to as the PWM comparator) produces the PWM signal (V PWM) by comparing the reference voltage (V c) sampled from the converter output against the sawtooth signal (V saw). The pulse width of V PWM is modulated by V c, and its frequency is determined by that of V saw. Circuit performances up to 1 MHz are investigated with a 5 V supply voltage. The generated sawtooth signal (V saw) is injected into the PWM comparator and compared against V c, yielding a PWM signal with its duty cycle modulated by V c. Figure 12.24 shows the PWM waveforms when the circuit is operated at ~1.08 MHz. The pulse width of the PWM signal can be modulated over a wide range (by varying V c from 1.3 to 2.0 V with V saw oscillating between 0.89 and 2.18 V).

12.4 Conclusions

Fluorine implantation, in particular the low-energy implantation using plasma tools, is shown to be able to locally incorporate negatively charged F ions into AlGaN/GaN heterojunctions. These negative fixed charges provide robust and flexible means of adjusting the threshold voltage in the 2DEG channel, enabling the realization of E-mode GaN HEMT and MIS-HEMTs on D-mode HEMT platform. Atomistic modeling based on molecular dynamics simulation reveals that F ions can be reasonably implanted into AlGaN/GaN heterojunctions assisted by the channeling effect of the (0001) C-plane AlGaN/GaN, but can be stably confined within the crystal because of the tight lattice structure of GaN and related compounds. The fluorine implantation technique offers robustness and flexibility in delivering GaN power components (transistors and rectifiers) and peripheral mixed-signal functional blocks on the same technology platform for the ultimate GaN system-on-a-chip solutions for various applications smart power amplifiers and smart power converters.

References

Cai Y, Zhou Y, Chen KJ, Lau KM (2005) High-performance enhancement-mode AlGaN/GaN HEMTs using fluoride-based plasma treatment. IEEE Electron Device Lett 26:435

Cai Y, Zhou Y, Lau KM, Chen KJ (2006) Control of threshold voltage of AlGaN/GaN HEMTs by fluoride-based plasma treatment: from depletion mode to enhancemend mode. IEEE Trans Electron Devices 53:2207

Jia S, Cai Y, Wang D, Zhang B, Lau KM, Chen KJ (2006) Enhancement-mode AlGaN/GaN HEMTs on silicon substrate. IEEE TransElectron Devices 53:1477

Yuan L, Wang MJ, Chen KJ (2008) Fluorine plasma ion implantation in AlGaN/GaN heterostructures: a molecular dynamics simulation study. Appl Phys Lett 92:102109

Segawa S, Kurihara M, Nakano N, Makabe T (1999) Dependence of driving frequency on capacitively coupled plasma in CF4. Jpn J Appl Phys 38:4416

Klein PB, Binari SC, Ikossi K, Wickenden AE, Koleske DD, Henry RL (2001) Current collapse and the role of carbon in AlGaN/GaN high electron mobility transistors grown by metalorganic vapor-phase epitaxy. Appl Phys Lett 79:21

Yi C, Wang R, Huang W, Tang WC-W, Lau KM, Chen KJ (2007) Reliability of enhancement-mode AlGaN/GaN HEMTs fabricated by fluorine plasma treatment. Technical digest. IEEE International Electron Device Meeting, p. 389

Robison RR, Law ME (2002) Fluorine diffusion: models and experiments. Technical digest. IEEE International Electron Device Meeting, p. 883

Hayafuji N, Yamamoto Y, Ishida T, Sato K (1996) Degradation mechanism of the AlInAs/GaInAs high electron mobility transistor due to fluorine incorporation. Appl Phys Lett 69:4075

Ma C, Chen H, Zhou C, Huang S, Yuan L, Roberts J, Chen KJ (2010) Reliability of enhancement-mode AlGaN/GaN HEMTs under ON-state gate overdrive. Technical digest. IEEE International Electron Device Meeting, p. 476

Yuan L, Wang M, Chen KJ (2008) Atomistic modeling of fluorine implantation and diffusion in III-nitride semiconductors.Technical digest. IEEE International Electron Device Meeting, p. 543

Wang MJ, Yuan L, Cheng CC, Beling CD, Chen KJ (2009) Defect formation and annealing behaviors of fluorine-implanted GaN layers revealed by positron annihilation spectroscopy. Appl Phys Lett 94:061910

Li BK, Chen KJ, Lau KM, Ge WK, Wang JN (2008) Characterization of fluorine-plasma-induced deep centers in AlGaN/GaN heterostructure by persistent photoconductivity. Phys Stat Sol C 5:1892

Khan MA, Hu X, Tarakji A, Simin G, Yang J, Gaska R, Shur MS (2000) AlGaN/GaN metal–oxide–semiconductor heterostructure field-effect transistors on SiC substrates. Appl Phys Lett 77:1339

Chen KJ, Zhou C (2011) Enhancement-mode AlGaN/GaN HEMT and MIS-HEMT technology. Stat Sol A 208:434

Wang R, Cai Y, Tang C-W, Lau KM, Chen KJ (2006) Enhancement-mode Si3N4/AlGaN/GaN MISHFETs. IEEE Electron Device Lett 27:793

Huang S, Jiang Q, Yang S, Zhou C, Chen KJ (2012) Effective passivation of AlGaN/GaN HEMTs by ALD-grown AlN thin film. IEEE Electron Device Lett 33:516

Tang Z, Jiang Q, Lu Y, Huang S, Yang S, Tang X, Chen KJ (2013) 600-V normally-off SiNx/AlGaN/GaN MIS-HEMT with large gate swing and low current collapse. IEEE Electron Device Lett 34:1373

Yang S, Tang Z, Wong K-Y, Lin Y-S, Liu C, Lu Y, Huang S, Chen KJ (2013) High-quality interface in Al2O3/GaN/AlGaN/GaN MIS structures with in situ pre-gate plasma nitridation. IEEE Electron Device Lett 34:1497

Lu Y, Yang S, Jiang Q, Tang Z, Li B, Chen KJ (2013) Characterization of VT-instability in enhancement-mode Al2O3-AlGaN/GaN MIS-HEMTs. Phys Stat Sol C 10:1397

Chu RM, Brown D, Zehnder D, Chen X, Williams A, Li R, Chen M, Newell S, Boutros K (2012) Normally-off GaN-on-Si metal-insulator-semiconductor field-effect transistor with 600-V blocking capability at 200 °C. Proceeding of 24th international symposium on power semiconductor devices and ICs, p. 237

Yang S, Liu S, Liu C, Chen KJ (2014) Thermally induced threshold voltage instability of III-Nitride MIS-HEMTs and MOSC-HEMTs: underlying mechanisms and optimization schemes. Technical digest. IEEE International Electron Device Meeting, p. 389

Liu C, Yang S, Liu S, Tang Z, Wang H, Jiang Q, Chen KJ (2015) Thermally stable enhancement-mode GaN metal-insulator-semiconductor high-electron-mobility transistor with partially recessed fluorine-implanted barrier. IEEE Electron Device Lett 36:318

Liu S, Yang S, Tang Z, Jiang Q, Liu C, Wang M, Chen KJ (2014) Al2O3/AlN/GaN MOS-channel-HEMTs with an AlN interfacial layer. IEEE Electron Device Lett 35:723

Wong K-Y, Chen W, Liu X, Zhou C, Chen KJ (2010) GaN smart power IC technology. Phys Stat Sol B 247:1732

Chen KJ, Kwan AMH, Jiang Q (2014) Technology for III-N heterogeneous mixed-signal electronics. Phys Stat Sol A 211:769

Chen W, Wong KY, Huang W, Chen KJ (2008) High-performance AlGaN/GaN lateral field-effect rectifiers compatible with high electron mobility transistors. Appl Phys Lett 92:253501

Chen W, Wong KY, Chen KJ (2009) Single-chip boost converter using monolithically integrated AlGaN/GaN lateral field-effect rectifier and normally-off HEMT. IEEE Electron Device Lett 30:430

Cai Y, Cheng Z, Yang Z, Tang WC-W, Lau KM, Chen KJ (2006) Monolithically integrated enhancement/depletion-mode AlGaN/GaN HEMT inverters and ring oscillators using CF4 plasma treatment. IEEE Trans Electron Devices 53:2223

Bahat-Treidel E, Hilt O, Zhytnytska R, Wentzel A, Meliani C, Würfl J, Tränkle G (2012) Fast-switching GaN-based lateral power schottky barrier diodes with low onset voltage and strong reverse blocking. IEEE Electron Device Lett 33:357

Cai Y, Cheng Z, Yang Z, Tang WC-W, Lau KM, Chen KJ (2007) High temperature operation of AlGaN/GaN HEMTs direct-coupled FET logic (DCFL) integrated circuits. IEEE Electron Device Lett 28:328

Wong K-Y, Chen WJ, Chen KJ (2010) Integrated voltage reference generator for GaN smart power chip technology. IEEE Trans Electron Devices 57:952

Liu X, Chen KJ (2011) GaN Single-polarity power supply bootstrapped comparator for high temperature electronics. IEEE Electron Device Lett 32:27

Kwan AMH, Liu X, Chen KJ (2012) Integrated gate-protected HEMTs and mixed-signal functional blocks for GaN smart power ICs. Technical digest. IEEE International Electron Device Meeting, p. 7.3.1

Kwan AM, Guan Y, Liu X, Chen KJ (2014) A highly linear integrated temperature sensor on a GaN smart power IC platform. IEEE Trans Electron Devices 61:2970

Jiang Q, Tang Z, Liu C, Lu Y, Chen KJ (2014) Substrate-coupled cross-talk effects on an AlGaN/GaN-on-Si smart power IC platform. IEEE Trans Electron Devices 61:762

Wang H, Kwan AM, Jiang Q, Chen KJ (2015) A GaN pulse width modulation integrated circuit for GaN power converters. IEEE Trans Electron Devices 62:1143

Acknowledgments

The author would like to thank his former students and postdoctoral fellows for the key contributions they have made to the work described in this chapter. They are Drs. Yong Cai, Ruonan Wang, Li Yuan, Maojun Wang, Wanjun Chen, Baikui Li, King Yuen Wong, Chunhua Zhou, Alex Man Ho Kwan, Shu Yang, Cheng Liu, and Hanxing Wang. This work also greatly benefited from collaboration with Prof. Kei May Lau and Prof. Jiannong Wang at Hong Kong University of Science and Technology.

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2017 Springer International Publishing Switzerland

About this chapter

Cite this chapter

Chen, K.J. (2017). Fluorine-Implanted Enhancement-Mode Transistors. In: Meneghini, M., Meneghesso, G., Zanoni, E. (eds) Power GaN Devices. Power Electronics and Power Systems. Springer, Cham. https://doi.org/10.1007/978-3-319-43199-4_12

Download citation

DOI: https://doi.org/10.1007/978-3-319-43199-4_12

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-319-43197-0

Online ISBN: 978-3-319-43199-4

eBook Packages: EngineeringEngineering (R0)